Данное изобретение относится к области вычислительной техники, а именно к подключаемым портативным сопроцессорам с изменяемой системой команд и способам их применения, и может быть использовано в цифровых вычислительных системах, особенно в маломощных и портативных, таких как лэптопы, нетбуки, портативные компьютеры и т.д. Время от времени пользователям подобных устройств необходимо выполнять разнообразные ресурсоемкие, но в то же время хорошо параллелизуемые задачи (например, в ходе выполнения специализированных функций графических редакторов или криптографического программного обеспечения). В этом случае особенно ощущается недостаток производительности.

Существующие средства повышения скорости выполнения хорошо параллелизуемых вычислительных задач, предоставляемые графическими процессорами (GPU - graphical processing units) видеоадаптеров высокого уровня, в большинстве случаев недоступны, поскольку в маломощных (низкопроизводительных) и дешевых компьютерных системах в подавляющем большинстве случаев находят применение лишь специализированные встроенные версии GPU, не располагающие подобным функционалом.

Наборы инструкций современных центральных процессоров предоставляют множество расширений, позволяющих обеспечить параллелизм на уровне данных (так называемые SIMD - "single instruction, multiply data" инструкции), ориентированных на требования мультимедийных приложений, однако их использование не столь эффективно из-за невозможности одновременной обработки действительно больших объемов данных (более 10-15 «машинных слов»). Кроме того, инструкции, предоставляемые подобными расширениями, формируют ортогональный набор базовых команд, что приводит к необходимости исполнения большой последовательности инструкций для выполнения комплексных операций (например, криптографического преобразования блока данных). Исполнение подобного набора операций требует большого количества времени, что ведет лишь к малому повышению производительности за счет параллелизации, особенно в случае скалярной организации вычислительного конвейера центрального процессора (подобные системы часто используются во встроенных и недорогих цифровых компьютерах), которая не предоставляет дополнительные блоки исполнения для инструкций мультимедийных расширений.

Для выполнения комплексных, определяемых конкретным пользователем инструкций, без затрат времени центрального процессора применяют сопроцессоры с изменяемой системой команд.

Известен перестраиваемый сопроцессор, приведенный в патенте US 6298366 [1], предназначенный для выполнения множественных операций умножения с накоплением, который содержит несколько пар умножителей, несколько сумматоров, получающих соответствующие выходные данные от умножителей, и, по меньшей мере, один вторичный сумматор, получающий выходные данные от первичных сумматоров. Один умножитель из каждой пары имеет фиксированный блок сдвига влево результата умножения. Другой умножитель в каждой паре содержит блок сдвига вправо результата умножения. На выходе первого умножителя находится мультиплексор, осуществляющий передачу на дальнейшую обработку либо результата умножения после сдвига, либо знакового расширения результата. На выходе второго умножителя находится мультиплексор, осуществляющий передачу на дальнейшую обработку либо результата умножения, либо его версии с осуществленным сдвигом вправо, либо одного из операндов блока умножения. Данные с выходов мультиплексоров поступают на первичный набор сумматоров. Промежуточный результат затем передают на вторичный суммирующий блок.

Недостаток данного сопроцессора заключается в том, что в нем отсутствует возможность применения программируемой логической интегральной схемы (PLD) общего назначения. Предложенный в патенте процесс реконфигурирования вычислительного конвейера устройства ограничен вследствие фиксированной структуры внутренних элементов - только малый набор арифметических операций может быть организован в единую инструкцию высокого уровня. В патенте также нет указания на возможность организации сопроцессора в качестве независимого устройства, подключаемого к периферийной шине цифрового компьютера.

В патенте US 6467009 [2] описана реконфигурируемая сопроцессорная система, содержащая процессор и программируемую логическую интегральную схему, соединенные между собой внутренней системной шиной и располагающиеся на единой интегральной схеме.

Недостатком данного аналога является то, что сопроцессорная система расположена на единой интегральной схеме (подложке) с центральным процессором (CPU) и внутренней системной шиной. Это делает сопроцессор постоянным элементом системы, что значительно снижает его портативность и делает невозможным его подключение лишь по необходимости.

Наиболее близким к заявленному изобретению является сопроцессор, описанный в патентной заявке US 2008/0028186 [3] и предназначенный для ускоренного выполнения вычислений, который содержит программируемую пользователем вентильную матрицу (FPGA - Field Programmable Gate Array) и программируемую логическую интегральную схему (PLD - Programmable Logic Device), соединенную с FPGA и предназначенную для ее конфигурирования. Долговременная память соединена с PLD и предназначена для хранения начального потока двоичных данных конфигурации FPGA. После завершения начального цикла конфигурирования вентильная матрица FPGA напрямую взаимодействует, по меньшей мере, с одним микропроцессором через специализированную микропроцессорную шину. Данный сопроцессор выбран в качестве прототипа заявленного изобретения.

Недостаток организации сопроцессора прототипа заключается в отсутствии возможности его подключения к периферийной шине цифрового компьютера, что ведет к невозможности достижения высокой портативности и динамического подключения по требованию. Более того, предложенное прямое соединение «центральный процессор - сопроцессор» и «сопроцессор - память» посредством шины микропроцессора делает невозможным применение изобретения для портативных низкопроизводительных систем, таких как лэптопы или ноутбуки (они не позволяют пользователю извне присоединять устройства к микропроцессорной шине).

Задачей заявленного изобретения является создание подключаемого портативного сопроцессора с изменяемой системой команд, предназначенного для увеличения скорости вычислений, например, за счет передачи хорошо параллелизуемых задач от центрального процессора цифрового компьютера сопроцессору с изменяемой высокоуровневой системой команд, за счет упрощения интеграции процедур управления деятельностью сопроцессора в существующее программное решение базового цифрового компьютера, а также с улучшенной функциональностью и удобством использования за счет возможности подключения сопроцессора к базовому цифровому компьютеру, по желанию, через одну из периферийных шин.

Технический результат достигается за счет создания подключаемого портативного сопроцессора с изменяемой системой команд, содержащего соединенные между собой программируемую логическую интегральную схему, микроконтроллер и контроллер периферийной шины, причем контроллер периферийной шины выполнен с возможностью динамического присоединения к цифровому компьютеру через периферийную шину и с возможностью обеспечения передачи данных между сопроцессором и цифровым компьютером, при этом микроконтроллер выполнен с возможностью анализа, на стадии инициализации, пакета конфигурации, получаемого от центрального процессора, и выполнения переконфигурирования программируемой логической интегральной схемы или ее части в соответствии с данными пакета конфигурации, а на стадии выполнения программы в цифровом компьютере, когда необходимо выполнение переданной сопроцессору процедуры, микропроцессор выполнен с возможностью подачи аргументов вызова процедуры, входящих в состав пакета «запрос выполнения», получаемого от центрального процессора, на вход программируемой логической интегральной схемы, с возможностью инициирования выполнения процедуры программируемой логической интегральной схемой, с возможностью оповещения центрального процессора об окончании выполнения процедуры, а также с возможностью получения результатов выполнения запрошенной процедуры с выходов программируемой логической интегральной схемы и передачи пакета результатов выполнения процедуры в центральный процессор, при этом программируемая логическая интегральная схема выполнена с возможностью выполнения процедуры под контролем микропроцессора и с возможностью подачи результатов выполнения на выходы, связанные с микропроцессором.

Для функционирования подключаемого портативного сопроцессора с изменяемой системой команд важно, чтобы пакет «запрос выполнения» содержал название процедуры, набор аргументов и уникальный идентификатор вызова для случаев нахождения более одной команды в очереди на выполнение сопроцессором.

Технический результат достигается также за счет разработки способа применения подключаемого портативного сопроцессора с изменяемой системой команд. В соответствии с заявляемым способом предусматривается выполнение следующих операций:

- присоединяют сопроцессор к периферийной шине цифрового компьютера, содержащего центральный процессор;

- выполняют инициализацию, при этом формируют в цифровом компьютере, по меньшей мере, один пакет конфигурации программируемой логической интегральной схемы сопроцессора, который состоит из поставленных в соответствие битовых потоков конфигурации программируемой логической интегральной схемы и названия процедуры;

- отправляют посредством центрального процессора пакет конфигурации в сопроцессор;

- анализируют посредством микроконтроллера сопроцессора пакет конфигурации и выполняют переконфигурирование программируемой логической интегральной схемы или ее части в соответствии с данными пакета конфигурации;

- при выполнении программы в цифровом компьютере, когда необходимо выполнение процедуры, переданной сопроцессору из цифрового компьютера, выполняют следующие операции:

посредством центрального процессора отправляют в сопроцессор пакет «запрос выполнения» от приложения;

посредством микроконтроллера сопроцессора подают аргументы вызова процедуры, входящие в состав пакета «запрос выполнения», получаемого от центрального процессора, на вход программируемой логической интегральной схемы, инициируют выполнение процедуры программируемой логической интегральной схемой;

посредством программируемой логической интегральной схемы под контролем микропроцессора выполняют процедуру;

посредством микроконтроллера оповещают центральный процессор об окончании выполнения процедуры;

посредством центрального процессора отправляют в сопроцессор пакет «запрос результатов»;

посредством микроконтроллера сопроцессора получают результаты выполнения запрошенной процедуры с выходов программируемой логической интегральной схемы и передают пакет результатов выполнения процедуры в центральный процессор,

при этом в описанных выше операциях пересылают данные между процессором и сопроцессором по периферийной шине посредством контроллера периферийной шины.

Для лучшего понимания заявленного изобретения далее приводится его подробное описание с соответствующими чертежами.

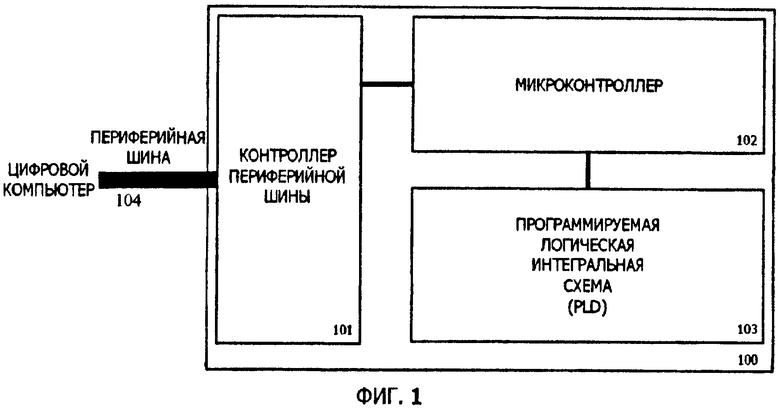

Фиг.1. Схема портативного сопроцессора с изменяемой системой команд, выполненная согласно изобретению.

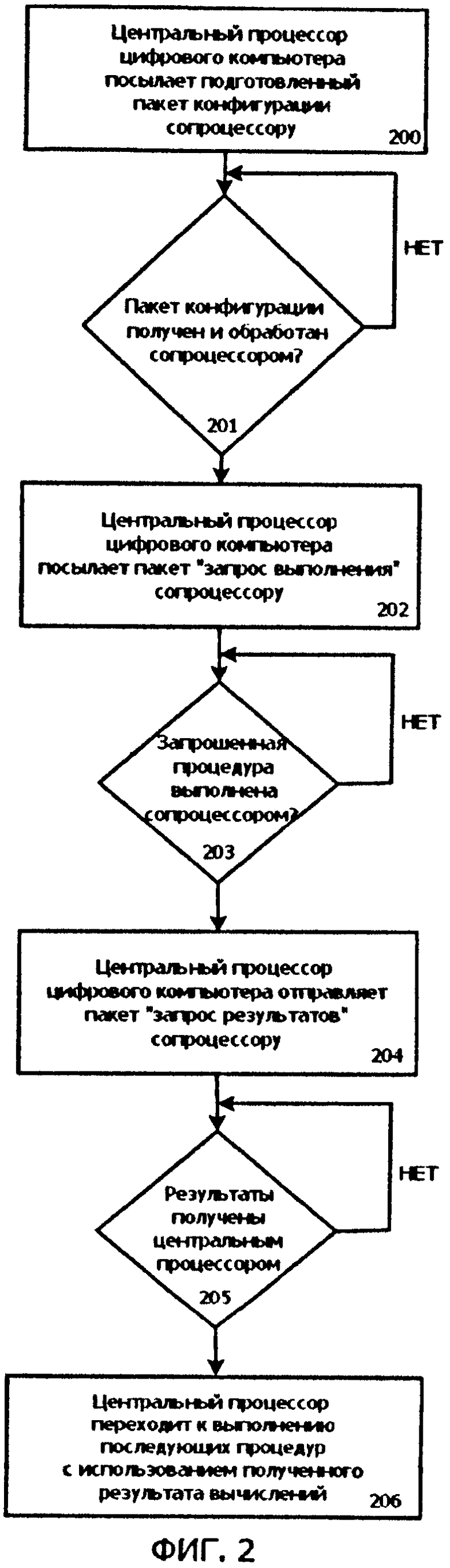

Фиг.2. Диаграмма функционирования портативного сопроцессора с изменяемой системой команд со стороны цифрового компьютера, выполненная согласно изобретению.

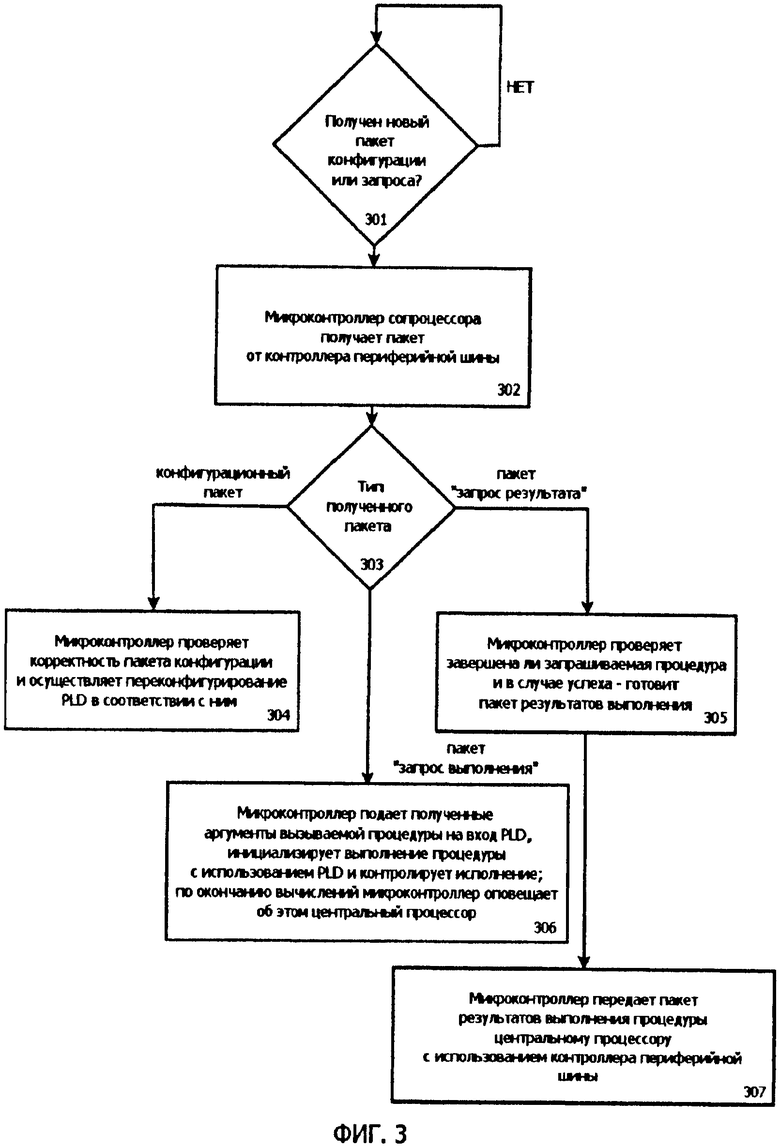

Фиг.3. Диаграмма функционирования портативного сопроцессора с изменяемой системой команд со стороны сопроцессора, выполненная согласно изобретению.

Сопроцессор 100 состоит из трех основных элементов (Фиг.1): контроллера 101 интерфейса периферийной шины 104 (PBIC - Peripheral bus interface controller), который обеспечивает возможность взаимодействия с центральным процессором по периферийной шине 104, микроконтроллера 102 (MD - Microcontroller device), который отвечает за реконфигурацию программируемой логической интегральной схемы и обработку входных и выходных пакетов данных, и программируемой логической интегральной схемы 103 (PLD - Programmable Logic Device), которая может быть выполнена в виде CPLD, FPGA и т.д. и отвечает за параллельное, с использованием или нет подхода вычислительного конвейера, выполнение изменяемого набора инструкций в соответствии с заданным соединением внутренних логических элементов.

Заявленный портативный сопроцессор с изменяемой системой команд применяют следующим образом (Фиг.1-3). Сначала присоединяют сопроцессор 100 к периферийной шине 104 цифрового компьютера. Перед постановкой задачи на выполнение сопроцессором 100 производят инициализацию, при этом выполняют следующие операции. Потенциально параллелизуемые блоки кода программы преобразовывают в пакет (файл) конфигурации программируемой логической интегральной схемы 103 сопроцессора одним из следующих методов: посредством трансляции кода приложения из высокоуровневого языка программирования (PL - programming language) в язык описания организации аппаратной части (HDL - hardware description language), а затем - в битовый поток настройки программируемой логической интегральной схемы 103; посредством написания кода HDL вручную на основе требуемого алгоритма и применения транслятора HDL или посредством доступного программного обеспечения. Пакет (файл) конфигурации содержит битовый поток настройки программируемой логической интегральной схемы, а именно информацию о соединении внутренних цифровых элементов, необходимом для корректного выполнения запрашиваемой процедуры. Если в приложении требуется выполнение нескольких различных процедур с использованием сопроцессора 100, то последовательно формируют несколько конфигурационных файлов или один объединенный конфигурационный файл, содержащий описание всех необходимых процедур.

Затем приложение отправляет посредством центрального процессора сформированный пакет конфигурации, состоящий из поставленных в соответствие битовых потоков конфигурации программируемой логической интегральной схемы и названий процедуры, в сопроцессор (с использованием предоставляемой операционной системой или написанной вручную подпрограммы доступа к периферийной шине 104) (шаг 200).

Получая пакет конфигурации через периферийную шину 104 цифрового компьютера с использованием PBIC, микроконтроллер 102 анализирует его и производит конфигурирование программируемой логической интегральной схемы 103 или ее части в соответствии с полученными данными (шаг 304). С этого момента программируемая логическая интегральная схема 103 или ее часть может выполнять требуемый набор команд (процедур) самостоятельно.

При дальнейшем выполнении программы, когда необходимо выполнение переданной сопроцессору 100 процедуры, приложение посредством центрального процессора посылает пакет «запрос выполнения» сопроцессору 100 (пакет «запрос выполнения» содержит название процедуры, набор аргументов и уникальный идентификатор вызова) (шаг 202).

Микроконтроллер 102 анализирует пакет «запрос выполнения» и планирует его выполнение предварительно сконфигурированной программируемой логической интегральной схемой 103 (шаг 306).

После завершения выполнения запрошенной процедуры с использованием программируемой логической интегральной схемы 103 микроконтроллер 102 уведомляет инициатора запроса (исходное приложение) с помощью команд, предоставляемых протоколом периферийной шины 104 (например, с помощью системного прерывания) (шаг 306).

Затем приложение может запросить результаты вызова процедуры у сопроцессора 100 с помощью пакета «запрос результатов» (шаг 204). Результаты выполнения возвращают посредством сопроцессора 100 по периферийной шине 104 с помощью пакета «результаты выполнения», который содержит уникальный идентификатор вызова, полученный на этапе запроса выполнения, и результаты вызова процедуры (шаг 307). После получения результатов выполнения центральный процессор переходит к выполнению последующих процедур с использованием данных результатов (шаг 206).

Заявленное изобретение обеспечивает дополнительный прирост вычислительной производительности для задач, допускающих параллельное выполнение (которые часто возникают, например, в ходе выполнения специализированных функций графических редакторов или криптографического программного обеспечения).

Благодаря упрощенному протоколу взаимодействия для эффективного применения заявляемого устройства требуется лишь небольшое изменение кода исходного программного продукта, поэтому многие производители программного обеспечения могут адаптировать свою продукцию для поддержки сопроцессора.

Следует отметить, что приведенный выше вариант выполнения изобретения изложен, в основном, с целью иллюстрации изобретения, и специалистам ясно, что возможны разные модификации, добавления и замены, не выходящие из объема и смысла настоящего изобретения, раскрытого в прилагаемой формуле изобретения.

Изобретение относится к подключаемым портативным сопроцессорам с изменяемой системой команд и способу их применения. Техническим результатом является повышение быстродействия работы процессора за счет упрощения интеграции процедур управления деятельностью сопроцессора в существующее программное решение базового цифрового компьютера. Устройство содержит соединенные между собой программируемую логическую интегральную схему, микроконтроллер и контроллер периферийной шины. Микроконтроллер выполнен с возможностью анализа на стадии инициализации пакета конфигурации, получаемого от центрального процессора, и переконфигурирования программируемой логической интегральной схемы, и с возможностью подачи аргументов вызова процедуры, входящих в состав пакета «запрос выполнения», получаемого от центрального процессора, на вход программируемой логической интегральной схемы. 2 н. и 1 з.п. ф-лы, 3 ил.

1. Подключаемый портативный сопроцессор с изменяемой системой команд, содержащий соединенные между собой программируемую логическую интегральную схему, микроконтроллер и контроллер периферийной шины, причем контроллер периферийной шины выполнен с возможностью динамического присоединения к цифровому компьютеру через периферийную шину и с возможностью обеспечения передачи данных между сопроцессором и цифровым компьютером, при этом микроконтроллер выполнен с возможностью анализа на стадии инициализации пакета конфигурации, получаемого от центрального процессора, и выполнения переконфигурирования программируемой логической интегральной схемы или ее части в соответствии с данными пакета конфигурации, причем микропроцессор выполнен с возможностью подачи, на стадии выполнения программы в цифровом компьютере, когда необходимо выполнение переданной сопроцессору процедуры, аргументов вызова процедуры, входящих в состав пакета «запрос выполнения», получаемого от центрального процессора, на вход программируемой логической интегральной схемы, с возможностью инициирования выполнения процедуры программируемой логической интегральной схемой, с возможностью оповещения центрального процессора об окончании выполнения процедуры, а также с возможностью получения результатов выполнения запрошенной процедуры с выходов программируемой логической интегральной схемы и передачи пакета результатов выполнения процедуры в центральный процессор, при этом программируемая логическая интегральная схема выполнена с возможностью выполнения процедуры под контролем микропроцессора и с возможностью подачи результатов выполнения на выходы, связанные с микропроцессором.

2. Подключаемый портативный сопроцессор с изменяемой системой команд по п.1, отличающийся тем, что пакет «запрос выполнения» содержит название процедуры, набор аргументов и уникальный идентификатор вызова, необходимый в случае нахождения более одной команды в очереди на выполнение сопроцессора.

3. Способ применения подключаемого портативного сопроцессора с изменяемой системой команд, заключающийся в выполнении следующих операций: присоединяют сопроцессор к периферийной шине цифрового компьютера, содержащего центральный процессор; выполняют инициализацию, формируя при этом в цифровом компьютере, по меньшей мере, один пакет конфигурации программируемой логической интегральной схемы сопроцессора, который состоит из поставленных в соответствие битовых потоков конфигурации программируемой логической интегральной схемы и названия процедуры; отправляют посредством центрального процессора пакет конфигурации в сопроцессор; анализируют посредством микроконтроллера сопроцессора пакет конфигурации и выполняют переконфигурирование программируемой логической интегральной схемы или ее части в соответствии с данными пакета конфигурации; при выполнении программы в цифровом компьютере, когда необходимо выполнение процедуры, переданной сопроцессору из цифрового компьютера, выполняют следующие операции: отправляют в сопроцессор посредством центрального процессора пакет «запрос выполнения» от приложения; подают посредством микроконтроллера сопроцессора аргументы вызова процедуры, входящие в состав пакета «запрос выполнения», получаемого от центрального процессора, на вход программируемой логической интегральной схемы и инициируют выполнение процедуры программируемой логической интегральной схемой; выполняют процедуру посредством программируемой логической интегральной схемы под контролем микропроцессора; оповещают центральный процессор посредством микроконтроллера об окончании выполнения процедуры; отправляют в сопроцессор посредством центрального процессора пакет «запрос результатов»; получают посредством микроконтроллера сопроцессора результаты выполнения запрошенной процедуры с выходов программируемой логической интегральной схемы и передают пакет результатов выполнения процедуры в центральный процессор, при этом в описанных выше операциях пересылают данные между процессором и сопроцессором по периферийной шине посредством контроллера периферийной шины.

| US 2008028186 A1, 31.01.2008 | |||

| US 6298366 B1, 02.10.2001 | |||

| US 6467007 В1, 15.10.2002 | |||

| ОБРАБОТКА ДАННЫХ С ПОМОЩЬЮ СОПРОЦЕССОРА | 2001 |

|

RU2275678C2 |

| Программируемый сопроцессор | 1988 |

|

SU1675880A1 |

Авторы

Даты

2011-02-10—Публикация

2009-09-08—Подача