Область техники, к которой относится изобретение

Варианты осуществления относятся к обработке прерывания.

Уровень техники

Устройства, такие как портативные устройства, например смартфоны, планшетные устройства и т.д., могут иметь высокую частоту асинхронных событий, которые происходят в результате разнообразия периферийных устройств, которые могут обеспечивать ввод данных. Например, асинхронные события могут включать в себя датчики движения, датчики света, сенсорный экран и т.д. Кроме того, такие портативные устройства могут принимать синхронные события, такие как периодические прерывания, относящиеся к пейджинговой передаче сотовой сети, периодическим событиям таймера и т.д.

Сообщения прерывания ("прерывания"), которые ассоциированы с синхронными и асинхронными событиями, поступающие в процессор, могут привести к постоянным частым переключениям процессора, например чрезмерным переключением между активным состоянием и неактивным состоянием, что, в свою очередь, может привести к высокому потреблению энергии из-за затрат энергии на "включение" устройства в результате перехода из неактивного в активное состояние, в результате чего может произойти уменьшение периода времени между зарядами источника питания, например аккумуляторной батареи.

Краткое описание чертежей

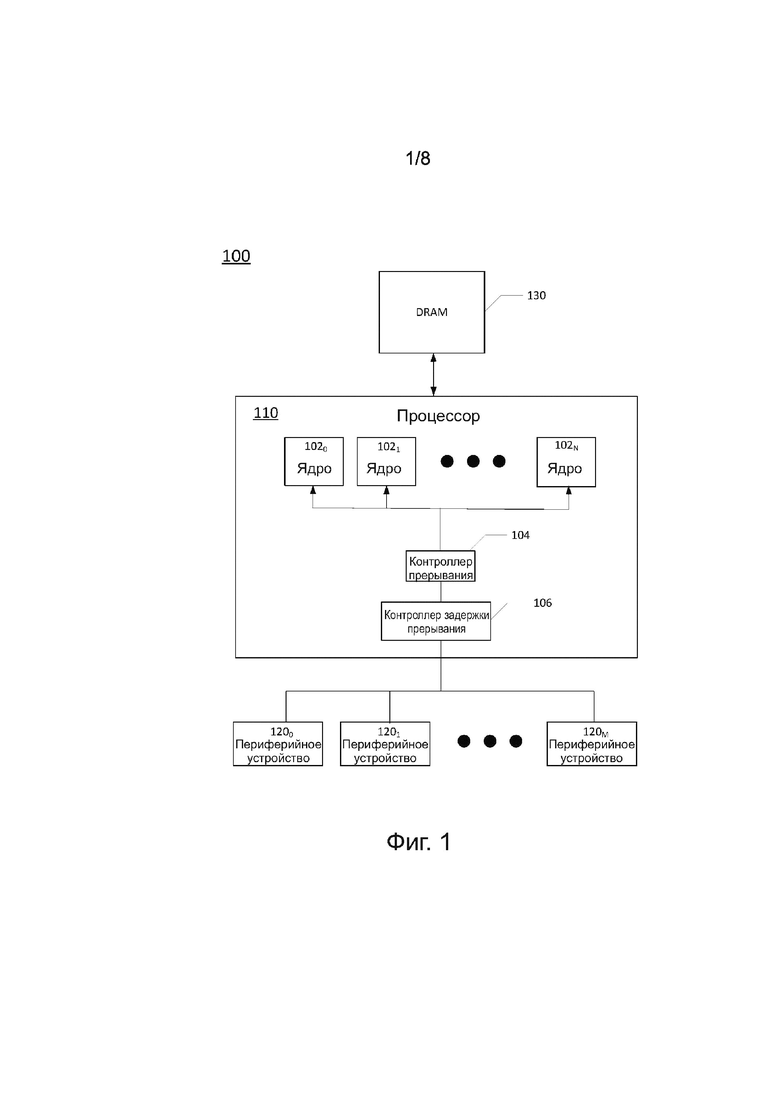

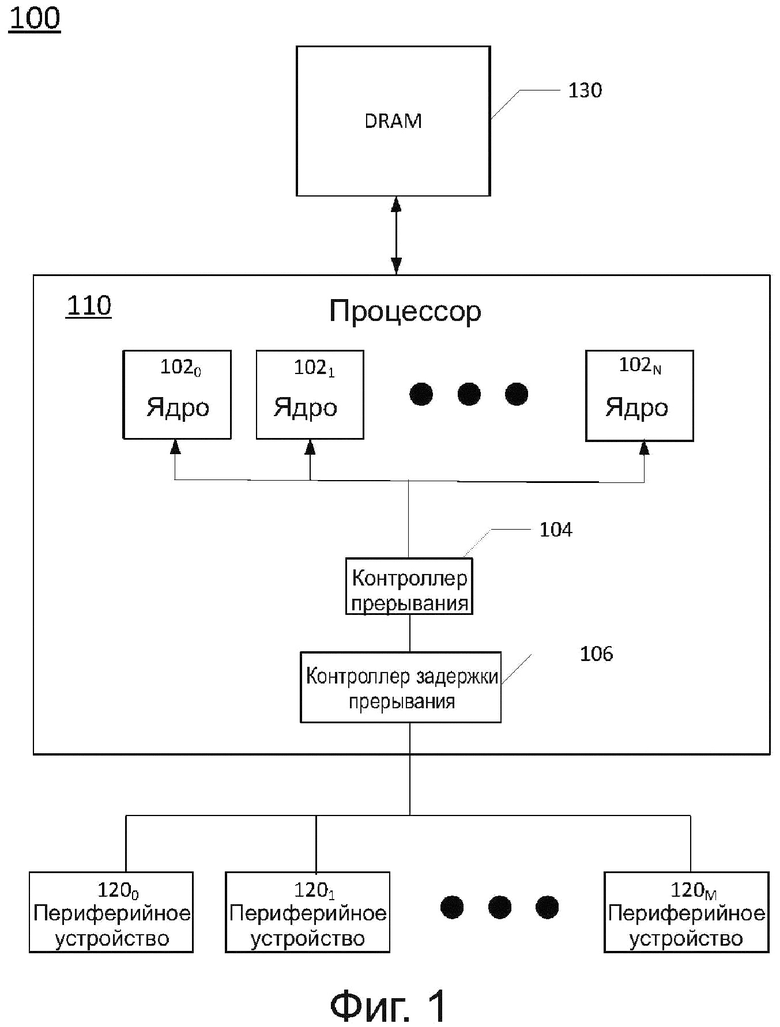

На фиг. 1 показана блок-схема системы в соответствии с вариантом осуществления настоящего изобретения.

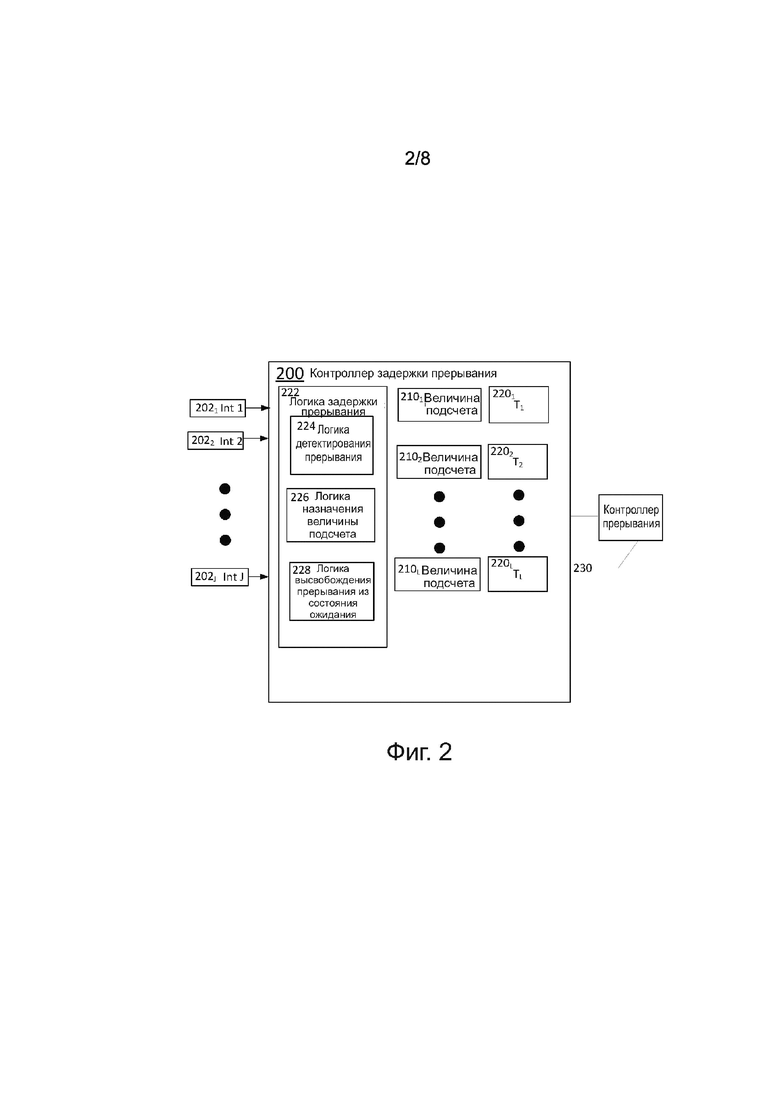

На фиг. 2 показана блок-схема контроллера задержки прерывания в соответствии с вариантом осуществления настоящего изобретения.

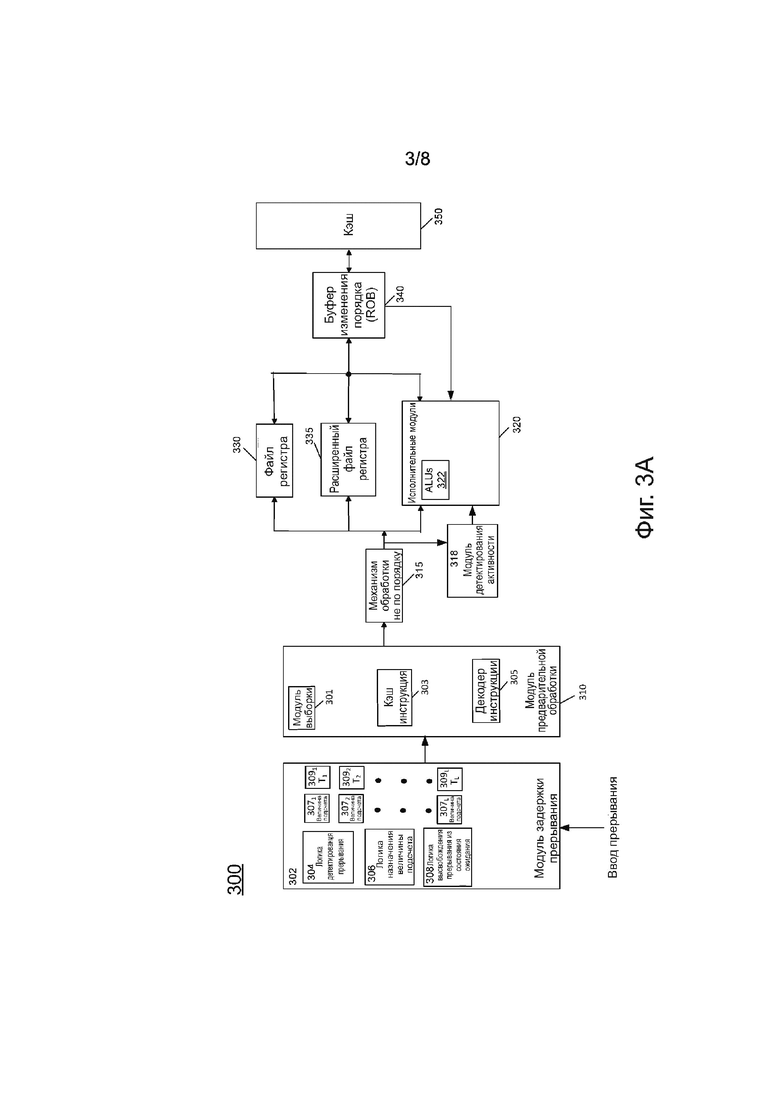

На фиг. 3A показана блок-схема ядра процессора в соответствии с вариантом осуществления настоящего изобретения.

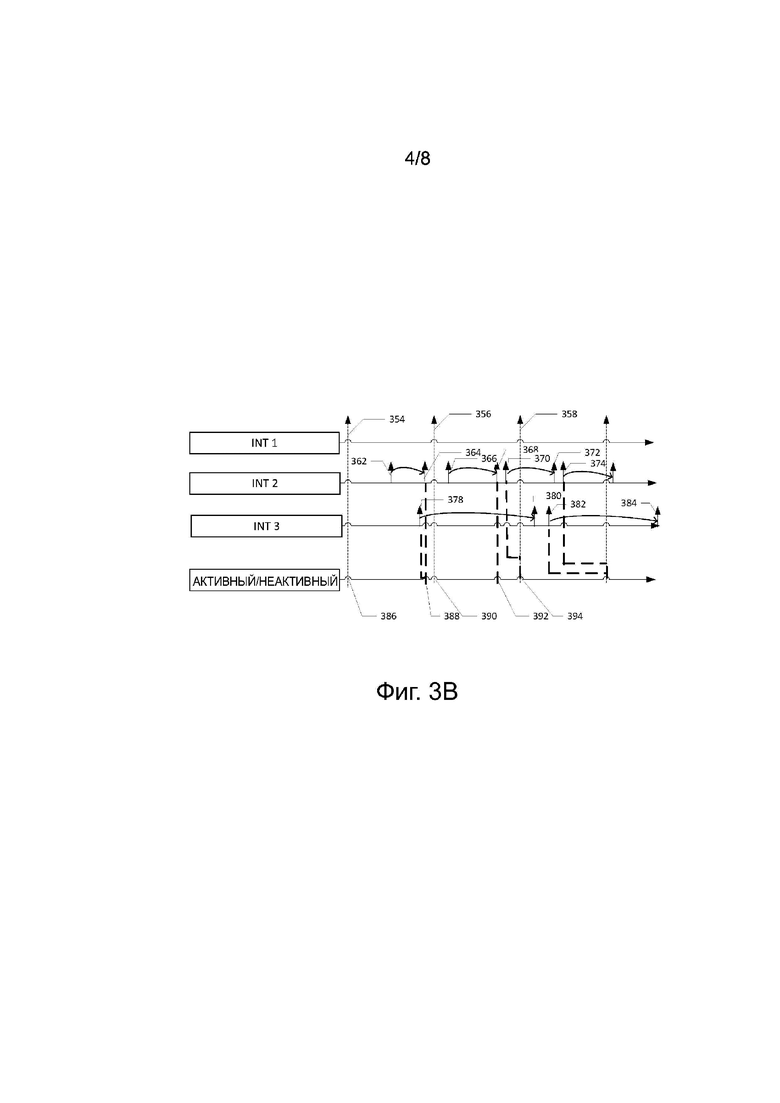

На фиг. 3B показана временная диаграмма прерываний, предназначенных для обработки в соответствии с вариантом осуществления настоящего изобретения.

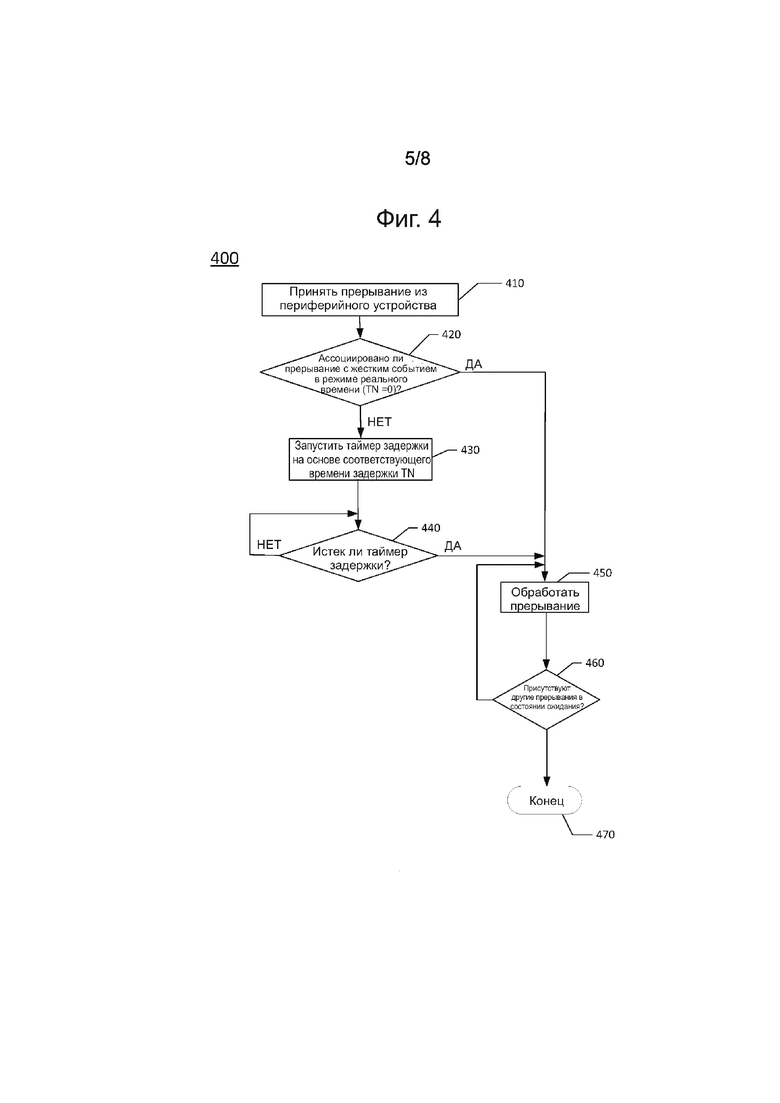

На фиг. 4 показана блок-схема последовательности операций способа обработки событий прерывания процессором в соответствии с вариантом осуществления настоящего изобретения.

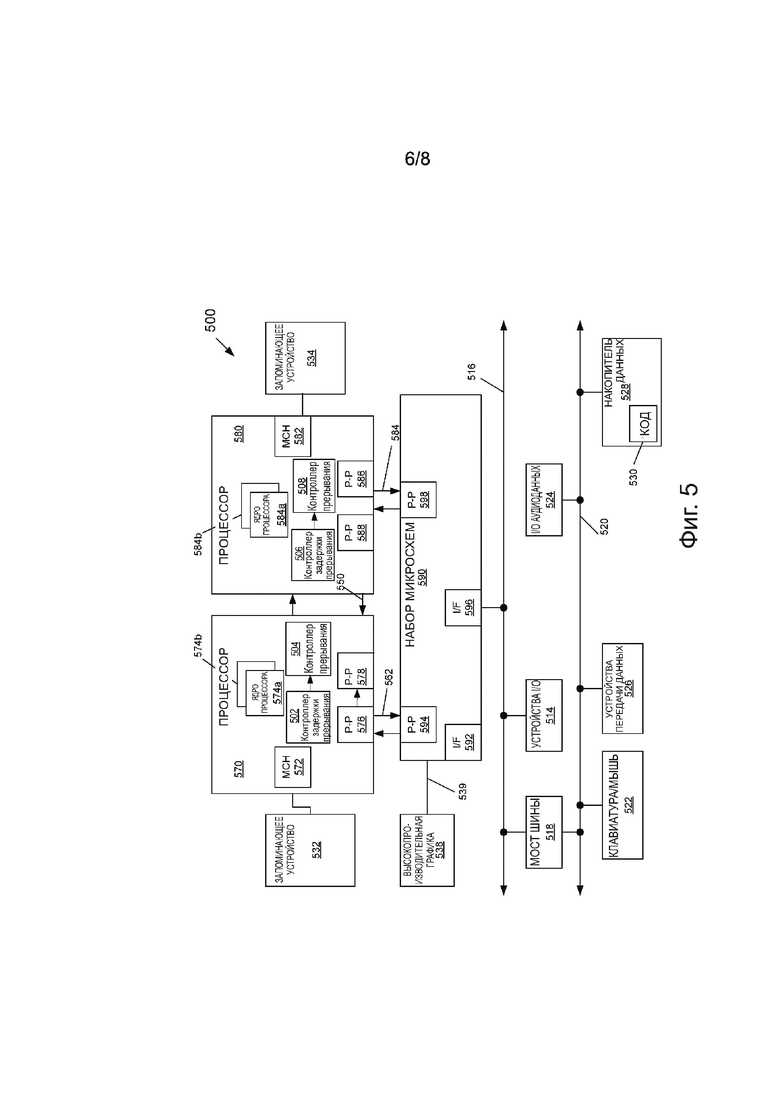

На фиг. 5 показана блок-схема системы в соответствии с вариантом осуществления настоящего изобретения.

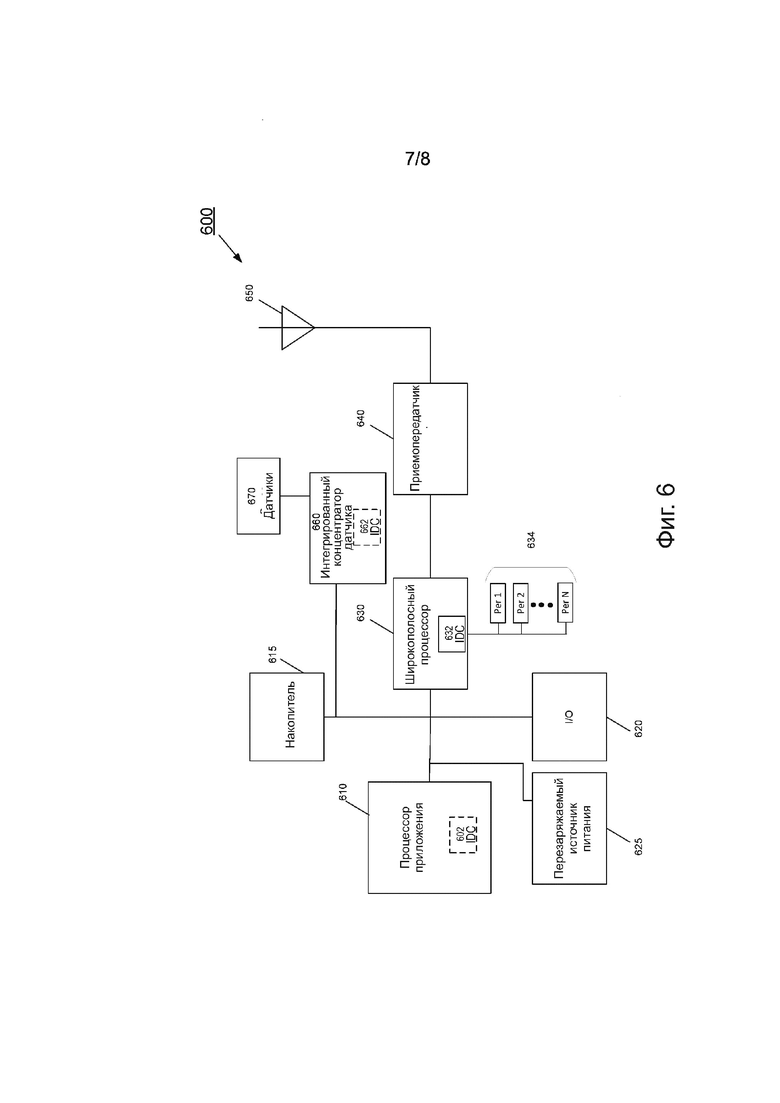

На фиг. 6 показана блок-схема системы в соответствии с другим вариантом осуществления настоящего изобретения.

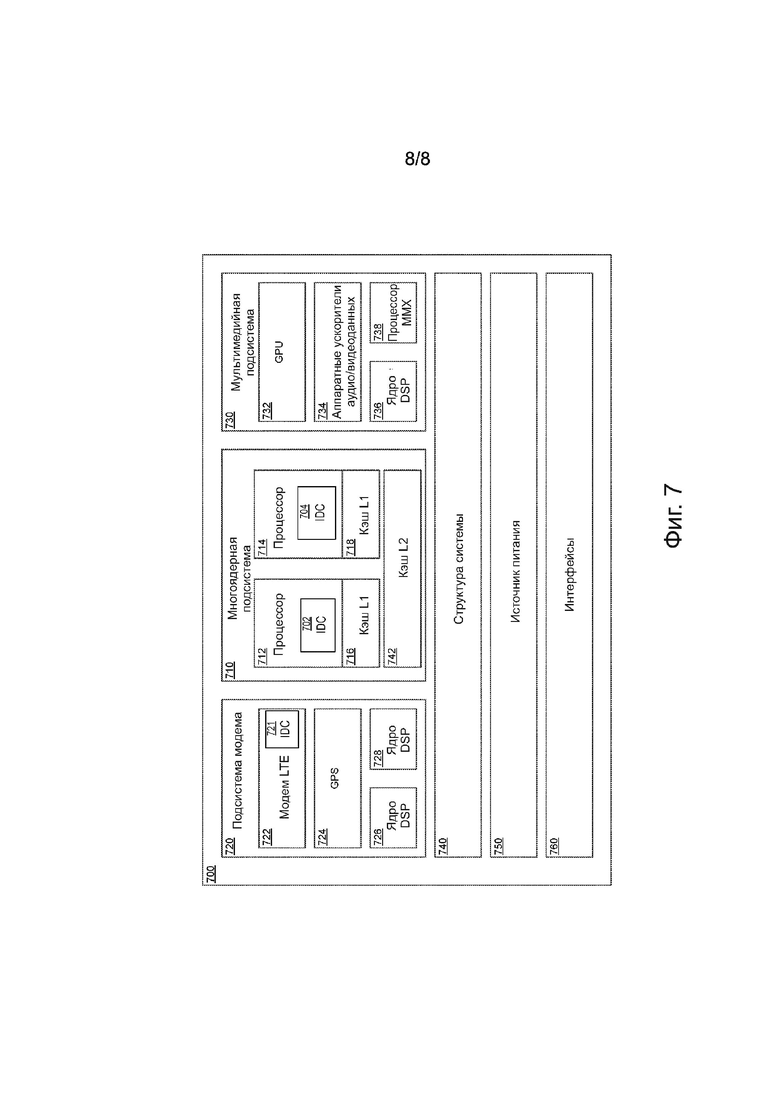

На фиг. 7 показана блок-схема системы на кристалле в соответствии с вариантом осуществления настоящего изобретения.

Подробное описание изобретения

Источники прерываний могут быть классифицированы в соответствии с характеристиками источника и требованиями для прерывания обработки, получаемыми из источника. Например, некоторые прерывания должны обслуживаться без преднамеренной задержки перед обработкой (“жесткие прерывания”, или “критические прерывания” в данном описании, например, периодические прерывания, ассоциированные, например, со стандартами сотовой передачи данных). Другие прерывания (здесь “мягкие прерывания”, или “некритические прерывания”) являются менее чувствительными ко времени и могут быть преднамеренно отсрочены на задержку времени, которая назначается в соответствии со свойством источника прерывания, например периферийное устройство/приложение.

В вариантах осуществления программируемое значение задержки может быть установлено для каждого события или группы событий. Прерывания могут быть сгруппированы таким образом, что процессор может обрабатывать (например, "пакетная обработка») множество прерываний, когда процессор активируют ("переключают в рабочее состояние") из неактивного состояния ("состояния ожидания"). Пакетная обработка прерываний может уменьшить общую величину подсчета активных/неактивных циклов, которые процессор выполняет в течение заданного интервала времени, что может уменьшить общее использование потребления энергии процессором.

В вариантах осуществления значение программируемого таймера задержки доступно для операционной системы для задержки обработки прерывания (например, путем выполнения обработчика, ассоциированного с прерыванием), например, когда процессор и/или система на кристалле (SoC) находятся в состоянии экономии энергии (неактивном состоянии), например, в одном из состояний отключенного питания усовершенствованного интерфейса управления вычислениями и питанием (ACPI), C1 - C6. Значения программируемой задержки для разных типов прерываний обеспечивают возможность выполнять обработку прерывания, как пакетную обработку, вместо обработки каждого прерывания по отдельности, которая может привести к значительному потреблению энергии из-за каждого перехода из неактивного в активное состояние процессора или SoC. В варианте осуществления обработка прерывания автоматически динамически группирует события на основе соответствующего времени задержки, назначенного для каждого прерывания.

На фиг. 1 показана блок-схема системы 100, в соответствии с вариантом осуществления настоящего изобретения. Система 100 включает в себя процессор 110, который включает в себя одно или больше ядер 1020 - 102N, контроллер 104 прерываний и контроллер 106 задержки прерывания, множество периферийных устройств 1200 - 120M, соединенных с процессором 110, и динамическое оперативное запоминающее устройство (DRAM) 130, соединенное с процессором 110.

Во время работы процессор 110 может принимать сообщения прерывания (также здесь называются "прерываниями") из одного или больше периферийных устройств 1200 - 120M. Одно или больше из прерываний ("жестких прерываний") может быть ассоциировано с соответствующим событием жесткого прерывания в режиме реального времени, для которого требуется обработка прерывания, во время ее приема, например, без преднамеренной задержки. Например, жесткое прерывание может быть ассоциировано с периодическим событием, относящимся к стандарту сотовой связи, и жесткое прерывание должно обрабатываться процессором 110 после приема, например, без преднамеренной задержки по времени.

Другие прерывания могут быть периодическими (например, синхронными) или апериодическими (например, асинхронными), но они не ассоциированы с событиями жесткого прерывания в режиме реального времени, и поэтому обработка таких прерываний (“мягких прерываний”) может быть задержана, например преднамеренно задержана по времени. Например, асинхронные прерывания могут быть ассоциированы с асинхронными событиями, такими как ввод датчика, сенсорного экрана, ввод данных, которые могут приниматься периодически, и т.д.

Для каждого периферийного устройства 1200 - 120M, которое формирует мягкие события (например, формирует мягкие прерывания), может быть назначена соответствующая задержка по времени для обработки каждого мягкого прерывания. Задержка по времени для обработки мягкого прерывания, принятого из периферийного устройства источника, может быть определена на основе характеристик периферийного устройства источника и может быть определена перед использованием системы 100. Например, один фактор, который может учитываться при определении приемлемой задержки по времени для мягких прерываний, может представлять собой частоту наихудшего случая частоты возникновений ассоциированного события. Например, если при оценке наихудшего случая, событие возникает каждые 100 миллисекунд, задержка 100 мкс для обработки ассоциированного прерывания могла бы оказать несущественное влияние на рабочие характеристики. Задержка по времени может быть предоставлена (например, сохранена в процессоре 110) перед приемом одного или больше прерываний процессором 110.

Жесткие прерывания, принятые контроллером 106 задержки прерывания от одного или больше периферийных устройств 1200 - 120M, могут быть переданы в контроллер 104 прерываний для обработки без преднамеренной задержки по времени. Когда процессор 110 принимает мягкое прерывание, контроллер 106 задержки прерывания может выбрать соответствующую задержку по времени (например, содержащуюся в контроллере 106 задержки прерывания) на основе периферийного устройства 120, которое предоставило мягкое прерывание. Для каждого принятого мягкого прерывания контроллер задержки прерывания может начать подсчет соответствующей задержки по времени, например, через соответствующий таймер, и когда соответствующий таймер достигает конца задержки по времени, мягкое прерывание может быть высвобождено для передачи в контроллер 104 прерываний и направлено контроллером 104 прерываний для обработки одним из ядер 1020-102n.

В варианте осуществления, когда принимают жесткое прерывание в процессоре 110 для немедленной обработки, контроллер 106 задержки прерывания может определять, ожидает ли какого-либо мягкого прерывания, например, ассоциированный таймер начала отсчета задержки по времени для мягкого прерывания и еще не закончил свой подсчет. Контроллер 106 задержки прерывания может высвободить одно или больше находящихся в состоянии ожидания мягких прерываний для контроллера 104 прерываний для обработки одним из ядер 1020 - 102N, например, без завершения подсчета ассоциированного таймера. Прерывания, которые высвобождаются для обработки ядром, должны быть обработаны, пока ядро активно, например, ядро остается активным от момента времени, в который было принято жесткое прерывание, до окончания обработки всех принятых мягких прерываний.

В другом варианте осуществления первое мягкое прерывание должно быть обработано первым ядром из ядер 1020 - 102N в результате истечения времени таймера, например ассоциированный таймер закончил свой подсчет соответствующей задержки по времени. Контроллер 106 задержки прерывания может высвободить одно или больше других находящихся в состоянии ожидания мягких прерываний с передачей в контроллер 104 прерываний для обработки первым ядром перед завершением каждой соответствующей задержки по времени. Прерывания, которые были высвобождены для обработки первым ядром, должны быть обработаны в режиме пакетной обработки, например обработаны, пока первое ядро является активным в результате обработки первого мягкого прерывания. Ядро должно оставаться активным до тех пор, пока обработка прерываний, которые были высвобождены, не будет закончена.

В каждом из описанных выше вариантов осуществления, когда определенное прерывание передают в контроллер прерывания для обработки, контроллер 106 задержки прерывания может высвобождать одно или больше прерываний, находящихся в состоянии ожидания, для обработки во время одного активного периода времени ядра. Поэтому конкретное ядро не выполняет частые переключения между неактивным и активным состояниями для каждого прерывания, предназначенного для обработки. Пакетная обработка прерываний может уменьшить колебания процессора и может снизить потребление энергии процессора, которая в противном случае была бы затрачена в связи с затратами энергии на переход в "активное состояние". Таким образом, благодаря пакетной обработке прерываний энергия, затрачиваемая на повторную активацию ядра, может быть уменьшена в связи с переходом от множества случаев перехода в активное состояние до одного случая перехода в активное состояние для множества обрабатываемых прерываний.

На фиг. 2 показана блок-схема контроллера 200 задержки прерывания в соответствии с вариантами осуществления настоящего изобретения. Контроллер 200 задержки прерывания включает в себя счетчики 2101 - 210L задержки по времени, регистры 2201 - 220L задержки по времени и логику 222 задержки прерывания, которая включает в себя логику 224 детектирования прерывания, логику 226 назначения счетчика и логику 228 высвобождения прерывания из состояния ожидания. Логика 222 задержки прерывания, включающая в себя логику 224 детектирования прерывания, логику 226 назначения счетчика и логику 228 высвобождения прерывания из состояния ожидания, может быть воплощена в виде программного обеспечения, аппаратных средств, встроенного программного обеспечения или их комбинации.

Во время работы множество периферийных устройств могут генерировать прерывания 2021 - 202J. Некоторые прерывания, принятые некоторыми периферийными устройствами, могут представлять собой жесткие прерывания, например, обрабатываемые без преднамеренной задержки. Другие прерывания могут представлять собой мягкие прерывания и могут быть задержаны перед обработкой.

Логика 224 детектирования прерывания может детектировать каждое принятое жесткое прерывание и может передавать каждое жесткое прерывание в контроллер 230 прерываний без задержки, для вывода в определенное ядро для обработки.

Каждый счетчик 2101-210L имеет ассоциированный регистр 2101 - 210L задержки по времени, который содержит определенную задержку по времени, соответствующую определенному периферийному устройству, которое вырабатывает мягкие прерывания. Задержка по времени для заданного периферийного устройства может быть сохранена в ассоциированном регистре 2101-210L задержки по времени (например, перед операцией контроллера 200 задержки прерывания) и может зависеть от множества факторов (например, влияние рабочих характеристик), как описано выше. Логика 226 назначения счетчика может назначать каждое прерывание, принятое из определенного периферийного устройства для соответствующего счетчика 210I, регистр 220I задержки по времени которого ассоциирован с определенным периферийным устройством. Например, когда принимают первое прерывание из первого периферийного устройства, первое прерывание может быть назначено логикой 226 назначения счетчика первому таймеру 2101, который начинает подсчет времени до первой величины задержки по времени, ассоциированной с первым периферийным устройством, и сохраненной в регистре 2201 (например, обратный отсчет от первой величины задержки по времени, или подсчет до первой величины задержки по времени. Когда подсчет времени истекает, прерывание высвобождают с передачей в контроллер 230 прерываний для обработки выбранным одним из ядер, определенных контроллером 230 прерываний.

Логика 224 детектирования прерывания может детектировать прием жесткого прерывания и может направлять принятое жесткое прерывание в контроллер 230 прерываний без преднамеренной задержки. Обработка жесткого прерывания может инициировать логику 228 высвобождения прерывания в состоянии ожидания выполнить высвобождение одного или больше мягких прерываний, которые находятся в состоянии ожидания, в контроллер 230 прерываний до окончания назначенной задержки времени, например, будучи преднамеренно задержанными через счетчик 210 задержки времени.

Кроме того, для каждого случая, когда счетчик 210 заканчивает свой подсчет ассоциированной задержки времени, соответствующее прерывание высвобождают в контроллер 230 прерываний для обработки определенным ядром процессора (конкретным ядром, определенным контроллером 230 прерываний). Высвобождение прерывания может привести к высвобождению логикой 228 высвобождения прерывания в состоянии ожидания одного или больше прерываний в состоянии ожидания с передачей в контроллер 230 прерываний для обработки определенным ядром.

Далее, на фиг. 3A, показана блок-схема ядра 300 процессора в соответствии с одним вариантом осуществления настоящего изобретения. Как показано на фиг. 3A, ядро 300 процессора может представлять собой многокаскадный процессор с магистральным конвейером обработки, работающим не по порядку.

Ядро 300 может включать в себя модуль 302 задержки прерывания в соответствии с вариантами осуществления настоящего изобретения. Прерывания могут быть приняты из различных периферийных устройств, и логика 304 детектирования прерывания может детектировать, является ли принятое прерывание жестким прерыванием или мягким прерыванием. Если принятое прерывание является жестким прерыванием, принятое прерывание передают в модули 310 предварительной обработки, и его обрабатывают исполнительными модулями 320 без задержки (например, без ввода преднамеренной задержки времени). Если принятое прерывание является мягким прерыванием, логика 304 детектирования прерывания может обозначать, чтобы логика 306 назначения счетчика назначила один из счетчиков 3071 - 307L задержки для принятого прерывания. Назначенный счетчик 307i задержки может подсчитывать заданную задержку Ti времени, где Ti содержится в соответствующем регистре 3091 - 309L задержки времени, и модуль 302 задержки прерывания может задерживать принятое мягкое прерывание до его обработки, пока соответствующий счетчик 307i задержки подсчитывает соответствующее время Ti задержки.

Если принятое (мягкое) прерывание находится в состоянии ожидания (например, задерживается модулем 302 задержки прерывания, до тех пор, пока не истечет соответствующий счетчик 307i задержки), когда обрабатывают другое прерывание (например, жесткое прерывание или другое мягкое прерывание, счетчик задержки которого истек), логика 308 высвобождения прерывания, находящегося в состоянии ожидания, может обеспечить высвобождение находящегося в состоянии ожидания мягкого прерывания для обработки до истечения его соответствующего счетчика 307i задержки в то время как исполнительные модули 320 являются активными в соответствии с вариантами осуществления настоящего изобретения.

Если прерывания не обрабатываются и отсутствуют инструкции, предназначенные для обработки, логика 318 регулирования питания может обозначать для исполнительных модулей 320, уменьшить потребление энергии от полностью активного уровня до более низкого уровня использования энергии. Когда прерывания и/или инструкции снова устанавливаются в очередь для обработки, логика 318 регулирования энергии может обозначать для исполнительных модулей 320 возобновить включенное рабочее состояние.

Как можно видеть на фиг. 3A, ядро 300 включает в себя модули 310 предварительной обработки, которые могут использоваться для выборки инструкций, предназначенных для выполнения, и подготовить их к последующему использованию в процессоре. Например, модули 310 предварительной обработки могут включать в себя модуль 301 выборки, кэш 303 инструкции и декодер 305 инструкции. В некоторых вариантах воплощения модули 310 предварительной обработки могут дополнительно включать в себя кэш трассы вместе с накопителем микрокода, а также накопитель микрооперации. Модуль 301 выборки может выполнять выборку макроинструкций, например, из памяти или кэш 303 инструкции и подавать их в декодер 305 инструкции для декодирования их в примитивы, то есть микрооперации для исполнения процессором.

Между модулями 310 предварительной обработки и исполнительными модулями 320 включен механизм 315 работы не по порядку (OOO), который может использоваться для приема микроинструкций и подготовки их для исполнения. Более конкретно, механизм 315 OOO может включать в себя различные буферы для изменения порядка микроинструкции и выделения различных ресурсов, необходимых для исполнения, а также для обеспечения переименования логических регистров на места расположения сохранения в пределах различных файлов регистров, таких как файл 330 регистра и расширенный файл 335 регистра. Файл 330 регистра может включать в себя отдельные файлы регистра для операций с целыми числами и с плавающей точкой. Расширенный файл 335 регистра может обеспечивать сохранение для модулей с размером вектора, например, 256 или 512 битов на регистр.

Различные ресурсы могут присутствовать в исполнительных модулях 320, включая в себя, например, различные логические модули, выполняющие операции с целыми числами с плавающей точкой, и множества данных с одной инструкцией (SIMD), помимо прочих специализированных аппаратных средств. Например, такие исполнительные модули могут включать в себя один или больше модулей 322 арифметической логики (ALU), помимо других таких исполнительных модулей.

Результаты исполнительных модулей могут быть поданы в логику вывода из работы, а именно в буфер 340 изменения порядка (ROB). Более конкретно, ROB 340 может включать в себя различные массивы и логику для приема информации, ассоциированной с исполняемыми инструкциями. Такая информация затем проверяется в ROB 340 для определения, могут ли эти инструкции быть действительно выведены из работы и полученные в результате данные переданы в архитектурное состояние процессора, или возникли ли одно или больше исключений, которые исключают соответствующий вывод из работы инструкций. Конечно, ROB 340 может обрабатывать другие операции, ассоциированные с выводом из работы.

Как показано на фиг. 3A, ROB 340 соединен в кэш 350, который в одном варианте осуществления может представлять собой кэш низкого уровня (например, кэш L1), хотя объем настоящего изобретения не ограничен в этом отношении. Кроме того, исполнительные модули 320 могут быть непосредственно соединены с кэш 350. Из кэш 350 может выполняться передача данных с кэш более высокого уровня, в системном запоминающем устройстве и т.д. Хотя в варианте осуществления, показанном на фиг. 3A, представлен этот высокий уровень, следует понимать, что объем настоящего изобретения не ограничен в этом отношении. Например, в то время как вариант воплощения на фиг. 3A относится к устройству, работающему не по порядку, такому, как так называемая архитектура набора инструкций (ISA) x86, объем настоящего изобретения не ограничен в этом отношении.

Таким образом, другие варианты осуществления могут быть воплощены в процессоре, работающем по порядку, в процессоре с сокращенным набором команд (RISC), таком как процессор на основе ARM, или в процессоре другого типа ISA, который может эмулировать инструкции и операции различных ISA через механизм эмуляции и ассоциированные логические схемы.

На фиг. 3B показана временная диаграмма прерываний, предназначенных для обработки, в соответствии с вариантами осуществления настоящего изобретения.

Сообщения (354-360) прерывания 1 представляют собой жесткие прерывания. Сообщения (362, 366, 370, 374) прерывания 2 представляют собой мягкие прерывания, которые являются периодическими. Сообщения (378, 382) прерывания 3 представляют собой мягкие прерывания, которые являются апериодическими.

Все прерывания будут обработаны одним и тем же ядром. Мягкие прерывания могут быть задержаны, при этом каждое мягкое прерывание имеет соответствующую задержку по времени, как описано выше со ссылкой на фиг. 2. Каждое из периодических мягких прерываний 362, 366, 370 и 374 задерживают по времени для обработки как задержанные прерывания 364, 368, 372 и 376 соответственно. Каждое из асинхронных мягких прерываний 378, 382 задерживают по времени для обработки как прерывания 380 и 384 соответственно.

Каждое из жестких прерываний 354-360 должно быть обработано без преднамеренной задержки, и каждое прерывание 354-360 ассоциировано с переходом из неактивного в активное состояние (386, 390, 394, 396) в ядре, которое обрабатывает прерывания. Прерывания 354, 356, 358 и 360 обрабатываются как моменты 386, 390, 394, и 396 времени ядра соответственно.

По мере того как обрабатывается каждое прерывание 354, 356, 358, 360, одно или больше прерываний в состоянии ожидания (например, еще не обработанных и ожидающих истечения соответствующего периода задержки времени) могут быть высвобождены для обработки, в то время как ядро находится в активном состоянии. Например, прерывание 370 задерживают для обработки до 372 (здесь обозначено 370 → 372), и оно находится в режиме ожидания, когда обрабатывают прерывание 358. Следовательно, прерывание (370 → 372) будет высвобождено для обработки в момент времени 394, высвобождение инициируется обработкой прерывания 358. Таким образом, два прерывания (358 и 370 → 372) должны быть обработаны в один и тот же активный период ядра, который начинается в 394.

Прерывание 374 задерживают до 376, и оно находится в состоянии ожидания, когда должно быть обработано прерывание 360, например в момент времени 396. Следовательно, прерывание (374 → 376) будет высвобождено для обработки в течение периода активности ядра, который начинается в 396. Кроме того, прерывание 382 задерживают до 384, и оно находится в режиме ожидания, когда начинается обработка прерывания 360. Поэтому прерывание (382 → 384) будет высвобождено для обработки во время периода активности ядра, которая начинается в 396. Таким образом, три прерывания 360, (374 → 376) и (382 → 384) должны быть обработаны во время постоянно активного периода ядра, который начинается в 396.

Прерывание 366 задерживают для обработки в 368. Никакое другое прерывание не планируют для обработки в период времени между 366 и 368, и, таким образом, задержанное прерывание (366-> 368) должно быть обработано в момент времени 392, и обработка приводит к переходу ядра из неактивного состояния в активное во время 392. Ядро должно возвратиться в неактивное состояние после обработки задержанного прерывания (366 → 368).

Прерывание 362 задерживают до 364 (362 → 364). Асинхронное мягкое прерывание 378 задерживают до 380 (378 → 380). Задержанное прерывание (362 → 364) не находится в состоянии ожидания, в то время как любое другое прерывание должно быть обработано, и поэтому будет обработано во время 388, соответствующее 364, которое представляет собой в конце его задержки по времени. Задержанное прерывание (378 → 380) находится в состоянии ожидания во время 388 и поэтому будет высвобождено для обработки, в то время как ядро находится в активном состоянии в результате обработки задержанного прерывания (362 → 364). Таким образом, два прерывания 364 и (378 → 380) обрабатывают в один активный период, который начинается в 388.

В общей сложности 6 переходов (386 - 396) из неактивного в активное состояние ядра получается в результате обработки 10 принятых прерываний. Следовательно, введение задержки по времени перед обработкой мягких прерываний может уменьшить общее количество переходов из неактивного в активное состояние ядра. Уменьшение количества переходов из неактивного в активное состояние ядра может уменьшить общее потребление энергии, из-за уменьшения затрат на энергию, ассоциированных с переходами из неактивного в активное состояние ядра.

На фиг. 4 показана блок-схема 400 последовательности операций способа обработки событий прерывания процессором в соответствии с вариантом осуществления настоящего изобретения. В блоке 410 процессор принимает прерывание из периферийного устройства. Обработка продолжается до ромба 420 принятия решения, если первое прерывание представляет собой жесткое прерывание, например ассоциировано с жестким событием в режиме реального времени, для которого время задержки TN=0, с переходом в блок 450 прерывание обрабатывается процессором без преднамеренной задержки по времени. Далее выполняется переход в ромб 460 принятия решения, если имеются другие прерывания в режиме ожидании, возвращаясь в блок 450, обрабатываются прерывания, находящиеся в состоянии ожидания. Если в ромбе 460 принятия решения отсутствуют другие прерывания в состоянии ожидания, способ заканчивается в 470.

Если в ромбе 420 принятия решения N-е прерывание не является жестким прерыванием, например N-е прерывание не ассоциировано с жестким событием в режиме реального времени, выполняется переход в блок 430, соответствующий таймер задержки начинает подсчет соответствующей задержки TN для N-го прерывания. Далее выполняется переход в ромб 440 принятия решения, когда таймер задержки истекает, с последующим переходом в блок 450, выполняется обработка N-го прерывания. Выполняется переход в ромб 460 принятия решения, если присутствуют другие прерывания, находящиеся в состоянии ожидания, когда обрабатывают N-е прерывание, возвращаясь в блок 450, выполняется обработка прерывания, находящегося в состоянии ожидания, например, перед истечением их соответствующих значений времени задержки в результате обработки N-го прерывания. Если в ромбе 460 принятия решения отсутствуют другие прерывания, находящиеся в состоянии ожидания, способ заканчивается в 470.

Варианты осуществления могут быть воплощены во множестве разных типов систем. На фиг. 5 показана блок-схема системы в соответствии с вариантом осуществления настоящего изобретения. Как показано на фиг. 5, мультипроцессорная система 500 представляет собой систему, взаимно соединенную из точки в точку, и включает в себя первый процессор 570 и второй процессор 580, соединенные через взаимное соединение 550 из точки в точку. Как показано на фиг. 5, каждый из процессоров 570 и 580 может представлять собой многоядерные процессоры, включающие в себя первое и второе ядра процессора (то есть ядра 574a и 574b, и ядра 584a, и 584b), хотя потенциально гораздо большее количество ядер могут присутствовать в процессорах. Процессор 570 включает в себя контроллер 502 задержки прерывания и контроллер 504 прерывания, и процессор 580 включает в себя контроллер 506 задержки прерывания и контроллер 508 прерывания в соответствии с вариантами осуществления настоящего изобретения. Каждый контроллер 502, 506 задержки прерывания должен детектировать входящие прерывания. Если входящее прерывание ассоциировано с жестким событием в режиме реального времени, прерывание должно быть передано в соответствующий контроллер 504, 508 прерывания для обработки без преднамеренной задержки.

Для первого прерывания, которое представляет собой мягкое прерывание, контроллер 502, 506 задержки прерывания должен задерживать обработку прерывания на определенное время задержки перед передачей первого прерывания в соответствующий контроллер 504, 508 прерывания, который направляет первое прерывание в ядро для обработки, в случае когда первое прерывание находится в состоянии ожидания, в то время как обрабатывают второе прерывание. Если первое прерывание находится в состоянии ожидания, в то время как второе прерывание обрабатывают, контроллер 502, 506 задержки прерывания должен передать первое прерывание в соответствующий контроллер 504, 508 прерывания для его направления в ядро для обработки, в то время как ядро находится в активном состоянии, обработка которого инициируется вторым прерыванием в соответствии с вариантами осуществления настоящего изобретения.

Также, как показано на фиг. 5, первый процессор 570 дополнительно включает в себя концентратор 572 контроллера памяти (MCH) и интерфейсы 576 и 578 из "точки в точку" (P-P). Аналогично второй процессор 580 включает в себя MCH 582 и интерфейсы 586 и 588 P-P. Как показано на фиг. 5, MCH 572 и 582 соединяют процессоры с соответствующими запоминающими устройствами, а именно, запоминающим устройством 532 и запоминающим устройством 534, которые могут представлять собой части системного запоминающего устройства (например, DRAM) локально установленного в соответствующих процессорах. Первый процессор 570 и второй процессор 580 могут быть соединены с набором 590 микросхем через взаимное соединение 562 и 584 P-P соответственно. Как показано на фиг. 5, набор 590 микросхем включает в себя интерфейсы 594 и 598 P-P.

Кроме того, набор 590 микросхем включает в себя интерфейс 592 для соединения набора 590 микросхем с высокопроизводительным графическим механизмом 538 через взаимное соединение 539 P-P. В свою очередь, набор 590 микросхем может быть соединен с первой шиной 516 через интерфейс 596. Как показано на фиг. 5, различные устройства 514 ввода/вывода (I/O) могут быть соединены c первой шиной 516, вместе с мостом 518 шины, который соединяет первую шину 516 со второй шиной 520. Различные устройства могут быть соединены со второй шиной 520, включая в себя, например, клавиатуру/мышь 522, устройства 526 передачи данных и модуль 528 сохранения данных, такой как привод диска или другое устройство массового сохранения, которое может включать в себя код 530, в одном варианте осуществления. Кроме того, модуль 524 ввода /вывода (I/O) аудиоданных может быть соединен со второй шиной 520. Одно или больше из устройств 514, 522, 524, 526 могут предоставлять прерывания для обработки процессором 570 или процессором 580 в соответствии с вариантами осуществления настоящего изобретения. Варианты осуществления могут быть включены в другие типы систем, включая в себя мобильные устройства, такие как сотовые телефоны-смартфоны, персональный компьютер, нетбук, Ultrabook™ и так далее.

Варианты осуществления могут быть встроены в другие типы систем, включающие в себя мобильные устройства, такие как сотовый телефон. На фиг. 6 показана блок-схема системы в соответствии с другим вариантом осуществления настоящего изобретения. Как показано на фиг. 6, система 600 может представлять собой мобильное устройство и может включать в себя различные компоненты. Как показано в виде высокого уровня на фиг. 6, процессор 610 приложений, который может представлять собой центральное процессорное устройство в этом устройстве, сообщается с различными компонентами, включая в себя накопитель 615. Накопитель 615 в различных вариантах осуществления может включать в себя как программы, так и части сохраняемых данных.

Процессор 610 приложений может дополнительно быть соединен с системой 620 ввода-вывода, которая в разных вариантах осуществления может включать в себя дисплей и одно или больше устройств ввода, таких как сенсорная клавишная панель, которая сама может появляться на дисплее при обработке. Система 600 может также включать в себя интегрированный сенсорный концентратор (ISH) 660, который может принимать данные из одного или больше датчиков 670. В некоторых вариантах осуществления интегрированный сенсорный концентратор включает в себя контроллер 662 задержки прерывания (IDC) для детектирования мягких прерываний и выполнения задержки мягкого прерывания на соответствующее время (TN) задержки. Если другое прерывание должно быть обработано, в то время как прерывание находится в состоянии ожидания, прерывание обрабатывают для завершения его задержки по времени в соответствии с вариантами осуществления настоящего изобретения.

Процессор 610 приложений может включать в себя контроллер 602 задержки прерывания (IDC) в соответствии с вариантами осуществления настоящего изобретения. IDC 602 может детектировать входящее жесткое прерывание (например, из приемопередатчика 640 и/или процессора 630 в основной полосе пропускания) в ассоциации с жестким событием в режиме реального времени и может без преднамеренной задержки передавать жесткое прерывание в контроллер прерывания (не показан), который передает прерывание в ядро процессора 610 приложений для обработки (например, оперирования).

Для первого прерывания, которое представляет собой мягкое прерывание (например, принятое из I/O 620 и/или интегрированного сенсорного концентратора 660), контроллер 602 задержки прерывания может выполнять задержку обработки первого прерывания на первое время задержки перед высвобождением первого прерывания в контроллер прерывания в случае, когда первое прерывание находится в состоянии ожидания, когда второе прерывание обрабатывается в первом ядре. Контроллер прерывания должен передавать первое прерывание в первое ядро процессора 610 приложений для обработки. Если первое прерывание находится в состоянии ожидания, когда второе прерывание обрабатывают в первом ядре, обработка второго прерывания инициирует контроллер 602 задержки прерывания передать первое прерывание в контроллер прерывания без завершения задержки по времени для направления в первое ядро для обработки, в то время как ядро находится в активном состоянии, то есть инициируют обработку первого прерывания в соответствии с вариантами осуществления настоящего изобретения.

Второе прерывание может представлять собой жесткое прерывание или мягкое прерывание, время задержки которого завершено (например, счетчик задержки времени истек).

Процессор 610 приложений также может соединяться с процессором 630 в основной полосе пропускания, который может обрабатывать сигналы, такие как голосовые сигналы, и передаваемые данные для вывода, а также для обработки входящих телефонных и других сигналов. Процессор 630 в основной полосе пропускания может включать в себя IDC 632, который принимает прерывания из периферийных устройств 634 и который может задерживать исполнение принятого мягкого прерывания в случае, когда мягкое прерывание находится в состоянии ожидания, в то время как другое прерывание обрабатывают, в соответствии с вариантами осуществления настоящего изобретения. Как можно видеть, процессор 630 в основной полосе пропускания соединяется с приемопередатчиком 640, который может обеспечивать возможности, как приема, так и передачи. В свою очередь, приемопередатчик 640 может быть сообщаться с антенной 650, например антенной любого типа, позволяющей передавать и принимать голосовые сигналы и сигналы данных через один или больше протоколов передачи данных, например, через беспроводную глобальную вычислительную сеть (такую как сеть 3G или 4G) и/или беспроводную локальную вычислительную сеть, такую как BLUETOOTH™ или так называемую сеть WI-FI™, в соответствии со стандартом Института инженеров по электронике и радиотехнике 802.11.

Как можно видеть, система 600 может дополнительно включать в себя перезаряжаемый источник 625 питания, имеющий перезаряжаемую батарею, которая обеспечивает операции в мобильной среде. Хотя вариант осуществления на фиг. 6 показан в этом конкретном воплощении, объем настоящего изобретения не ограничен в этом отношении.

На фиг. 7 показана блок-схема системы на кристалле (SOC) в соответствии с вариантами осуществления настоящего изобретения. SOC 700 включает в себя многоядерную подсистему 710, подсистему 720 модема, мультимедийную подсистему 730, системную структуру 740, источник 750 питания и интерфейсы 760 для формирования интерфейса с одним или больше внешними устройствами. SOC 700 может выполнять множество задач одновременно, например задачи модема, мультимедийные задачи и другие задачи обработки.

Многоядерная подсистема 710 включает в себя многоядерные процессоры 712 и 714, кэш 716 и 718 L1, и кэш 742 L2. Каждый из многоядерных процессоров 712 и 714 может включать в себя соответствующий контроллер 702, 704 задержки прерывания (IDC).

Каждый контроллер 702, 704 задержки прерывания должен детектировать входящие жесткие прерывания, ассоциированные с жесткими событиями в режиме реального времени (например, из интерфейсов 760), и после приема должен передавать каждое жесткое прерывание в соответствующий контроллер прерывания (не показан), который направляет прерывание в ядро соответствующего процессора 712, 714, для обработки.

Для первого прерывания, которое представляет собой мягкое прерывание (например, принятое из интерфейсов 760), контроллер 702, 704 задержки прерывания должен выполнять задержку на первое время задержки, передавая первое прерывание в соответствующий контроллер прерывания, который должен направлять прерывание в ядро для обработки в случае, когда первое прерывание находится в состоянии ожидания, второе прерывание обрабатывается ядром. Если первое прерывание находится в состоянии ожидания, в то время как второе прерывание обрабатывается ядром, контроллер 702, 704 задержки прерывания должен передавать первое прерывание в контроллер прерывания без завершения задержки по времени для направления в ядро для обработки, в то время как ядро находится в активном состоянии, которое инициируется при обработке второго прерывания в соответствии с вариантами осуществления настоящего изобретения.

Подсистема 720 модема может включать в себя модем 722, соответствующий стандарту долгосрочного развития (LTE), для беспроводной передачи данных с высокой скоростью передачи данных. Подсистема 720 модема также может включать в себя систему 724 глобальной навигации (GPS) и по меньшей мере два ядра 726 и 728 цифрового сигнального процессора (DSP). Модем 722 LTE может включать в себя IDC 721 для детектирования прерываний, вводимых из подсистемы 720 модема (например, из GPS 724) и для задержки мягких прерываний в соответствии с вариантами осуществления настоящего изобретения.

Мультимедийная подсистема 730 может включать в себя графический процессор 732 (GPU), аудио/видеоаппаратные ускорители 734, ядро 736 обработки цифровых сигналов и процессор 738 MMX, который может быть выполнен с возможностью обработки, например, с одним потоком команд и множеством потоков данных (SIMD).

Другие варианты осуществления описаны ниже.

В первом примере процессор включает в себя по меньшей мере одно ядро, включая в себя первое ядро. Процессор также включает в себя логику задержки прерывания для приема первого прерывания в первое время, задержки на первое время задержки, которое начинается в первое время, обработки первого прерывания первым ядром до случая, когда первое прерывание находится в состоянии ожидания, во второе время, когда начинается обработка второго прерывания первым ядром, и если первое прерывание находится в состоянии ожидания во второе время, обозначения для первого ядра начинать обработку первого прерывания перед завершением первого времени задержки.

Во втором примере, который включает в себя процессор по примеру 1, логика задержки прерывания должна принимать множество прерываний, которые находятся в состоянии ожидания во второе время, включающее в себя первое прерывание, и первое ядро должно обрабатывать множество находящихся в состоянии ожидания прерываний в течение первого активного периода, который начинается во второе время, где первое ядро остается в активном состоянии в течение первого активного периода.

В третьем примере, который включает в себя процессор по примеру 2, первое ядро должно переходить из активного состояния в неактивное состояние после обработки второго прерывания и множества прерываний в состоянии ожидания.

В четвертом примере, который включает в себя процессор по примеру 1, первое ядро должно оставаться в активном состоянии, в то время как обрабатываются первое прерывание и второе прерывание, и переходить в неактивное состояние после обработки первого прерывания и второго прерывания.

В пятом примере, который включает в себя процессор по примеру 1, второе прерывание принимают периодически, и для каждого появления второго принятого прерывания второе прерывание должно быть обработано первым ядром без преднамеренной задержки и логика задержки прерывания должна обозначать для первого ядра начать обработку дополнительных прерываний в состоянии ожидания до завершения соответствующей задержки и пока ядро остается в активном состоянии.

В шестом примере, который включает в себя процессор по примеру 5, для каждого возникновения приема второго прерывания, после завершения обработки второго прерывания и дополнительных прерываний в состоянии ожидания, первое ядро должно переходить в неактивное состояние.

В седьмом примере, который включает в себя процессор по примеру 1, логика задержки прерывания должна дополнительно принимать третье прерывание в третье время и назначать для третьего прерывания второе время задержки и логика задержки прерывания должна задерживать обработку третьего прерывания от третьего времени на второе время задержки случае, когда третье прерывание находится в состоянии ожидания, в то время как обрабатывают первое прерывание или второе прерывание, и если третье прерывание находится в состоянии ожидания, в то время как обрабатывают первое прерывание или второе прерывание, обозначать для первого ядра обрабатывать третье прерывание без завершения второго времени задержки.

В восьмом примере, который включает в себя процессор по примеру 7, если третье прерывание не находится в состоянии ожидания, в то время как должны быть обработаны первое прерывание или второе прерывание, логика задержки прерывания должна обозначать для ядра обрабатывать третье прерывание после завершения второго времени задержки.

В девятом примере, который включает в себя процессор по примеру 1, логика задержки прерывания включает в себя счетчик для подсчета первого времени задержки.

В десятом примере система включает в себя динамическое оперативное запоминающее устройство (DRAM) и процессор, который включает в себя одно или больше ядер, и контроллер прерывания для направления каждого из одного или больше принятых прерываний в первое ядро из одного или больше ядер. Процессор также включает в себя контроллер задержки прерывания, который включает в себя один или больше счетчиков задержки для подсчета соответствующего времени задержки, для обработки соответствующего прерывания, в котором каждый счетчик задержки начинает соответствующий подсчет после приема процессором соответствующего некритического прерывания, и логику высвобождения прерывания в состоянии ожидания для того, чтобы в ответ на выполнение другого прерывания передавать каждое прерывание в состоянии ожидания в контроллер прерывания для направления в первое ядро, в то время как первое ядро находится в активном состоянии.

В 11-м примере, который включает в себя систему по примеру 10, если никакое другое прерывание не обрабатывают в течение соответствующего времени задержки, ассоциированного со вторым прерыванием, контроллер задержки прерывания должен передавать прерывание в контроллер прерывания после завершения подсчета соответствующего счетчика задержки.

В 12-м примере, который включает в себя систему по примеру 10, в которой, когда подсчет второго счетчика задержки завершается, логика высвобождения прерывания в состоянии ожидания должна передавать каждое прерывание в состоянии ожидания в контроллер прерывания для обработки, в то время как первое ядро находится в активном состоянии.

В 13-м примере, который включает в себя систему по примеру 10, после обработки прерываний в состоянии ожидания соответствующее ядро должно стать неактивным.

В 14-м примере, который включает в себя систему по примеру 10, процессор дополнительно включает в себя логику детектирования критического прерывания, предназначенную для, после приема жесткого прерывания, передачи жесткого прерывания в контроллер прерывания без преднамеренной задержки.

В 15-м примере, который включает в себя систему по примеру 10, процессор дополнительно включает в себя логику назначения счетчика для назначения соответствующего счетчика задержки для каждого принятого некритичного прерывания.

В 16-м примере способ включает в себя обработку первого прерывания ядром процессора, начинающуюся в первое время, назначение процессором задержки времени для второго прерывания, принятого во второе время, обработку второго прерывания ядром после истечения задержки времени, которое начинается во второе время в то время как второе прерывание находится в состоянии ожидания в первое время и, если второе прерывание находится в состоянии ожидания в первое время, обработку второго прерывания ядром перед истечением задержки времени.

В 17-м примере, который включает в себя способ по примеру 16, если второе прерывание находится в состоянии ожидания в первое время, обрабатывают второе прерывание, в то время как ядро находится в активном состоянии, в ответ на обработку первого прерывания.

В 18-м примере, который включает в себя способ по примеру 16, после обработки первого прерывания и второго прерывания ядро переходит в неактивное состояние.

В 19-м примере, который включает в себя способ по примеру 16, если множество прерываний находится в состоянии ожидания в первое время, передают множество прерываний, перед завершением соответствующей задержки времени каждого из множества прерываний, в ядро для обработки ядром, где ядро поддерживается в активном состоянии в то время, как обрабатывается множество прерываний.

В 20-м примере, который включает в себя способ по примеру 19, после обработки всех прерываний в состоянии ожидания, выполняет переход ядра в неактивное состояние.

В 21-м примере, который включает в себя способ по примеру 16, задержку времени определяют на основе одной или больше характеристик периферийного устройства, из которого принимают второе прерывание.

В 22-м примере, который включает в себя способ по примеру 16, назначают соответствующую задержку времени для каждого из множества прерываний, обработка каждого из которых должна быть задержана на соответствующую задержку времени, которая начинается от соответствующего времени приема, в то время как обрабатывается другое прерывание.

В 23-м примере, который включает в себя способ по примеру 22, когда начинается обработка определенного прерывания, передают каждое прерывание в состояние ожидания в ядро для обработки без завершения соответствующей задержки времени.

В 24-м примере устройство включает в себя средство для выполнения способа по любому из примеров 16-23.

В 25-м примере по меньшей мере один считываемый компьютером носитель информации включает в себя инструкции, которые при их исполнении обеспечивают выполнение системой способа по любому из примеров 16-23.

Варианты осуществления могут использоваться во множестве разных типов систем. Например, в одном варианте осуществления устройство передачи данных может быть выполнено с возможностью выполнения различных описанных здесь способов и технологий. Конечно, объем настоящего изобретения не ограничен устройством передачи данных, и вместо этого другие варианты осуществления могут быть направлены на другие типы устройства для обработки инструкций или один или больше считываемых устройством носителей информации, включающих в себя инструкции, которые в ответ на обработку в вычислительном устройстве обеспечивают выполнение устройством описанных здесь одного или больше способов и технологий.

Варианты осуществления могут быть воплощены в коде и могут быть сохранены на непереходном носителе сохранения, на котором содержатся инструкции, которые могут использоваться для программирования системы для выполнения этих инструкций. Носитель сохранения может включать в себя, но не ограничен этим, любой тип диска, включающий в себя гибкие диски, оптические диски, твердотельные приводы (SSD), постоянное запоминающее устройство на компактных дисках (CD-ROM), компактные диски с возможностью перезаписи (CD-RW) и магнитооптические диски, полупроводниковые устройства, такие как постоянные запоминающие устройства (ROM), оперативные запоминающие устройства (RAM), такие как динамические оперативные запоминающие устройства (DRAM), статические оперативные запоминающие устройства (SRAM), стираемые программируемые постоянные запоминающие устройства (EPROM), память флэш, электрически стираемые программируемые постоянные запоминающие устройства (EEPROM), магнитные или оптические карты или любой другой тип носителей, пригодных для сохранения электронных инструкций.

В то время как настоящее изобретение было описано в отношении ограниченного количества вариантов осуществления, для специалистов в данной области техники будут понятны различные модификации и варианты на их основе. Предполагается, что приложенная формула изобретения охватывает все такие модификации и варианты как попадающие в пределы истинной сущности и объема данного настоящего изобретения.

Группа изобретений относится к области вычислительной техники и может быть использована для обработки прерываний. Техническим результатом является уменьшение потребления энергии процессором. Процессор содержит, по меньшей мере, одно ядро, включая в себя первое ядро; и логику задержки прерывания, предназначенную для: приема первого прерывания в первое время; задержки на первое время задержки, которое начинается в первое время, обработки первого прерывания первым ядром, в то время как первое прерывание находится в состоянии ожидания, во второе время, когда начинается обработка второго прерывания первым ядром; и если первое прерывание находится в состоянии ожидания во второе время, обозначения для первого ядра, начинать обработку первого прерывания перед завершением первого времени задержки, в котором второе прерывание принимают периодически, и для каждого появления второго принятого прерывания второе прерывание должно быть обработано первым ядром без преднамеренной задержки, и логика задержки прерывания должна обозначать для первого ядра начать обработку дополнительных прерываний в состоянии ожидания до завершения соответствующей задержки и пока ядро остается в активном состоянии. 3 н. и 16 з.п. ф-лы, 8 ил.

1. Процессор, содержащий:

по меньшей мере, одно ядро, включая в себя первое ядро; и логику задержки прерывания, предназначенную для:

приема первого прерывания в первое время;

задержки на первое время задержки, которое начинается в первое время, обработки первого прерывания первым ядром, в то время как первое прерывание находится в состоянии ожидания, во второе время, когда начинается обработка второго прерывания первым ядром; и

если первое прерывание находится в состоянии ожидания во второе время, обозначения для первого ядра начинать обработку первого прерывания перед завершением первого времени задержки,

в котором второе прерывание принимают периодически, и для каждого появления второго принятого прерывания второе прерывание должно быть обработано первым ядром без преднамеренной задержки, и логика задержки прерывания должна обозначать для первого ядра начать обработку дополнительных прерываний в состоянии ожидания до завершения соответствующей задержки и пока ядро остается в активном состоянии.

2. Процессор по п. 1, в котором, когда множество принятых прерываний находится в состоянии ожидания во второе время, первое ядро должно обрабатывать множество прерываний в состоянии ожидания в течение первого активного периода, который начинается во второе время, в котором первое ядро остается в активном состоянии в течение первого активного периода.

3. Процессор по п. 2, в котором первое ядро должно переходить из активного состояния в неактивное состояние после обработки второго прерывания и множества прерываний в состоянии ожидания.

4. Процессор по п. 1, в котором первое ядро должно оставаться в активном состоянии, в то время как обрабатываются первое прерывание и второе прерывание, и переходить в неактивное состояние после обработки первого прерывания и второго прерывания.

5. Процессор по п. 1, дополнительно содержащий: для каждого возникновения приема второго прерывания, после завершения обработки второго прерывания и дополнительных прерываний в состоянии ожидания, первое ядро должно переходить в неактивное состояние.

6. Процессор по п. 1, в котором логическая схема задержки прерывания дополнительно предназначена для приема третьего прерывания в третье время и назначать для третьего прерывания второе время задержки и в котором логика задержки прерывания предназначена для:

задержки обработки третьего прерывания от третьего времени на второе время задержки, в то время как третье прерывание находится в состоянии ожидания, пока обрабатывают первое прерывание или второе прерывание; и

если третье прерывание находится в состоянии ожидания, пока обрабатывают первое прерывание или второе прерывание, обозначать для первого ядра обрабатывать третье прерывание без завершения второго времени задержки.

7. Процессор по п. 6, в котором, если третье прерывание не находится в состоянии ожидания, в то время как должны быть обработаны первое прерывание или второе прерывание, логика задержки прерывания должна обозначать для ядра обрабатывать третье прерывание после завершения второго времени задержки.

8. Процессор по п. 1, в котором логическая схема задержки прерывания включает в себя счетчик для подсчета первого времени задержки.

9. Система для обработки прерываний, содержащая:

динамическое оперативное запоминающее устройство (DRAM) и процессор, который включает в себя одно или больше ядер;

контроллер прерывания для направления каждого из одного или больше принятых прерываний в первое ядро из одного или больше ядер;

контроллер задержки прерывания, включающий в себя:

один или больше счетчиков задержки для подсчета соответствующего времени задержки для обработки соответствующего прерывания, в котором каждый счетчик задержки начинает соответствующий подсчет после приема процессором соответствующего прерывания; и

логику высвобождения прерывания в состоянии ожидания для того, чтобы в ответ на выполнение первого обрабатываемого прерывания передавать каждое прерывание в состоянии ожидания в контроллер прерывания до истечения соответствующей задержки времени,

в которой периодически принимают второе прерывание, и для каждого появления второго принятого прерывания второе прерывание должно быть обработано первым ядром без преднамеренной задержки, и логика задержки прерывания должна обозначать для первого ядра начать обработку дополнительных прерываний в состоянии ожидания до завершения соответствующей задержки и пока ядро остается в активном состоянии.

10. Система по п. 9, в которой, если никакое другое прерывание не обрабатывают в течение соответствующего времени задержки, ассоциированного со вторым прерыванием, контроллер задержки прерывания должен передавать прерывание в контроллер прерывания после завершения подсчета соответствующего счетчика задержки.

11. Система по п. 9, в которой, когда подсчет второго счетчика задержки завершается, логика высвобождения прерывания в состоянии ожидания должна передавать каждое прерывание в состоянии ожидания в контроллер прерывания для обработки, в то время как первое ядро находится в активном состоянии.

12. Система по п. 9, в которой после обработки прерываний в состоянии ожидания соответствующее ядро должно стать неактивным.

13. Система по п. 9, в которой процессор дополнительно включает в себя логику детектирования критического прерывания, предназначенную для, после приема жесткого прерывания, передачи жесткого прерывания в контроллер прерывания без преднамеренной задержки.

14. Система по п. 9, в которой процессор дополнительно включает в себя логику назначения счетчика для назначения соответствующего счетчика задержки для каждого принятого некритичного прерывания.

15. Способ обработки прерываний, содержащий:

обработку первого прерывания ядром процессора, начинающуюся в первое время, назначение процессором задержки времени для второго прерывания, принятого во второе время,

обработку второго прерывания ядром после истечения задержки времени, которое начинается во второе время, в то время как второе прерывание находится в состоянии ожидания в первое время; и

если второе прерывание находится в состоянии ожидания в первое время, обработку второго прерывания ядром перед истечением задержки времени,

в котором второе прерывание принимают периодически, и для каждого появления второго принятого прерывания второе прерывание должно быть обработано первым ядром без преднамеренной задержки, и логика задержки прерывания должна обозначать для первого ядра начать обработку дополнительных прерываний в состоянии ожидания до завершения соответствующей задержки и пока ядро остается в активном состоянии.

16. Способ по п. 15, в котором, если второе прерывание находится в состоянии ожидания в первое время, обрабатывают второе прерывание, в то время как ядро находится в активном состоянии, в ответ на обработку первого прерывания.

17. Способ по п. 15, дополнительно содержащий: после обработки первого прерывания и второго прерывания ядро переходит в неактивное состояние.

18. Способ по п. 15, дополнительно содержащий: если множество прерываний находится в состоянии ожидания в первое время, передают множество прерываний, перед завершением соответствующей задержки времени каждого из множества прерываний, в ядро для обработки ядром, где ядро поддерживается в активном состоянии, в то время как обрабатывается множество прерываний.

19. Способ по п. 18, дополнительно содержащий: после обработки всех прерываний в состоянии ожидания выполняет переход ядра в неактивное состояние.

| Приспособление для суммирования отрезков прямых линий | 1923 |

|

SU2010A1 |

| US 6115779 A, 05.09.2000 | |||

| US 6629252 B1, 30.09.2003 | |||

| ПЕРЕМЕННЫЙ ТАЙМЕР ПРЕРЫВАНИЯ | 2009 |

|

RU2471296C2 |

Авторы

Даты

2018-04-18—Публикация

2014-03-24—Подача