Изобретение относится к вычислительной технике и может быть использовано в блоках контроля запоминающих устройств.

Известно устройство обнаружения и коррекции ошибок, содержащее регистр входных данных, регистр контрольных данных, регистр реж-има диагностики, регистр входных данных, буфер входных контрольных данных, генератор признаков ошибки, формирователь данных, устройство управления, дешифратор признаков ошибки.

Недостатком данного устройства является большое количество выходов (48), в том числе восемь выходов управляющих команд, определяемых внешним устройством управления, что приводит к усложнению устройства.

Из известных устройств наиболее близким техническим решением к данному изобретению является устройство обнаружения и исправления ошибок содержащее, входные регистры и шинные формирователи, формирователи контрольных разрядов и синдрома ошибок, блок обнаружения одиночной и многократной ошибки, дешифратор адреса ошибки, корректирующий блок и блок управления.

Недостатком этого устройства является отсутствие возможности контроля устройств в режиме диагностики, что приводит к усложнению запоминающих устройств в которых применено данное устройство и снижает надежность данных запоминающих устройств.

Целью изобретения является расширение области применения устройства за счет введения возможности контроля устройства в режиме диагностики.

ч|

00

со ел

00

СА)

Поставленная цель достигается тем, что в устройство обнаружения и коррекции ошибок, содержащее первый и второй регистры, формирователь контрольных разрядов и синдрома ошибки, дешифратор адреса ошибки, блок коррекции, блок обнаружения одиночной и многократной ошибок, блок сравнения и шинные формирователи информационных и контрольных разрядов, причем информационные входы первого регистра являются информационными входами - выходами устройства, контрольными входами - выходами которого являются информационные входы второго регистра, выходы которого соединены с входами первой группы формирователя контрольных разрядов и синдрома ошибки, входы второй группы которого и входы первой группы блока коррекции объединены и соединены с выходами первого регистра, управляющий вход которого соединен с первым выходом блока управления, второй выход которого подключен к входу формирователя контрольных разрядов и синдрома ошибки, соответствующие входы дешифратора адреса ошибки, информационные входы шинных формирователей контрольных разрядов и входы блока обнаружения одиночной и многократной ошибок объединены и подключены к выходам формирователя контрольных разрядов и синдрома ошибки, выходы дешифратора адреса ошибки соединены с соответствующими входами второй группы блока коррекции, выходы которого соединены с соответствующими информационными входами шинных формирователей информационных разрядов, управляющий вход которых соединен с третьим выходом блока управления, четвертый выход которого соединен с управляющим входом шинных формирователей контрольных разрядов, выходы которых являются контрольными входами- выходами устройств, информационными входами - выходами которых являются выходы шинных формирователей информационных разрядов, первый и второй входы задания режима блока управления являются соответственно первым и вторым управляющими входами устройства и введены элементами и, ИЛИ, НЕ, триггер с установочными входами, двоичный счетчик и шинные формирйватели флагов ошибки, причем управляющие входы шинных формирователей соединены с выходом элемента НЕ вход которого соединен с первым выходом устройства управления, информационные входы первого и второго шинного формирователя соединены соответственно с первым и вторым выходом блока обнаружения одиночной и многократной ошибок,

а выходы шинных формирователей флагов ошибки соединены с выходами устройства флагов ошибки EF и МЕР и с первыми входами соответственно первого и второго элемента ИЛИ, вторые входы которых соединены с выходом элемента НЕ, выход первого элемента ИЛИ соединен с установочным входом триггера, вход сброса которого соединен с выходом второго элемента

0 ИЛИ и с входом сброса счетчика, счетный вход которого соединен с выходом первого элемента И первый вход которого соединен с выходом триггера, а второй вход соединен с первым выходом устройства управления и

5 с первым входом второго элемента И, второй вход которого соединен с инверсным выходом счетчика, а выход второго элемента И соединен со стробирующим входом регистра контрольных разрядов.

0 Рассмотрение показало, что предложенное техническое решение в сравнении с прототипом обладает новыми отличительными признаками, что доказывает соответствие заявляемого решения критерию

5 новизна.

Введение новых элементов И, ИЛИ, НЕ, триггера с установочными входами, двоичного счетчика, шинных формирователей в указанной связи с другими элементами схе0 мы позволяет получить новое свойство осуществления возможности контроля устройства в режиме диагностики, что доказывает соответствие технического решения критерию существенное отличие.

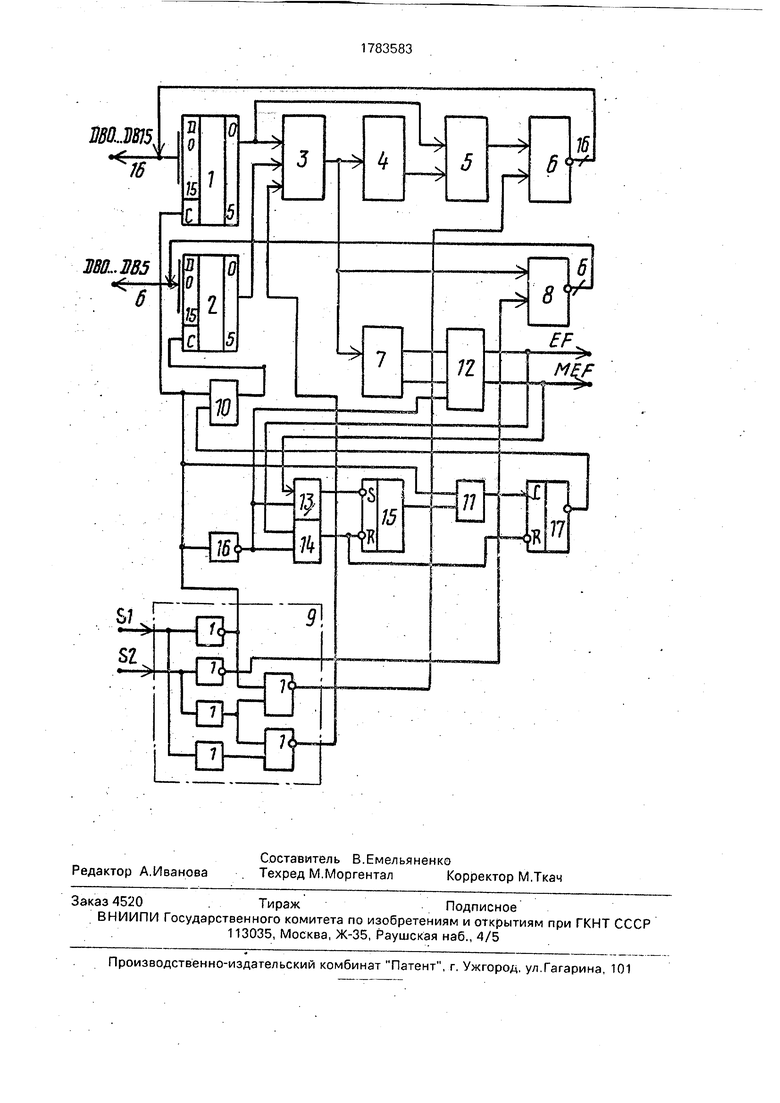

5 На чертеже представлена функциональная схема предлагаемого устройства.

Устройство содержит: входной информационный регистр 1, регистр контрольных разрядов 2, формирователь контрольных

0 разрядов и синдрома ошибок 3, дешифратор адреса ошибок 4, блок коррекции 5, шинные формирователи информационных разрядов 6,блок обнаружения одиночных и многократных ошибок 7, шинные формиро5 ватели контрольных разрядов 8, устройство управления 9, первый и второй элементы И 10 и 11, шинные формирователи флагов ошибки 12, элементы ИЛИ 13 и 14, триггер с установочными входами 15, элемент НЕ

0 16, двоичный счетчик 17, информационные входы/выходы DBO...DB15. входы/выходы контрольной информации СВО...СВ5. входы/выходы флагов ошибки EF и МЕР, управляющие входы SO и S1.

5 Входной информационный регистр 1 и регистр контрольных разрядов 2 предназначены для приема информации поступающей по входам/выходам DBO...DB15 и СВО...СВ5 с внешних запоминающих устройств.

Формирователь контрольных разрядов и синдрома ошибок 3 осуществляет в цикле записи формирование контрольных разрядов, поступающих через шинные формирователи на входы/выходы СВО...СВ5 из информационных, в соответствии с кодом Хэмминга. Каждый контрольный разряд представляет собой результат суммирования по модулю два восьми информационных разрядов. В цикле считывание формируется синдром ошибки в результате сравнения входной информации свернутой по коду Хэмминга и контрольных разрядов.

Дешифратор адреса ошибки 4 осуществляет дешифрации синдрома ошибки, фор- мирует сигнал указывающий ошибочный разряди выдает сигнал блоку коррекции на его исправление.

Блок коррекции 5 осуществляет коррекцию (инвертирование) ошибочных разрядов информации занесенной на входной информационный регистр 1 и выдачу откорректированной информации на входные шинные формирователи.

Входные шинные формирователи 6 осу- ществляют коммутацию информации с выхода блока корректора на входы/выходы DBO...DC15 в соответствии с табл. 1 по сигналу с выхода устройства управления.

Блок обнаружения одиночной и много- кратной ошибок 7 формирует сигналы однократной ошибки EF и многократной ошибки МЕР по результатам анализа синдрома ошибки. Входные шинные формирователи 8 осуществляют коммутацию информации с выхода формирователя контрольных разрядов и синдрома ошибок на входы/выходы контрольной информации СВО...СВ5. Устройство управления 9 осуществляет управление работой устройства обнаружения и коррекции ошибок (УОКО) по входным сигналам 0 и 1 в соответствии с табл. 2.

Элементы И 10 и 11,,двоичный счетчик 17 предназначены для блокировки через обращение записи информации в регистр кон- трольных разрядов 2. Элементы ИЛИ 13 и 14, триггер 15.позволяют переключить УОКО в диагностический режим. Элемент НЕ 16 и шинные формирователи 12-осуще- ствляют коммутацию сигналов по вхо- дам/выходам ЕР и МЕР.

Устройство работает следующим образом.

По начальной установке процессор устанавливает S1 в нулевое состояние и фор- мирует нулевой сигнал на входе ЕР, который через элемент 2 ИЛИ 14 производит сброс триггера 15 и сче тчика 17. Инверсный выход счетчика 17 разрешает через элемент И 10 прохождение сигнала с выхода устройства

управления 9 на стробирующий вход регистра контрольных разрядов 2 одновременно с сигналов поступающих на стробирующий вход информационного регистра 1. После окончания информационной установки процессор снимает нулевой сигнал на входе ЕР и дальнейшая работа устройства осуществляется аналогично работе прототипа. Устройство работает в двух основных режимах, соответствующих циклам записи и считывания с ЗУ. В цикле записи происходит процесс кодирования, т.е. формирование контрольных разрядов из информационных в соответствии с кодом Хэмминга. Каждый контрольный разряд представляет сббой результат суммирования по модулю 2 восьми информационных разрядов.

Сформированные контрольные разряды выдаются на двунаправленную шину и поступают вместе с информационными разрядами в ЗУ. На этом цикл записи заканчивается.

В течение цикла считывания информационные и контрольные разряды с ЗУ заносятся на регистры 1 и 2 (S1 О, SO - 1) и формирователь контрольных разрядов и синдрома ошибок сформирует из содержимого информационного регистра 1 контрольные разряды и сравнит их с контрольными разрядами занесенными в регистр контрольных разрядов 2. Если достигнуто равенство всех шести разрядов, то это означает, что нет ошибок и при SO и S1 равным единице, на входах ЕР и МЕР не появляются сигналы ошибок.

При несовпадении одного или более разрядов в контрольных битах формирователь контрольных разрядов и синдрома ошибок 3 формирует сигнал ошибки который поступает на дешифратор адреса ошибок 4 и блок обнаружения одиночных и многократных ошибок 7. По синдрому ошибок дешифратор адреса ошибок 4 определяет ошибочный разряд информации и выдает сигнал блоку коррекции 5 на исправление (инвертирование) информации поступающей с выхода регистра 1. С выхода блока коррекции 5 информация поступает на вход шинных формирователей 6, который по управляющему сигналу (при SO О, S I 1) с выхода устройства управления выдает од- корректированную информацию на входы/выходы DBO...DB15. Кроме того блок обнаружения одиночных ошибок и многократных ошибок 7 формирует сигналы однократной и многократной ошибки, которые поступают на шинные формирователи 12 и по управляющему сигналу (при S1 1) с выхода устройства управления 9 выдается на входы/выходы ЕР и МЕР.

Отличием от прототипа является возможность установки диагностического режима, который позволяет провести контроль УОКО. Установка в данный режим осуществляется подачей одновременно с управляющим сигналом низкого логического уровня по входу/выходу МЕР, который через элемент ИЛИ 13 устанавливает в единичное состояние триггер 15, задающий диагностический режим УОКО и разрешаю- щий поступление выходного сигнала с устройства управления через элемент И 11 на счетный вход счетчика 17, который изменяет состояние по окончанию сигнала, с выхода устройства управления 9 стробирующего запись информации в регистры 1 и 2. Нулевой сигнал с инверсного выхода счетчика 17 поступает на второй вход элемента И 10 и блокирует прохождение сигнала с выхода устройства управления 9 нашстробирующий вход регистра контрольных разрядов 2. Таким образом после установки в диагностический режим УОКО, при 2п-1 (п 1,2,3...) считывании информации с внешнего ЗУ, в регистр контрольных разрядов 2 записыва- ется информация одновременно с занесением информации во входной информационный регистр 1, при 2п считывании информации с внешнего ЗУ записывается только во входной информационный регистр 1, информа- ция в регистре контрольных разрядов 2 не изменяется и на вход формирователя контрольных разрядов и синдрома ошибок 3 поступает информационное слово с регистра

1записанное при 2п обращении и контроль- ное слово с регистра 2 записанное при(2п-1) обращении. Контроль УОКО будет осуществляться считыванием с внешнего ЗУ информации, отличающейся при 2п-1 и 2п (при равных п) обращения соответственно в пер- вом цикле на 1 разряд, во втором цикле - на

2разряда. При каждом 2п считывании в первом цикле в регистр контрольных разрядов 2 будет занесено контрольное слово предыдущего 2п-1 считывания информации отличной от информации занесенной при 2п считывании во входной информационный регистр 1 на один разряд, поэтому формирователь контрольных разрядов и синдрома ошибок формирует синдромом ошибки, ко- торый поступает на дешифратор адреса ошибки 4 и блок обнаружения ошибок 7, формирующий сигнал однократная ошибка EF. Дешифратор адреса ошибки 4 опознает разряд информационного слова в 2л обращение, который отличается от 2п-1 обращения и выдает сигнал корректирующему блоку на его исправление,. При правильной работе УОКО в первом цикле информации на входах/выходах DBO...DB15 (SO 0.51 1)

при 2 считывании будет равна информации при 2-1 считывании и на входе/выходе EF будет выдаваться сигнал однократная ошибка. При втором цикле проверки в каждом 2 считывании на входе МЕР будет выдаваться сигнал многократная ошибка.

После окончания .проверки процессор устанавливает S1 в нулевое состояние и формирует нулевой сигнал на входе/выход ЕР и переводит УОКО в исходное состояние.

Описанное устройство позволяет проводить контроль устройства обнаружения и коррекции ошибок, используя аппаратные средства расположенные непосредственно в устройствах, что расширяет область применения устройства.

Устройство для обнаружения и коррекции ошибок выполняется в виде интегральной микросхемы выполненной по технологии 533 серии и размещенной в корпусе аналогичному корпусу микросхемы 533 ВЖ1.

Формула изобретения

Устройство для обнаружения и коррекции ошибок, содержащее первый и второй регистры, формирователь контрольных разрядов и синдрома ошибки, дешифратор адреса ошибки, блок коррекции, блок обнаружения одиночной и многократной ошибок, блок управления и шинные формирователи информационных и контрольных разрядов, причем информационные входы первого регистра являются информационными входами-выходами устройства, контрольными входами-выходами которого являются информационные входы второго регистра, выходы которого соединены с входами первой группы формирователя контрольных разрядов и синдрома ошибки, входы второй группы которого и входы первой группы блока коррекции объединены и соединены с выходами первого регистра., управляющий вход которого соединен с первым выходом блока управления, второй выход которого подключен к входу формирователя контрольных разрядов и синдрома ошибки, соответствующие входы дешифратора адреса ошибки, информационные входы шинных формирователей контрольных разрядов и входы блока обнаружения одиночной и многократной ошибок объединены и подключены к выходам формирователя контрольных разрядов и синдрома ошибки, выходы дешифратора адреса ошибки соединены с соответствующими входами второй группы блока коррекции, выходы которого соединены с соответствующими информационными входами шинных формирователей информационных разрядов, управляющий вход которых соединен с

третьим выходом блока управления, четвертый выход которого соединен с управляющим входом шинных формирователей контрольных разрядов, выходы которых являются контрольными входами-выходами устройства, информационные входы-выходы которого соединены с выходами шинных формирователей информационных разрядов, первый и второй входы задания режима блока управления являются соответственно первым и вторым управляющими входами устройства, отличающееся тем, что, с целью расширения области применения устройства за счет обеспечения контроля в режиме диагностики, в него введены первый и второй элементы И, первый и второй элементы ИЛИ, элемент НЕ, триггер, двоичный счетчик и шинные формирователи флагов ошибки, причем вход элемента НЕ, второй вход первого элемента И и первый вход второго элемента И объединены и подключены к первому выходу блока управления, управляющие входы шинных

0

5

0

5

формирователей флагов ошибки, вторые входы первого и второго элементов ИЛИ объединены и подключены к выходу элемента НЕ, первый и второй выходы блока обнаружения одиночной и многократной ошибок соединены соответственно с первым и вторым входами шинных формирователей флагов ошибки, первый и второй выходы которых соединены соответственно с первыми входами второго и первого элементов ИЛИ и являются входами-выходами флагов ошибки устройства, выходы первого элемента ИЛИ соединены с установочным входом триггера, входы сброса триггера и двоичного счетчика объединены и подключены к выходу второго элемента ИЛИ, выход триггера соединен с первым входом первого элемента И, выход которого соединен со счетным входом двоичного счетчика, инверсный выход которого соединен с вторым входом второго элемента И, выход которого подключен к управляющему входу второго регистра.

Таблица 1

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропрограммное устройство для управления каналами ЭВМ | 1982 |

|

SU1068938A1 |

| Резервированное оперативное запоминающее устройство | 1982 |

|

SU1137538A1 |

| Запоминающее устройство с самоконтролем | 1983 |

|

SU1167659A1 |

| Процессор ввода-вывода с коррек-циЕй ОшибОК | 1979 |

|

SU849221A1 |

| Запоминающее устройство на цилиндрических магнитных доменах | 1990 |

|

SU1737511A1 |

| Запоминающее устройство с автономным контролем | 1990 |

|

SU1785040A1 |

| Запоминающее устройство на цилиндрических магнитных доменах | 1990 |

|

SU1737510A1 |

| Запоминающее устройство с контролем цепей коррекции ошибок | 1988 |

|

SU1751818A1 |

| Запоминающее устройство на цилиндрических магнитных доменах | 1985 |

|

SU1273999A1 |

| Запоминающее устройство с коррекцией информации | 1982 |

|

SU1070610A1 |

Изобретение относится к вычислительной технике, в частности к запоминающим устройствам. Цель изобретения - расширение области применения устройства за счет обеспечения контроля в режиме диагностики. Для достижения цели в устройство обнаружения и коррекции ошибок, содержащее первый и второй регистры, формирователь контрольных разрядов и синдрома ошибки, блок обнаружения одиночной и многократной ошибок, дешифратор адреса ошибки, блок коррекции, блок управления и шинные формирователи информационных и контрольных разрядов, вводятся элемент НЕ, триггер, первый и второй элементы И, первый и второй элементы ИЛИ, двоичный счет- чик и шинные формирователи флагов ошибок. Ввод данных элементов позволяет при считывании внешней информации и занесении ее во входные регистры осуществить контроль цепей коррекции ошибок изменением алгоритма занесения информации в регистр контрольных разрядов. 1 ил. (Л С

-Таблица 2

| Безфитильная бензиновая горелка для наборных машин "Линотип" | 1922 |

|

SU1804A1 |

| 0.347.328-06 ТУ | |||

| Домовый номерной фонарь, служащий одновременно для указания названия улицы и номера дома и для освещения прилежащего участка улицы | 1917 |

|

SU93A1 |

| ГИДРАВЛИЧЕСКИЙ ТАРАН | 1921 |

|

SU533A1 |

| 0.347.141 ТУ 41 | |||

| ГИДРАВЛИЧЕСКИЙ ТАРАН | 1921 |

|

SU533A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Способ закалки пил | 1915 |

|

SU140A1 |

Авторы

Даты

1992-12-23—Публикация

1990-07-02—Подача