Текст описания в факсимильном виде (см. чертежи) Та

| название | год | авторы | номер документа |

|---|---|---|---|

| МАКРОПРОЦЕССОР | 2001 |

|

RU2210808C2 |

| УСТРОЙСТВО УМНОЖЕНИЯ | 1998 |

|

RU2148270C1 |

| МАТРИЧНЫЙ КОММУТАТОР | 1994 |

|

RU2103729C1 |

| Устройство для формирования карты местности перед транспортным средством | 1989 |

|

SU1689971A1 |

| УСТРОЙСТВО ДЛЯ МОДЕЛИРОВАНИЯ НЕЙРОНА | 1991 |

|

RU2029368C1 |

| Устройство для распаковки команд | 1990 |

|

SU1702367A1 |

| УСТРОЙСТВО МИКРОПРОГРАММНОГО УПРАВЛЕНИЯ | 1991 |

|

RU2020559C1 |

| Микропрограммное устройство управления | 1989 |

|

SU1636845A1 |

| Коммутационное устройство | 1989 |

|

SU1645963A1 |

| Коммутационное устройство | 1989 |

|

SU1672464A1 |

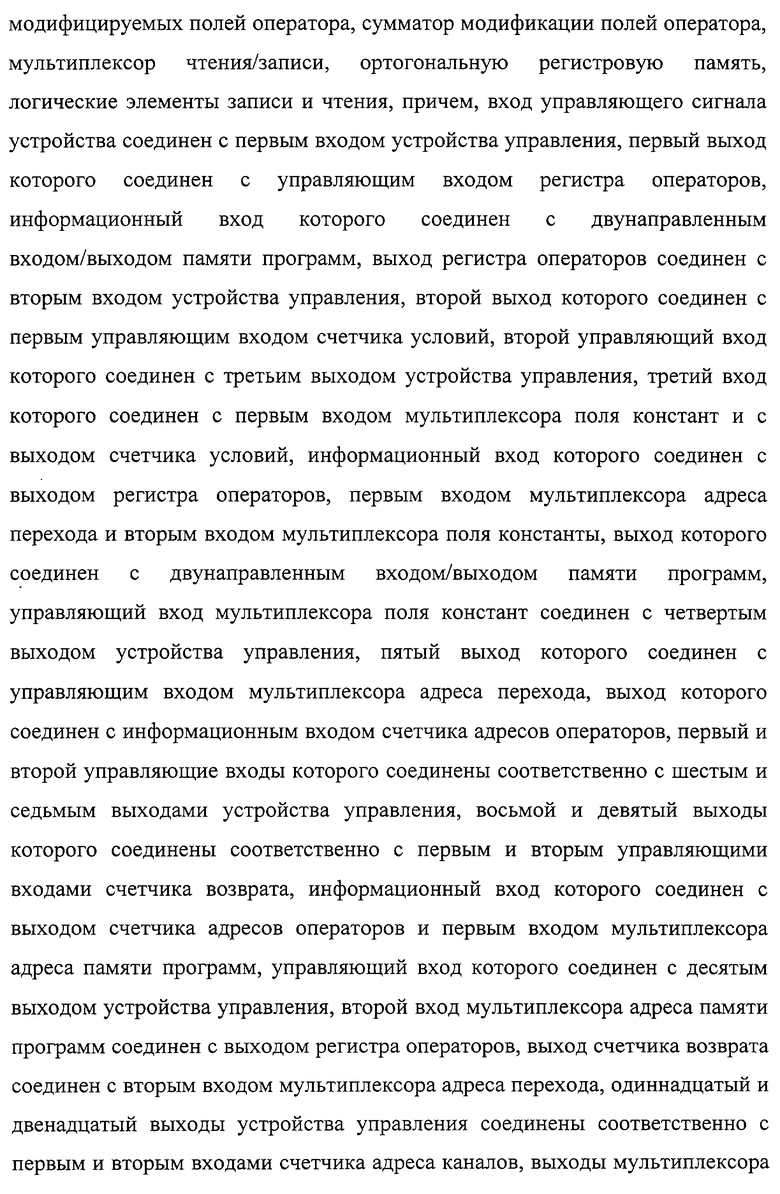

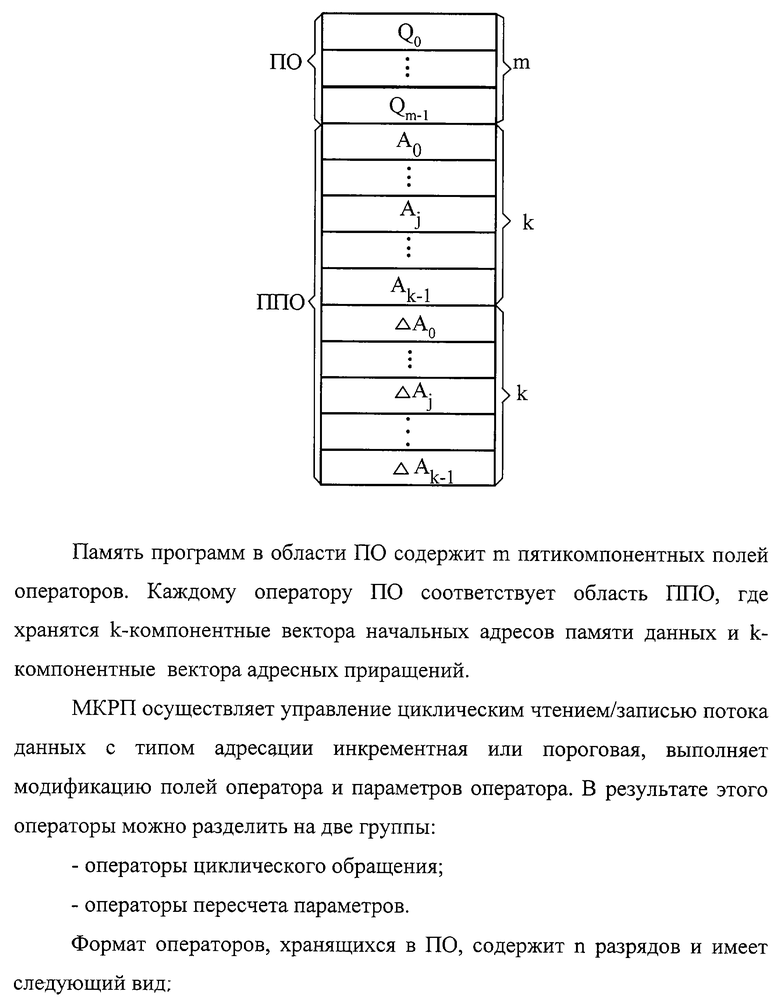

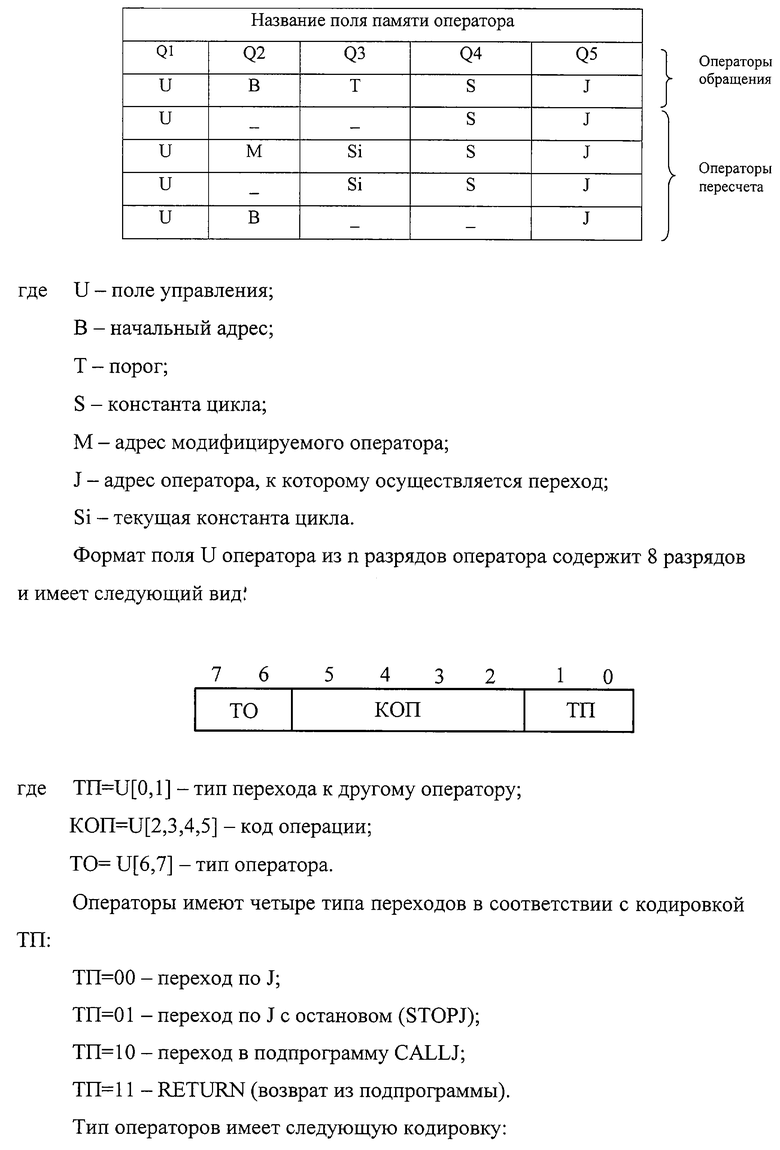

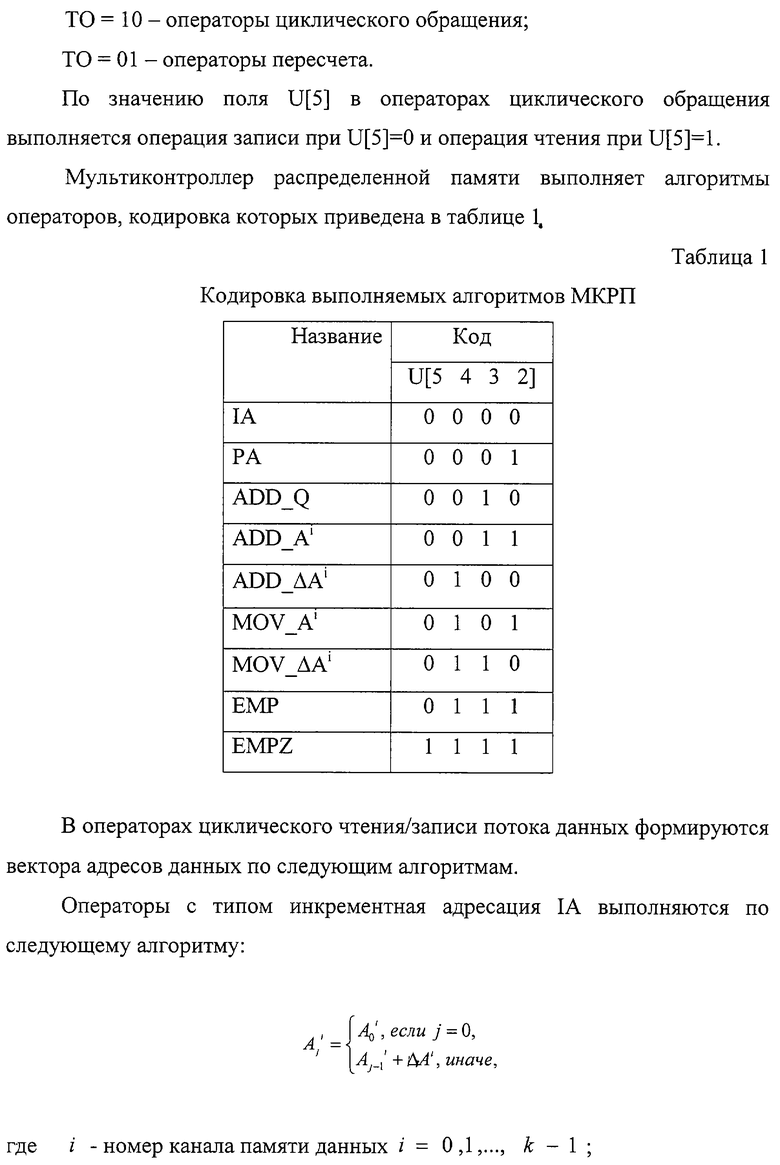

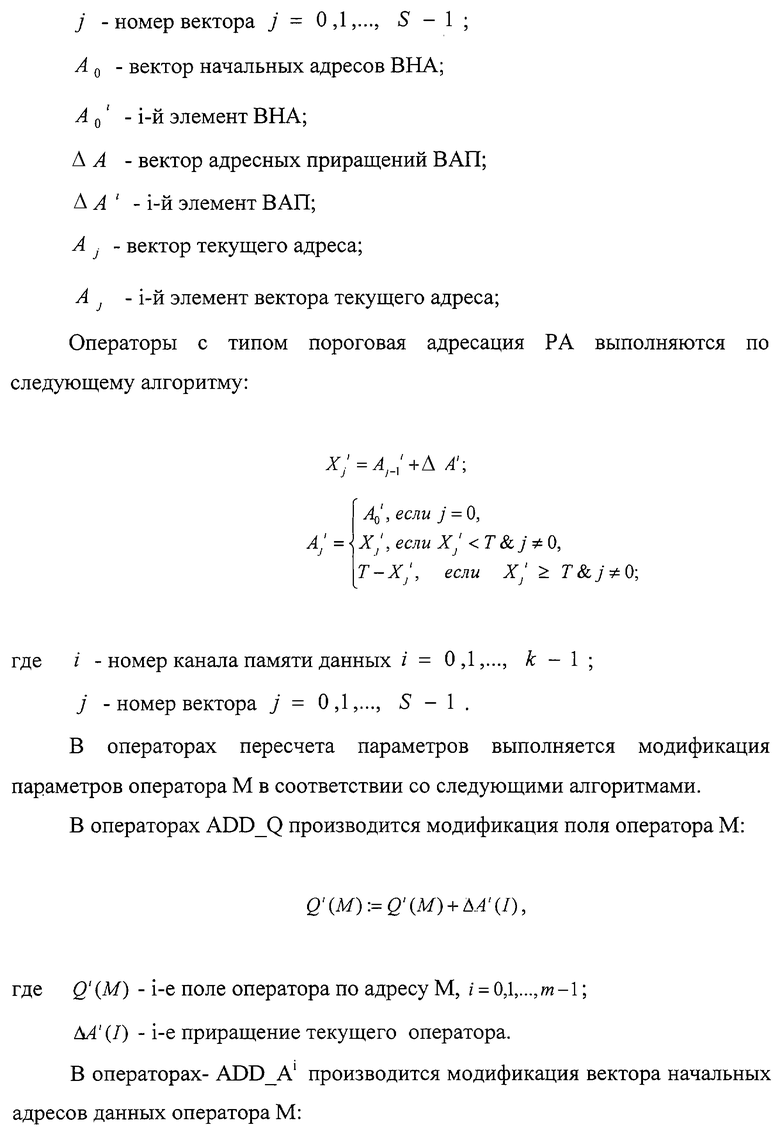

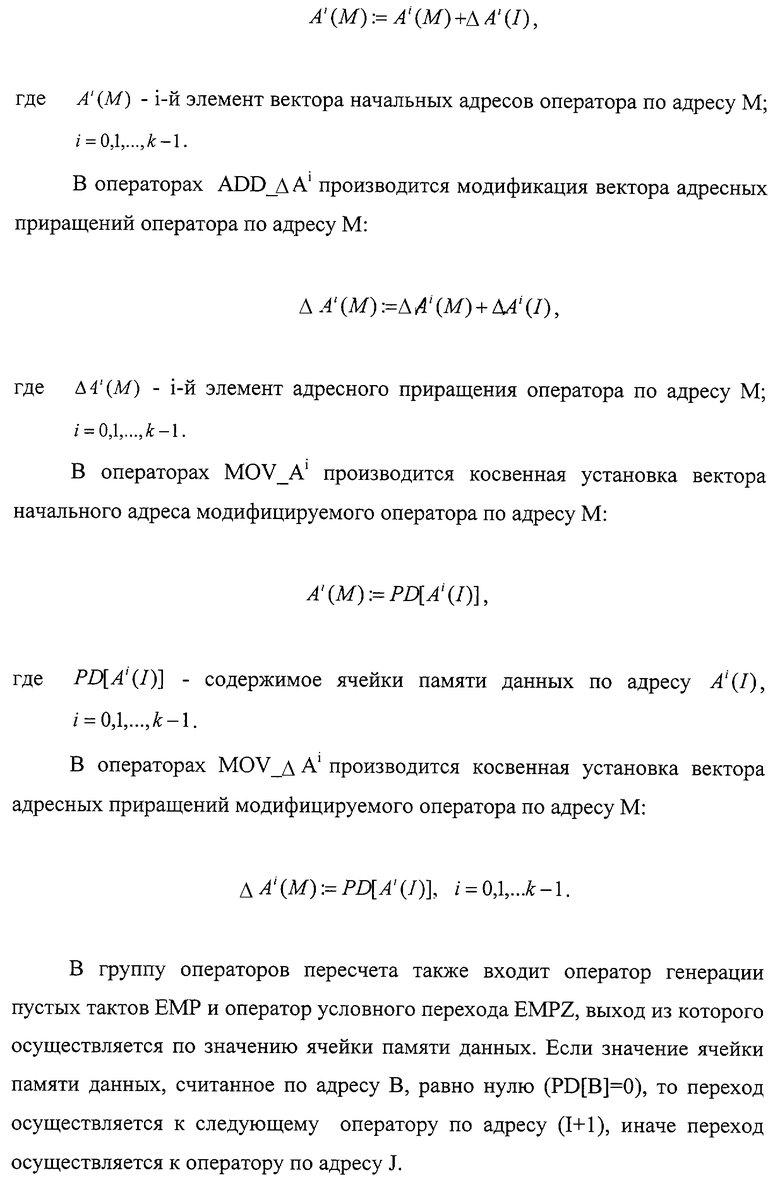

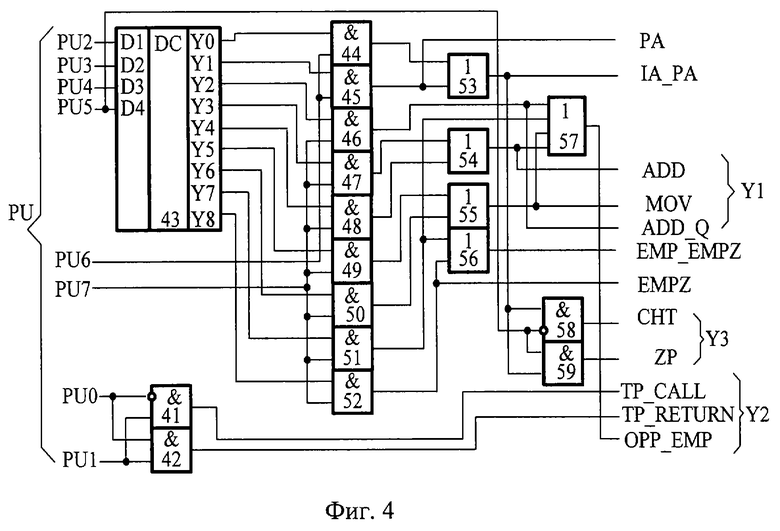

Изобретение относится к области вычислительной техники и может найти применение в конвейерных потоковых машинах и многопроцессорных вычислительных системах. Технический результат - расширение функциональных возможностей за счет более сложной процедуры изменения адресов каналов, возможность для модификации начальных адресов доступа и адресных приращений, а также средств для организации вложенных циклов, что позволяет организовывать сложные процедуры обращения к памяти. Для достижения указанного технического результата в устройство вводится ряд логических устройств, что позволяет реализовать автономно практически любую процедуру доступа к памяти без привлечения дополнительных устройств или ресурсов процессора. 10 ил., 1 табл.

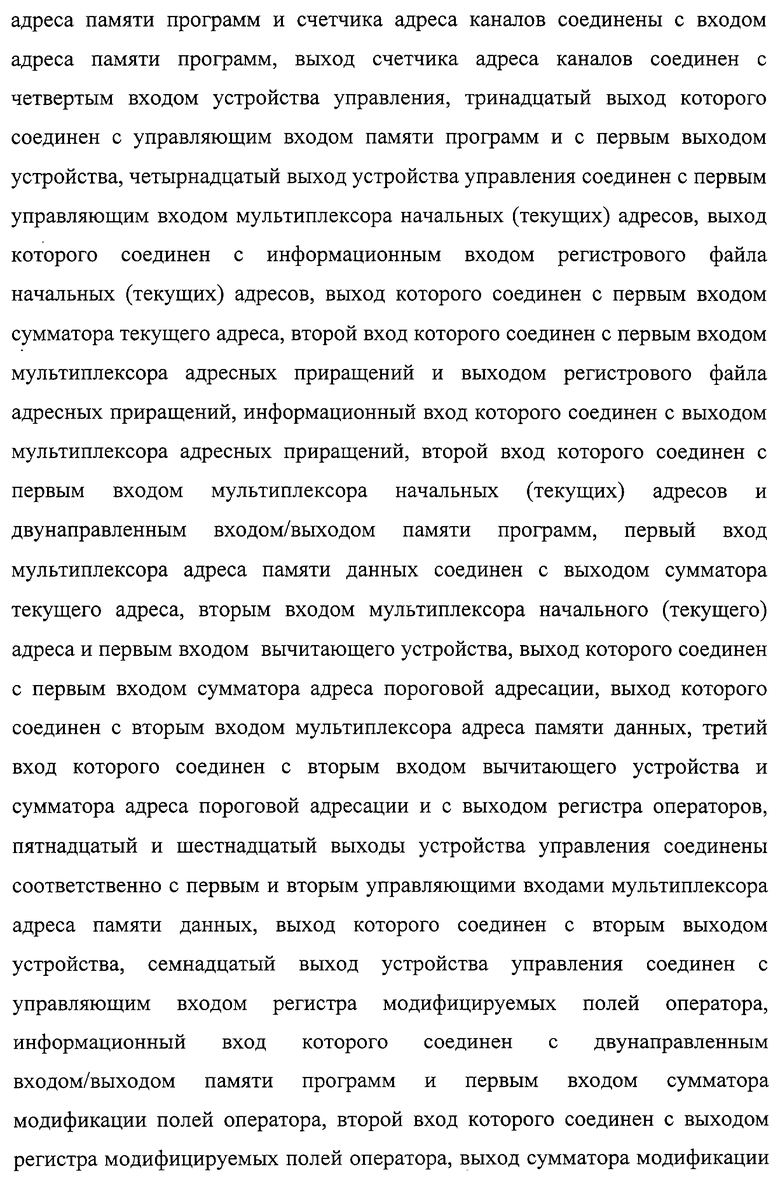

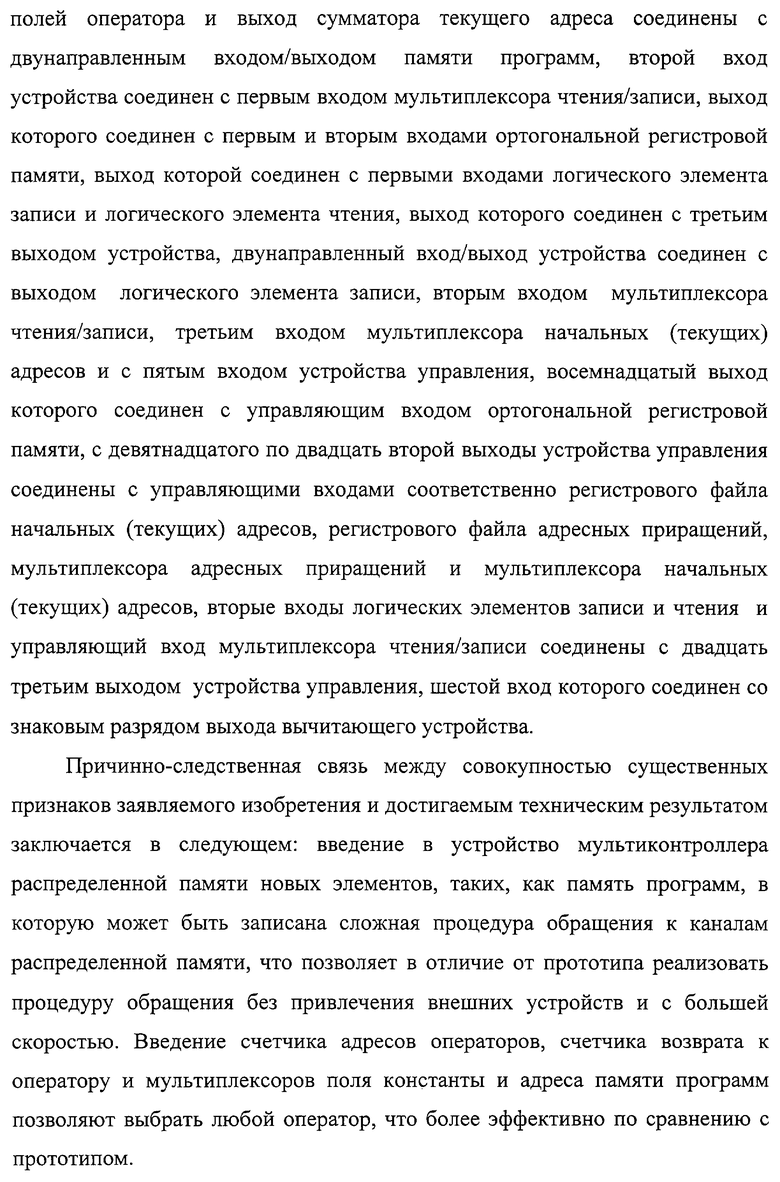

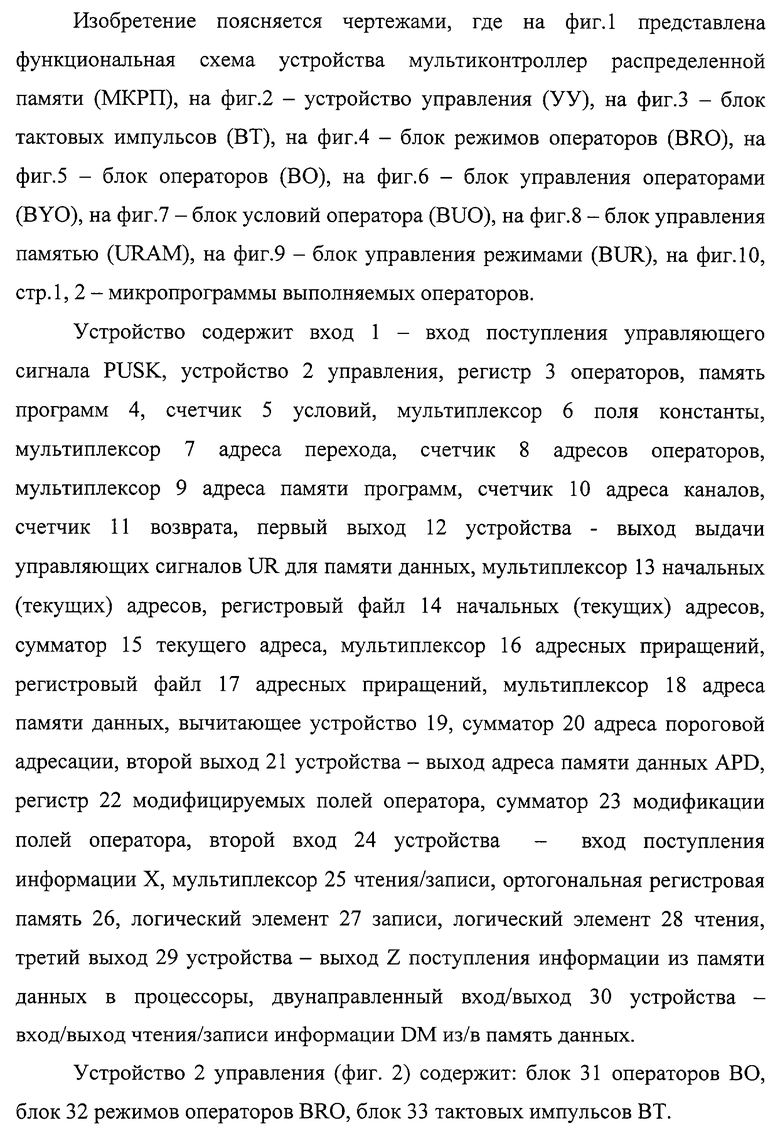

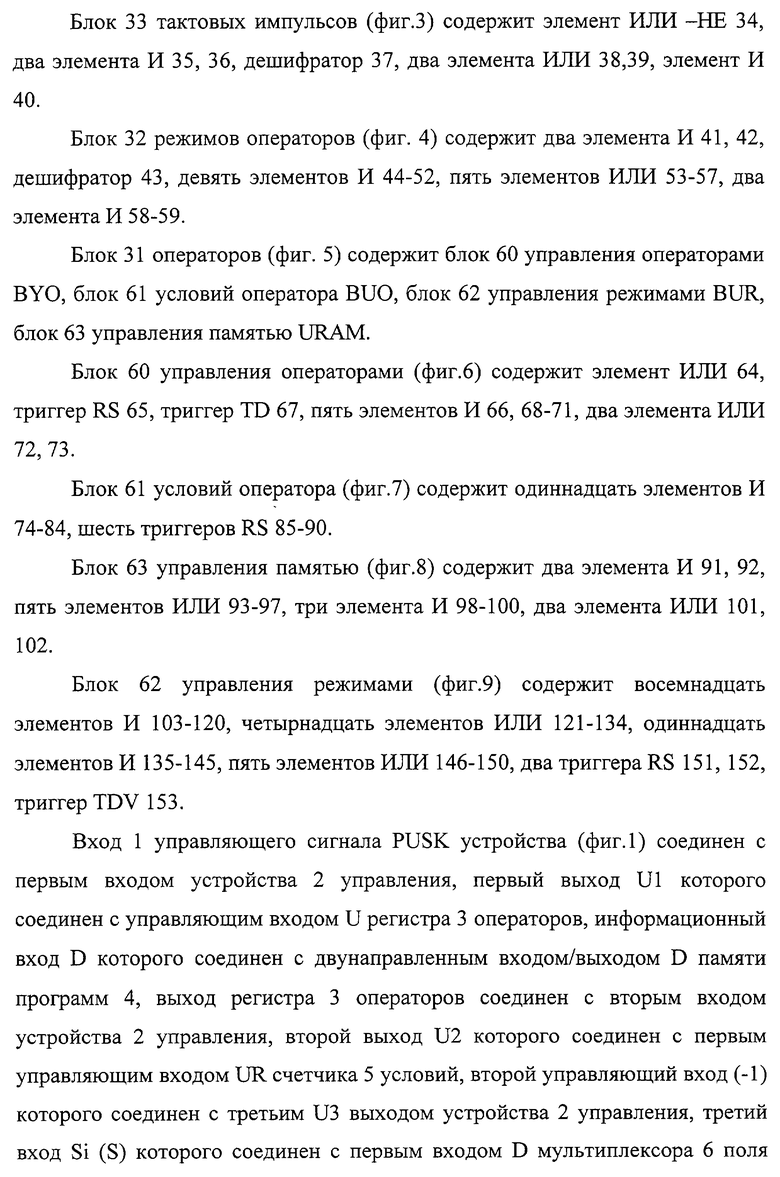

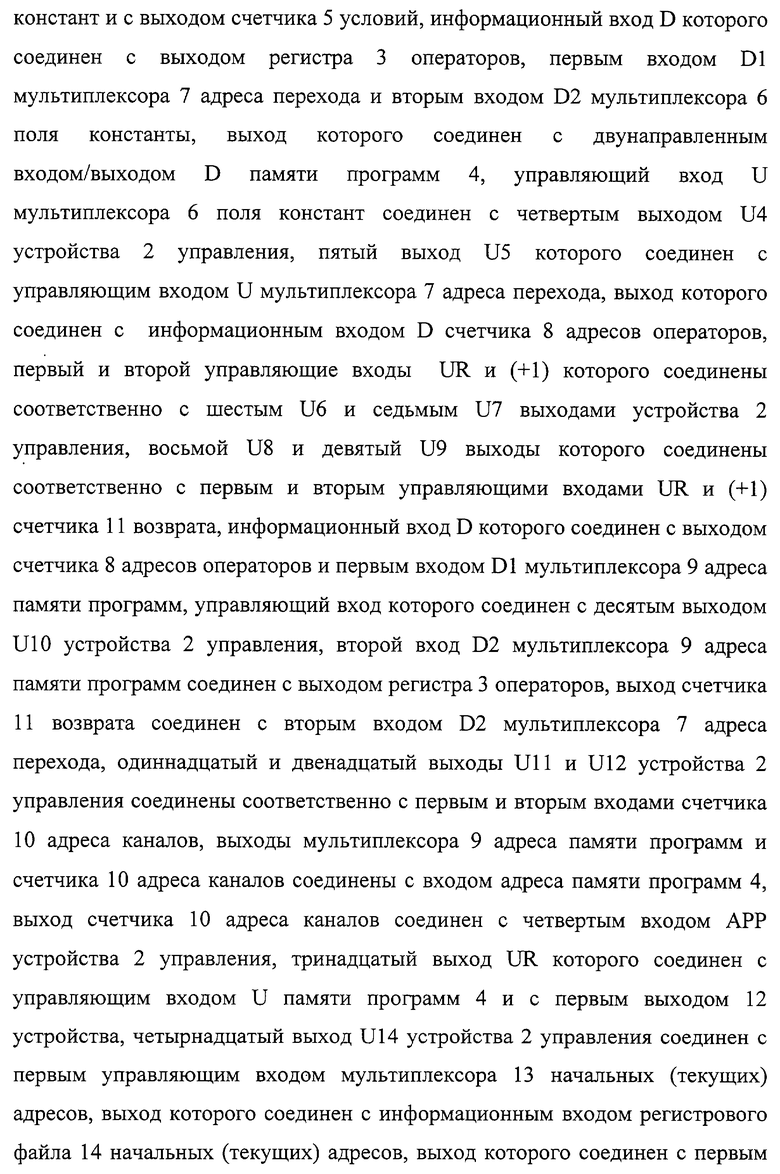

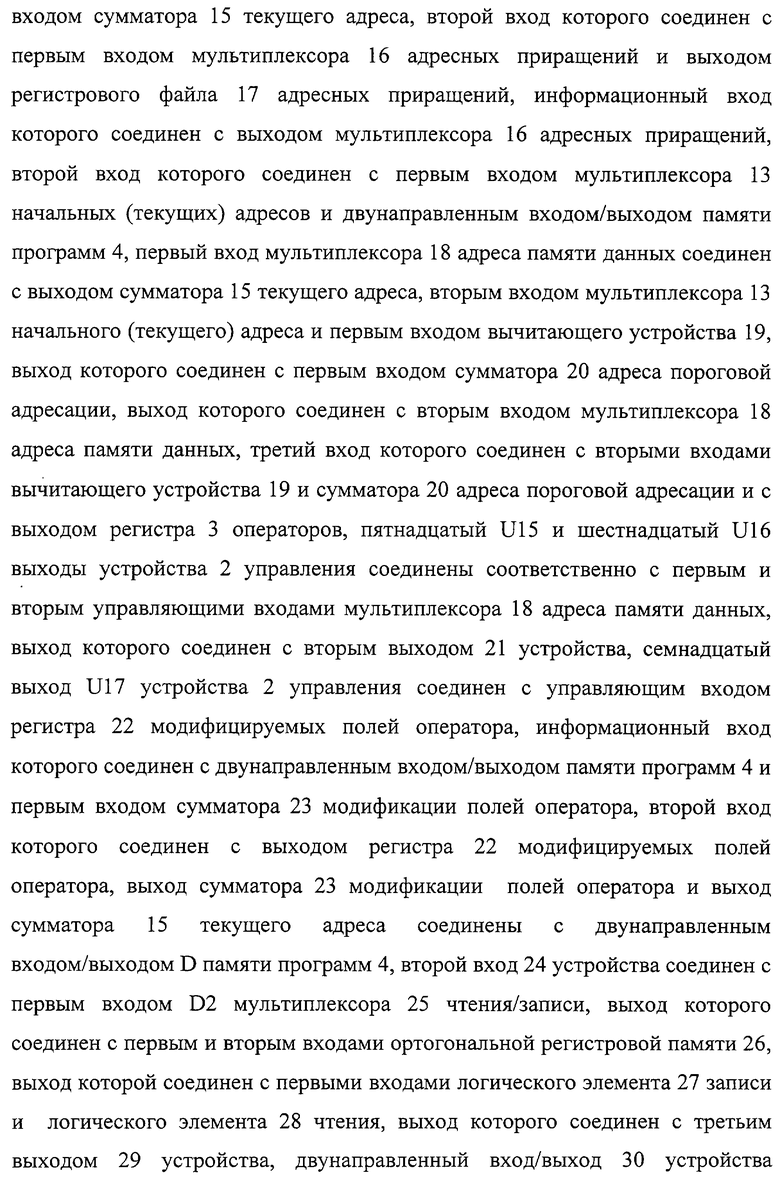

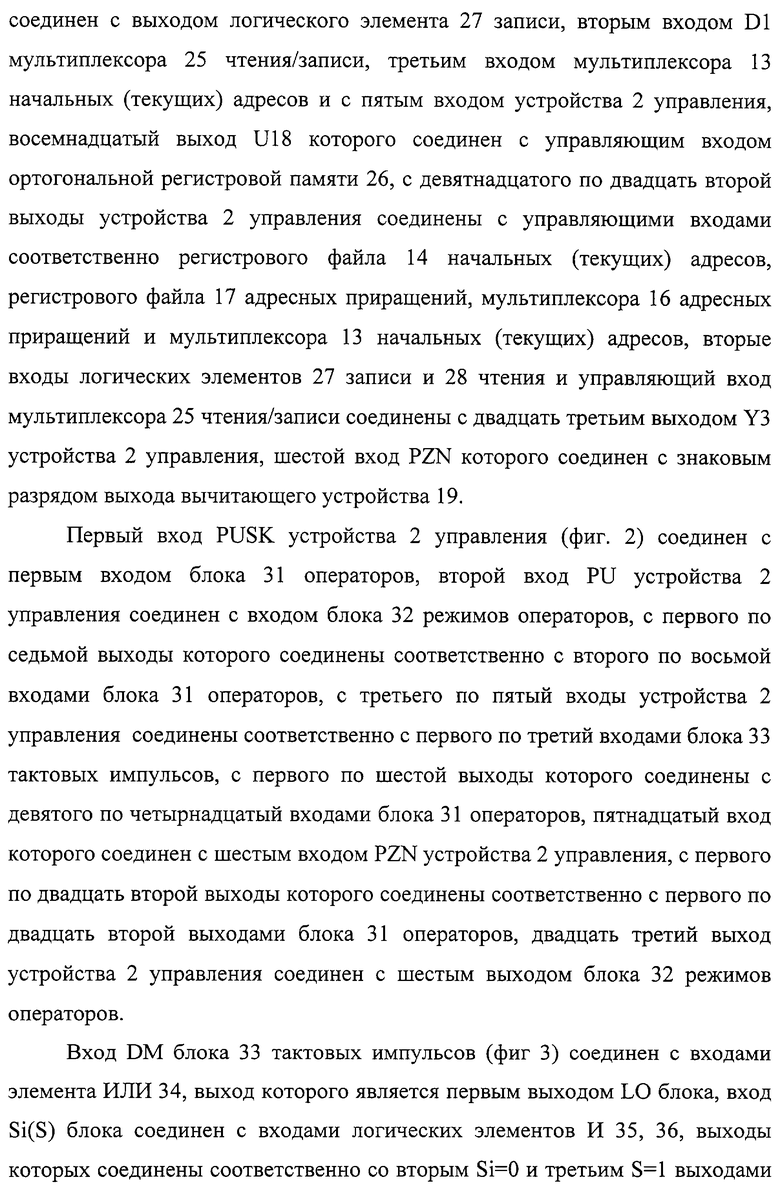

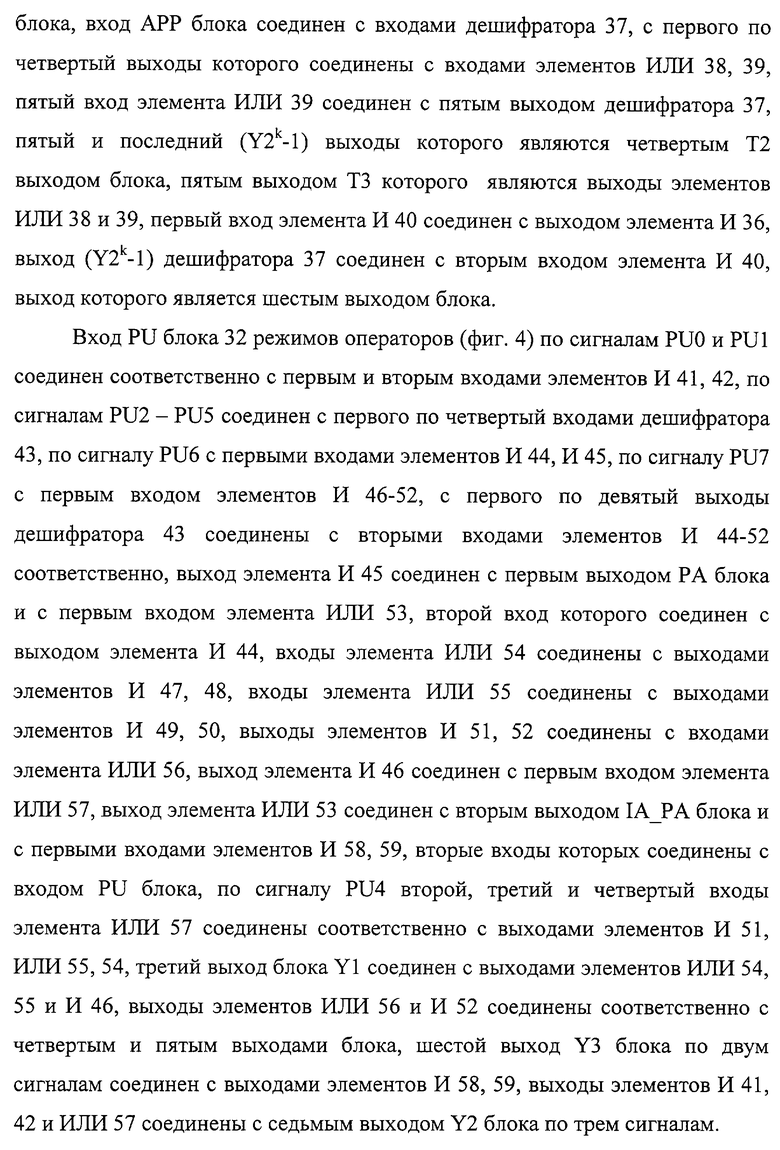

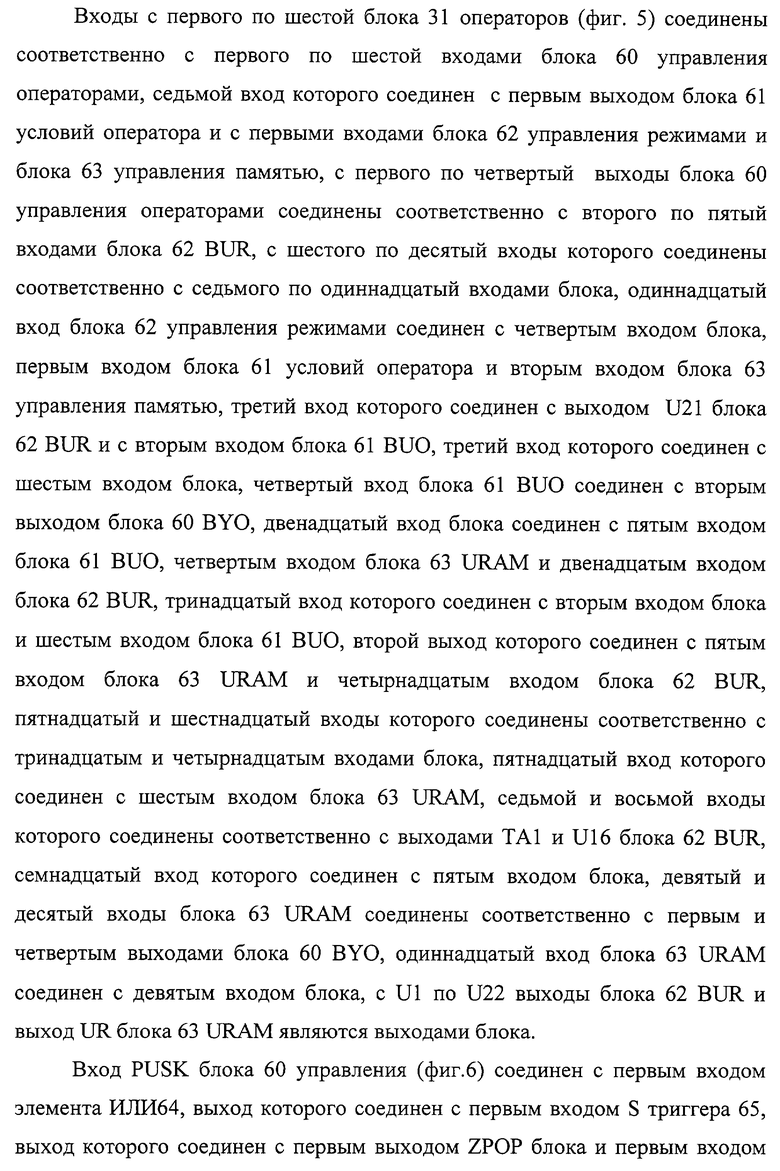

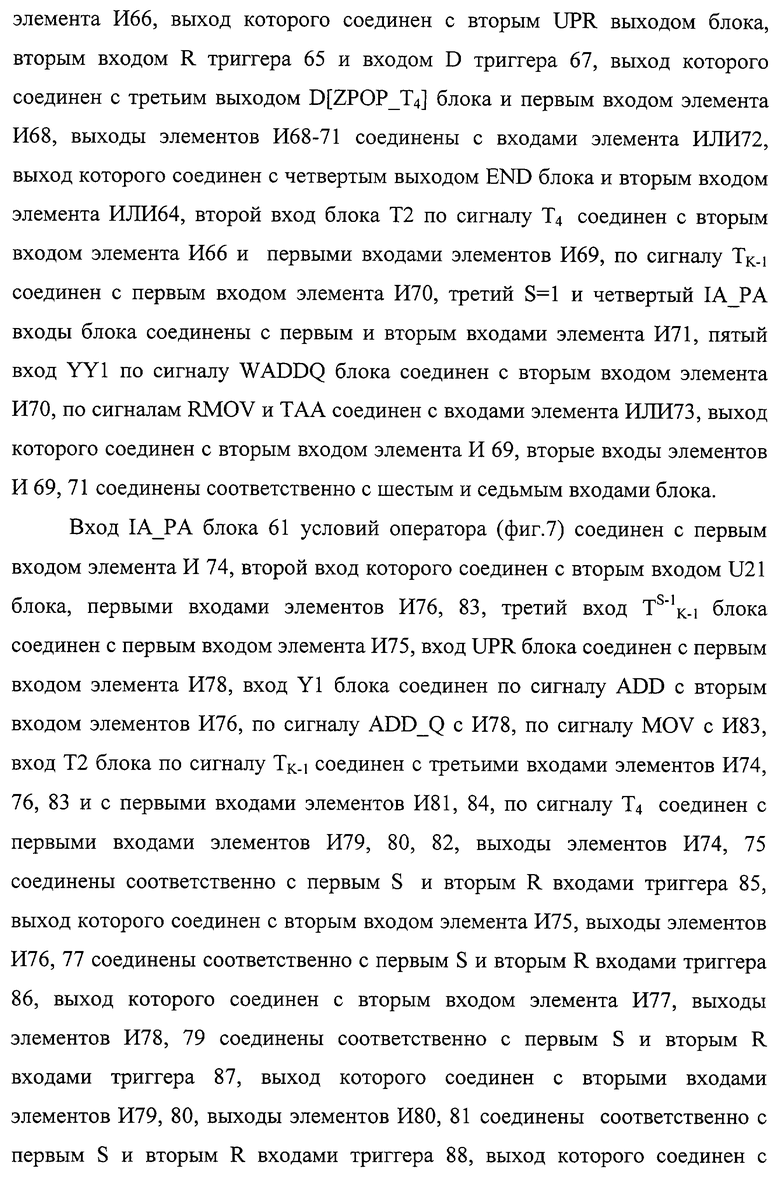

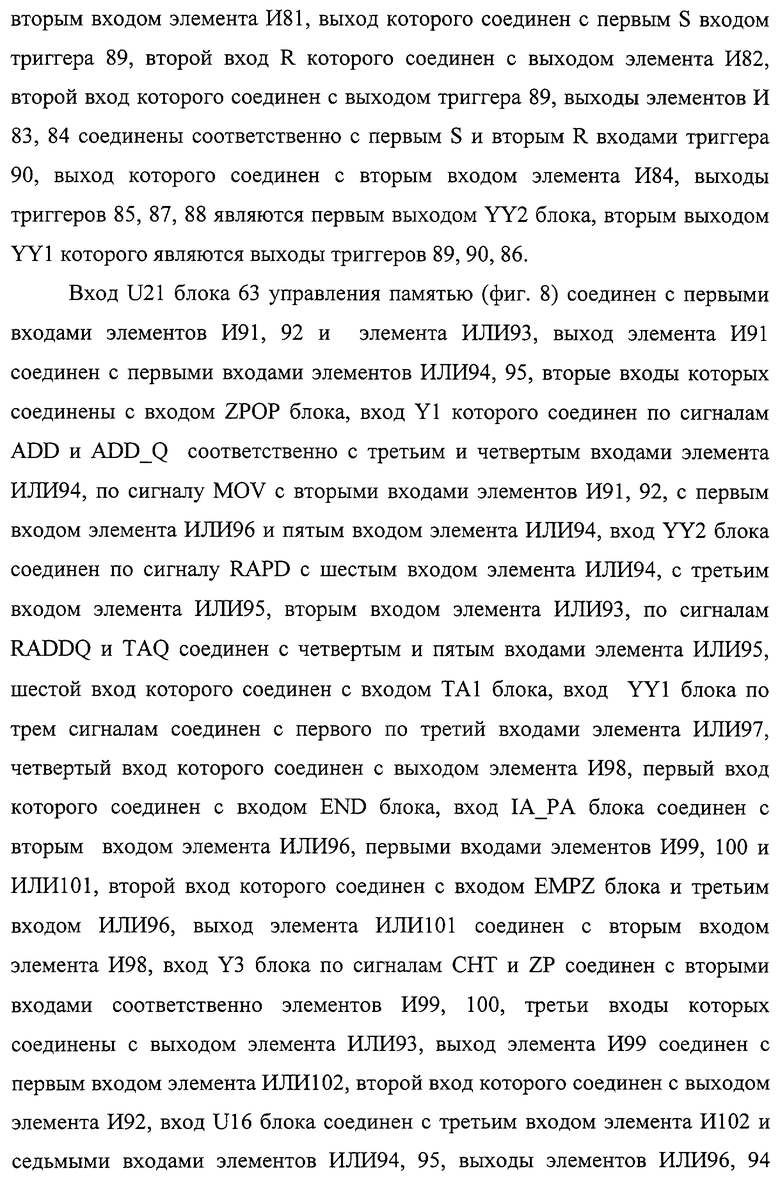

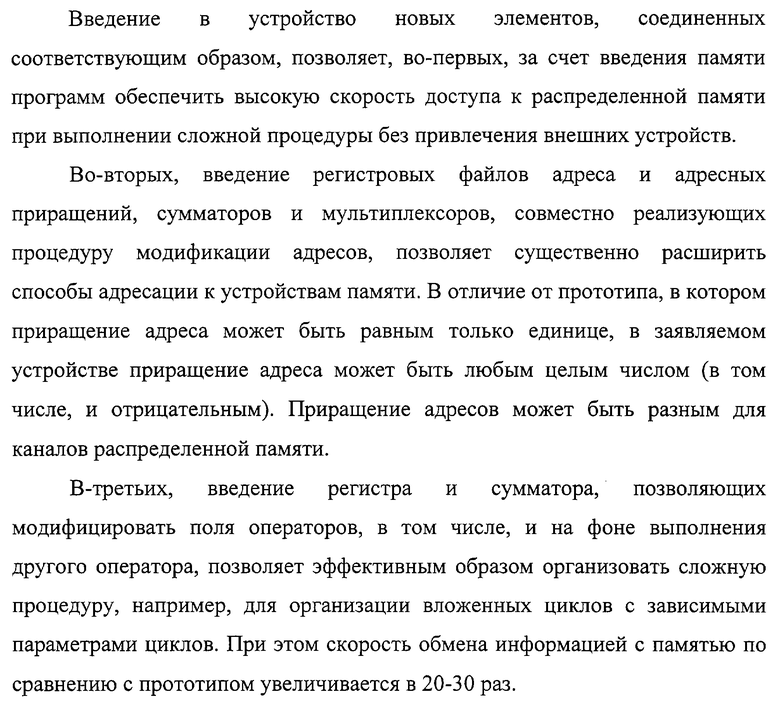

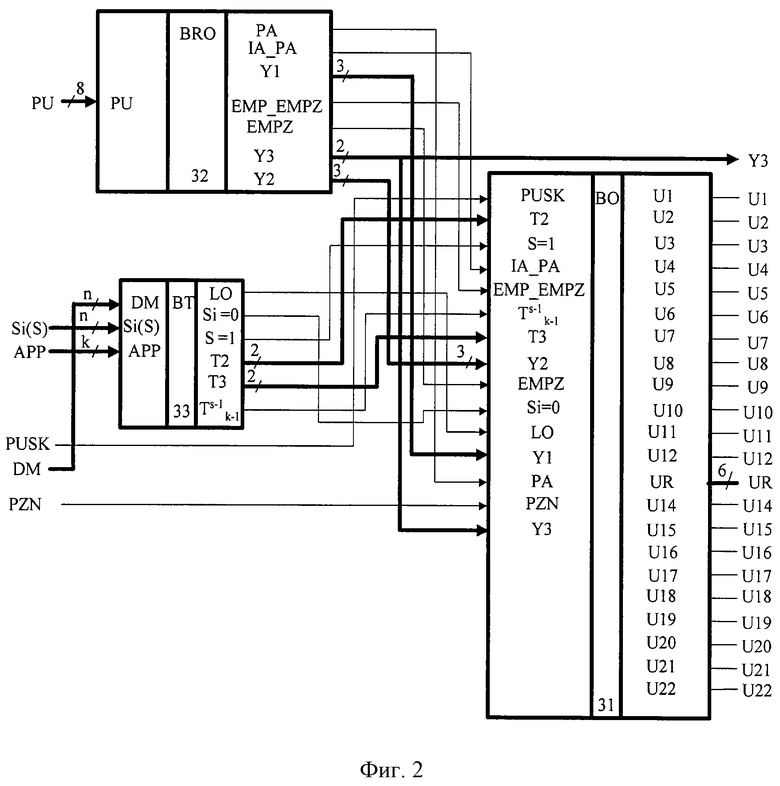

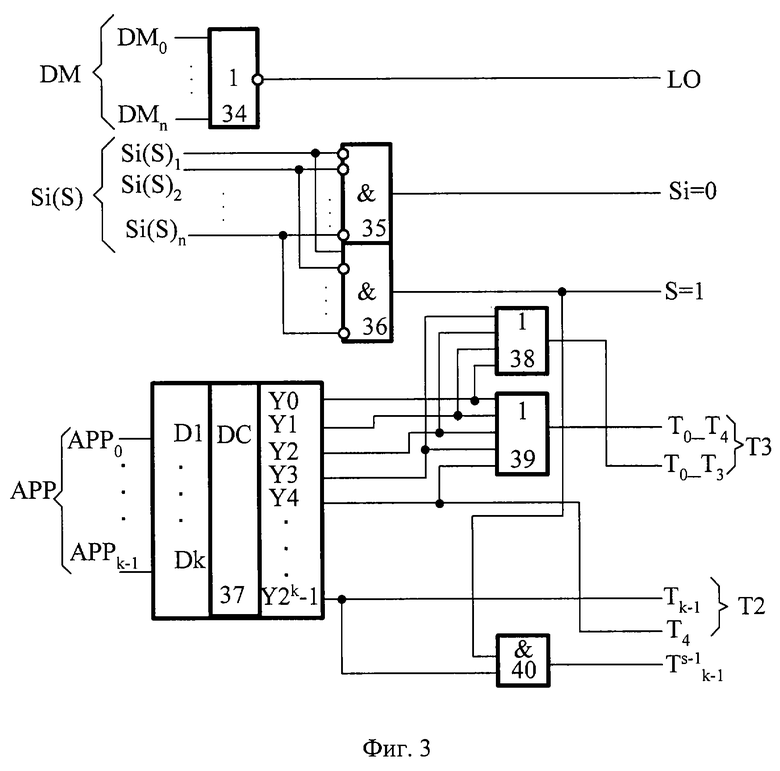

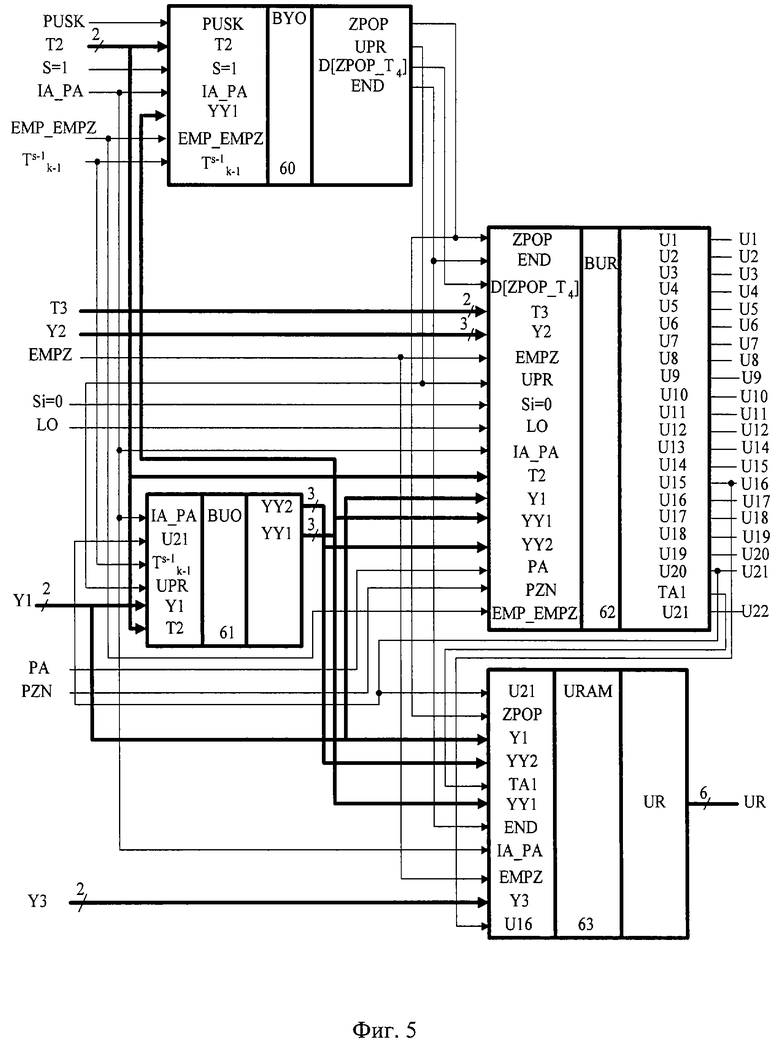

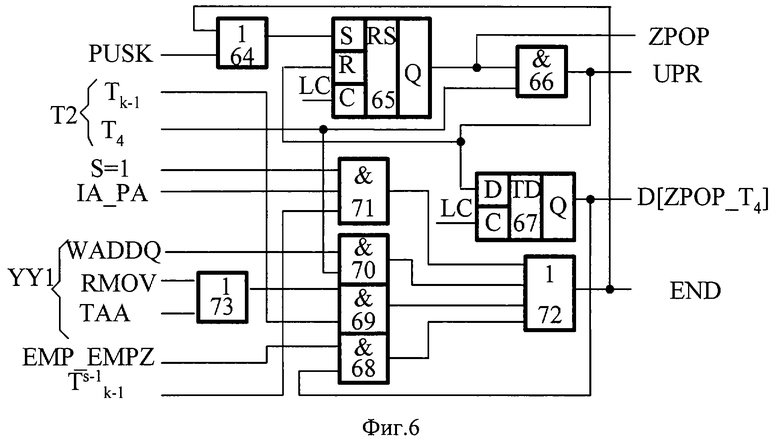

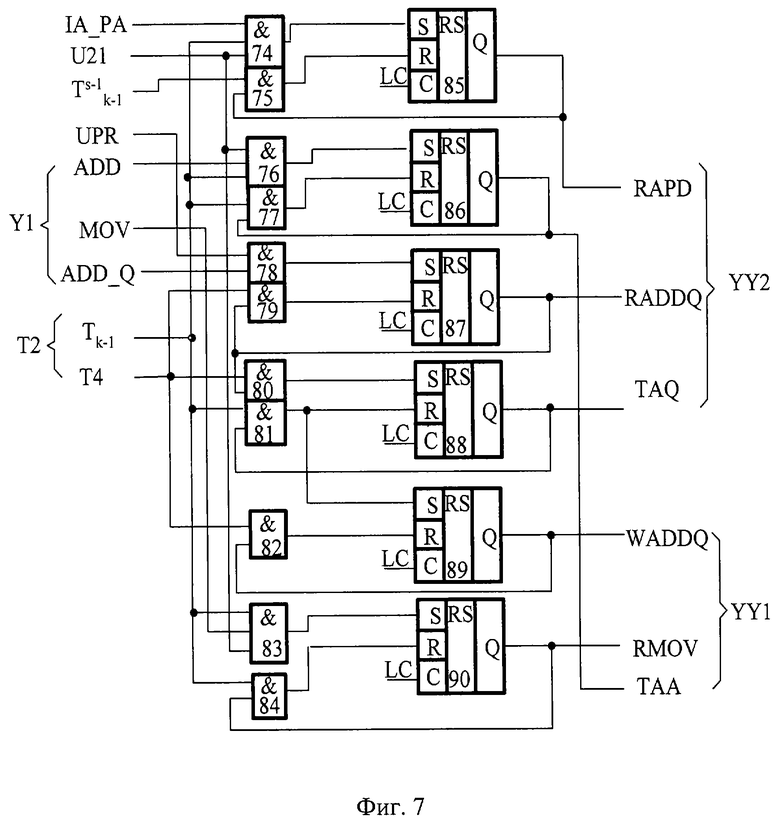

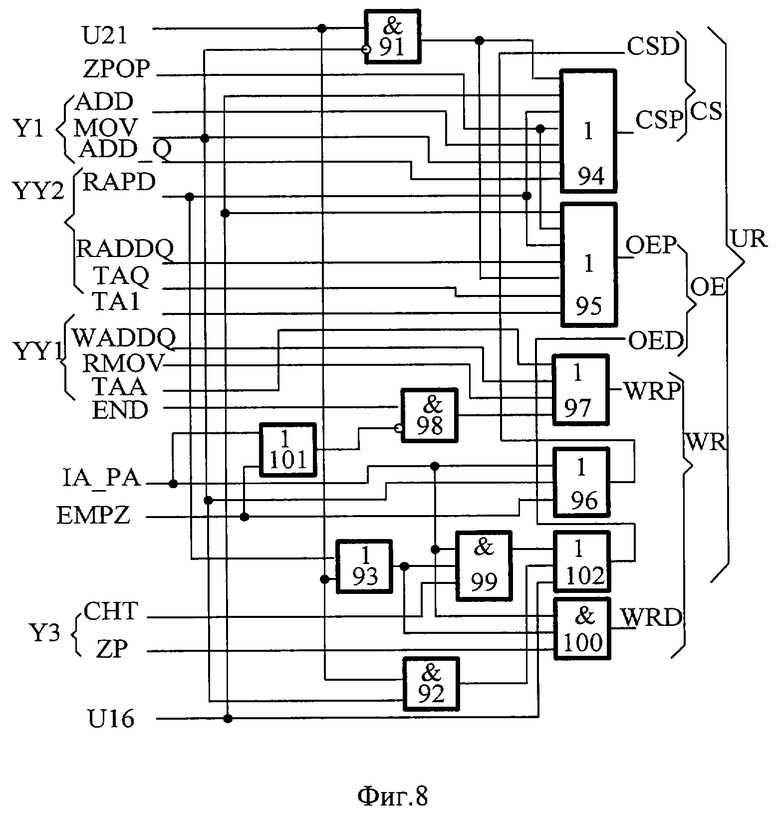

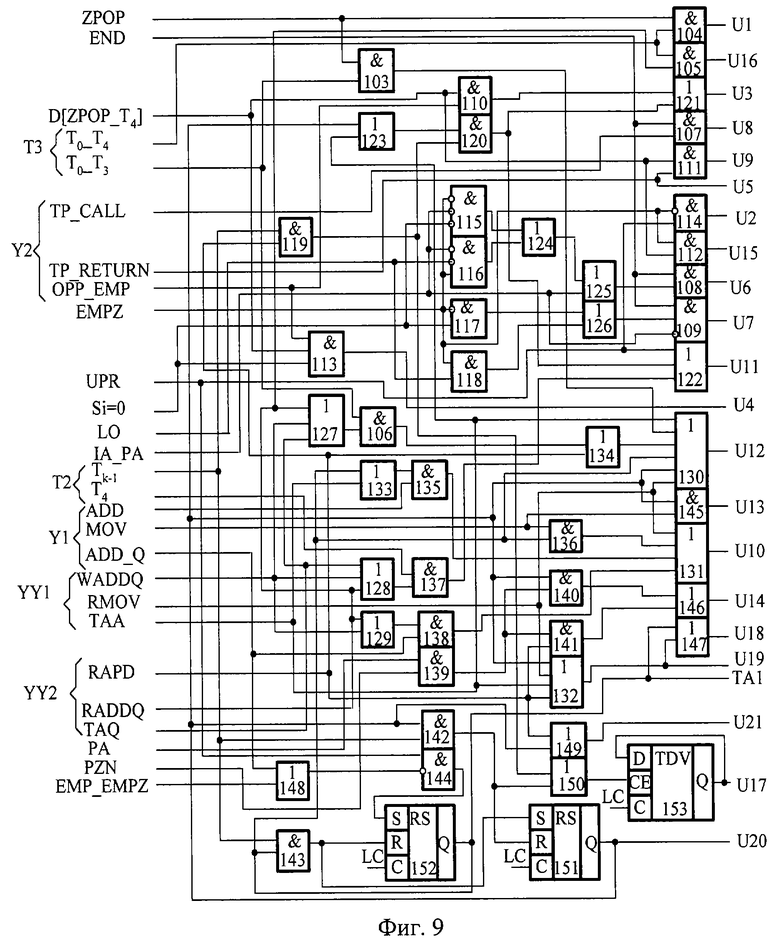

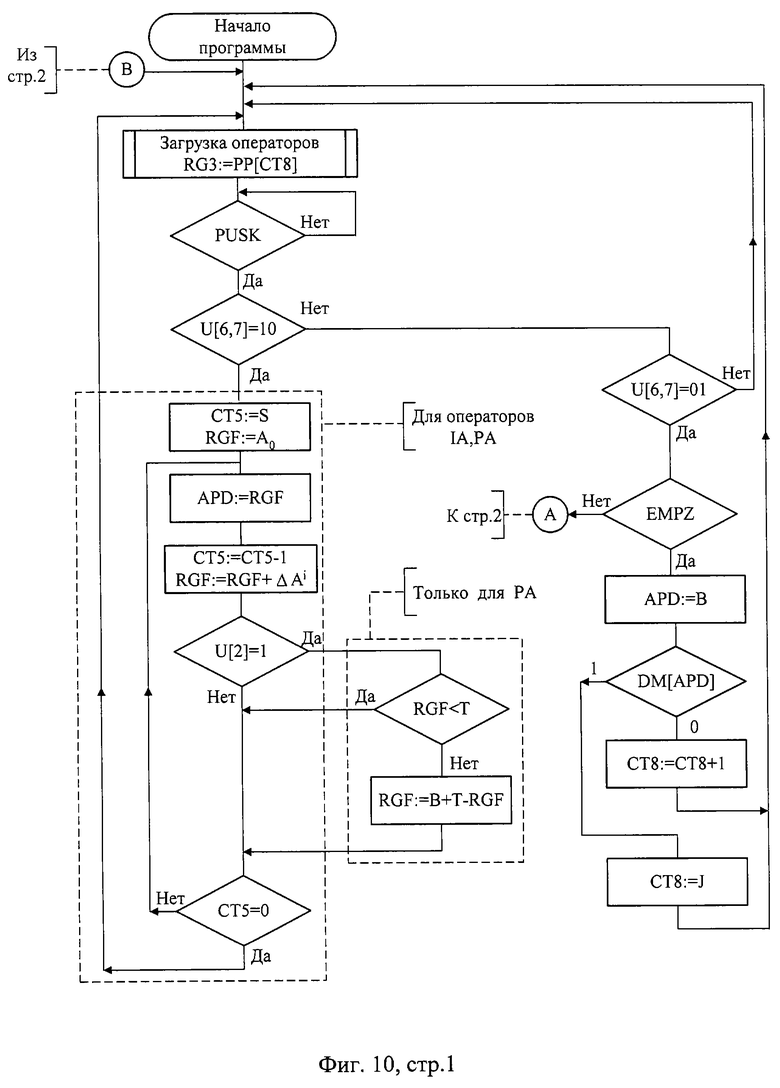

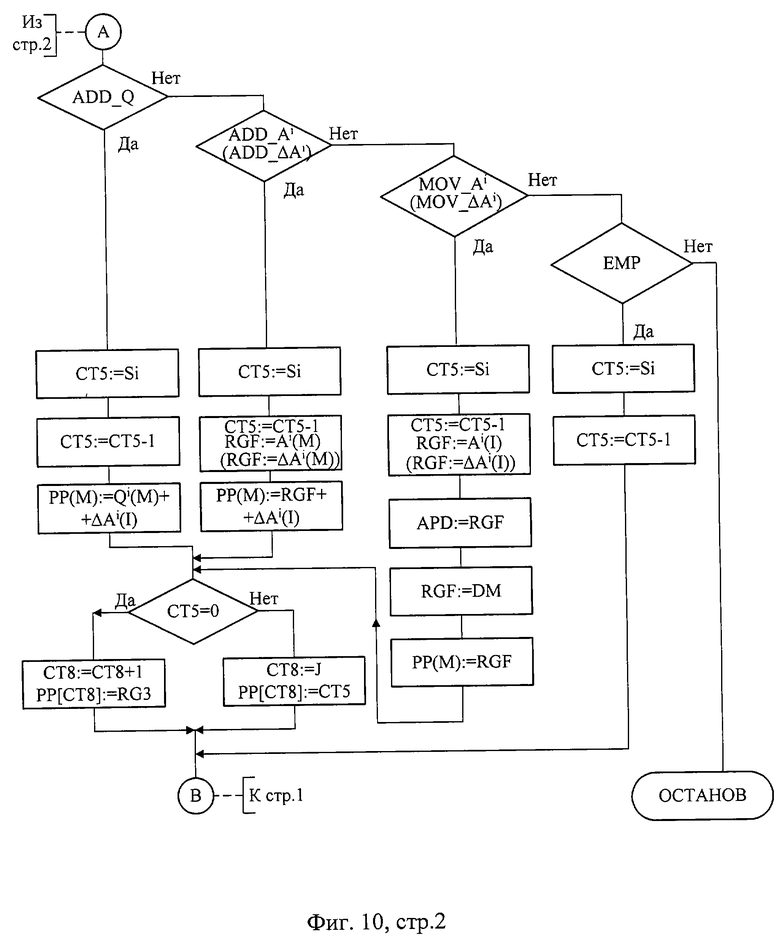

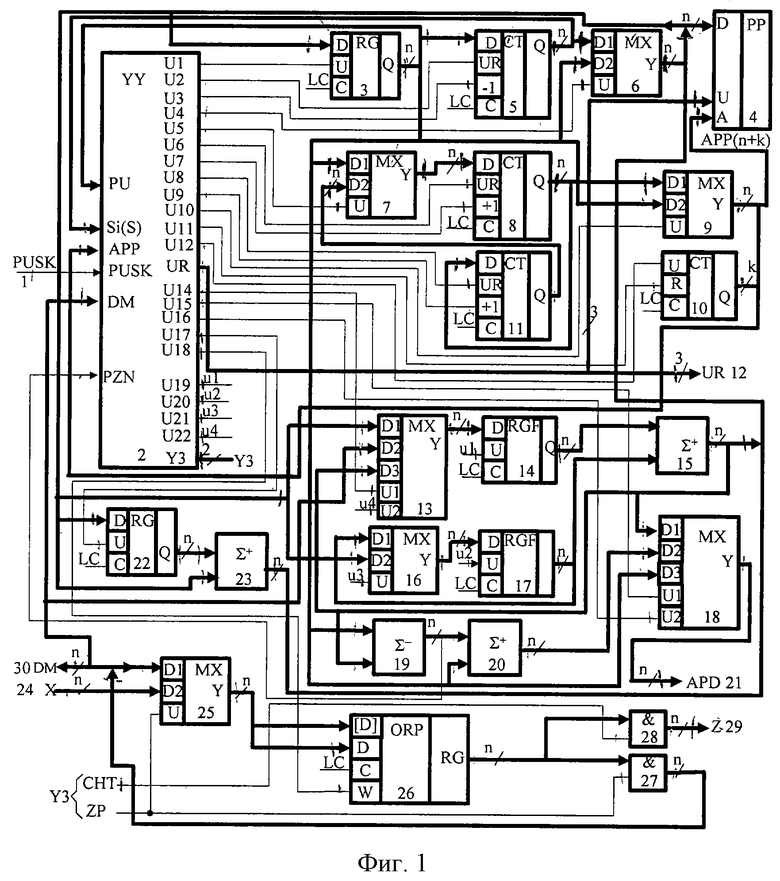

Устройство мультиконтроллер распределенной памяти, обеспечивающее сложную автономную процедуру доступа к каналам распределенной памяти, отличающееся тем, что устройство содержит память программ, устройство управления, регистр операторов, счетчик условий, мультиплексор поля константы, мультиплексор адреса перехода, счетчик адресов операторов, мультиплексор адреса памяти программ, счетчик адреса каналов, счетчик возврата, мультиплексор начальных (текущих) адресов, мультиплексор адресных приращений, два регистровых файла начальных (текущих) адресов и адресных приращений, сумматор текущего адреса, мультиплексор адреса памяти данных, вычитающее устройство, сумматор адреса пороговой адресации, регистр модифицируемых полей оператора, сумматор модификации полей оператора, мультиплексор чтения/записи, ортогональную регистровую память, логические элементы записи и чтения, причем вход управляющего сигнала устройства соединен с первым входом устройства управления, первый выход которого соединен с управляющим входом регистра операторов, информационный вход которого соединен с двунаправленным входом/выходом памяти программ, выход регистра операторов соединен с вторым входом устройства управления, второй выход которого соединен с первым управляющим входом счетчика условий, второй управляющий вход которого соединен с третьим выходом устройства управления, третий вход которого соединен с первым входом мультиплексора поля констант и с выходом счетчика условий, информационный вход которого соединен с выходом регистра операторов, первым входом мультиплексора адреса перехода и вторым входом мультиплексора поля константы, выход которого соединен с двунаправленным входом/выходом памяти программ, управляющий вход мультиплексора поля констант соединен с четвертым выходом устройства управления, пятый выход которого соединен с управляющим входом мультиплексора адреса перехода, выход которого соединен с информационным входом счетчика адресов операторов, первый и второй управляющие входы которого соединены соответственно с шестым и седьмым выходами устройства управления, восьмой и девятый выходы которого соединены соответственно с первым и вторым управляющими входами счетчика возврата, информационный вход которого соединен с выходом счетчика адресов операторов и первым входом мультиплексора адреса памяти программ, управляющий вход которого соединен с десятым выходом устройства управления, второй вход мультиплексора адреса памяти программ соединен с выходом регистра операторов, выход счетчика возврата соединен с вторым входом мультиплексора адреса перехода, одиннадцатый и двенадцатый выходы устройства управления соединены соответственно с первым и вторым входами счетчика адреса каналов, выходы мультиплексора адреса памяти программ и счетчика адреса каналов соединены с входом адреса памяти программ, выход счетчика адреса каналов соединен с четвертым входом устройства управления, тринадцатый выход которого соединен с управляющим входом памяти программ и с первым выходом устройства, четырнадцатый выход устройства управления соединен с первым управляющим входом мультиплексора начальных (текущих) адресов, выход которого соединен с информационным входом регистрового файла начальных (текущих) адресов, выход которого соединен с первым входом сумматора текущего адреса, второй вход которого соединен с первым входом мультиплексора адресных приращений и выходом регистрового файла адресных приращений, информационный вход которого соединен с выходом мультиплексора адресных приращений, второй вход которого соединен с первым входом мультиплексора начальных (текущих) адресов и двунаправленным входом/выходом памяти программ, первый вход мультиплексора адреса памяти данных соединен с выходом сумматора текущего адреса, вторым входом мультиплексора начального (текущего) адреса и первым входом вычитающего устройства, выход которого соединен с первым входом сумматора адреса пороговой адресации, выход которого соединен с вторым входом мультиплексора адреса памяти данных, третий вход которого соединен с вторым входом вычитающего устройства и сумматора адреса пороговой адресации и с выходом регистра операторов, пятнадцатый и шестнадцатый выходы устройства управления соединены соответственно с первым и вторым управляющими входами мультиплексора адреса памяти данных, выход которого соединен с вторым выходом устройства, семнадцатый выход устройства управления соединен с управляющим входом регистра модифицируемых полей оператора, информационный вход которого соединен с двунаправленным входом/выходом памяти программ и первым входом сумматора модификации полей оператора, второй вход которого соединен с выходом регистра модифицируемых полей оператора, выход сумматора модификации полей оператора и выход сумматора текущего адреса соединены с двунаправленным входом/выходом памяти программ, второй вход устройства соединен с первым входом мультиплексора чтения/записи, выход которого соединен с первым и вторым входами ортогональной регистровой памяти, выход которой соединен с первыми входами логического элемента записи и логического элемента чтения, выход которого соединен с третьим выходом устройства, двунаправленный вход/выход устройства соединен с выходом логического элемента записи, вторым входом мультиплексора чтения/записи, третьим входом мультиплексора начальных (текущих) адресов и с пятым входом устройства управления, восемнадцатый выход которого соединен с управляющим входом ортогональной регистровой памяти, с девятнадцатого по двадцать второй выходы устройства управления соединены с управляющими входами соответственно регистрового файла начальных (текущих) адресов, регистрового файла адресных приращений, мультиплексора адресных приращений и мультиплексора начальных (текущих) адресов, вторые входы логических элементов записи и чтения и управляющий вход мультиплексора чтения/записи соединены с двадцать третьим выходом устройства управления, шестой вход которого соединен со знаковым разрядом выхода вычитающего устройства.

| МИКРОПРОГРАММНОЕ УСТРОЙСТВО УПРАВЛЕНИЯ | 1991 |

|

RU2042189C1 |

| КОНТРОЛЛЕР | 1991 |

|

RU2012043C1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ ПАМЯТЬЮ | 1993 |

|

RU2037874C1 |

| УСТРОЙСТВО ДЛЯ ПРИЕМА И ПЕРЕДАЧИ ИНФОРМАЦИИ | 1991 |

|

RU2023295C1 |

| US 5261058 A, 09.11.1993 | |||

| US 5835940 A, 10.11.1998. | |||

Авторы

Даты

2003-08-20—Публикация

2001-08-08—Подача