Изобретение относится к вычислительной технике и может быть использовано для создания программного обеспечения управляющих вычислительных систем, которые являются центральным звеном систем управления изделиями ракетно-космической техники.

Одним из наиболее важных этапов создания программного обеспечения электронных вычислительных машин является этап отработки созданного текста программ и подтверждения его корректной работы для различных наборов исходных параметров и состава обрабатываемой информации, что является достаточно трудоемким и продолжительным процессом, занимающим значительную часть времени проектирования и требующим значительных материальных затрат. Поэтому во всем мире уделяется серьезное внимание как методике, так и средствам верификации программного обеспечения (ПО).

Особенно большие сложности верификации ПО возникают при создании программ реального времени для управляющих вычислительных машин (УВМ), входящих в состав систем автоматического управления (САУ) робототехническими комплексами (РТК). Примерами таких систем являются УВМ, работавшие в составе РТК, при ликвидации последствий аварии на Чернобыльской АЭС, а также УВМ, входящие в состав САУ изделий ракетно-космической техники.

Сложность создания ПО для таких САУ усугубляется необходимостью введения в его состав задач контроля исправности УВМ, а также нейтрализации возникающих в процессе работы отказов в аппаратуре САУ, а также задачи сохранения работоспособности САУ в целом при деградации параметров компонентов. В результате ПО должно быть работоспособным в условиях изменения вычислительных ресурсов в процессе работы.

Известны принципы отладки ПО, используемые американскими специалистами для ЭВМ общего назначения (см. монографию Наука отладки, авторы Мэтт Тэллес и Юань Хсих /перевод с английского/ изд. КУДИЦ - ОБРАЗ, Москва, 2003, с.217). В основе отладки лежит анализ результатов вычислений самим разработчиком ПО путем выдачи на внешние носители, например на цифровую печать, промежуточных результатов вычислений при фиксированном наборе входных параметров, для чего в текст программы делаются технологические вставки, обеспечивающие выдачу результатов для анализа. Недостатком такой отладки является необходимость коррекции программ после завершения отладки для устранения технологических вставок, что требует повторения проверок.

Такая отладка совершенно непригодна для верификации программ, работающих в реальном масштабе времени с непрерывно меняющейся входной информацией, так как любые вставки в текст программы искажают реальное время вычислений. Наиболее полно задача отработки ПО реального времени для управляющих вычислительных систем решена отечественными специалистами (см. Б.А.Микрин. Бортовые комплексы управления космическими аппаратами и проектирование их программного обеспечения, изд. МГТУ им. Н.Э.Баумана, 2003 с.243-249, рис.4.1). Для отработки аппаратуры и порограммного обеспечения используется комплексный моделирующий стенд (КМС), содержащий бортовую вычислительную систему(БВС) с отрабатываемым программным обеспечением, пульт управления стендом, моделирующая вычислительная платформа на основе ЭВМ общего назначения, полный комплект датчиков и исполнительных устройств, связанных с БВС соответственно через аналого-цифровые и цифроаналоговые преобразователи. В состав КМС входит также весь комплект штатной аппаратуры космического аппарата, включая рабочие места экипажа. Такой состав аппаратуры комплексного стенда позволяет обеспечить проверку функционирования бортовой управляющей вычислительной системы и ее программного обеспечения в реальном масштабе времени. В тоже время в случае неправильного функционирования из-за ошибок ПО поиск причин возникновения ошибок затруднен, так как наличие штатной аппаратуры с датчиками входной информации и аналого-цифровых преобразователей не позволяет провести несколько повторений вычислений цикла управления с полностью идентичной входной информацией, что является обязательным условием для обнаружения места ошибки в тексте программ. Кроме того, в такой системе затруднен процесс проверки функционирования при возникновении неисправностей в бортовой аппаратуре по экономическим причинам. Более того даже просто создание такого стенда и поддержание его в рабочем состоянии требует существенных финансовых затрат, что ограничивает возможности верификации ПО.

Для обеспечения оперативности и полноты проверки программ бортовых УВМ предлагается

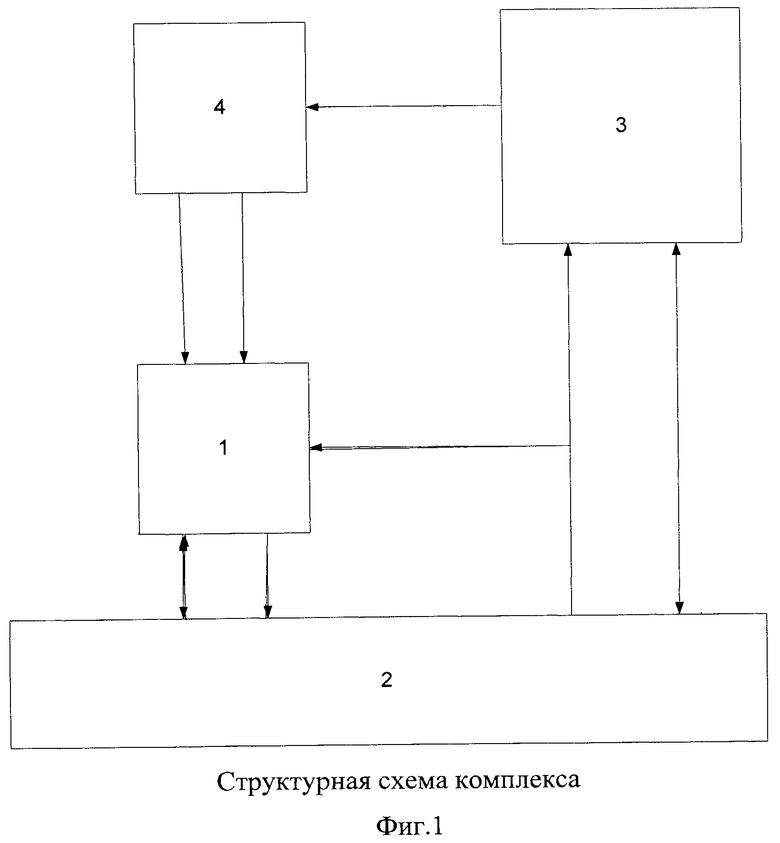

КОМПЛЕКС ОТЛАДКИ, содержащий собственно бортовую УВМ, пульт управления комплексом, ЭВМ общего назначения и группу имитаторов входной информации. Структурная схема комплекса отработки приведена на рисунке (фиг.1), где цифрой 1 обозначена бортовая УВМ, цифрой 2 обозначен пульт управления комплексом. Цифрой 3 обозначена ЭВМ общего назначения, в качестве которой может использоваться ПЭВМ типа IBM PC, цифрой 4 обозначена группа имитаторов входной информации. При этом пульт управления через первые магистральные связи подключен к ЭВМ общего назначения, а через вторые магистральные связи подключен к бортовой УВМ, входы которой подключены к имитаторам входной информации, входы которых подключены к ЭВМ общего назначения, сигнальный вход которой объединен с управляющим входом бортовой УВМ и подключен к выходу пульта управления, синхронизирующий вход которого подключен к синхронизирующему выходу УВМ.

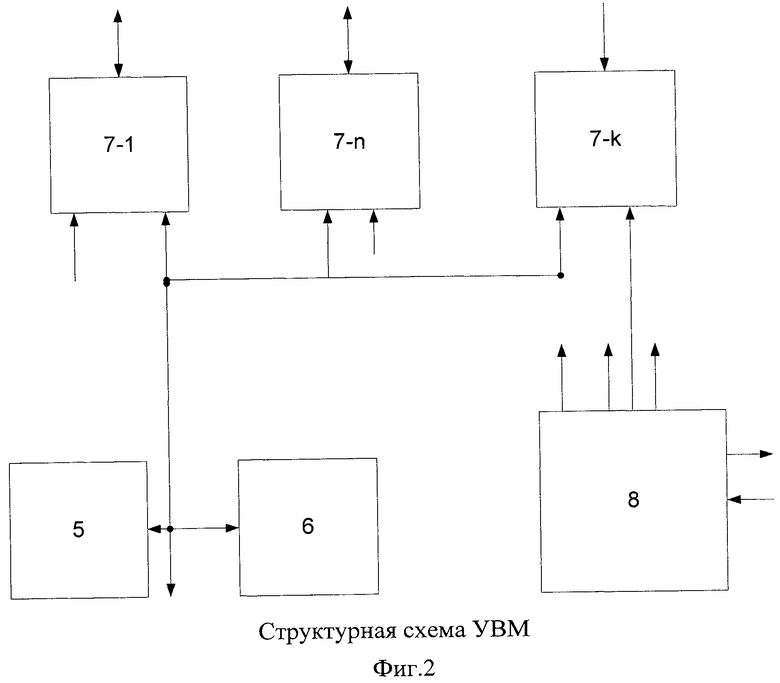

Структурная схема бортовой УВМ приведена на рисунке (фиг.2), где цифрой 5 обозначен процессор, цифрой 6 обозначено запоминающее устройство, цифрами от 7-1 до 7-к обозначены К устройств обмена, цифрой 8 обозначен формирователь синхроимпульсов.

Процессор, устройства обмена и запоминающие устройства связаны между собой магистральными линиями связи, которые является внешними вторыми магистральными связями УВМ в комплексе. При этом выходы формирователя синхроимпульсов подключены к синхронизирующим входам процессора и всех устройств обмена, входы которых являются входами УВМ, управляющий вход которой является входом формирователя синхроимпульсов, дополнительный выход которого является синхронизирующим выходом УВМ.

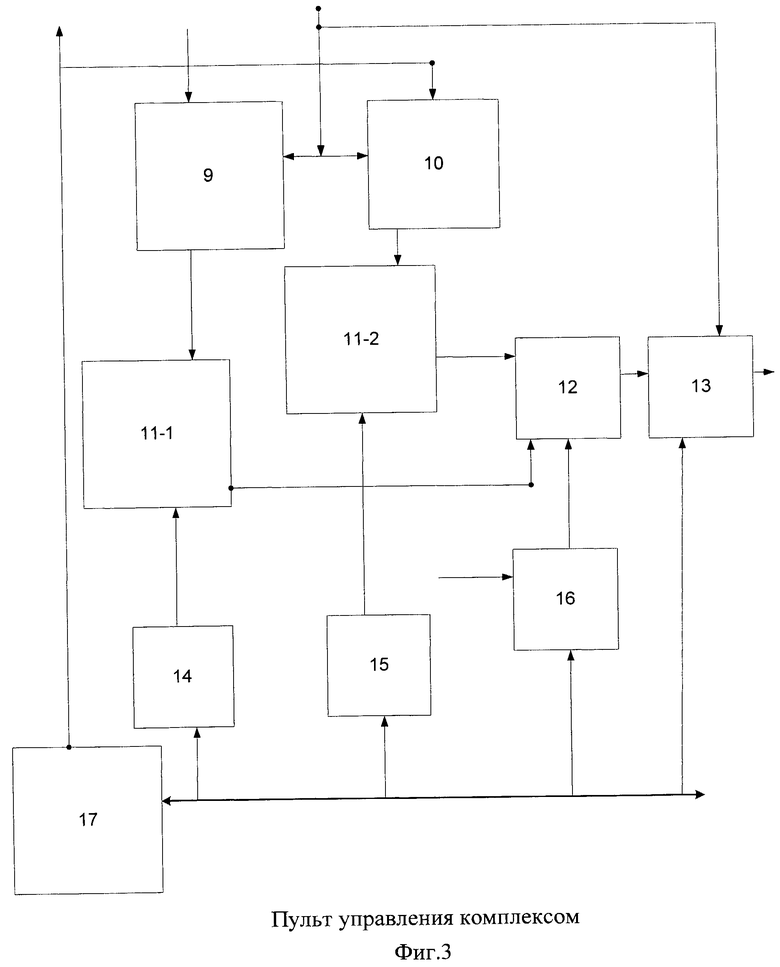

Структурная схема пульта управления комплексом приведена на рисунке (фиг.3), где цифрой 9 обозначен регистр адреса, цифрой 10 обозначен регистр данных. Цифрами 11 обозначена группа схем сравнения (цифрой 11-1 - схема сравнения адреса - первая, цифрой 11-2 - схема сравнения данных - вторая), цифрой 12 обозначен элемент ИЛИ, цифрой 13 обозначен триггер-формирователь сигнала «Останов», цифрой 14 обозначен регистр кода адреса, цифрой 15 обозначен регистр кода данных, цифрой 16 обозначен счетчик контрольного интервала времени, цифрой 17 обозначены буферные приемопередатчики. Входы регистров кода адреса и кода данных, а также входы-выходы буферных приемопередатчиков подключены к двунаправленной информационной шине, являющейся первой внешней магистральной шиной пульта управления для связи с ЭВМ общего назначения. Входы регистра адреса и регистра данных объединены между собой и выходами буферных приемопередатчиков и являются внешней второй магистральной шиной пульта для связи с УВМ. Синхронизирующие входы регистров адреса и данных, счетчика контрольного интервала и триггер-формирователя являются синхронизирующим входом пульта управления. Кроме того, выходы регистра адреса и регистра данных подключены соответственно к первым входам первой и второй схем сравнения, у которых ко вторым входам подключены соответственно выходы регистра кода адреса и регистра кода данных, а выходы схем сравнения подключены к первому и второму входам элемента ИЛИ, к третьему входу которого подключен выход счетчика контрольного интервала времени. Выход элемента ИЛИ подключен ко входу триггер-формирователя, выход которого является управляющим выходом пульта управления.

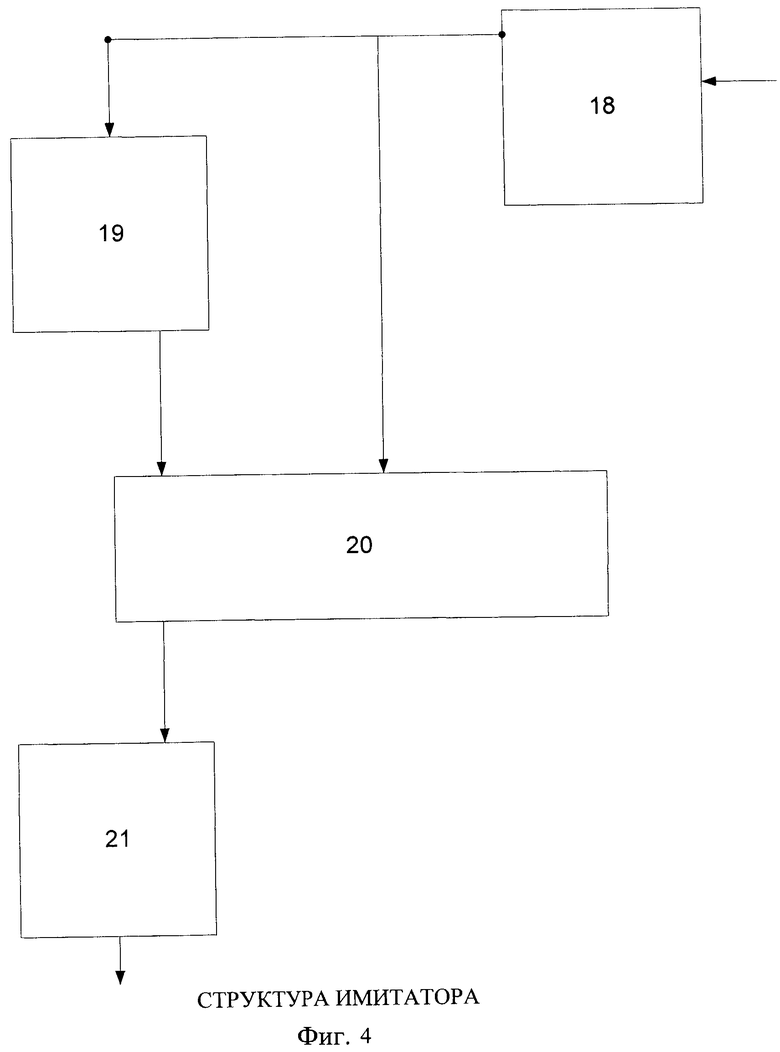

Структурная схема имитатора приведена на рисунке (фиг.4), где цифрой 18 обозначен блок связи с ЭВМ, цифрой 19 обозначено запоминающее устройство, цифрой 20 обозначен контроллер обмена с собственной памятью программ, цифрой 21 обозначен буферный регистр для связи с УВМ. Вход блока связи с ЭВМ является входом имитатора, а его выход подключен ко входам запоминающего устройства и контроллера, подключенного двунаправленными связями к запоминающему устройству, а выходом - буферному регистру, выход которого является выходом имитатора.

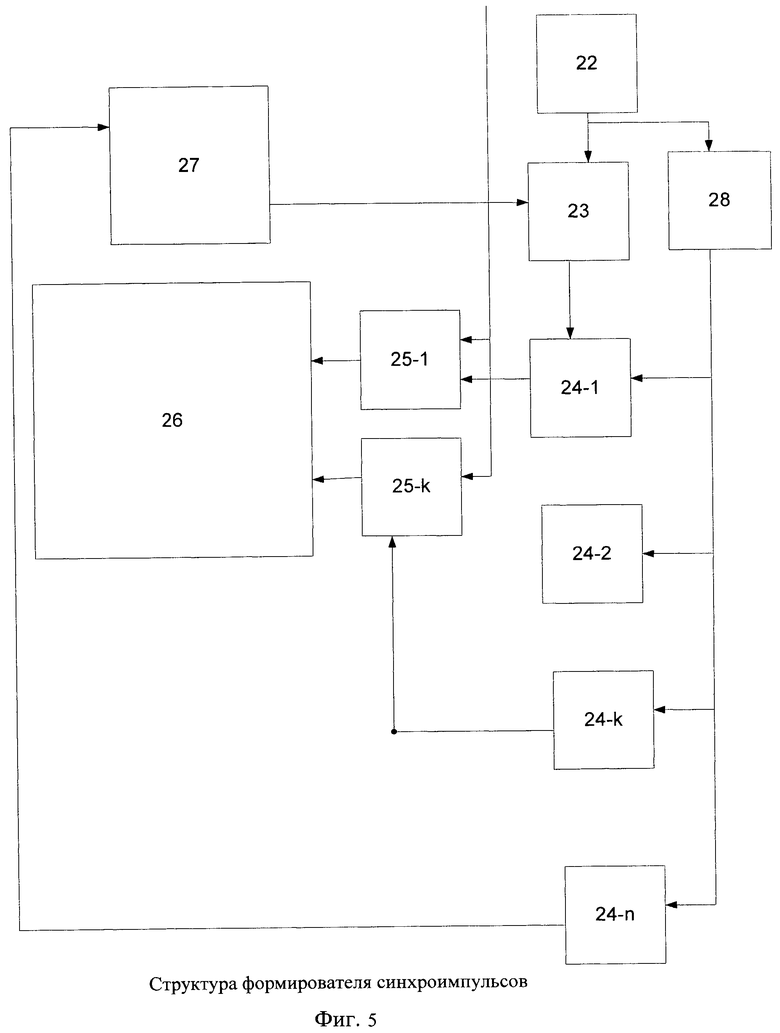

Структурная схема формирователя синхроимпульсов приведена на рисунке (фиг.5), где цифрой 22 обозначен задающий генератор, цифрой 23 обозначен элемент И, цифрами от 24-1 до 24-n обозначены n последовательно соединенных триггеров, образующих сдвиговый регистр, цифрами от 25-1 до 25-k (где k меньше n) обозначены триггеры привязки, цифрой 26 обозначен элемент ИЛИ, цифрой 27 обозначен триггер «Останов», цифрой 28 обозначен инвертор (элемент НЕ). Выход задающего генератора подключен ко входу инвертора и первому входу элемента И, выход которого подключен к входу первого из n последовательно включенных триггеров, стробирующие входы которых подключены к выходу инвертора, а выходы триггеров с первого по k-й подключены к стробирующим входам триггеров привязки, информационные входы которых объединены между собой и являются управляющим входом формирователя, а выходы триггеров привязки подключены к входам элемента ИЛИ, выход которой подключен к запускающему входу триггера «Останов», выход которого подключен ко второму входу элемента И, а стробирующий вход этого триггера подключен к выходу n-го триггера сдвигового регистра, являющегося синхронизирующим выходом формирователя и УВМ.

Комплекс работает следующим образом.

1. Перед началом отладки программ УВМ из ЭВМ общего назначения в запоминающее устройство имитаторов внешних подсистем загружается массив заранее рассчитанной информации, соответствующий работе системы управления в отрабатываемом режиме. В процессе проведения отладки по программе контроллеров обмена эта информация пересылается в буферный регистр, откуда считывается УВМ. Программа работы контроллеров может быть изменена записью из ЭВМ общего назначения.

2. Контроль промежуточных результатов работы программы обеспечивается считыванием информации из запоминающего устройства УВМ в определенных точках программы. С этой целью в регистры кодов адреса и данных пульта управления заносятся контрольные коды, при совпадении которых с адресом команды или данных при выполнении программы УВМ срабатывают соответствующие схемы сравнения, в результате чего включается триггер, формирующий сигнал «Останов». Этот сигнал поступает в формирователь синхроимпульсов УВМ и запрещает выработку серии синхроимпульсов, начиная с очередного такта работы. Кроме того, он переводит внутренние шины УВМ в третье состояние с высоким импедансом, делая их доступными по связям с пультом управления. Получив сигнал «Останов» ЭВМ по заранее подготовленной программе или по указаниям оператора проводит чтение состояния внутренней памяти УВМ и вывод на общедоступные средства отображения. Получив необходимую информацию, оператор через ЭВМ задает очередные контрольные точки и снимает сигнал «Останов». Формирователь синхроимпульсов начинает работу и программа УВМ продолжает выполнение без нарушения работы реального времени. Кроме того, контрольная точка остановки программ может быть задана записью кода в счетчик контрольного интервала времени пульта управления.

| название | год | авторы | номер документа |

|---|---|---|---|

| ТЕХНОЛОГИЧЕСКАЯ УВМ | 2013 |

|

RU2563139C2 |

| МОДЕЛИРУЮЩИЙ КОАП | 2013 |

|

RU2516703C1 |

| КОНТРОЛЛЕР ПЕРЕДАЧИ ДАННЫХ | 2013 |

|

RU2514135C1 |

| СИСТЕМА ДЛЯ ПЕРЕДАЧИ ДАННЫХ | 2011 |

|

RU2444052C1 |

| СИСТЕМА ОБРАБОТКИ ИЗОБРАЖЕНИЙ | 2011 |

|

RU2452125C1 |

| НЕЙРОВЫЧИСЛИТЕЛЬ | 2013 |

|

RU2553098C2 |

| СИСТЕМА АСТРОНАВИГАЦИИ | 2013 |

|

RU2548927C1 |

| АДАПТИВНАЯ ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 2011 |

|

RU2477882C2 |

| ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО БИНС | 2011 |

|

RU2469376C1 |

| САМООРГАНИЗУЮЩАЯСЯ ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 2011 |

|

RU2473113C1 |

Изобретение относится к вычислительной технике и может быть использовано при создании программного обеспечения управляющих вычислительных систем. Техническим результатом является обеспечение оперативности и полноты проверки программ бортовых управляющих вычислительных машин за счет повторений вычислений цикла управления с полностью идентичной входной информацией. Комплекс отладки программ содержит управляющую вычислительную машину; пульт управления и ЭВМ общего назначения, причем в его состав введена группа имитаторов входной информации, подключенных входами к ЭВМ общего назначения, а выходами - к управляющей вычислительной машине, синхронизирующий выход которой подключен к синхронизирующему входу пульта управления, который через первую магистральную шину подключен к управляющей вычислительной машине, а через вторую - к ЭВМ общего назначения, сигнальный вход которой объединен с управляющим входом управляющей вычислительной машины и подключен к выходу пульта управления. 4 з.п. ф-лы, 5 ил.

1. Комплекс отладки программ, содержащий управляющую вычислительную машину, пульт управления и ЭВМ общего назначения, отличающийся тем, что, с целью повышения полноты отладки, в его состав введена группа имитаторов входной информации, подключенных входами к ЭВМ общего назначения, а выходами - к управляющей вычислительной машине, синхронизирующий выход которой подключен к синхронизирующему входу пульта управления, который через первую магистральную шину подключен к управляющей вычислительной машине, а через вторую - к ЭВМ общего назначения, сигнальный вход которой объединен с управляющим входом управляющей вычислительной машины и подключен к выходу пульта управления.

2. Комплекс отладки по п.1, отличающийся тем, что управляющая вычислительная машина содержит формирователь синхроимпульсов, а также модуль процессора, модуль запоминающего устройства, связанные первой магистральной шиной с k модулями связи, входы которых являются входами управляющей вычислительной машины, причем синхронизирующие входы модуля процессора и модулей связи подключены к синхронизирующим выходам формирователя синхроимпульсов, у которого синхронизирующий выход и управляющий вход являются одноименными выходом и входом управляющей вычислительной машины.

3. Комплекс отладки по п.1, отличающийся тем, что пульт управления содержит регистр адреса и регистр данных, первую и вторую схемы сравнения, регистр кода адреса, регистр кода данных, элемент ИЛИ, триггер-формирователь, счетчик контрольного времени и группу приемопередатчиков, подключенную с одной стороны к первой магистральной шине, являющейся одноименной шиной комплекса отладки, а с другой стороны подключенную совместно с регистром кода адреса, регистром кода данных и счетчиком контрольного интервала и триггером-формирователем ко второй магистральной шине, являющейся одноименной шиной комплекса отладки, причем выход регистра адреса подключен к первому входу первой схемы сравнения, ко второму входу которой подключен выход регистра кода адреса, а выход регистра кода данных подключен к второму входу второй схемы сравнения, выход которой и выход первой схемы сравнения подключены к одноименным входам элемента ИЛИ, к третьему входу которого подключен выход счетчика контрольного времени, при этом выход элемента ИЛИ подключен к входу триггера-формирователя, выход которого является управляющим выходом пульта управления, у которого синхронизирующий вход подключен к синхронизирующим входам регистров адреса, данных и триггера-формирователя, выход которого является выходом пульта управления.

4. Комплекс отладки по п.1, отличающийся тем, что каждый имитатор содержит блок связи с ЭВМ, вход которого является входом имитатора, а выход подключен к входам запоминающего устройства и программируемого контроллера обмена, подключенного двунаправленной шиной к запоминающему устройству, а выходом - к буферному регистру, выход которого является выходом имитатора.

5. Комплекс отладки по п.2, отличающийся тем, что формирователь синхроимпульсов содержит задающий генератор, n последовательно соединенных триггеров, образующих сдвиговый регистр, k триггеров привязки, элемент ИЛИ, триггер, элемент И и инвертор, выход которого подключен к синхронизирующим входам триггеров сдвигового регистра, а вход подключен к выходу задающего генератора и первому входу элемента И, ко второму входу которого подключен выход триггера, а выход элемента И подключен ко входу первого триггера сдвигового регистра, у которого выход последнего n-го триггера подключен к стробирующему входу триггера, к запускающему входу которого подключен выход элемента ИЛИ, к входам которого подключены выходы k триггеров привязки, стробирующие входы которых подключены к выходам первых k триггеров сдвигового регистра, а информационные входы подключены к управляющему входу формирователя, являющегося управляющим входом управляющей вычислительной машины.

| Экономайзер | 0 |

|

SU94A1 |

| Велосипед | 1984 |

|

SU1234277A2 |

| СПОСОБ ПРОИЗВОДСТВА И СОПРОВОЖДЕНИЯ ИНДИВИДУАЛЬНОГО ПРОГРАММНОГО ПРОДУКТА - ТЕХНОЛОГИЯ "ESC-M" | 2002 |

|

RU2195016C2 |

| Устройство для отладки программ | 1988 |

|

SU1624461A1 |

Авторы

Даты

2012-04-20—Публикация

2010-08-05—Подача