2. Устройство по п. 1, отличающееся тем, что блок памяти содержит элемент з.адержки, элемент сравнения, элемент свертки, регистр и накопитель, вход которого соединен с информационным входом блока памяти, первый выход - с входом элемента свертки и первым входом регистра, второй выход - с первым входом элемента сравнения, второй, третий входы и выход которого соединены соответственно с выходом элемента свертки, входом запрета кон роля и контрольным выходом блока памяти, вход обращения которого соединен с входом элемента задержки, первьй ыход которого соединен с выходом обращения блока памяти, а второй выход - с в торым входом регистра, выход которого являет ся информационным выходом блока памяти.

3, Устройство по п. 1, о т л и чающееся тем, что блок управления содержит элемент И, счетчик и два триггера, первые и вторые входы которых являются соответственно входами контроля и обращения блока управления, первый управляющий выход и выход запрета контроля которого соединены с первьм и вторым выходами первого триггера,, а второй управляющий выход - с выходом второго триггера и первым входом элемента И, второй вход которого соединен с синхровходом блока памяти и первым входом счетчика, а выхбд - с вторым входом счетчика, выход которого соединен с третьим входом второго триг.гера,.

| название | год | авторы | номер документа |

|---|---|---|---|

| Логический анализатор | 1987 |

|

SU1476474A1 |

| Устройство для сбора данных о работе ЭВМ | 1982 |

|

SU1121679A1 |

| Устройство для сопряжения ЭВМ с объектами управления | 1986 |

|

SU1401469A1 |

| Микропрограммный процессор | 1987 |

|

SU1553984A1 |

| Устройство для контроля микропроцессорной системы | 1987 |

|

SU1474650A2 |

| Устройство обмена данными | 1988 |

|

SU1649556A1 |

| Динамическое запоминающее устройство с восстановлением информации | 1989 |

|

SU1689990A1 |

| Динамическое запоминающее устройство | 1987 |

|

SU1474739A1 |

| УСТРОЙСТВО ДЛЯ ВИЗУАЛЬНОГО КОНТРОЛЯ ИСПОЛНЕНИЯ ПРОГРАММ | 1991 |

|

RU2012044C1 |

| ИМИТАТОР СИГНАЛОВ УПРАВЛЕНИЯ ПОЗИЦИОНИРОВАНИЕМ МАГНИТНЫХ ГОЛОВОК ОТНОСИТЕЛЬНО МАГНИТНЫХ ДИСКОВ | 1991 |

|

RU2017239C1 |

1. РЕЗЕРВИРОВАННОЕ ВЬИИСЛИТЕЛЬНОЕ УСТРОЙСТВО, содержащее два блока памяти и процессор, информационный выход и выход обращения которого соединены с одноименными входами блоков памяти, информационные выходы которых через мультиплексор подклю/ -. / ,..,.-,., ..:,. -liMS ;.; / .%. / чены к информационному входу процессора, отличающееся тем, что, с целью повышения быстродействия, в него введены генератор импульсов, блок запрета и блок управления, вход контроля, вход обращения и выход запрета контроля которого соединены с . одноименными выходами и входом первого блока памяти, первый и второй управляющие выходы - с соответствующими входами мультиплексора и блока запрета, а синхровход - с первым выходом генератора импульсов, второй выход которого соединен с соответствздащим синхровходом блока запрета, выход которого соединен с синхровходом процессора.

Изобретение относится к вычислительной технике и может быть использовано в системах с повьшенными требованиями к надежности и быстродействию.

Цель изобретения - повьшение быстродействия устройства.

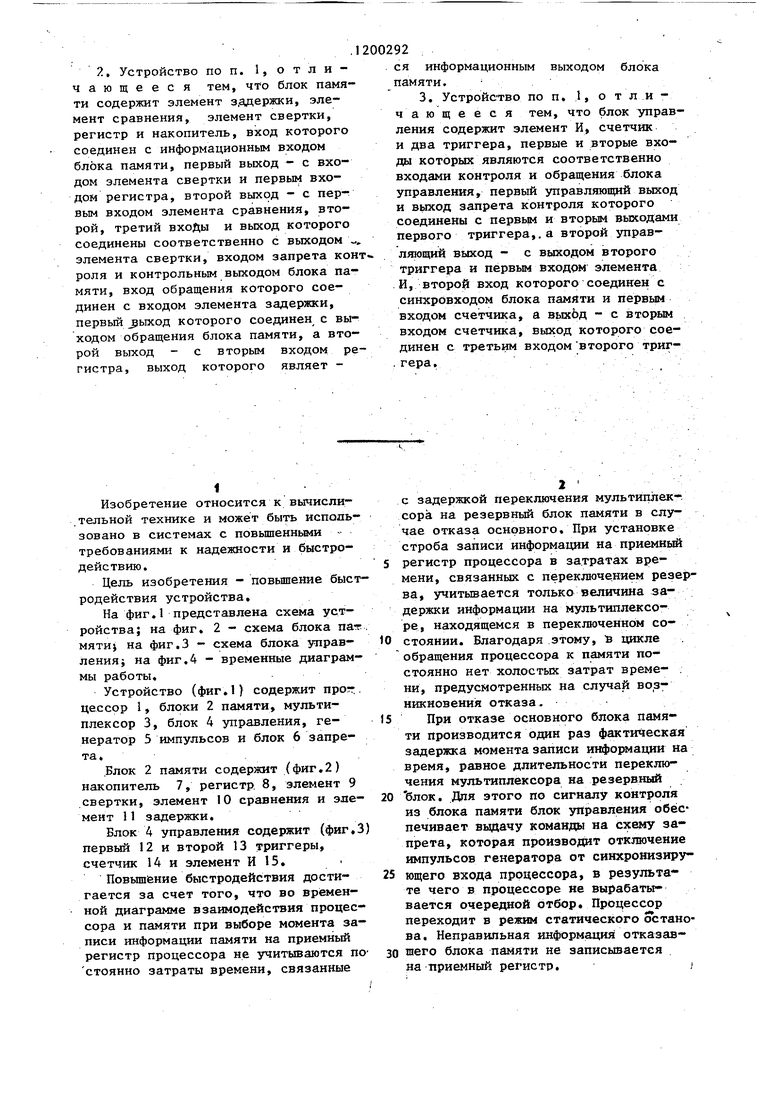

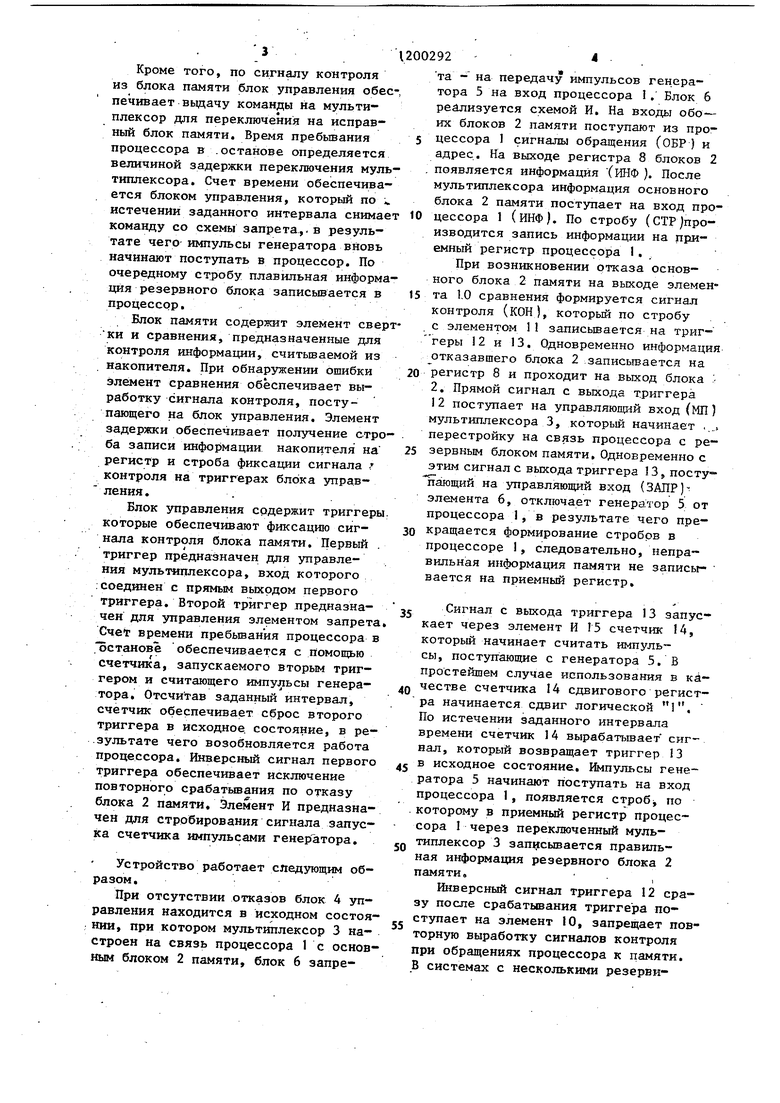

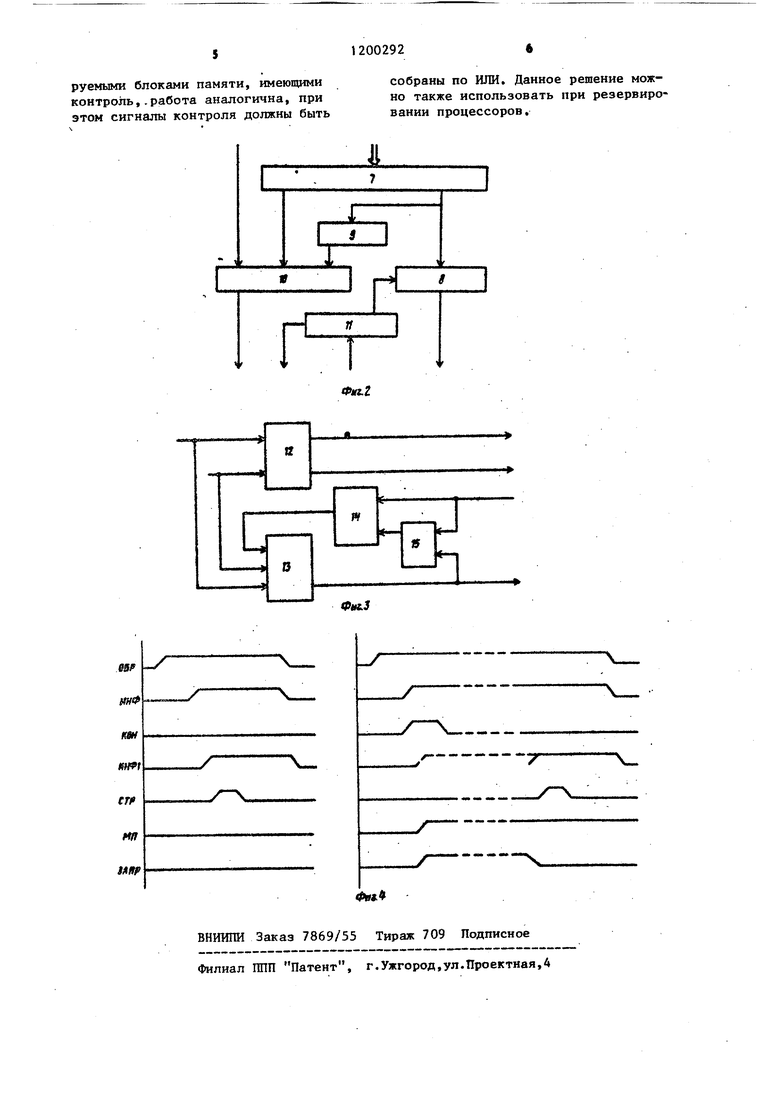

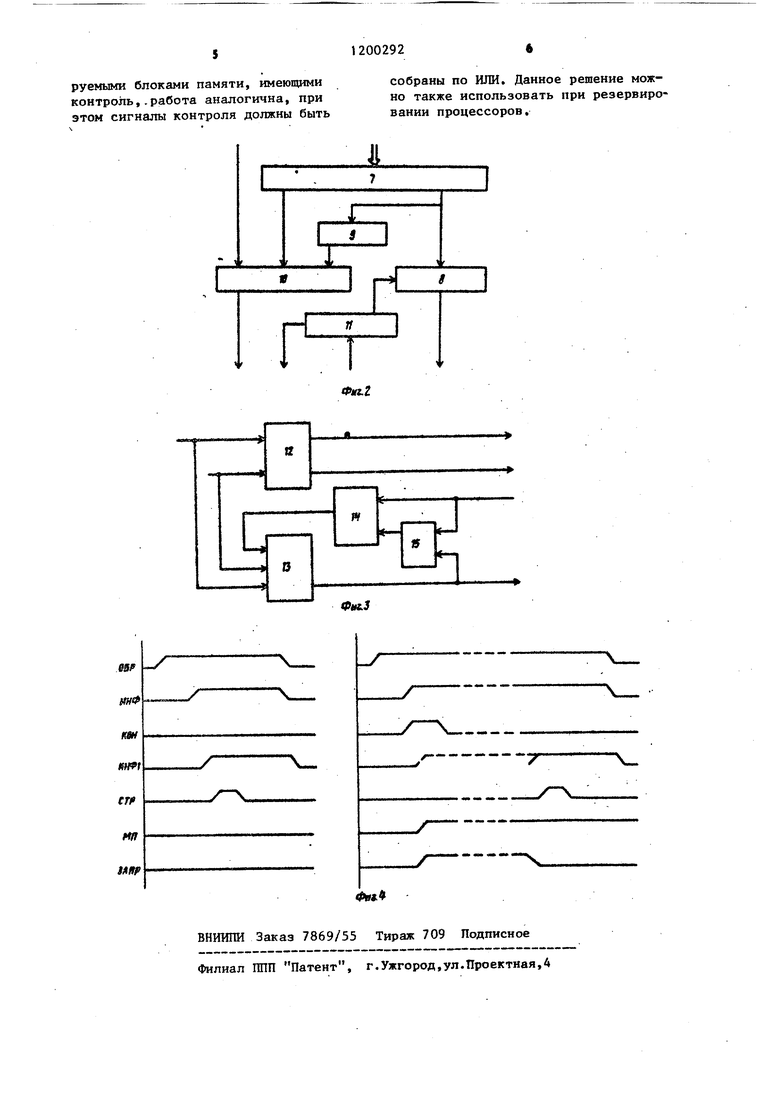

На фиг,I представлена схема устройства; на фиг, 2 - схема блока пат мяти; на фиг.З - схема блока управления; на фиг,4 - временные диаграммы работы.

Устройство (фиг,1) содержит прогт цессор 1, блоки 2 памяти, мультиплексор 3, блок 4 управления, генератор 5 импульсов и блок 6 запрета,

Блок 2 памяти содержит (фиг,2) накопитель 7, регистр. 8, элемент 9 свертки, элемент 10 сравнения и элемент 11 задержки.

Блок 4 управления содержит (фиг,3 первый 12 и второй 13 триггеры, счетчик 14 и элемент И 15.

Повыш1ение быстродействия достигается за счет того, что во временной диаграмме взаимодействия процессора и памяти при выборе момента записи информации памяти на приемный регистр процессора не учитываются постоянно затраты времени, связанные

с задержкой переключения мультицлексора на резервный блок памяти в случае отказа основного. При установке строба записи информации на приемный регистр процессора в затратах времени, связанных с переключением резерва, учитывается только величина задержки информации на мультиплексоре, находящемся в переключенном состоянии. Благодаря этому, в цикле обращения процессора к памяти постоянно нет холостых затрат време- . ни, предусмотренных на случай возникновения отказа.

При отказе основного блока памяти производится один раз фактическая задержка момента записи информации на время, равное длительности переключения мультиплексора на резервный

блок. Для этого по сигналу контроля из блока памяти блок управления обеспечивает выдачу команды на схему запрета , которая производит отключение импульсов генератора от синхронизирующего входа процессора, в результате чего в процессоре не вырабатывается очередной отбор. Процессор переходит в режим статического останова. Неправильная информация отказавшего блока памяти не записывается на приемный регистр,i Кроме того, по сигналу контроля из блока памяти блок управления обес печивает вьщачу команды на мультиплексор для переключения на исправный блок памяти. Время пребьшания процессора в .останове определяется величиной задержки переключения муль типлексора. Счет времени обеспечивается блоком управления, который по :. истечении заданного интервала снимае команду со схемы запрета,, в результате чего импульсы генератора вновь начинают поступать в процессор. По очередному стробу плавильная информа ция резервного блока записывается в процессор. Блок памяти содержит элемент свер ки и сравнения, предназначенные для контроля информации, считьюаемой из накопителя. При обнаружении ошибки элемент сравнения обеспечивает выработку сигнала контроля, поступающего на блок управления. Элемент задержки обеспечивает получение стро ба записи информации накопителя на регистр и строба фиксации сигнала г контроля на триггерах блока управления. . Блок управления содержит триггеры которые обеспечивают фиксацию сигнала контроля блока памяти. Первый . триггер предназначен для управления мультиплексора, вход которого .соединен с прямым вькрдом первого триггера. Второй Tpiwrrep предназначен для управления злементом запрета Счет времени пребьшания процессора в останове обеспечивается с помощью счетчика, запускаемого вторым триггером и считающего импульсы генератора. Отсчитав заданный интервал, счетчик обеспечивает сброс второго триггера в исходное, состояние, в ре.зультате чего возобновляется работа процессора. Инверсный сигнал первого триггера обеспечивает исключение повторного срабатывания по отказу блока 2 памяти. Элемент И предназначен для стробирования сигнала запуска счетчика импульсами генератора. Устройство работает следующим образом. При отсутствии отказов блок 4 управления находится в исходном состоя нии, при котором мультиплексор 3 настроен на связь процессора 1 с основ ным блоком 2 памяти, блок 6 запре92- на передачу импульсов генератора 5 на вход процессора I , Блок 6 реализуется схемой И. На входы обо- их блоков 2 памяти поступают из процессора I сигналы обращения (ОБР ) и адрес. На выходе регистра 8 блоков 2 появляется информация (ШФ ). После мультиплексора информация основного блока 2 памяти поступает на вход процессора 1 (ИНФ). По стробу (CTPjnpoизводится запись информации на приемный регистр процессора 1. При возникновении отказа основного блока 2 памяти на выходе элемента 1.0 сравнения формируется сигнал контроля (кон), который по стробу с элементом 11 записьюается на триггеры 12 и 13. Одновременно информация отказавшего блока 2 записывается на регистр 8 и проходит на выкод блока 2. Прямой сигнал с выхода триггера 12 постзшает на управляющий вход (МП) мультиплексора 3, который начинает ,. перестройку на связь процессора с ре- зервным блоком памяти. Одновременно с этим сигнал с выхода триггера 13, поступающий на управляющий вход (ЗАПР) элемента 6, отключает генератор 5 от процессора 1, в результате чего прекращается формирование стробов в процессоре 1, следовательно, неправильная информация памяти не записывается на приемный регистр. Сигнал с выхода триггера 13 запускает через элемент И 15 счетчик 14, который начинает считать импульсы, поступающие с генератора 5. В простейшем случае использования в кй- честве счетчика 14 сдвигового регистра начинается сдвиг логической 1. По истечении заданного интервала времени счетчик 14 вырабатывает сигнал, который возвращает триггер 13 в исходное состояние. Импульсы генератора 5 начинают поступать на вход процессора 1, появляется строб по которому в приемный регистр процессора I через переключенный мультиплексор 3 зап1 сывается правильная информация резервного блока 2 памяти. . , Инверсный сигнал триггера 12 сразу после срабатьюания триггера поступает на элемент 10, запрещает повторную выработку сигналов контроля при обращениях процессора к памяти. В системах с несколькими резервируемыми блоками памяти, имеющими контроль,.работа аналогична, при этом сигналы контроля должны быть

собраны по ИЛИ. Данное решение можно также использовать при резервировании процессоров.

гМ

Авторы

Даты

1985-12-23—Публикация

1983-02-08—Подача