Изобретение относится к области вычислительной техники и может использоваться в высокопроизводительных микропроцессорных системах.

Известно устройство предсказания команд условного перехода, входящее в состав буфера инструкций гибридного микропроцессора, включающего центральный процессор, системный контроллер, внешнюю память, двухуровневую кэш-память (Патент RU №2359315, кл. G06F 9/30, опубл. 20.06.2009 г.).

Недостатком описанного блока является недостаточная производительность системы в связи с низкой точностью статического предсказания команд условного перехода.

Известен также блок динамического предсказания команд условного перехода микропроцессора, включающий сдвиговый регистр глобальной истории переходов, регистр программного счетчика, логический элемент «исключающее ИЛИ», память предсказания и устройство выбора предсказания (Заявка на изобретение US №20100169626, кл. G06F 9/38, опубл. 01.07.2010 г.).

Недостатком описанного выше устройства является недостаточная точность предсказания, которое формирует устройство выбора предсказания.

Наиболее близким по технической сути и достигаемому техническому результату является устройство динамического предсказания команд условного перехода микропроцессора, состоящее из сдвигового регистра глобальной истории переходов, регистра программного счетчика, регистра режима работы процессора, логического элемента «исключающее ИЛИ», памяти глобального предсказания, памяти двухбитового предсказаний и мультиплексора выбора итогового предсказания. (Заявка на изобретение US 20080215866, кл. G06F 9/38, опубл. 04.09.2008 г.).

Недостатком описанного выше блока является недостаточная точность предсказания команд условного перехода при параллельном выполнении прикладных программ (когда их переключение происходит без изменения режима работы процессора).

Технический результат от использования данного изобретения состоит в повышении производительности микропроцессора путем повышения точности предсказания направления условных переходов.

Указанный технический результат достигается тем, что в устройстве динамического предсказания команд условного перехода, состоящем из сдвигового регистра глобальной истории переходов, регистра программного счетчика, регистра режима работы процессора, логического элемента «исключающее ИЛИ», памяти глобального предсказания, памяти двухбитового предсказаний и мультиплексора выбора итогового предсказания, согласно изобретению дополнительно содержит регистр идентификатора адресного пространства процесса, память истории переходов процесса, логический элемент «исключающее ИЛИ», память локального предсказания процесса, регистр адреса управляющей памяти предсказания процесса, управляющую память предсказания процесса и мультиплексор выбора промежуточного предсказания процесса, при этом мультиплексор выбора промежуточного предсказания процесса связан с памятью двухбитового предсказания, управляющей памятью предсказания процесса, связанной с регистром адреса управляющей памяти предсказания процесса, который объединяет значения регистра идентификатора адресного пространства процесса и регистра программного счетчика, и памятью локального предсказания процесса, которая связана с памятью истории переходов процесса, связанной с регистром идентификатора адресного пространства процесса, и регистром программного счетчика логическим элементом «исключающее ИЛИ».

Использование механизма выбора промежуточного предсказания позволяет накапливать историю эффективности предсказания разных схем предсказания и использовать для каждой конкретной команды условного перехода ту схему предсказания, которая дает для данной обрабатываемой команды наибольшую точность предсказания.

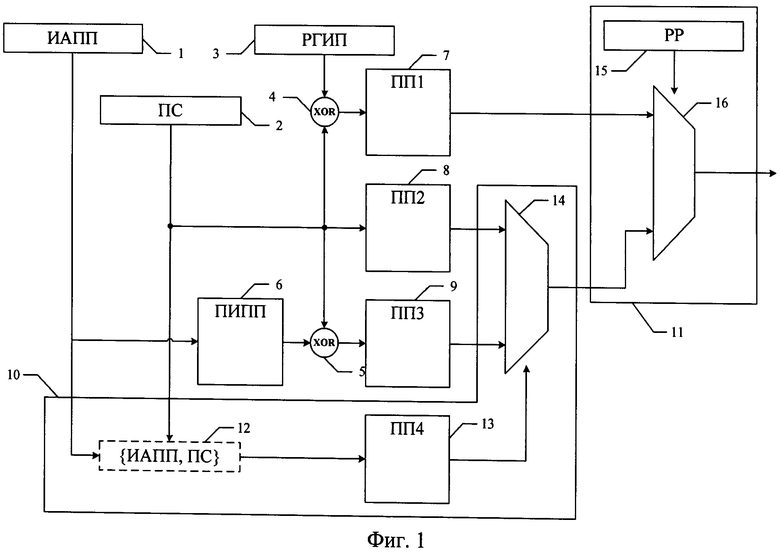

Изобретение поясняется фиг.1, на которой изображена блок-схема динамического предсказания команд условного перехода.

Блок динамического предсказания состоит из регистра идентификатора адресного пространства процесса (ИАПП) 1, программного счетчика (ПС) 2, сдвигового регистра глобальной истории переходов (РГИП) 3, логических элементов «исключающее ИЛИ» (XOR) 4 и 5, памяти истории переходов процесса (ПИПП) 6, памяти глобального предсказания (ПП1) 7, памяти двухбитового предсказания (ПП2) 8 и памяти локального предсказания процесса (ПП3) 9. Также двух устройств выбора предсказаний - первое (для выбора промежуточного предсказания) 10 и второе (для выбора итогового предсказания) 11. Первое устройство выбора промежуточного предсказания 10 включает в свой состав регистр адреса управляющей памяти предсказания процесса 12, управляющую память предсказания процесса (ПП4) 13 и мультиплексор выбора промежуточного предсказания процесса 14. Второе устройство выбора итогового предсказания 11 содержит в себе статусный регистр режима работы процессора (РР) 15 и мультиплексор выбора итогового предсказания 16.

Механизм предсказания с использованием данных регистра идентификации адресного пространства процесса (ИАПП) 1 работает следующим образом.

При декодировании команды условного перехода по адресу, содержащемуся в регистре программного счетчика (ПС) 2, данные регистра идентификации адресного пространства процесса (ИАПП) 1 используются как адрес для памяти истории переходов процесса (ПИПП) 6, и одновременно с этим объединяют часть своих бит с частью бит регистра программного счетчика (ПС) 2, записывая полученный набор бит в регистр адреса управляющей памяти предсказания процесса 12. Данные регистра адреса управляющей памяти предсказания процесса 12 адресуют управляющую память предсказания процесса (ПП4) 13.

Полученные из памяти истории переходов процесса (ПИПП) 6 данные объединяются с данными регистра программного счетчика (ПС) 2 логическим элементом «исключающее ИЛИ» 5, формируя адрес для памяти локального предсказания процесса (ПП3) 9.

Программный счетчик (ПС) 2 используется как:

1. адрес для памяти двухбитового предсказания (ПП2) 8,

2. вход элемента «исключающее ИЛИ» 4, который объединяет его со значением сдвигового регистра глобальной истории перехода (РГИП) 3, для получения адреса памяти глобального предсказания (ПП1) 7,

3. вход элемента «исключающее ИЛИ» 5, который объединяет его с данными, считанными из памяти истории переходов процесса (ПИПП) 6, для получения адреса памяти локального предсказания процесса (ПП3) 9.

Предсказание инструкции ветвления для текущего процесса формируется из выходов данных памяти двухбитового предсказания (ПП2) 8 и памяти локального предсказания процесса (ПП3) 9, которые выбираются мультиплексором выбора промежуточного предсказания процесса 14, используя для управления значение выхода данных управляющей памяти предсказания процесса (ПП4) 13. Выход мультиплексора выбора промежуточного предсказания процесса 14 подается в устройство выбора итогового предсказания 11, где мультиплексор выбора итогового предсказания 16 выбирает или выход данных памяти глобального предсказания (ПП1) 7 или выход устройства промежуточного предсказания 10, используя для управления данные статусного регистра режима процессора (РР) 15. Полученный на выходе устройства выбора итогового предсказания 11 двухбитовый код стандартным способом используется в процессоре для определения направления перехода инструкций ветвления. Описанный блок динамического предсказания позволяет увеличить точность предсказания направления перехода команд условного перехода по сравнению с известными блоками динамического предсказания и, как следствие, повысить производительность микропроцессорной системы в целом.

| название | год | авторы | номер документа |

|---|---|---|---|

| ПРОЦЕССОР С УСОВЕРШЕНСТВОВАННЫМ ПРЕДСКАЗАТЕЛЕМ ПЕРЕХОДА | 2024 |

|

RU2832441C1 |

| ПРЕДСТАВЛЕНИЕ ПЕРЕХОДОВ ЦИКЛА В РЕГИСТРЕ ПРЕДЫСТОРИИ ПЕРЕХОДОВ С ПОМОЩЬЮ МНОЖЕСТВА БИТ | 2007 |

|

RU2447486C2 |

| МИКРОПРОЦЕССОР ГИБРИДНЫЙ | 2007 |

|

RU2359315C2 |

| Устройство обработки информации | 1989 |

|

SU1631549A1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ ПАМЯТЬЮ | 1993 |

|

RU2037874C1 |

| Микропрограммное устройство управления | 1986 |

|

SU1481759A1 |

| СИСТЕМА ДЛЯ ПРОГРАММНОГО УПРАВЛЕНИЯ ТЕХНОЛОГИЧЕСКИМ ОБОРУДОВАНИЕМ | 2000 |

|

RU2189623C2 |

| МУЛЬТИКОНТРОЛЛЕР РАСПРЕДЕЛЯЕМОЙ ПАМЯТИ | 2014 |

|

RU2550555C1 |

| ТРАНСЛЯЦИЯ АДРЕСОВ ВВОДА-ВЫВОДА В АДРЕСА ЯЧЕЕК ПАМЯТИ | 2010 |

|

RU2547705C2 |

| ОПРЕДЕЛЕНИЕ ФОРМАТОВ ТРАНСЛЯЦИИ ДЛЯ ФУНКЦИЙ АДАПТЕРА ВО ВРЕМЯ ВЫПОЛНЕНИЯ | 2010 |

|

RU2556418C2 |

Устройство динамического предсказания команд условного перехода микропроцессора относится к области вычислительной техники и может использоваться в высокопроизводительных микропроцессорных системах. Технический результат состоит в повышении производительности микропроцессора путем повышения точности предсказания направления условных переходов. Устройство состоит из сдвигового регистра глобальной истории переходов, регистра программного счетчика, регистра режима работы процессора, логического элемента «исключающее ИЛИ», памяти глобального предсказания, памяти двухбитового предсказаний, мультиплексора выбора итогового предсказания, регистра идентификатора адресного пространства процесса, памяти истории переходов процесса, логического элемента «исключающее ИЛИ», памяти локального предсказания процесса, регистра адреса управляющей памяти предсказания процесса, управляющей памяти предсказания процесса и мультиплексора выбора промежуточного предсказания процесса. 1 ил.

Устройство динамического предсказания команд условного перехода микропроцессора, состоящее из сдвигового регистра глобальной истории переходов, регистра программного счетчика, регистра режима работы процессора, логического элемента «исключающее ИЛИ», памяти глобального предсказания, памяти двухбитового предсказаний и мультиплексора выбора итогового предсказания, отличающееся тем, что устройство дополнительно содержит регистр идентификатора адресного пространства процесса, память истории переходов процесса, логический элемент «исключающее ИЛИ», память локального предсказания процесса, регистр адреса управляющей памяти предсказания процесса, управляющую память предсказания процесса и мультиплексор выбора промежуточного предсказания процесса, при этом мультиплексор выбора промежуточного предсказания процесса связан с памятью двухбитового предсказания, управляющей памятью предсказания процесса, связанной с регистром адреса управляющей памяти предсказания процесса, который объединяет значения регистра идентификатора адресного пространства процесса и регистра программного счетчика, и памятью локального предсказания процесса, которая связана с памятью истории переходов процесса, связанной с регистром идентификатора адресного пространства процесса, и регистром программного счетчика логическим элементом «исключающее ИЛИ».

| US 20080215866 A1, 04.09.2008 | |||

| Приспособление для суммирования отрезков прямых линий | 1923 |

|

SU2010A1 |

| МИКРОПРОЦЕССОР ГИБРИДНЫЙ | 2007 |

|

RU2359315C2 |

| СИСТЕМА ДЛЯ ПРОГРАММНОГО УПРАВЛЕНИЯ ТЕХНОЛОГИЧЕСКИМ ОБОРУДОВАНИЕМ | 2000 |

|

RU2189623C2 |

Авторы

Даты

2014-01-10—Публикация

2012-07-20—Подача