Предлагаемое изобретение относится к цифровой вычислительной технике и может быть использовано при построении схем, использующих функцию ИСКЛЮЧАЮЩЕЕ-ИЛИ - многоразрядных сумматоров, схем четности/нечетности, счетных регистров и многих других быстродействующих многоразрядных электронных устройств.

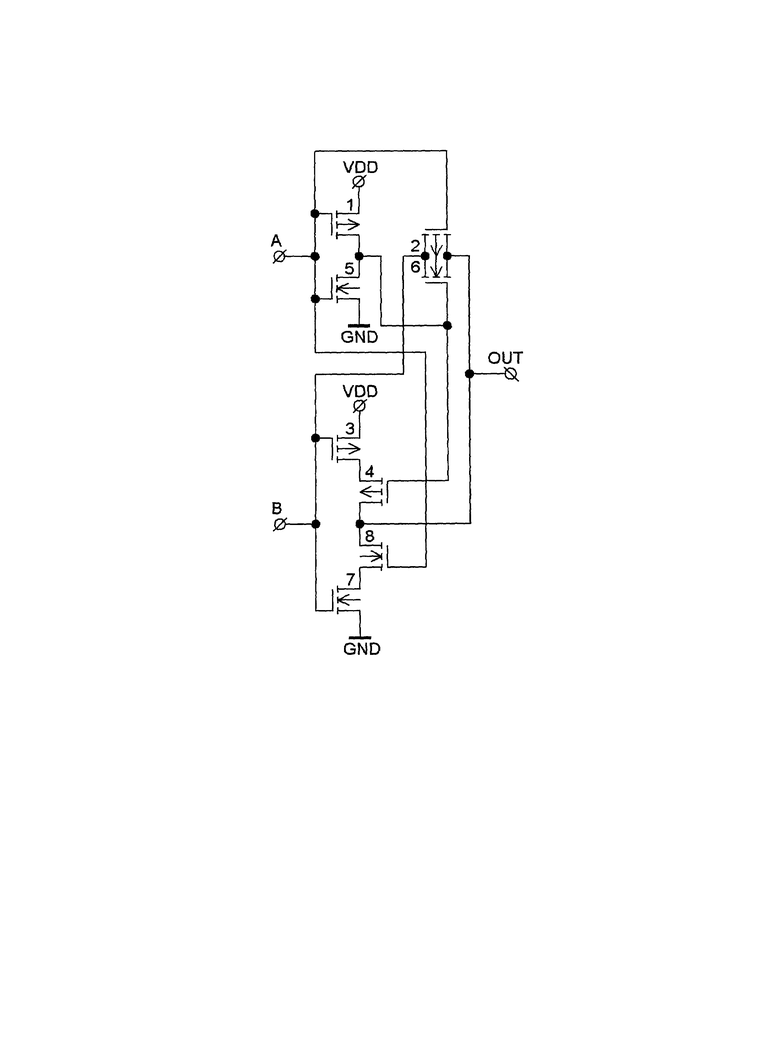

Известна Схема вентиля ИСКЛЮЧАЮЩЕЕ-ИЛИ, использующая передаточные вентили (XOR gate circuit using TG) [1] (p. 652, Fig. 7.5), построенная на 8-ми МОП транзисторах, образующих два КМОП инвертора и два полно-уровневых КМОП передаточных вентиля (Transmission Gates, TGs).

Данная Схема вентиля ИСКЛЮЧАЮЩЕЕ-ИЛИ [1] содержит входы а и b и выход out, шины источника питания высокого и низкого уровней напряжения, МОП транзисторы P-типа с первого по четвертый и N-типа с пятого по восьмой.

Недостатком известной Схемы вентиля ИСКЛЮЧАЮЩЕЕ-ИЛИ [1] является низкое быстродействие, вызванное наличием больших значений встроенных паразитных узловых емкостей на выходе инвертора в цепи прохождения сигнала от входа b до выхода out через передаточный вентиль, подсоединенный к выходу КМОП инвертора, формирующего инверсный сигнал b.

Кроме того, динамический ток потребления известной Схемы вентиля ИСКЛЮЧАЮЩЕЕ-ИЛИ [1] увеличивается из-за повышенного времени переходного процесса перезаряда данного узла, что приводит к дополнительному перегреву элементов схемы и снижает общую надежность схемы.

Задачей предлагаемого изобретения является повышение быстродействия известной Схемы вентиля ИСКЛЮЧАЮЩЕЕ-ИЛИ [1] и повышение ее надежности за счет уменьшения динамического тока потребления.

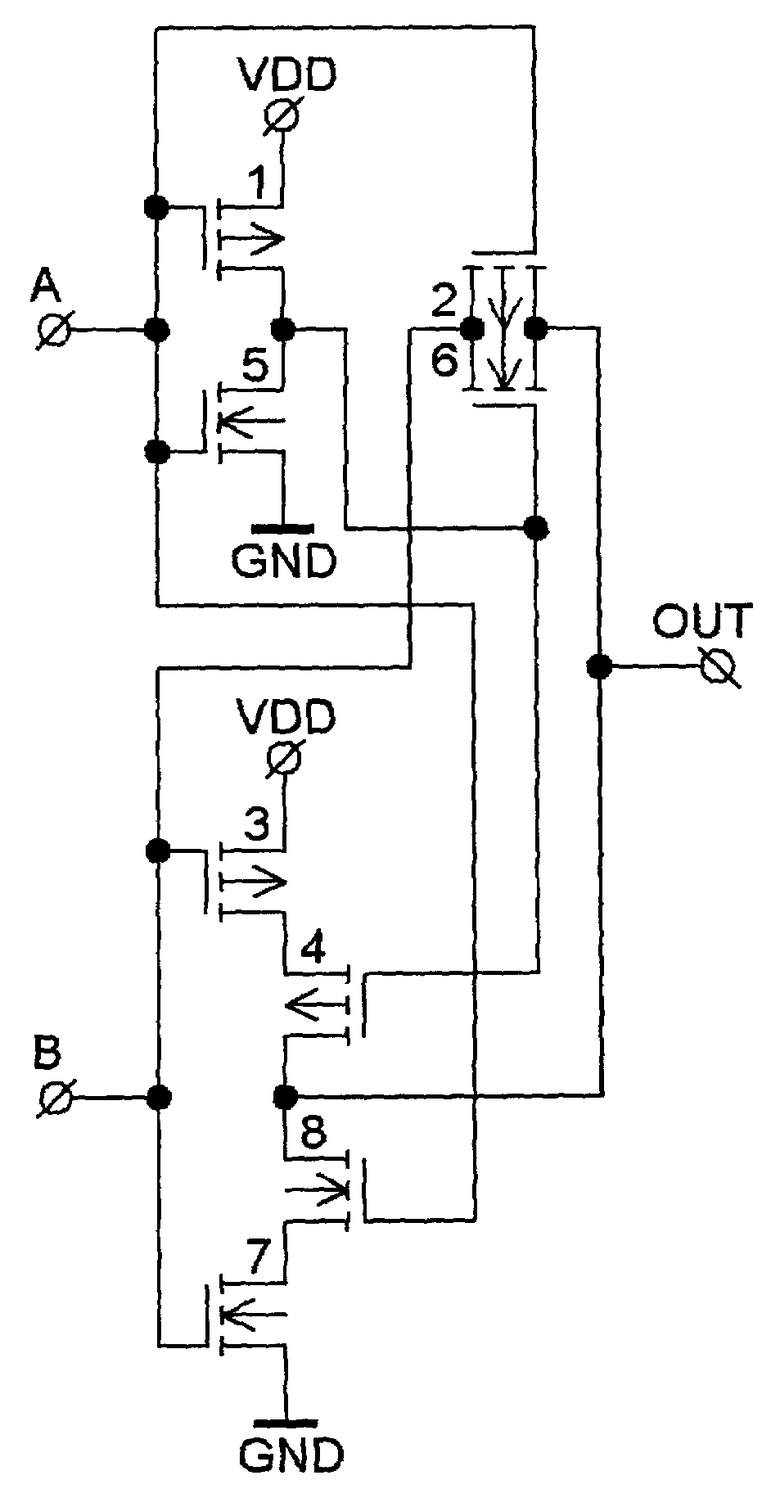

Поставленная задача достигается тем, что, в отличие от известной Схемы вентиля ИСКЛЮЧАЮЩЕЕ-ИЛИ [1], содержащей МОП транзисторы P-типа с первого по четвертый и N-типа с пятого по восьмой, вход сигнала А, соединенный с затворами транзисторов первого, второго, пятого и восьмого, причем стоки первого и пятого транзисторов соединены между собой и соединены с затворами транзисторов четвертого и шестого, вход сигнала В, соединенный с затворами транзисторов третьего и седьмого и истоками транзисторов второго и шестого, шину источника питания высокого уровня напряжения VDD, соединенную с истоками транзисторов первого и третьего, шину источника питания низкого уровня напряжения GND, соединенную с истоками транзисторов пятого и седьмого, выход OUT, соединенный со стоками транзисторов второго, четвертого, шестого и восьмого, в предложенном Логическом вентиле ИСКЛЮЧАЮЩЕЕ-ИЛИ сток третьего транзистора соединен с истоком четвертого, а сток седьмого - с истоком восьмого.

Таким образом, в предлагаемом техническом решении Логического вентиля ИСКЛЮЧАЮЩЕЕ-ИЛИ, в отличие от известной Схемы вентиля ИСКЛЮЧАЮЩЕЕ-ИЛИ [1], отсутствует физическое соединение стоков комплементарной пары МОП транзисторов третьего и седьмого между собой и истоками ключевых МОП транзисторов четвертого и восьмого, которое увеличивает емкость данного узла и тем самым снижает быстродействие Схемы вентиля ИСКЛЮЧАЮЩЕЕ-ИЛИ [1] из-за увеличения длительности переходного процесса переключения этого узла. Поэтому быстродействие в предлагаемом Логическом вентиле ИСКЛЮЧАЮЩЕЕ-ИЛИ выше быстродействия известной Схемы вентиля ИСКЛЮЧАЮЩЕЕ-ИЛИ [1].

Кроме того, повышение быстродействия схемы за счет уменьшения длительности переходного процесса приводит к уменьшению времени протекания сквозного тока между шинами источника питания высокого VDD и низкого GND уровней, снижению величины динамического тока потребления схемы и уменьшению дополнительного перегрева элементов схемы, что повышает общую надежность предлагаемого Логического вентиля ИСКЛЮЧАЮЩЕЕ-ИЛИ.

На Рисунке приведена схема предлагаемого Логического вентиля ИСКЛЮЧАЮЩЕЕ-ИЛИ.

Предлагаемый Логический вентиль ИСКЛЮЧАЮЩЕЕ-ИЛИ содержит транзисторы P-типа с первого по четвертый 1-4 и N-типа с пятого по восьмой 5-8, вход сигнала А, соединенный с затворами транзисторов первого 1, второго 2, пятого 5 и восьмого 8, причем стоки первого 1 и пятого 5 транзисторов соединены между собой и соединены с затворами транзисторов четвертого 4 и шестого 6, вход сигнала В, соединенный с затворами транзисторов третьего 3 и седьмого 7 и истоками транзисторов второго 2 и шестого 6, шину источника питания высокого уровня напряжения VDD, соединенную с истоками транзисторов первого 1 и третьего 3, шину источника питания низкого уровня напряжения GND, соединенную с истоками транзисторов пятого 5 и седьмого 7, выход OUT, соединенный со стоками транзисторов второго 2, четвертого 4, шестого 6 и восьмого 8, в котором сток третьего 3 транзистора соединен с истоком четвертого 4, а сток седьмого 7 - с истоком восьмого 8.

Предлагаемый Логический вентиль ИСКЛЮЧАЮЩЕЕ-ИЛИ представляет собой логическую схему комбинационного типа, предназначенную для формирования логической функции ИСКЛЮЧАЮЩЕЕ-ИЛИ, и работает согласно нижеприведенной таблице истинности.

В исходном состоянии (Комбинация №1) на входы А и В поступает напряжение низкого уровня GND, которое соответствует напряжению низкого логического уровня «0» таблицы истинности. При этом транзисторы P-типа 1, 2 и 3 открываются, а N-типа 5, 7 и 8 закрываются. Через открытый транзистор 1 на затворы транзисторов P-типа 4 и N-типа 6 поступает напряжение высокого уровня VDD, которое соответствует напряжению высокого логического уровня «1» таблицы истинности, в результате чего транзистор 6 открывается, а транзистор 4 - закрывается. Поэтому с входа В на выход OUT через открытые транзисторы 2 и 6 поступает напряжение низкого логического уровня «0», которое соответствует значению таблицы истинности комбинации №1.

Если на вход А поступает напряжение высокого логического уровня «1», а на вход В напряжение низкого логического уровня «0» (Комбинация №2), то транзисторы P-типа 1 и 2 и транзистор N-типа 7 закрываются, а транзистор P-типа 3 и транзисторы N-типа 5 и 8 открываются. Через открытый транзистор 5 на затворы транзисторов P-типа 4 и N-типа 6 поступает напряжение низкого логического уровня «0», в результате чего транзистор 4 открывается, а транзистор 6 закрывается. Поэтому на выход OUT через открытые транзисторы 3 и 4 поступает напряжение высокого логического уровня «1», которое соответствует значению таблицы истинности комбинации №2.

Если на вход А поступает напряжение низкого логического уровня «0», а на вход В напряжение высокого логического уровня «1» (Комбинация №3), то транзисторы P-типа 1 и 2 и транзистор N-типа 7 открываются, а транзистор P-типа 3 и транзисторы N-типа 5 и 8 закрываются. Через открытый транзистор 1 на затворы транзисторов P-типа 4 и N-типа 6 поступает напряжение высокого логического уровня «1», вследствие чего транзистор 4 закрывается, а транзистор 6 открывается. Поэтому с входа В на выход OUT через открытые транзисторы 2 и 6 поступает напряжение высокого логического уровня «1», которое соответствует значению таблицы истинности комбинации №3.

Если на входы А и В поступает напряжение высокого логического уровня «1» (Комбинация №4), то транзисторы P-типа 1, 2 и 3 закрываются, а транзисторы N-типа 5, 7 и 8 открываются. Через открытый транзистор 5 на затворы транзисторов P-типа 4 и N-типа 6 поступает напряжение низкого логического уровня «0», в результате чего транзистор 6 закрывается, а транзистор 4 открывается. Поэтому напряжение шины источника питания низкого уровня GND, соответствующее напряжению низкого логического уровня «0», через открытые транзисторы 7 и 8 поступает на выход OUT. Таким образом данное состояние соответствует значениям таблицы истинности комбинации №4.

При возврате схемы в исходное состояние (Комбинация №1 таблицы истинности) на входы А и В поступает напряжение низкого логического уровня «0». При этом транзисторы P-типа 1, 2 и 3 открываются, а N-типа 5, 7 и 8 закрываются. Через открытый транзистор 1 на затворы транзисторов P-типа 4 и N-типа 6 поступает напряжение высокого логического уровня «1», в результате чего транзистор 6 открывается, а транзистор 4 закрывается. Поэтому с входа В на выход OUT через открытые транзисторы 2 и 6 поступает напряжение низкого логического уровня «0», которое соответствует значению таблицы истинности комбинации №1 и Логический вентиль ИСКЛЮЧАЮЩЕЕ-ИЛИ переходит в исходное состояние.

Так как в предложенном Логическом вентиле ИСКЛЮЧАЮЩЕЕ-ИЛИ физическое соединение стоков комплементарной пары МОП транзисторов третьего и седьмого между собой и истоками ключевых МОП транзисторов четвертого и восьмого отсутствует, то емкость данного узла существенно уменьшена. Поэтому длительность переходного процесса, связанная с перезарядом паразитных емкостей, уменьшена и быстродействие предлагаемого Логического вентиля ИСКЛЮЧАЮЩЕЕ-ИЛИ выше известной Схемы вентиля ИСКЛЮЧАЮЩЕЕ-ИЛИ [1].

Кроме того, повышение быстродействия схемы за счет уменьшения длительности переходного процесса приводит к уменьшению времени протекания сквозного тока между шинами источника питания высокого VDD и низкого GND уровней, снижению динамического тока потребления, уменьшению дополнительного перегрева элементов схемы и тем самым повышает общую надежность предлагаемого Логического вентиля ИСКЛЮЧАЮЩЕЕ-ИЛИ.

Таким образом, предлагаемый Логический вентиль ИСКЛЮЧАЮЩЕЕ-ИЛИ по сравнению с известной Схемой вентиля ИСКЛЮЧАЮЩЕЕ-ИЛИ [1] обладает более высоким быстродействием и надежностью.

Литература

1. Balaji, G.N. Combinational Circuits Using Transmission gate Logic for Power Optimization / G. Naveen Balaji, V. Aathira, K. Ambhikavathi, S. Geethiga, R. Havin // International Research J. of Eng. and Tech. - May 2016. - Vol.03, Issue 05. - ISO 9001: 2008 Certified Journal. - P. 649-654. - e-ISSN: 2395-0056, p-ISSN: 2395-0072 (Fig. 7.5, p. 652).

| название | год | авторы | номер документа |

|---|---|---|---|

| КМОП ЛОГИЧЕСКИЙ ВЕНТИЛЬ ИСКЛЮЧАЮЩЕЕ-ИЛИ | 2023 |

|

RU2814896C1 |

| ЭЛЕМЕНТ ВХОДНОГО РЕГИСТРА | 2022 |

|

RU2787930C1 |

| ЭЛЕМЕНТ ВХОДНОГО РЕГИСТРА | 2021 |

|

RU2771447C1 |

| ПРЕОБРАЗОВАТЕЛЬ УРОВНЯ НАПРЯЖЕНИЯ | 2017 |

|

RU2667798C1 |

| ПРЕОБРАЗОВАТЕЛЬ УРОВНЯ НАПРЯЖЕНИЯ | 2016 |

|

RU2604054C1 |

| ТРЁХВХОДОВОЙ КМОП ЛОГИЧЕСКИЙ ВЕНТИЛЬ ИСКЛЮЧАЮЩЕЕ ИЛИ/ИСКЛЮЧАЮЩЕЕ ИЛИ-НЕ | 2020 |

|

RU2761172C1 |

| ПРЕОБРАЗОВАТЕЛЬ УРОВНЯ НАПРЯЖЕНИЯ | 2018 |

|

RU2679186C1 |

| ПРЕОБРАЗОВАТЕЛЬ УРОВНЯ НАПРЯЖЕНИЯ | 2021 |

|

RU2756445C1 |

| ПРЕОБРАЗОВАТЕЛЬ УРОВНЯ НАПРЯЖЕНИЯ | 2020 |

|

RU2739487C1 |

| ЧЕТЫРЁХВХОДОВОЙ КМОП ЛОГИЧЕСКИЙ ВЕНТИЛЬ ИСКЛЮЧАЮЩЕЕ-ИЛИ/ИСКЛЮЧАЮЩЕЕ-ИЛИ-НЕ | 2022 |

|

RU2784457C1 |

Изобретение относится к цифровой вычислительной технике и может быть использовано при построении схем, использующих функцию ИСКЛЮЧАЮЩЕЕ-ИЛИ - многоразрядных сумматоров, схем четности/нечетности, счетных регистров и многих других быстродействующих многоразрядных электронных устройств. Техническим результатом изобретения является повышение быстродействия схемы вентиля ИСКЛЮЧАЮЩЕЕ-ИЛИ и повышение ее надежности за счет уменьшения динамического тока потребления. Логический вентиль ИСКЛЮЧАЮЩЕЕ-ИЛИ содержит шину питания высокого уровня напряжения VDD, шину питания низкого уровня напряжения GND, четыре МОП транзистора P-типа и четыре МОП транзистора N-типа, входы А и В и выход OUT. 1 ил., 1 табл.

Логический вентиль ИСКЛЮЧАЮЩЕЕ-ИЛИ, содержащий МОП транзисторы P-типа с первого по четвертый и N-типа с пятого по восьмой, вход сигнала А, соединенный с затворами транзисторов первого, второго, пятого и восьмого, причем стоки транзисторов первого и пятого соединены между собой и соединены с затворами транзисторов четвертого и шестого, вход сигнала В, соединенный с затворами транзисторов третьего и седьмого и истоками транзисторов второго и шестого, шину источника питания высокого уровня напряжения VDD, соединенную с истоками транзисторов первого и третьего, шину источника питания низкого уровня напряжения GND, соединенную с истоками транзисторов пятого и седьмого, выход OUT, соединенный со стоками транзисторов второго, четвертого, шестого и восьмого, отличающийся тем, что сток третьего транзистора соединен с истоком четвертого, а сток седьмого - с истоком восьмого.

| BALAJI G.N | |||

| Combinational Circuits Using Transmission gate Logic for Power Optimization // International Research J | |||

| of Eng | |||

| and Tech | |||

| Токарный резец | 1924 |

|

SU2016A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| ПРИСПОСОБЛЕНИЕ ДЛЯ АВТОМАТИЧЕСКОЙ ПЕРЕДАЧИ НА ПОЕЗД И С НЕГО ЖЕЗЛОВ | 1927 |

|

SU9001A1 |

| - P | |||

| ИСКРОУЛОВИТЕЛЬ ДЛЯ ПАРОВОЗОВ | 1923 |

|

SU649A1 |

| МАШИНА ДЛЯ РАСЩИПКИ ТКАНЕЙ | 1925 |

|

SU2395A1 |

| Способ восстановления хромовой кислоты, в частности для получения хромовых квасцов | 1921 |

|

SU7A1 |

| Оконное сигнальное приспособление | 1923 |

|

SU652A1 |

| ЧЕТЫРЁХВХОДОВОЙ КМОП ЛОГИЧЕСКИЙ ВЕНТИЛЬ ИСКЛЮЧАЮЩЕЕ-ИЛИ/ИСКЛЮЧАЮЩЕЕ-ИЛИ-НЕ | 2022 |

|

RU2784457C1 |

| ТРЁХВХОДОВОЙ КМОП ЛОГИЧЕСКИЙ ВЕНТИЛЬ ИСКЛЮЧАЮЩЕЕ ИЛИ/ИСКЛЮЧАЮЩЕЕ ИЛИ-НЕ | 2020 |

|

RU2761172C1 |

| CN 110611503 A, | |||

Авторы

Даты

2023-08-30—Публикация

2023-02-16—Подача