Изобретение относится к области радиотехники и связи и может быть использовано в качестве устройства усиления широкополосных сигналов, в структуре аналоговых микросхем различного функционального назначения (видеоусилителей, операционных усилителей, непрерывных стабилизаторов напряжения, перемножителей сигналов и т.д.).

Известны дифференциальные усилители (ДУ) на комплементарных n-p-n и p-n-p-транзисторах [1-29], которые составляют основу многих аналоговых микросхем ведущих микроэлектронных фирм (µА741, µА748, µА776 и др.) [1].

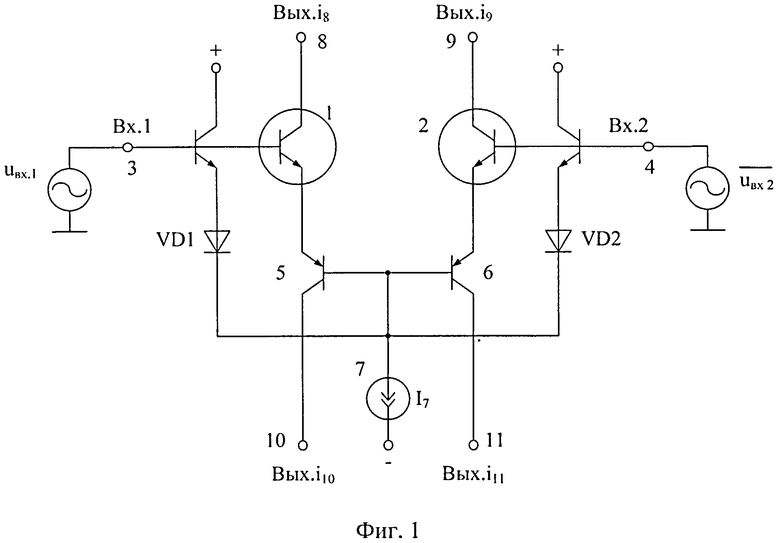

Ближайшим прототипом (фиг.1) заявляемого устройства является дифференциальный усилитель по патенту US №4.901.031. Он содержит первый 1 и второй 2 входные транзисторы, входные управляющие выводы которых соединены с соответствующими первым 3 и вторым 4 входами устройства, первый 5 и второй 6 выходные биполярные транзисторы, базы которых соединены друг с другом, первый 7 источник опорного тока, первую (8-9) группу противофазных токовых выходов 8 и 9 устройства, связанных соответствующими токовыми выводами первого 1 и второго 2 входных транзисторов, вторую группу (10, 11) противофазных токовых выходов 10 и 11 устройства, связанных с соответствующими коллекторами первого 5 и второго 6 выходных биполярных транзисторов, причем инжектирующий вывод первого 1 входного транзистора соединен с эмиттером первого 5 выходного биполярного транзистора, инжектирующий вывод второго 2 входного транзистора соединен с эмиттером второго 6 выходного транзистора.

Существенный недостаток известного ДУ состоит в том, что уровень постоянных составляющих его выходных противофазных напряжений смещен относительно общей шины источников питания. Это не позволяет обеспечить в ДУ:

- высокое усиление (Ку) при нулевом уровне статических напряжений на потенциальных выходах устройства;

- каскодное (последовательное) соединение двух и более идентичных ДУ без специальных цепей смещения статического уровня выходов ДУ относительно общей шины.

Основная задача предлагаемого изобретения состоит в создании условий, при которых выходные статические напряжения ДУ всегда близки к потенциалу общей шины источников питания ДУ. То есть такой ДУ обеспечивает преобразование входных сигналов, изменяющихся относительно общей шины источников питания в выходные напряжения, которые имеют близкие к нулю уровни постоянной составляющей и также изменяются противофазно относительно общей шины источников питания. Идентичные каскады данного класса допускают непосредственное соединение друг с другом и не требуют специальных цепей смещения статического уровня, ухудшающих их частотные и другие свойства.

Поставленная задача достигается тем, что в дифференциальном усилителе фиг.1, содержащем первый 1 и второй 2 входные транзисторы, входные управляющие выводы которых соединены с соответствующими первым 3 и вторым 4 входами устройства, первый 5 и второй 6 выходные биполярные транзисторы, базы которых соединены друг с другом, первый 7 источник опорного тока, первую (8-9) группу противофазных токовых выходов 8 и 9 устройства, связанных соответствующими токовыми выводами первого 1 и второго 2 входных транзисторов, вторую группу (10, 11) противофазных токовых выходов 10 и 11 устройства, связанных с соответствующими коллекторами первого 5 и второго 6 выходных биполярных транзисторов, причем инжектирующий вывод первого 1 входного транзистора соединен с эмиттером первого 5 выходного биполярного транзистора, инжектирующий вывод второго 2 входного транзистора соединен с эмиттером второго 6 выходного транзистора, предусмотрены новые элементы и связи - первый 7 источник опорного тока включен между коллектором первого 5 выходного транзистора и первой 12 шиной источника питания, второй дополнительный 13 источник опорного тока включен между коллектором второго 6 выходного транзистора и первой 12 шиной источника питания, между коллекторами первого 5 и второго 6 выходных транзисторов включены последовательно соединенные первый 14 и второй 15 дополнительные резисторы, общий узел которых связан с базами первого 5 и второго 6 выходных транзисторов, причем противофазными потенциальными выходами устройства 16, 17 являются коллекторы первого 5 и второго 6 выходных транзисторов, а в качестве первого 1 и второго 2 входных транзисторов используются полевые транзисторы с управляющими p-n переходами, затворы которых являются входными управляющими выводами первого 1 и второго 2 входных транзисторов, стоки - выходными токовыми выводами первого 1 и второго 2 входных транзисторов, а истоки - инжектирующими выводами первого 1 и второго 2 входных транзисторов.

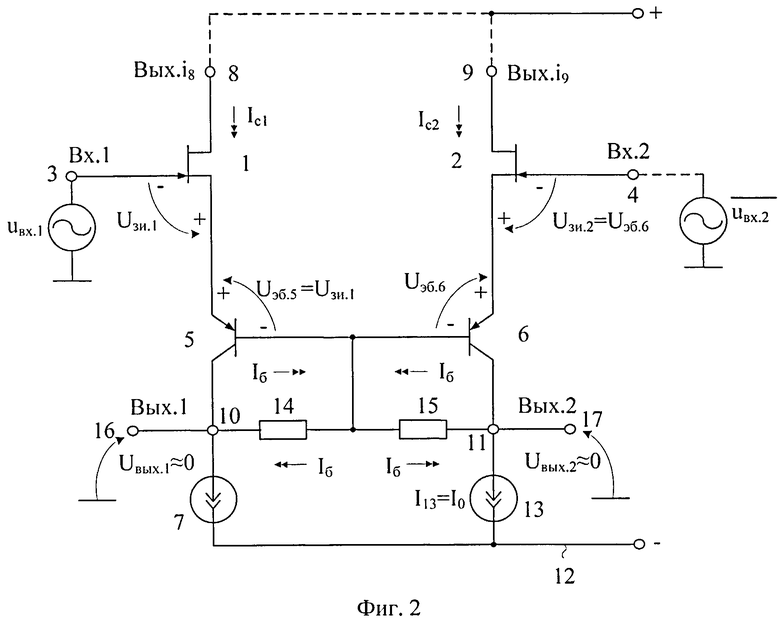

На чертеже фиг.1 показана схема ДУ-прототипа, а на чертеже фиг.2 - схема заявляемого устройства в соответствии с п.1 формулы изобретения.

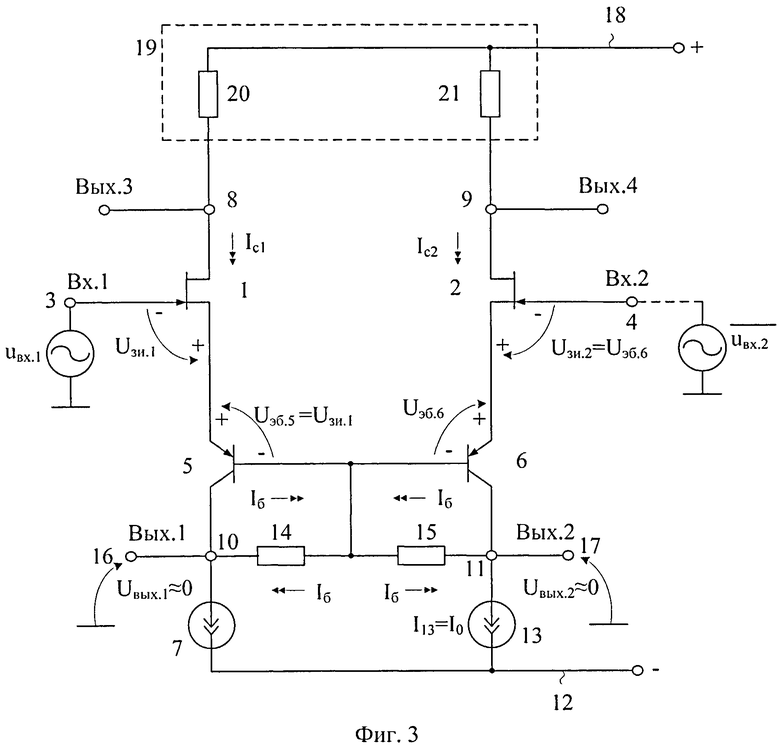

На чертеже фиг.3 показана схема усилителя в соответствии с п.2 формулы изобретения, где первая группа (8, 9) противофазных токовых выходов дифференциального усилителя связана со второй 18 шиной источника питания через дополнительную цепь нагрузки 19, причем токовые выходы 8 и 9 являются дополнительными потенциальными противофазными выходами устройства.

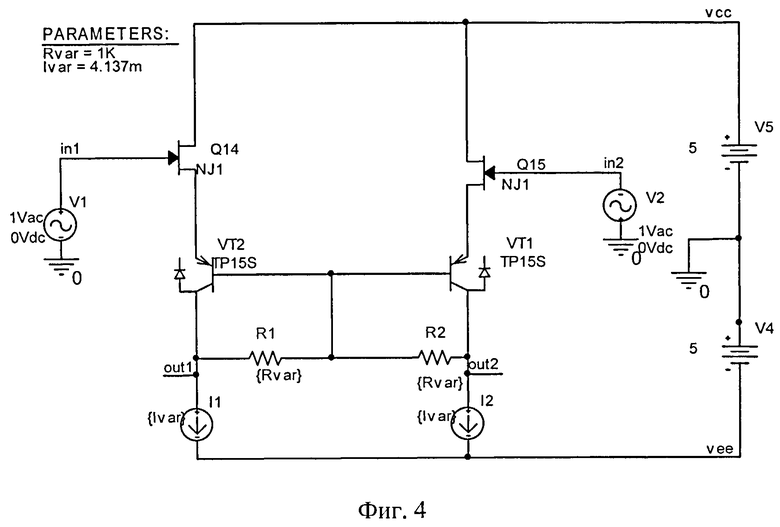

На чертеже фиг.4 показана схема усилителя фиг.2 в среде PSpice на моделях интегральных транзисторов АБМК_1_3 НПО «Интеграл» (г.Минск).

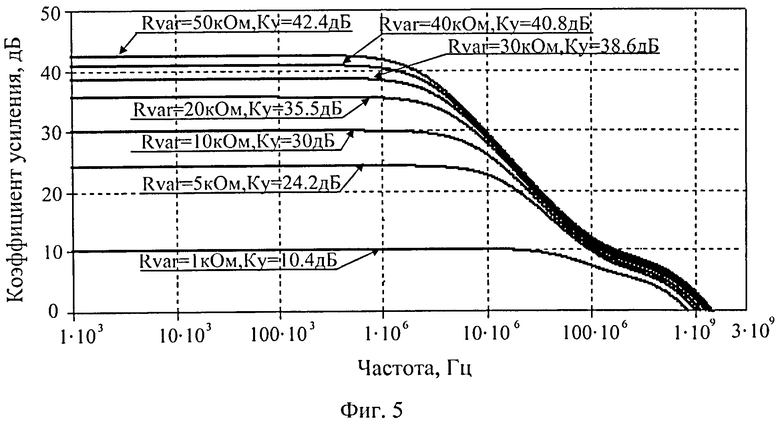

На чертеже фиг.5 показана зависимость коэффициента усиления ДУ фиг.4 от сопротивлений дополнительных резисторов R1 R2 (14 и 15 в обозначениях фиг.2).

Дифференциальный усилитель с нулевым уровнем выходных статических напряжений фиг.2 содержит первый 1 и второй 2 входные транзисторы, входные управляющие выводы которых соединены с соответствующими первым 3 и вторым 4 входами устройства, первый 5 и второй 6 выходные биполярные транзисторы, базы которых соединены друг с другом, первый 7 источник опорного тока, первую (8-9) группу противофазных токовых выходов 8 и 9 устройства, связанных соответствующими токовыми выводами первого 1 и второго 2 входных транзисторов, вторую группу (10, 11) противофазных токовых выходов 10 и 11 устройства, связанных с соответствующими коллекторами первого 5 и второго 6 выходных биполярных транзисторов, причем инжектирующий вывод первого 1 входного транзистора соединен с эмиттером первого 5 выходного биполярного транзистора, инжектирующий вывод второго 2 входного транзистора соединен с эмиттером второго 6 выходного транзистора. В данной схеме первый 7 источник опорного тока включен между коллектором первого 5 выходного транзистора и первой 12 шиной источника питания, второй дополнительный 13 источник опорного тока включен между коллектором второго 6 выходного транзистора и первой 12 шиной источника питания, между коллекторами первого 5 и второго 6 выходных транзисторов включены последовательно соединенные первый 14 и второй 15 дополнительные резисторы, общий узел которых связан с базами первого 5 и второго 6 выходных транзисторов, причем противофазными потенциальными выходами устройства 16, 17 являются коллекторы первого 5 и второго 6 выходных транзисторов, а в качестве первого 1 и второго 2 входных транзисторов используются полевые транзисторы с управляющими p-n переходами, затворы которых являются входными управляющими выводами первого 1 и второго 2 входных транзисторов, стоки - выходными токовыми выводами первого 1 и второго 2 входных транзисторов, а истоки - инжектирующими выводами первого 1 и второго 2 входных транзисторов.

На чертеже фиг.3, в соответствии с п.2 формулы изобретения, введена дополнительная цепь нагрузки 19, содержащая в частном случае резисторы нагрузки 20 и 21.

Рассмотрим работу заявляемого ДУ фиг.2.

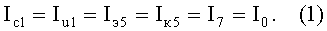

При нулевом входном сигнале (uвх.1=uвх.2=0) статический режим транзисторов 1, 2 и 5, 6 устанавливается источниками опорного тока 7 и 13:

где Ic, Iu - токи стока и истока полевых транзисторов 1, 2;

Iэ, Iк - токи эмиттера и коллектора транзисторов 5 и 6.

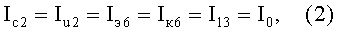

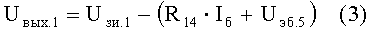

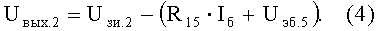

При этом на основании второго закона Кирхгофа можно найти, что выходные статические напряжения ДУ фиг.2:

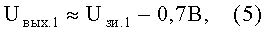

При относительно небольших значениях напряжений на резисторах 14 и 15 (R14Iб=R15Iб<<Uэб.5) из (3), (4) для кремниевых технологий можно получить:

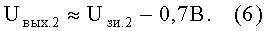

Напряжения затвор-исток Uзи полевого транзистора связаны с током стока (истока) следующей приближенной формулой

где Ic.max - максимальный ток стока при Uзи=0;

Uотс - напряжение отсечки при Ic≈0.

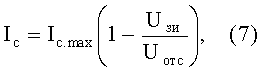

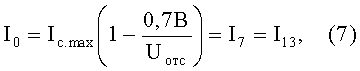

Учитывая, что численные значения напряжений затвор-исток (Uзи) полевого транзистора с управляющим p-n переходом могут изменяться в зависимости от тока стока Iс в широких пределах, из (5) и (6) можно найти, что при линейной аппроксимации стоко-затворной характеристики полевого транзистора (7) и выборе токов двухполюсников 7 и 13 в соответствии с формулой:

выходные статические напряжения (5) и (6) в заявляемом ДУ будут близки к нулю. Данный аналитический вывод подтверждается экспериментом. То есть к выходам 16 и 17 ДУ фиг.2 можно присоединить (без потери эффективности использования напряжения питания) входы 3 и 4 такого же ДУ и увеличить общий Ку такой двухкаскадной структуры. В классических структурах это невозможно.

Таким образом, заявляемое устройство имеет существенные преимущества в сравнении с прототипом.

БИБЛИОГРАФИЧЕСКИЙ СПИСОК

1. Операционные усилители и компараторы. М.: Издательский дом «Додека», 2001.- 560 с.

2. Патент США №3.786.362

3. Патент США №4.030.044

4. Патент США №4.059.808, фиг.5

5. Патент США №4.286.227

6. Авт.свид. СССР №375754, H03f 3/38

7. Авт.свид. СССР №843164, H03f 3/30

8. Патент США №3.660.773

9. Патент США №4.560.948

10. Патент РФ №2930041, H03f 1/32

11. Патент Японии №57-5364, H03f 3/343

12. Патент ЧССР №134845, кл. 21а2 18/08

13. Патент ЧССР №134849, кл. 21а2 18/08

14. Патент ЧССР №135326, кл. 21а2 18/08

15. Патент США №4.389.579

16. Патент Англии №1543361, НЗТ

17. Патент США №5.521.552 (фиг.3а)

18. Патент США №4.059.808

19. Патент США №5.789.949

20. Патент США №4.453.134

21. Патент США №4.760.286

22. Авт.свид. СССР №1283946

23. Патент РФ №2019019

24. Патент США №4.389.579

25. Патент США №4.453.092

26. Патент США №3.566.289

27. Патент США №4.059.808 (фиг.2)

28. Патент США №3.649.926

29. Патент США №4.714.894 (фиг.1).

| название | год | авторы | номер документа |

|---|---|---|---|

| СИММЕТРИЧНАЯ АКТИВНАЯ НАГРУЗКА ДИФФЕРЕНЦИАЛЬНЫХ УСИЛИТЕЛЕЙ ДЛЯ БИПОЛЯРНО-ПОЛЕВЫХ РАДИАЦИОННО-СТОЙКИХ ТЕХНОЛОГИЧЕСКИХ ПРОЦЕССОВ | 2014 |

|

RU2572380C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С ПАРАФАЗНЫМ ВЫХОДОМ | 2010 |

|

RU2421887C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С МАЛЫМ НАПРЯЖЕНИЕМ ПИТАНИЯ | 2011 |

|

RU2444116C1 |

| КОМПЛЕМЕНТАРНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С РАСШИРЕННЫМ ДИАПАЗОНОМ АКТИВНОЙ РАБОТЫ | 2012 |

|

RU2519544C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С МАЛЫМ НАПРЯЖЕНИЕМ СМЕЩЕНИЯ НУЛЯ | 2007 |

|

RU2331966C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С МАЛЫМ НАПРЯЖЕНИЕМ ПИТАНИЯ | 2011 |

|

RU2444117C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С ОТРИЦАТЕЛЬНОЙ ОБРАТНОЙ СВЯЗЬЮ ПО СИНФАЗНОМУ СИГНАЛУ | 2007 |

|

RU2364020C1 |

| БИПОЛЯРНО-ПОЛЕВОЙ ДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ | 2015 |

|

RU2615068C1 |

| КОМПЛЕМЕНТАРНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2009 |

|

RU2412530C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ КАСКАД С ПОВЫШЕННЫМ УСИЛЕНИЕМ ПО НАПРЯЖЕНИЮ | 2011 |

|

RU2461957C1 |

Изобретение относится к области радиотехники и связи и может быть использовано в качестве устройства усиления широкополосных сигналов, в структуре аналоговых микросхем различного функционального назначения (видеоусилителей, операционных усилителей, непрерывных стабилизаторов напряжения, перемножителей сигналов и т.д.). Технический результат заключается в обеспечении преобразования входных сигналов, изменяющихся относительно общей шины источников питания в выходные напряжения, которые имеют близкие к нулю уровни постоянной составляющей и также изменяются противофазно относительно общей шины источников питания. Технический результат достигается за счет дифференциального усилителя с нулевым уровнем выходных статических напряжений, который содержит первый (1) и второй (2) входные транзисторы, первый (5) и второй (6) выходные биполярные транзисторы, первый (7) источник опорного тока, первую (8-9) группу противофазных токовых выходов (8) и (9) устройство, вторую группу (10, 11) противофазных токовых выходов (10) и (11) устройство. 5 ил.

1. Дифференциальный усилитель с нулевым уровнем выходных статических напряжений, содержащий первый (1) и второй (2) входные транзисторы, входные управляющие выводы которых соединены с соответствующими первым (3) и вторым (4) входами устройства, первый (5) и второй (6) выходные биполярные транзисторы, базы которых соединены друг с другом, первый (7) источник опорного тока, первую (8-9) группу противофазных токовых выходов (8) и (9) устройства, связанных соответствующими токовыми выводами первого (1) и второго (2) входных транзисторов, вторую группу (10, 11) противофазных токовых выходов (10) и (11) устройства, связанных с соответствующими коллекторами первого (5) и второго (6) выходных биполярных транзисторов, причем инжектирующий вывод первого (1) входного транзистора соединен с эмиттером первого (5) выходного биполярного транзистора, инжектирующий вывод второго (2) входного транзистора соединен с эмиттером второго (6) выходного транзистора, отличающийся тем, что первый (7) источник опорного тока включен между коллектором первого (5) выходного транзистора и первой (12) шиной источника питания, второй дополнительный (13) источник опорного тока включен между коллектором второго (6) выходного транзистора и первой (12) шиной источника питания, между коллекторами первого (5) и второго (6) выходных транзисторов включены последовательно соединенные первый (14) и второй (15) дополнительные резисторы, общий узел которых связан с базами первого (5) и второго (6) выходных транзисторов, причем противофазными потенциальными выходами устройства (16), (17) являются коллекторы первого (5) и второго (6) выходных транзисторов, а в качестве первого (1) и второго (2) входных транзисторов используются полевые транзисторы с управляющими p-n переходами, затворы которых являются входными управляющими выводами первого (1) и второго (2) входных транзисторов, стоки - выходными токовыми выводами первого (1) и второго (2) входных транзисторов, а истоки - инжектирующими выводами первого (1) и второго (2) входных транзисторов.

2. Дифференциальный усилитель с нулевым уровнем выходных статических напряжений по п.1, отличающийся тем, что первая группа (8, 9) противофазных токовых выходов дифференциального усилителя связана со второй (18) шиной источника питания через дополнительную цепь нагрузки (19), причем токовые выходы (8) и (9) являются дополнительными потенциальными противофазными выходами устройства.

| US 4901031 A1, 13.02.1990 | |||

| US 4389579 A1, 21.06.1983 | |||

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 1991 |

|

RU2019019C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С ПОВЫШЕННЫМ ОСЛАБЛЕНИЕМ ВХОДНОГО СИНФАЗНОГО СИГНАЛА | 2005 |

|

RU2293433C1 |

Авторы

Даты

2013-07-27—Публикация

2012-08-15—Подача