Изобретение относится к области вычислительной техники, а именно к микропроцессорным системам с кэш-памятью, блоками обнаружения и коррекции ошибок и встроенным блоком самотестирования.

Известна схема самотестирования блоков памяти, содержащая блоки памяти, (подлежащие тестированию), компаратор, регистр сигнатур, регистры сбора статистики, схему управления блоком самотестирования, блоки формирования тестовой последовательности (Заявка на изобретение US №2002/0194558 A1, кл. G06F 17/50, опубл. 19.12.2002 г.).

Недостатком приведенной схемы является низкое быстродействие из-за передачи тестовых данных непосредственно на входы тестируемого блока памяти путем мультиплексирования.

Также известна схема самотестирования блоков памяти, где данные с блока памяти обрабатываются и затем записываются в сигнатурный регистр, что так же снижает быстродействие канала передачи данных между памятью и рабочей логикой (Заявка на изобретение US 2011/0055646 A1, кл. G06F 17/50, 03.03.2011 г.).

Недостатком приведенной схемы является низкое быстродействие и излишние нагрузки выходов памяти из-за использования для сравнения данных и определения ошибок компаратора непосредственно на выходах блоков памяти. Также недостатком представленной схемы является формирование признака ошибки блоком самотестирования не используемом в рабочем режиме.

Наиболее близким по технической сути и достигаемому результату является Устройство детектирования и корректирования ошибок с функцией самотестирования памяти включающее кэш-память второго уровня, содержащую четыре секции памяти тэгов и данных, блок логики помехоустойчивого кодирования и декодирования (Патент US №6,038,693, G06F 11/10, опубл. 14.03. 2000 г.).

Недостатком описанного устройства является невозможность одновременного определения нескольких однократных ошибок в тегах различных секций, приводящее к низкому быстродействию рабочего режима канала передачи данных памяти.

Технический результат от использования данного изобретения состоит в снижении, занимаемой на кристалле блоком самотестирования, площади, уменьшение необходимого для тестирования времени, повышение быстродействия рабочего режима канала передачи данных памяти.

Указанный технический результат достигается тем, что устройство детектирования и корректирования ошибок с функцией самотестирования памяти включающее кэш-память второго уровня, содержащую четыре секции памяти тэгов и данных, блок логики помехоустойчивого кодирования и декодирования, согласно изобретению снабжено блоком самотестирования со статусным регистром, портом доступа к тестовой логике, блоком формирования тестовой последовательности, генераторами адреса и данных, блоком выбора режима работы, дополнительным блоком кодирования, содержащим независимые кодеры, блоком декодирования, содержащим независимые декодеры, блоком управления контрольными битами, связанными с тэгами каждой секции, для независимой и параллельной проверки каждой секции кэш-памяти функцией самотестирования, при этом статусный регистр блока самотестирования связан с блоком декодирования и с портом доступа к тестовой логике, а генератор данных и генератор адреса связаны с блоком выбора режима работы.

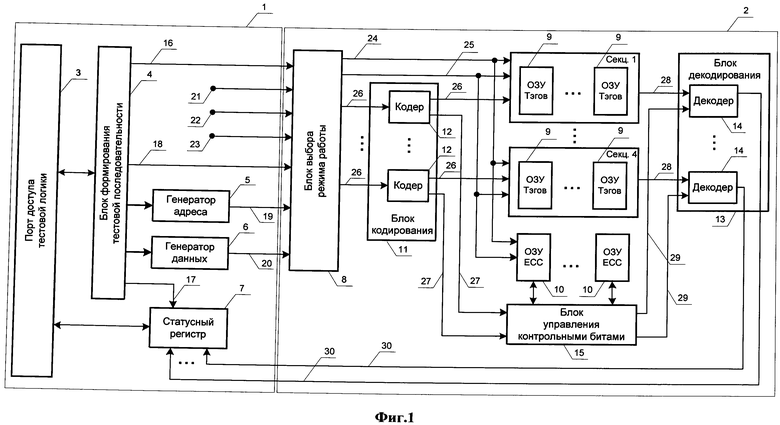

Изобретение поясняется чертежом, где приведена схема совместного использования логики самотестирования и модулей помехоустойчивого кодирования (ЕСС).

Схема устройства состоит из блока самотестирования 1, кэш-памяти второго уровня 2, порта доступа к тестовой логике 3, блока формирования тестовой последовательности 4, генераторов адреса 5, генератора данных 6, статусного регистра 7, блока выбора режима работы 8, ОЗУ тегов 9, ОЗУ битов ЕСС 10, блока кодирования 11, кодеров 12, блока декодирования 13, декодеров 14, блока управления контрольными битами 15.

Управление режимом работы схемы производится блоком формирования тестовой последовательности посредством сигналов: управления режимом работы 16, управления режимом работы статусного регистра 17.

Также схема содержит шины управления 18, адреса 19 и тэгов 20 тестового режима, шины управления 21, адреса 22 и тэгов 23 рабочего режима, входные шины управления 24, адреса 25, тэгов 26, входные шины контрольных битов 27, выходные шины тэгов 28, выходные шины контрольных битов 29, шину статуса ЕСС 30.

Устройство работает следующим образом. На порт доступа к тестовой логике 3 подаются управляющие сигналы, например, по интерфейсу JTAG. Блок формирования тестовой последовательности 4 переходит в тестовый режим, выдавая сигнал управления 16, производящий включение генераторов адреса 5 и данных 6. Одновременно, сигнал управления 16 распространяется на блок выбора режима работы 8, производя переключение кэш-памяти в тестовый режим, отключая шины тэгов 23, адреса 22 и управления 21 рабочего режима.

Блок формирования тестовой последовательности 4 по заранее определенным алгоритмам тестирования (маршевые тесты, бегущий ноль/единица) формирует сигналы управления блоками памяти. Распространение сигналов управления на блоки памяти производится по шинам управления 18 и 24. Одновременно включается по одной памяти тэгов 9 в каждой секции и соответствующее им ОЗУ ЕСС 10.

Управляемый блоком формирования тестовой последовательности 4 генератор адреса 5 создает физический адрес, передаваемый по шинам адреса тестового режима 17 в блок выбора режима работы, откуда по входной шине адреса 25, адрес распространяется на все блоки памяти тэгов 9 каждой секции и блоки памятей ЕСС 10 одновременно.

Полученные с генератора данных 6, тэги через шину тэгов тестового режима 20 и входную шину тэгов 26 распространяются на все блоки ОЗУ тэгов 9 каждой секции, и в блок ЕСС кодирования 11, содержащий в себе кодеры 12. Количество кодеров соответствует количеству секций кэш-памяти второго уровня. Рассчитанные кодерами 12 в блоке кодирования 11, контрольные биты по входным шинам контрольных битов 27 передаются в блок управления контрольными битами 15, в котором из контрольных бит каждой секции формируется строка. Полученная строка записывается в соответствующее ОЗУ ЕСС 10, выбор которого производится шиной управления 24.

В тестовом режиме блок формирования тестовой последовательности 4 для операций чтения и записи в блоки памяти тэгов генерирует набор управляющих сигналов и передает их по шине управления тестового режима 18 и входной шине управления 24. При этом одновременно может быть включена только одна память тэгов 9 в каждой секции и соответствующее им одно ОЗУ ЕСС 10. Полученные с каждой секции тэги, по выходным шинам тэгов 28 передаются в блок декодирования 13. Считанные из соответствующего ОЗУ ЕСС 10, контрольные биты через блок управления контрольными битами 15 также передаются в блок декодирования 12. Блок декодирования 15 состоит из нескольких декодеров 14 (по одному на каждую секцию). Полученные в результате декодирования статусы тэгов по шинам статуса ЕСС 30 передаются в статусный регистр 7 схемы самотестирования, где аккумулируются данные о наличии ошибок в блоках ОЗУ тэгов 9 и соответствующих им ОЗУ ЕСС 10 за время прохождения выбранных алгоритмов тестирования. По завершению тестирования из статусного регистра 7 на порт тестовой логики 3 выдается статус завершения, по которому определяется работоспособность каждого блока памяти тэгов и битов ЕСС кэш-памяти второго уровня.

| название | год | авторы | номер документа |

|---|---|---|---|

| ОТОБРАЖЕНИЕ ВСТРОЕННОГО АДРЕСА ЕСС | 2014 |

|

RU2644529C2 |

| МНОГОСКОРОСТНОЙ ПОСЛЕДОВАТЕЛЬНЫЙ ДЕКОДЕР ВИТЕРБИ ДЛЯ ИСПОЛЬЗОВАНИЯ В СИСТЕМЕ МНОГОСТАНЦИОННОГО ДОСТУПА С КОДОВЫМ РАЗДЕЛЕНИЕМ | 1994 |

|

RU2222110C2 |

| Имитатор для тестирования компонентов моноканальной локальной вычислительной сети | 1987 |

|

SU1446621A1 |

| УСТРОЙСТВО КОДИРОВАНИЯ-ДЕКОДИРОВАНИЯ ИНФОРМАЦИИ | 1994 |

|

RU2115231C1 |

| СИСТЕМА НА ОПТИЧЕСКИХ ДИСКАХ | 1996 |

|

RU2181217C2 |

| ОПЕРАТИВНОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО С ВЫСОКОЙ СТЕПЕНЬЮ ОТКАЗОУСТОЙЧИВОСТИ | 2005 |

|

RU2327236C2 |

| ЭНТРОПИЙНЫЙ КОДЕР ДЛЯ СЖАТИЯ ИЗОБРАЖЕНИЯ | 2011 |

|

RU2575679C2 |

| АРХИТЕКТУРА ПАМЯТИ ДЛЯ ДЕКОДЕРА МАКСИМАЛЬНОЙ АПОСТЕРИОРНОЙ ВЕРОЯТНОСТИ | 1999 |

|

RU2236085C2 |

| СИСТЕМА И СПОСОБ ПОДСЧЕТА НАЧАЛЬНЫХ НУЛЕВЫХ РАЗРЯДОВ И ПОДСЧЕТА НАЧАЛЬНЫХ ЕДИНИЧНЫХ РАЗРЯДОВ В ЦИФРОВОМ ПРОЦЕССОРЕ СИГНАЛОВ | 2006 |

|

RU2409837C2 |

| Устройство для коррекции ошибок в блоках памяти с последовательным доступом | 1987 |

|

SU1510014A1 |

Изобретение относится к области вычислительной техники, а именно к микропроцессорным системам с кэш-памятью, блоками обнаружения и коррекции ошибок и встроенным блоком самотестирования. Техническим результатом является повышение быстродействия рабочего режима канала передачи данных памяти за счет одновременного определения нескольких однократных ошибок в тегах различных секций. Устройство детектирования и корректирования ошибок с функцией самотестирования памяти включает кэш-память второго уровня, содержащую четыре секции памяти тэгов и данных, блок логики помехоустойчивого кодирования и декодирования, снабжено блоком самотестирования со статусным регистром, портом доступа к тестовой логике, блоком формирования тестовой последовательности, генераторами адреса и данных, блоком выбора режима работы, дополнительным блоком кодирования, содержащим независимые кодеры, блоком декодирования, содержащим независимые декодеры, блоком управления контрольными битами, связанными с тэгами каждой секции, для независимой и параллельной проверки каждой секции кэш-памяти функцией самотестирования, при этом статусный регистр блока самотестирования связан с блоком декодирования и с портом доступа к тестовой логике, а генератор данных и генератор адреса связаны с блоком выбора режима работы. 1 ил.

Устройство детектирования и корректирования ошибок с функцией самотестирования памяти, включающее кэш-память второго уровня, содержащую четыре секции памяти тэгов и данных, блок логики помехоустойчивого кодирования и декодирования, отличающееся тем, что устройство снабжено блоком самотестирования со статусным регистром, портом доступа к тестовой логике, блоком формирования тестовой последовательности, генераторами адреса и данных, блоком выбора режима работы, дополнительным блоком кодирования, содержащим независимые кодеры, блоком декодирования, содержащим независимые декодеры, блоком управления контрольными битами, связанными с тэгами каждой секции, для независимой и параллельной проверки каждой секции кэш-памяти функцией самотестирования, при этом статусный регистр блока самотестирования связан с блоком декодирования и с портом доступа к тестовой логике, а генератор данных и генератор адреса связаны с блоком выбора режима работы.

| МУЛЬТИМЕДИА-ПРОЦЕССОР, МНОГОПОТОЧНЫЙ ПО ТРЕБОВАНИЮ | 2008 |

|

RU2425412C2 |

| КОНФИГУРИРОВАНИЕ КАНАЛОВ УПРАВЛЕНИЯ В СИСТЕМЕ МОБИЛЬНОЙ СВЯЗИ | 2007 |

|

RU2437222C2 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

2013-08-20—Публикация

2012-07-20—Подача