СО

С

г

СП

наружения ошибок 1, блок памяти адресов ошибок 2, блок памяти кода ошибки 3, буферный блок памяти А, счетчик 5, блок выбора адреса 6, фор. шрователь сигналов обращения 7, блок коррекции 8, шинный формирователь 9, блок сравнения 10, элемент ИЛИ 11, кодер 12, первый 13 и второй 14 коммутаторы и первый 15 и второй 16 сдвиговые регистры. Введение в устройство кодера шинного форми- рователя, второго сдвигового регистра и второго коммутатора позволяет реализовать функции кодирования и декодирования в одном устройстве, 5 ил.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для коррекции ошибок внешней памяти | 1987 |

|

SU1501173A1 |

| Устройство для коррекции ошибок в информации | 1986 |

|

SU1372365A1 |

| Устройство для коррекции ошибок | 1987 |

|

SU1541677A1 |

| Устройство для коррекции ошибок | 1986 |

|

SU1372364A1 |

| Устройство защиты от ошибок внешней памяти | 1981 |

|

SU1018119A1 |

| Устройство для обнаружения и коррекции ошибок | 1986 |

|

SU1372367A1 |

| Динамическое запоминающее устройство с коррекцией ошибок | 1983 |

|

SU1133625A1 |

| Запоминающее устройство с самоконтролем | 1984 |

|

SU1249590A1 |

| Устройство для коррекции ошибок в блоках памяти | 1985 |

|

SU1257708A1 |

| Имитатор для тестирования компонентов моноканальной локальной вычислительной сети | 1987 |

|

SU1446621A1 |

Изобретение относится к вычислительной технике, а именно к устройствам для коррекции ошибок в запоминающих устройствах (ЗУ) с последовательным доступом. Целью изобретения является упрощение устройства и повышение быстродействия за счет обеспечения кодирования информации при записи ее в ЗУ. Устройство для коррекции ошибок в ЗУ с последовательным доступом содержит блок обнаружения ошибок 1, блок памяти адресов ошибок 2, блок памяти кода ошибки 3, буферный блок памяти 4, счетчик 5, блок выбора адреса 6, формирователь сигналов обращения 7, блок коррекции 8, шинный формирователь 9, блок сравнения 10, элемент ИЛИ 11, кодер 12, первый 13 и второй 14 коммутаторы и первый 15 и второй 16 сдвиговые регистры. Введение в устройство кодера шинного формирователя, второго сдвигового регистра и второго коммутатора позволяет реализовать функции кодирования и декодирования в одном устройстве. 5 ил.

Изобретение относится к вычислительной технике, а именно к устройствам коррекции ошибок в запомина- юшрих устройствах (ЗУ) с последовательным доступом, и может быть использовано для повьш1ения надежности за счет исправления пакетных ошибок.

Цель изобретения - упрощение устройства для коррекции ошибок и повышение его быстродействия за счет- обеспечения кодироьания информации при записи ее в ЗУ с последовательным доступом,

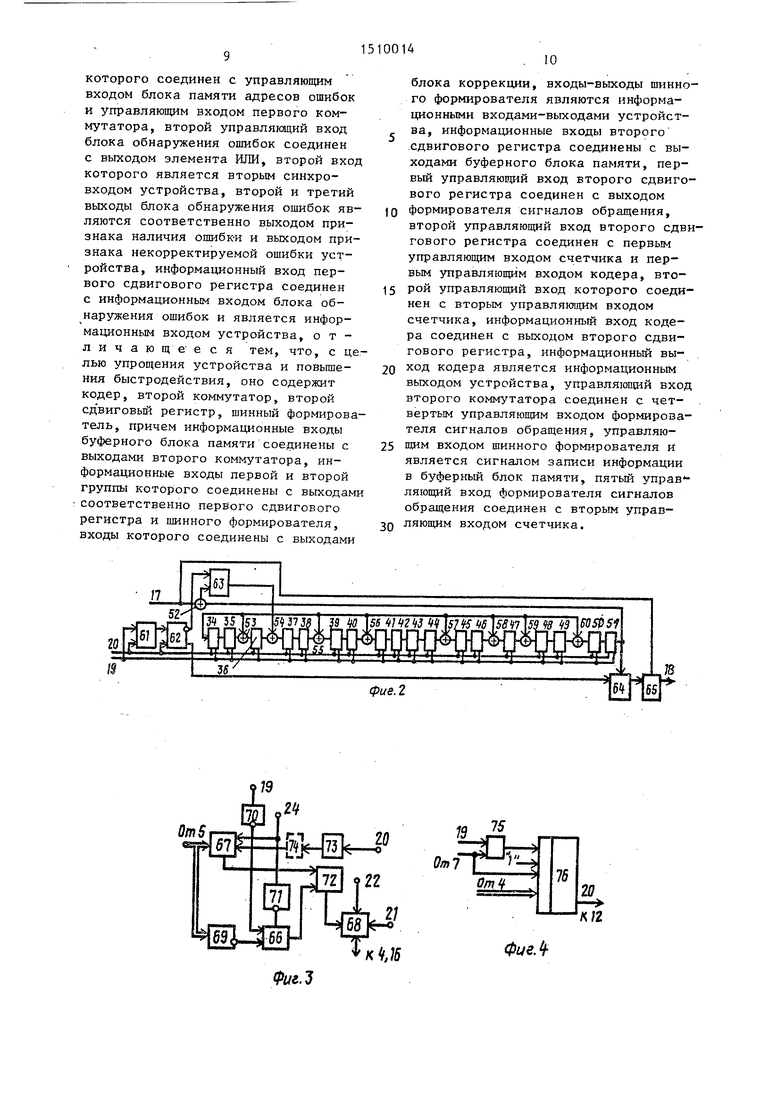

На фиг,1 представлена структурна схема устройства; на.фиг.2 - структурная схема кодера; на фиг,3 - структурная схема формирователя сигналов обращения; на фиг,4 - структурная схема второго сдвигового регистра; на фиг.5 - структурная схем блока сравнения.

Устройство для коррекции ошибок в блоках памяти с последовательным доступом (фиг,1) содержит блок 1 обнаружения ошибок, блок 2 памяти адресов ошибок, блок 3 памяти кода ошибки, буферный блок 4 памяти, счетчик 5, блок 6 выбора адреса, формирователь 7 сигналов обращения, блок 8 коррек ши, шинный формирователь 9, блок 10 сравнения, элемент ИЛИ It-, кодер 12, первый 13 и второй 14 коммутаторы, первьй 15 и второй 16 сдвиговые регистры, информационные вход 17 и выход 18 устройства, первый синхровход 19, вход 20 начальной установки, вход 21 обращения, вход 22 управления режимом работы, второй синхровход 23, вход 24 записи информации в буферный блок памяти устройства, информационные входы-выходы 25 устройства, - адресные входы 26 устройства, выход 27 признака наличия ошибки и выход 28 признака некорректируемой

ошибки. На фиг,1 представлен так- же блок 29 запуска, содержащий инвертор 30, генератор 31 импульсов, элемент И 32 и триггер 33

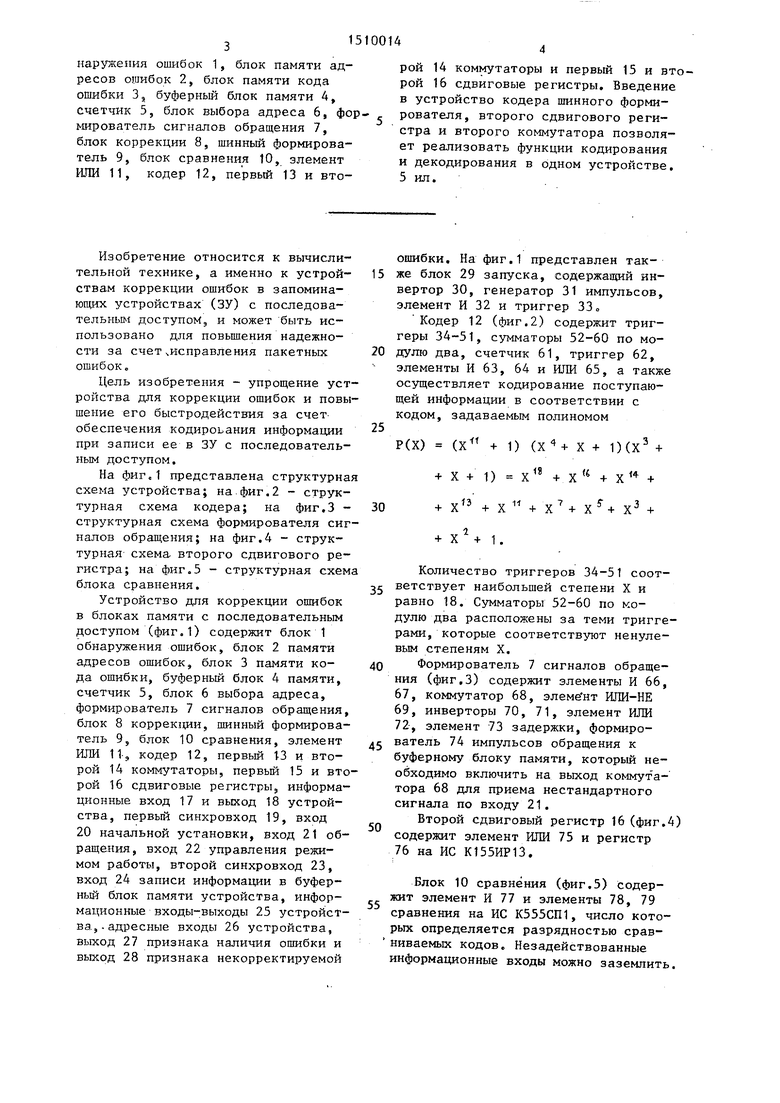

Кодер 12 (фиг.2) содержит триггеры 34-51, сумматоры 52-60 по мо- дулю два, счетчик 61, триггер 62, элементы И 63, 64 и ИЛИ 65, а также осуществляет кодирование поступающей информации в соответствии с кодом, задаваемым полиномом

Р(Х) (Х + 1) ( X + 1)(Х +

(4

4

+ X + 1) Х + X + X

+ + X + Х + X + Х +

+ X + 1,

Количество триггеров 34-51 соот- ветствует наибольшей степени X и равно 18, Сумматоры 52-60 по модулю два расположены за теми триггерами, которые соответствзпот ненулевым степеням X,

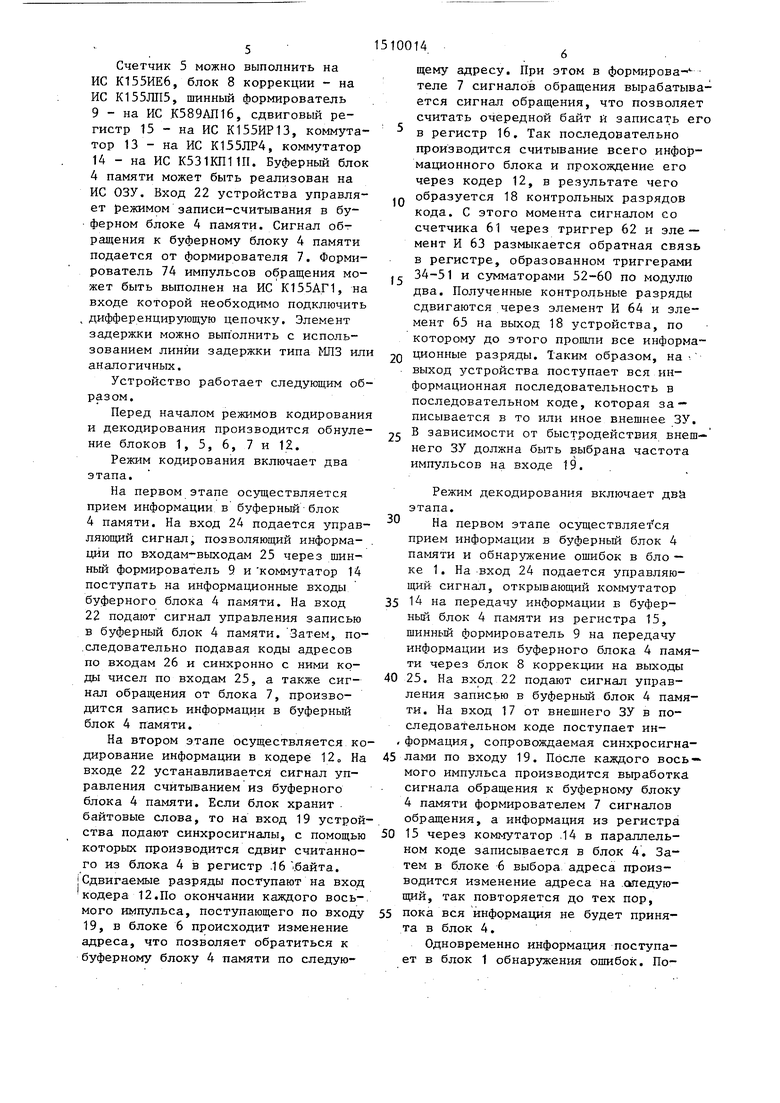

Формирователь 7 сигналов обращения (фиг.З) содержит элементы И 66, 67, коммутатор 68, элеме нт ИЛИ-НЕ 69, инверторы 70, 71, элемент ИЛИ 72, элемент 73 задержки, формиро- ватель 74 импульсов обращения к

буферному блоку памяти, который необходимо включить на выход коммут а- тора 68 для приема нестандартного сигнала по входу 21,

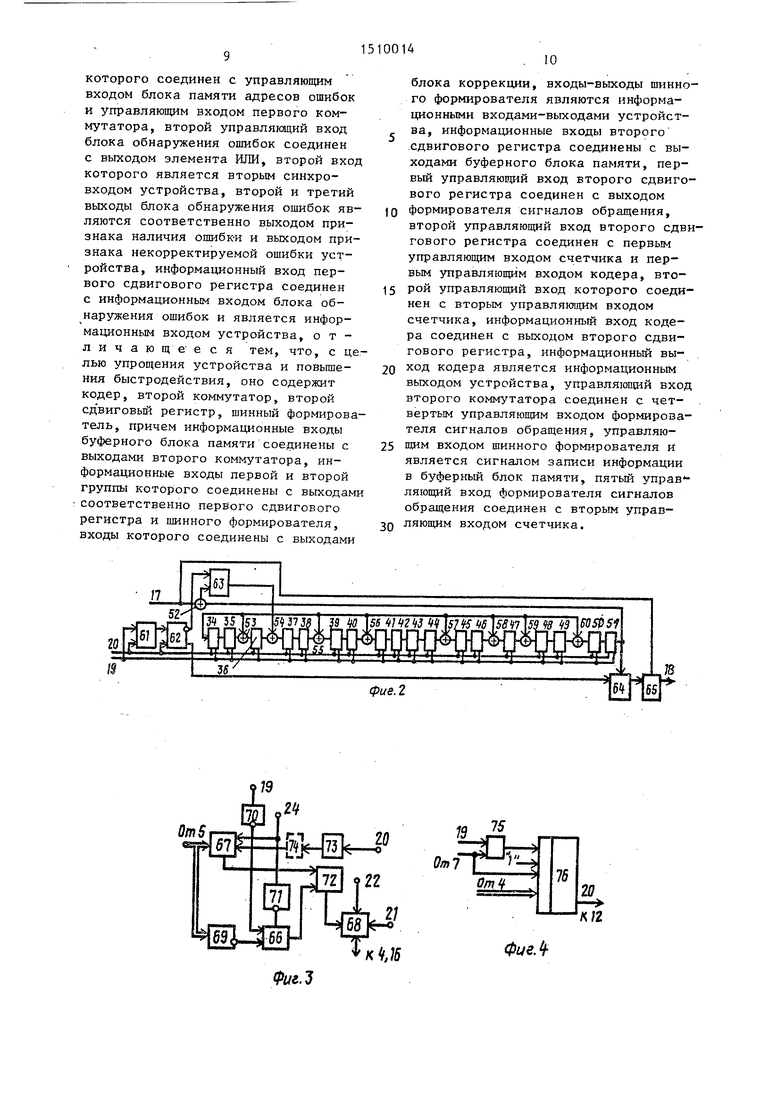

Второй сдвиговый регистр 16 (фиг,4) содержит элемент ИЖ 75 и регистр 76 на ИС К155ИР13.

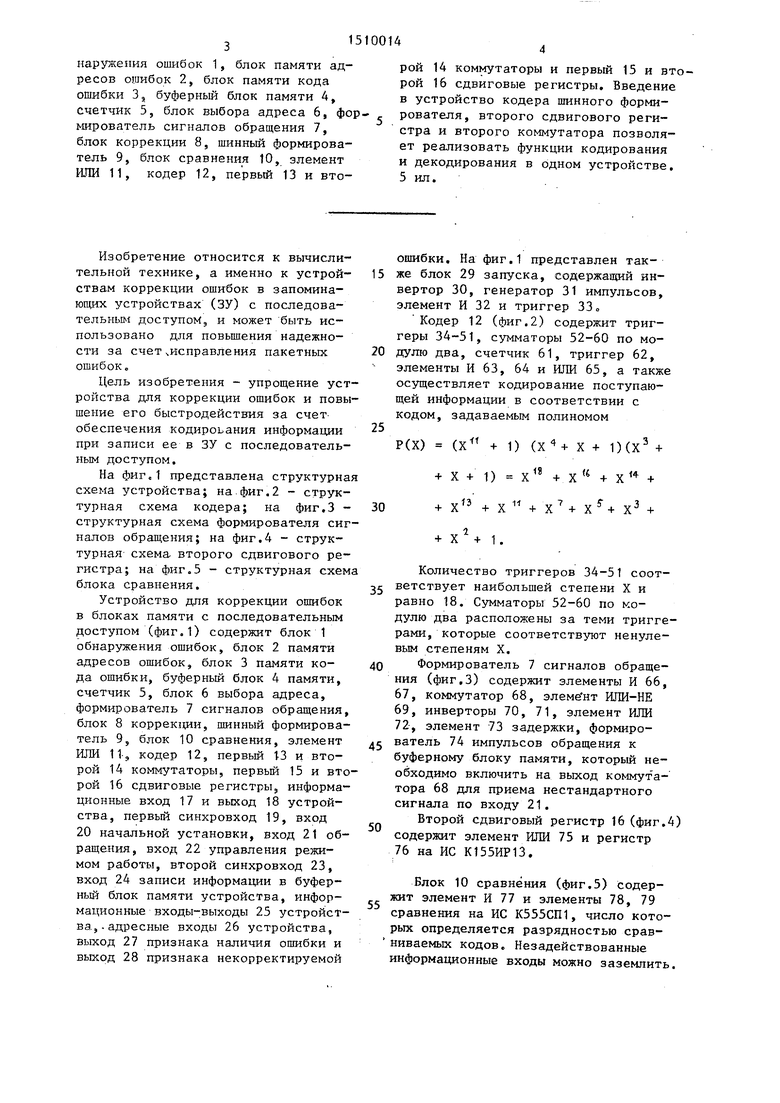

Блок 10 сравнения (фиг,5) содержит элемент И 77 и элементы 78, 79 сравнения на ИС К555СП1, число которых определяется разрядностью срав- ниваемьк кодов. Незадействованные информационные входы можно заземлить.

Счетчик 5 можно выполнить на ИС К155ИЕ6, блок 8 коррекции - на ИС К155ЛП5, шинный формирователь 9 - на ИС .К589АП16, сдвиговый регистр 15 - на ИС К155ИР13, коммутатор 13 - на ИС К155ЛР4, коммутатор 14 - на ИС К531КП11Г1. Буферный блок 4 памяти может быть реализован на ИС ОЗУ. Вход 22 устройства управляет режимом записи-считывания в буферном блоке 4 памяти. Сигнал обращения к буферному блоку 4 памяти подается от формирователя 7. Формирователь 74 импульсов обращения может быть выполнен на ИС К155АГ1, на входе которой необходимо подключить дифференцирующую цепочку. Элемент задержки можно вып олнить с использованием линии задержки типа МЛЗ или аналогичных.

Устройство работает следующим образом.

Перед началом режимов кодирования и декодирования производится обнуление блоков 1, 5, 6, 7 и 12.

Режим кодирования включает два этапа.

На первом этапе осуществляется прием информации в буферный - блок 4 памяти. На вход 24 подается управляющий сигнал, позволяющий информа- . цйи по входам-выходам 25 через шинный формирователь 9 и коммутатор 14 поступать на информационные входы буферного блока 4 памяти. На вход 22 подают сигнал управления записью в буферный блок 4 памяти. Затем, по- следовательно подавая коды адресов по входам 26 и синхронно с ними коды чисел по входам 25, а также сигнал обращения от блока 7, производится запись информации в буферный блок 4 памяти.

На втором этапе осуществляется кодирование информации в кодере 12о На входе 22 устанавливается сигнал управления считыванием из буферного блока 4 памяти. Если блок хранит байтовые слова, то на вход 19 устройства подают синхросигналы, с помощью которых производится сдвиг считанного из блока 4 в регистр .16 мбайта, Сдвигаемые разряды поступают на вход кодера 12.no окончании каждого вось-/ мого импульса, поступающего по входу 19, в блоке 6 происходит изменение адреса, что позволяет обратиться к буферному блоку 4 памяти по следую0

щему адресу. При этом в формирова- теле 7 сигналов обращения вырабатывается сигнал обращения, что позволяет считать очередной байт и записать его в регистр 16, Так последовательно производится считывание всего информационного блока и прохождение его через кодер 12, в результате чего образуется 18 контрольных разрядов кода. С этого момента сигналом со счетчика 61 через триггер 62 и элемент И 63 размыкается обратная связь в регистре, образованном триггерами г 34-51 и С5т маторами 52-60 по модулю два. Полученные контрольные разряды сдвигаются через элемент И 64 и элемент 65 на выход 18 устройства, по которому до этого прошли все информационные разряды. Таким образом, на выход устройства поступает вся информационная последовательность в последовательном коде, которая записывается в то или иное внешнее ЗУ. В зависимости от быстродействия внешнего ЗУ должна быть выбрана частота импульсов на входе 19.

0

5

Режим декодирования включает два этапа.

На первом этапе осуществляемся прием информации в буферный блок 4 памяти и обнаружение ошибок в бло - ке 1. На вход 24 подается управляющий сигнал, открывающий коммутатор

14 на передачу информации в буферный блок 4 памяти из регистра 15, шинньш формирователь 9 на передачу информации из буферного блока 4 памяти через блок 8 коррекции на выходы

15 через коммутатор .14 в параллельном коде записывается в блок 4, Затем в блоке 6 выбора адреса произодится изменение адреса на .сшедую- ий, так повторяется до тех пор,

ока вся информация не будет принята в блок 4.

Одновременно информация поступает в блок 1 обнаружения ошибок. По-

еле того, как будут приняты все 1155 разрядов, блок 1 выработает по выходу 27 сигналы Опшбка, Нет ошибки, а по выходу 28 - Корректируемая ошибка, Некорректируемая ошибка. Сигнал Ошибка по выходу 27 запускает блок 29 запуска, который через элемент ИЛИ 11 продолжает подавать синхросигналы, частота ко- торых может быть значительно больше. После того, как блок 1 выработает сигнал Ошибка зафиксирована, поступающий на блок 2 и коммутатор 13, начинается этап коррекции ошиб- ки.

На втором этапе осуществляется передача информации из буферного блока 4 памяти на выход устройства. На входе 22 устройства устанавлива- ется сигнал управления считыванием из блока 4, На вход 21 подаются сигналы обращения, синхронно с которыми на входы 26 подаются коды а д- ресов. На выходе блока.4, находятся байты данных, передаваемые на выходы 25„ В случае корректируемой ошибки в блоке 10 сравнения по адресам, содержащим ошибку, вырабатываются сигналы сравнения, через коммутатор 13 коды векторов-ошибок передаются в блок 8 коррекции, где происходит поразрядное исправление ошибки. Предлагаемое устройство в режиме коррекции работает аналогично известному.

Таким образом, путем введения четырех новых блоков и изменения конструкции двух известных обеспечено расширение функциональных возможностей предлагаемого устройства за счет- реализации процедуры кодирования информации. Это создает положи- тельньш технический и экономический эффект. Последнее достигается за сче того, что реализация отдельного ко- дера привела бы к увеличению аппаратных затрат примерно в 1,7 раза, тогда как изменение конструкции связано лишь с 20%-ным увеличением аналогичных затрат.

Формула изобретения

- Устройство для коррекции ошибок в блоках памяти с последовательным доступом, содержащее блок обнаружени ошибок,блок памяти адресов ошибок, блок памяти кода ошибки,буферный

0 5 п 5

5 0

5

0

блок памяти,счетчик,блок выбора адреса, формирователь сигналов обращения, блок коррекции,элемент ИЛИ,блок сравнения, первый коммутатор, первый сдвиговый регистр, причем первый управляющий вход формирователя сигналов обращения соединен с управляющим входом первого сдвигового регистра, первым управляющим входом блока выбора адреса и является первым синхровходом устройства, второй управляющий вход счетчика соединен с вторым управляющим входом блока выбора адреса, первым управ- входом блока обнаружения опш- бок и является входом начальной установки устройства, второй управляющий вход формирователя сигналов обращения является входом обращения устройства, первый управляющей вход буферного блока памяти соединен с третьим управляющим входом блока выбора адреса, третьим управляющим входом формир ователя сигналов обращения и является входом задания режима работы устройства, выход формирователя сигналов обращения соединен с вторым управляющим входом буферного блока памяти, адресные входы которого соединены с выходами блока выбора адреса,.адресные входы первой группы которого соединены с адресными входами формирователя сигналов обращения и выходами счетчика, адресные входы второй группы блока выбора адреса соединены с адресными входами первой группы блока сравнения и являются адресными вхо- дани устройства, выходы буферного блока памяти соединены с информа- : ционными входами первой группы блока коррекции, информационные входы второй группы которого соединены с выходами первого коммутатора, информационные входы первой и второй групп которого соединены соответственно с выходами блока сравнения и блока памяти кода ошибки, информационные входы первой и второй групп которого соответственно соединены с выходами второй группы блока - обнаружения ошибок, выходами блока памяти адресов ошибок и с информа- ционньми входами второй группы блока сравнения, информационные входы блока памяти адресов ошибок соединены с выходами первой группы блока обнаружения ошибок, первый выход

которого соединен с управляющим входом блока памяти адресов ошибок и управляющим входом первого коммутатора, второй управляюций вход блока обнарз ения ошибок соединен с выходом элемента ИЛИ, второй вход которого является вторым синхро- входом устройства, второй и третий выходы блока обнаружения ошибок являются соответственно выходом признака наличия ошибк-и и выходом признака некорректируемой ошибки устройства, информационный вход первого сдвигового регистра соединен с информационным входом блока обнаружения ошибок и является информационным входом устройства, отличающееся тем, что, с целью упрощения устройства и повьше- ния быстродействия, оно содержит кодер, второй коммутатор, второй сд виговьй регистр, шинный формирователь, причем информационные входы буферного блока памяти соединены с выходами второго коммутатора, информационные входы первой и второй группы которого соединены с выходами соответственно перв ого сдвигового регистра и шинного формирователя, входы которого соединены с выходами

От 5

Фиг. 5

блока коррекции, входы-выходы шинного формирователя являются информационными входами-выходами устройства, информационные входы второго сдвигового регистра соединены с выходами буферного блока памяти, первый управляющий вход второго сдвигового регистра соединен с выходом

формирователя сигналов обращения,

второй управляющий вход второго сдвигового регистра соединен с первым управляющим входом счетчика и первым управляющим входом кодера, второй управляюш 1й вход которого соединен с вторым управляющим входом счетчика, информационный вход кодера соединен с выходом второго сдвигового регистра, информационный выход кодера является информационным выходом устройства, управляющий вход второго коммутатора соединен с четвертым управляющим входом формирователя сигналов обращения, управляюш м входом шинного формирователя И является сигналом записи информации в буферный блок памяти, пятый управ - ляюшJ й вход формирователя сигналов обращения соединен с вторым управ-

входом счетчика.

фие.2

Kif.K

ФиеЛ

25

ше

Г

От г / -с:

фиг,5

7J

Л

| Хетагуров Я.А., Руднев Ю.П | |||

| По- вьшение надежности цифровых устройств методами избыточного кодирования | |||

| - М.: Энергия, 1974, с.71 | |||

| Устройство для обнаружения и коррекции ошибок | 1986 |

|

SU1372366A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1989-09-23—Публикация

1987-12-30—Подача