i4

|li

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля информации в многоканальной локальной вычислительной сети | 1987 |

|

SU1446622A1 |

| Запоминающее устройство | 1987 |

|

SU1413674A1 |

| ИМИТАТОР СИГНАЛОВ УПРАВЛЕНИЯ ПОЗИЦИОНИРОВАНИЕМ МАГНИТНЫХ ГОЛОВОК ОТНОСИТЕЛЬНО МАГНИТНЫХ ДИСКОВ | 1991 |

|

RU2017239C1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО ИЗОБРАЖЕНИЙ | 1990 |

|

RU2047921C1 |

| Устройство для диагностирования периферийных устройств | 1990 |

|

SU1716518A1 |

| Запоминающее устройство для телевизионного изображения | 1985 |

|

SU1265785A1 |

| Станция локальной сети | 1987 |

|

SU1478221A1 |

| Запоминающее устройство на цилиндрических магнитных доменах | 1987 |

|

SU1451768A1 |

| Контроллер станции локальной сети | 1988 |

|

SU1647590A1 |

| Устройство для считывания и отображения видеоинформации | 1988 |

|

SU1817116A1 |

Изобретение относится к области вычислительной техники и может быть использовано для тестовой проверки ксжпонентов моноканальной локальной вычислительной сети (абонентских сис- тем« транспортных и канальньвс станций, контроллеров моноканала, блоков доступа к физической среде передачи данных). Цель изобретения - расширение функциональных возможностей за счет введения дополнительных режимов имитации. Цель достигается тем, что в имитатор, содержащий блоки памяти и управления,формирователь контрольной последовательности кадра, генератор импульсов, блок вывода данных, введены блок адресации, блок счета . длины кадра, блок ошибок, мультиплексор данных, счетчик мультиплексора данных и блок задержки. Имитатор дает возможность формировать разнообразные тестовые кадры за C4et изменения в широких пределах длины кадра, внесения ошибки д«обрй комбинации в контрольное поле, регулирования межкадрового интервала, что. в конечном итоге позволяет повысить достоверность (полноту и точность) диагностирования сетевых компоиен- тов. 8 нп. С

©d td

Изобретение относится к вычислительной технике и может быть исполь зовано для тестовой проверки компонентов моноканальной локальной вы- числительной сети, в частности для тестовой проверки абонентских систем, транспортных и канальных станций, контроллеров моноканала и блоков доступа к физической среде пере- дачи данных.

Целью изобретения является расширение функциональных возможностей за счет введения дополнительных режимов имитации.

На фиг. 1 представлена блок-схема имитатора на фиг.2-8 - примеры реализации функциональных схем блока памяти, блока управления, блока адресации, блока счета длины кадра, блока фиксации ошибок, блока задержки и блока вывода данных.

Имитатор (фиг. 1) содержит блок 1 памяти, блок 2 управления, блок 3 вьшода данных, мультиплексор 4 дан- ных, счетчик 5 мультиплексора данных блок 6 адресации, блок 7 счета длины кадра, формирователь 8 контрольной последовательности кадра (КПК), блок 9 фиксации ошибок, блок 10 за- держки и генератор 11 импульсов.

Блок 1 памяти содержит (фиг. 2) коммутатор 12 адреса, первую 13, 14 и вторую 15, 16 группы запоминающих узлов (ЗУ) и v yльтиплeкcop 17. В блоке 1 памяти используются группы ЗУ емкостью 2 х (8 х 2048) бит, заполняемые по 16-ти разрядной шине Данные путем последовательной адресации ячеек памяти. При записи об- разуется сообщение, кратное по длине числу 16 и содержащее до 4096 октетов. Разбиение ЗУ на две группы предназначено для записи -текущего и последующего кадров.

Блок 2 управления содержит (фиг.З элементы ИЛИ 18-20 и распределитель 21 импульсов.

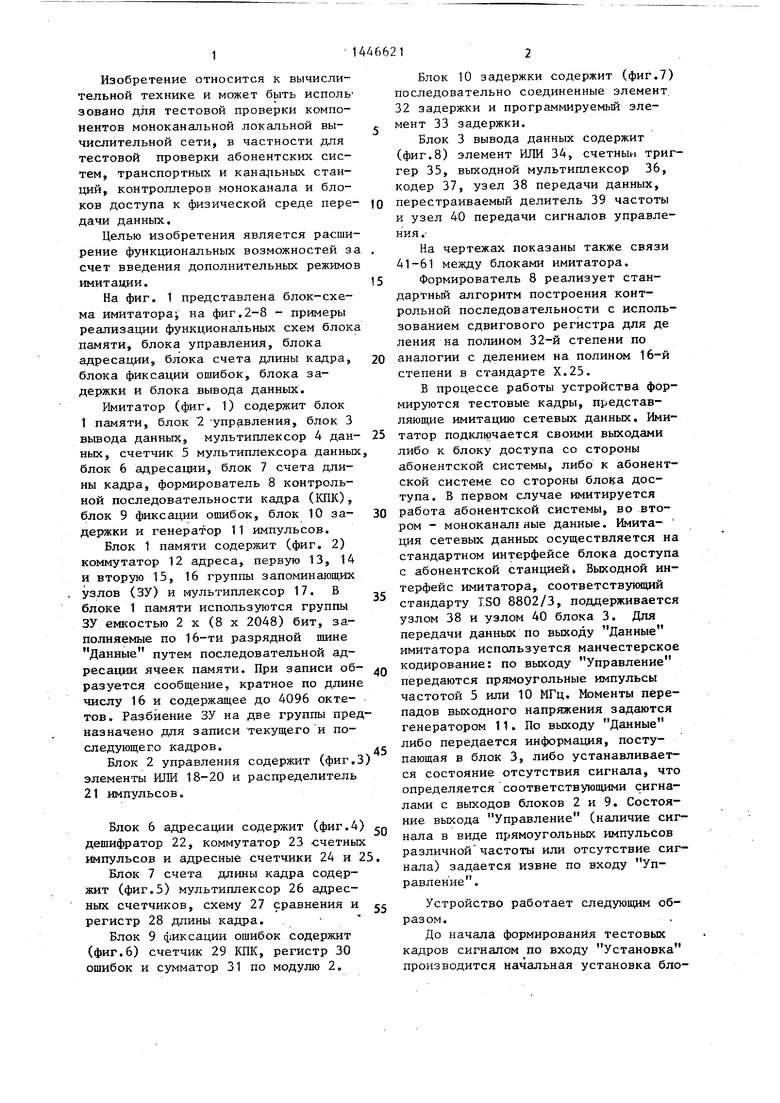

Блок 6 адресации содержит (фиг.4) дешифратор 22, коммутатор 23 счетных импульсов и адресные счетчики 24 и 2

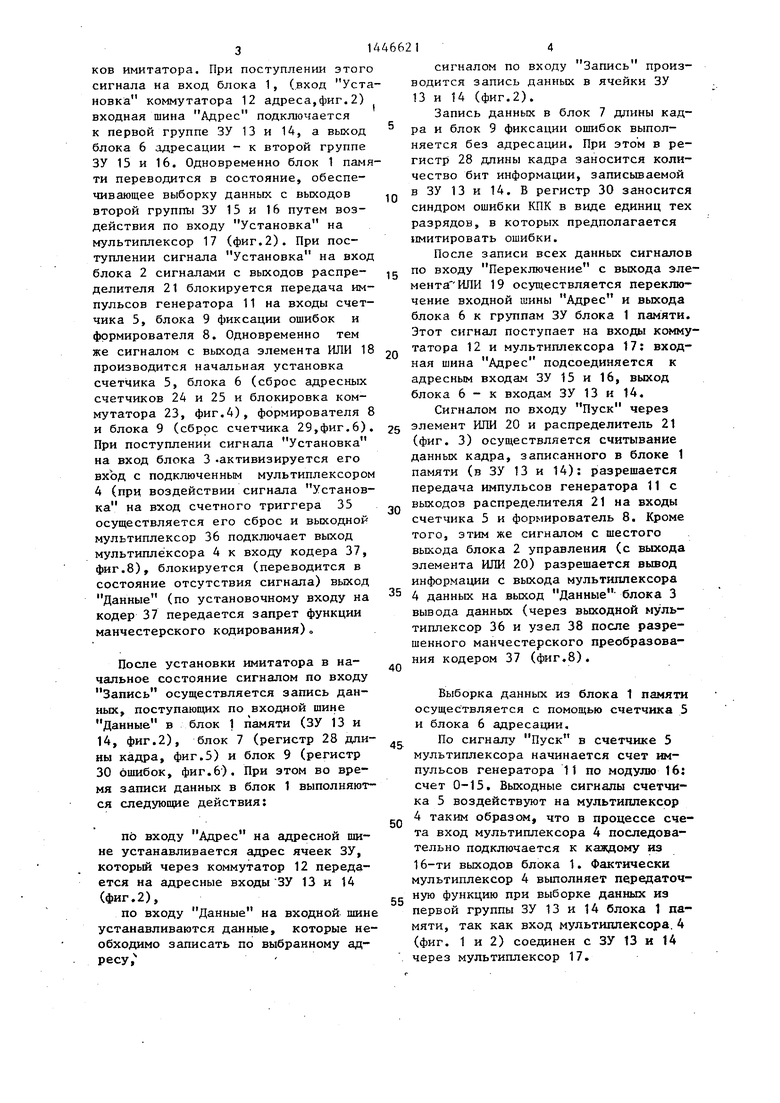

Блок 7 счета длины кадра содержит (фиг.З) мультиплексор 26 адресных счетчиков, схему 27 сравнения и регистр 28 длины кадра.

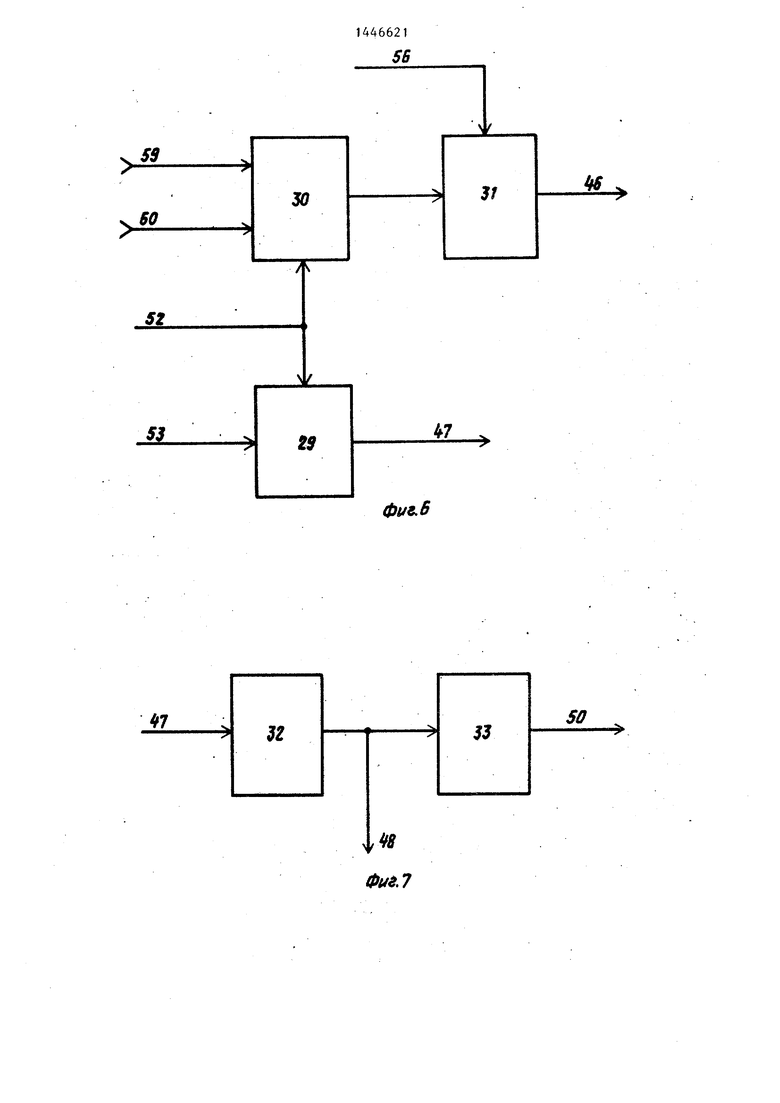

Блок 9 фиксации ошибок содержит (фиг.6) счетчик 29 ЮЖ, регистр 30 ошибок и сумматор 31 по модулю 2.

5

0

5 0

Q с

п

г

5

Блок 10 задержки содержит (фиг.7) последовательно соединенные элемент 32 задержки и программируемый элемент 33 задержки.

Блок 3 вывода данных содержит (фиг.8) элемент ИЛИ 34, счетный триггер 35, выходной мультиплексор 36, кодер 37, узел 38 передачи данных, перестраиваемый делитель 39 частоты и узел 40 передачи сигналов управления .

На чертежах показаны также связи 41-61 между блоками имитатора.

Формирователь 8 реализует стан- дартньй алгоритм построения контрольной последовательности с использованием сдвигового регистра для де ления на полином 32-й степени по аналогии с делением на полином 16-й степени в стандарте Х.25.

В процессе работы устройства формируются тестовые кадры, представляющие имитацию сетевых данных. Имитатор подключается своими выходами либо к блоку доступа со стороны абонентской системы, либо к абонентской системе со стороны блока доступа. В первом случае имитируется работа абонентской системы, во втором - моноканал ные данные. Имита- ция сетевых данных осуществляется на стандартном интерфейсе блока доступа с абонентской станцией. Выходной интерфейс имитатора, соответствующий стандарту ISO 8802/3, поддерживается узлом 38 и узлом 40 блока 3. Для передачи данных по выходу Данные имитатора используется манчестерское кодирование: по выходу Управление передаются прямоугольные импульсы частотой 5 или 10 МГц. Моменты перепадов выходного напряжения задаются генератором 11. По выходу Данные либо передается информация, поступающая в блок 3, либо устанавливается состояние отсутствия сигнала, что определяется соответствующими сигна лами с выходов блоков 2 и 9. Состояние выхода Управление (наличие сигнала в виде прямоугольных импульсов различной частоты или отсутствие сигнала) задается извне по входу Управление.

Устройство работает следующим образом.

До начала формирования тестовых кадров сигналом по входу Установка производится начальная установка блоков имитатора. При поступлении этого сигнала на вход блока 1, (вход Установка коммутатора 12 адреса,фиг. 2) входная шина Адрес подключается к первой группе ЗУ 13 и 14, а выход блока 6 адресации - к второй группе ЗУ 15 и 16. Одновременно блок 1 памяти переводится в состояние, обеспечивающее выборку данных с выходов второй группы ЗУ 15 и 16 путем воздействия по входу Установка на мультиплексор 17 (фиг.2). При поступлении сигнала Установка на вход блока 2 сигналами с выходов распределителя 21 блокируется передача импульсов генератора 11 на входы счетчика 5, блока 9 фиксации ошибок и формирователя 8. Одновременно тем же сигналом с выхода элемента ИЛИ 18 производится начальная установка счетчика 5, блока 6 (сброс адресных счетчиков 24 и 25 и блокировка коммутатора 23, фиг.4), формирователя 8 и блока 9 (сброс счетчика 29,фиг.6), При поступлении сигнала Установка на вход блока 3 .активизируется его вход с подключенным мультиплексором 4 (прн воздействии сигнала Установка на вход счетного триггера 35 осуществляется его сброс и выходной мультиплексор 36 подключает выход мультиплексора 4 к входу кодера 37, фиг.8), блокируется (переводится в состояние отсутствия сигнала) выход Данные (по установочному входу на кодер 37 передается запрет функции манчестерского кодирования).

После установки имитатора в начальное состояние сигналом по входу Запись осуществляется запись данных поступающих по входной шине Данные в блок 1 памяти (ЗУ 13 и 14, фиг.2), блок 7 (регистр 28 длины кадра, фиг.5) и блок 9 (регистр 30 ошибок, фиг.6). При этом во время записи данных в блок 1 выполняются следующие действия:

по входу Адрес на адресной шине устанавливается адрес ячеек ЗУ, который через коммутатор 12 передается на адресные входы ЗУ 13 и 14 (фиг.2),

по входу Данные на входной шине устанавливаются данные, которые необходимо зависать по выбранному адресу,

0

5

сигналом по входу Запись производится запись данных в ячейки ЗУ 13 и 14 (фиг.2).

Запись данных в блок 7 длины кадра и блок 9 фиксации ошибок выполняется без адресации. При этом в регистр 28 длины кадра заносится количество бит информации, записьтаемой в ЗУ 13 и 14. В регистр 30 заносится синдром ошибки КПК в виде единиц тех разрядов, в которых предполагается имитировать ошибки.

После записи всех данных сигналов по входу Переключение с выхода элемента ИЛИ 19 осуществляется переключение входной шины Адрес и выхода блока 6 к группам ЗУ блока 1 памяти. Этот сигнал поступает на входы коммутатора 12 и мультиплексора 17; входная шина Адрес подсоединяется к адресным входам ЗУ 15 и 16, выход блока 6 - к входам ЗУ 13 и 14.

Сигналом по входу Пуск через элемент ИЛИ 20 и распределитель 21 (фиг. 3) осуществляется считывание данных кадра, записанного в блоке 1 памяти (в ЗУ 13 и 14): разрешается передача импульсов генератора 11 с выходов распределителя 21 на входы счетчика 5 и формирователь 8. Кроме того, этим же сигналом с шестого выхода блока 2 управления (с выхода элемента ИЛИ 20) разрешается вывод информации с выхода мультиплексора 4 данных на выход Данные блока 3 вывода данных (через выходной мультиплексор 36 и узел 38 после разрешенного манчестерского преобразования кодером 37 (фиг.8).

5

0

0

50

5

Выборка данных из блока 1 памяти осуществляется с помощью счетчика 5 и блока 6 адресации.

По сигналу Пуск в счетчике 5 мультиплексора начинается счет импульсов генератора 11 по модулю 16: счет 0-15. Выходные сигналы счетчика 5 воздействуют на мультиплексор 4 таким образом, что в процессе счета вход мультиплексора 4 последовательно подключается к каждому из 16-ти выходов блока 1. Фактически мультиплексор 4 выполняет передаточную функцию при выборке данных из первой группы ЗУ 13 и 14 блока 1 памяти, так как вход мультиплексора.4 (фиг. 1 и 2) соединен с ЗУ 13 и 14 через мультиплексор 17.

5

Адреса выбираемых данных из указанной группы ЗУ блока 1 задаются блоком 6 с помощью адресных счетчиков 24 и 25 (фиг.4), выходы которых соединены через коммутатор 12 адреса блока 1 памяти с адресными входами соответствующих ЗУ 13 и 14 (фиг.2). Переключение адресных счетчиков 24 и 25 и, следовательно, смена адресации ЗУ 13 и 14 осуществляется через коммутатор 23 сигналами в виде выходных 1мпульсов дешифратором 22 при соответствукяцем счете 12 и 14 счетчика 5, причем первьм переключается адресный счетчик 24, так как, коммутатор 23 запускается импульсом, выделяемым на выходе дешифратора 22 : при счете восемь счетчика 5 (снимается блокировка кс 1мутатора 23, сделанная сигнале Установка). Помимо упсмянутых импульсов 22 выделяет в виде выходного сигнала также импульс При. счете О счетчика 5, который совместно с шу1пульсом счета 8 поступает на мультиплексор 26 (фиг.5).

Таким образом, выборка данных из блока 1 памяти носит циклический характер. Цикл состоит из 16-ти тактов восемь тактов (счет 0-7) для выборки восьми битов ЗУ 13 и восемь тактов (счет 8-13) для выборки восьми битов ЗУ 14. Смена адреса ячеек ЗУ 13 производится во зрезля считывания данных ЗУ 14 и наоборот.

Битовый поток, образуемый на выходе мультиплексора 4 данных, поступав ет на вход формирователя 8 и блок 3 вывода данных. Блок 3 (фиг.8) обеспечивает передачу информациичерез выходной мультиплексор 36, кодер 37 и узел 38 на выход Данные имитатора. Кодер 37 реализует манчестерское кодирование двоичной последовательности, поступающей с выходного мультиплексора 36J моменты возможных перепадов значений сигнала в манчестерском коде задаются генератором 11 импульсов. Помимо кодера 37 импульсы генератора 11 частотой 20 МГц подаются также на перестраи- ваемьй делитель 39 частоты, который в зависимости от сигналов по входу Управление выдает прямоугольные импульсы частотой 10, 5 или О.МГц. Узел 38 и узел 40 осуществляют преобразование уровней и гальваническую развязку соответствующих сигналов

466216

согласно стандарту 150 на интерфейсе с блока доступа с абонентской системой.

5 Формирователь 8 переводится битовой последовательностью с выхоМа мультиплексора 4 в состояние, отвечающее расчетному значению, вычисляемому по алгоритму определения конт10 рольной последовательности кадра в стандарте ISO 8802/3. Расчет КПК производится по известной схеме циклического кодирования путем деления на образующий полином 32-й степени,

15 Функция деления входного номинала (двоичной последовательности на выходе мультиплексора 4) обеспечивается тактовыми импульсами и приводит к образованию контрольного кода, яв20 ляющегося 32-разрядаьм остатком от производимого полиноминального деления. Сформированный таким способом код сохраняется до поступления сигнала с выхода блока 7.

25 Битовый поток на выходе мультиплексора 4 прерывается по сигналу блока 7. В предлагаемс Имитаторе длина кадра ограничена только сверху 4096 байтами. Отсутствие даугих 30 ограничений позволяет менять длину кадра от теста к тесту в широких пределах. Информация о числе бит, подлежащих передаче, записывается в блок 7 во время записи данных и в

35 процессе передачи даншлх кадра это число сравнивается с другим числсж, соответствуияяз текущему значению количества переданных бит. Число пе- редан1шк бит определяется в блоке 7

40 в зависимости от значения сигналов, поступающих с выходов счетчика 5 и блока 6. Информация о числе бит, подлежащих передаче, записывается в регистр 28, младвше разряды текущего

45 числа переданных бит задаются счетчиком 5, разрядные выходные сигналы которого поступают на схему 27 сравнения, а старшие разряды числа передающих бит задаются мультиплексоре 26.

50 При выделении счета О счетчика 5 де- ши атором 22 (ф1г.4) в соответствии с упомянучъм 16-ти-тактным циклом к схеме 27 сравнения подключается адресный счетчик 24 (фиг.4), а при вы55 делении счета 8 мультиплексор 26 переключается на пересылку данных адресного счетчика 25. Таким образомj четьфе младших разряда показывают те кущее число бит данных по модулю 16;

двенадцать старших разрядов определяют число 16-ти тактных циклов. В сумме образуется длина переданного кадра.

При равенстве текущего и заданного значений у1ины кадра с выхода схе мы 27 сравнения (фиг.5) поступает сигнал на входы блока 2, блока 3 и формирователя 8. При этом формирова тель 8 прекращает расчетные функции по определению КПК, переходя из состояния вычисления в состояние вывода контрольного кода в блоке 3 вьшода данных прекращается прием данных с выхода мультиплексора 4 и подключается выход сумматора 31 (фиг. 6) блока 9, В блоке 2 при поступлении сигнала с выхода блока 7 на вход распределителя 21 (фиг.З) блокируется подача импульсов генератора 11 на счетчик 5, в результате чего прекращается выборка данных из блока 1 памяти (из ЗУ 13 и 14, фиг. 2); выход генератора 11 (через распределитель 21) коммутируется на вход блока 9, в котором определяется тестовая контрольная последовательность (суммарный сигнал контрольных значений и ошибок) и ее длина. Импульсы по линии 52 поступают на входы счетчика 29 и регистра 30. Содержание регистра 30 ошибок, заданное во время записи данных, сдвигается и поступает в последовательном виде на сумматор 31. На другой вход сумматора 31 поступает контрольная последовательность с выхода формирователя 8 после прекращения в нем расчета КПК по сигналу с выхода блока 7. Вывод контрольного кода из формирователя 8 осуществляется в последовательном виде под воздействием тех же импульс.ов, поступающих с выхода блока 2, которые предназначались ранее для расчета КЖ. Суммарный сигнал контрольных значений и ошибок с выхода сумматора 31 по линии 46 поступает на вход блока 3 вывода данных и далее на его выход Данные. Одновременно в счетчике 29 производится подсчет длины контрольной последовательности. После поступления 32-х бит, т.е. 32г-х импульсов с выхода распределителя 21, на выходе счетчика 29 образуется сигнал конца контрольной-последовательности, которьй поступает на входы блока 2, блока 3 вывода данных и блока 10. При этом, в блоке 2

10

20

466218

сигнал конца КПК блокирует генерацию импульсов генератора 11 (на выходах распределителя 21 импульсов, фиг.З) в блоке 3 вывода данных блокируется выход Данные (по линии 47 сигнал конца КПК поступает на вход кодера 37, который прекращает функцию манчестерского кодирования).

В блоке 10 задержки (фиг.7) величина задержки элемента 32 выбирается с учетом минимального межкадрового интервала, величина задержки элемента 33 изменяется. Задержанный: элемен15 том 32 сигнал конца КПК (по линии 48) посту пает на вход блока 3 вывода данных и вновь активизирует его вход, соединенный с выходом мультиплексора 4 (через элемент ИЛИ 34 этот сигнал переключает счетный триггер 35, сигнал с выхода которого воздействует на выходной мультиплексор 36). В блоке 2 (фиг.З) задержанный элементом 32 сигнал используется для перевода

25 имитатора в начальное состояние готовности к передаче следукяцего кадра, поступая с выхода элемента ИЛИ 18 на входы счетчика 5, блока 6, блока 9 и формирования 8 КПК, задержанный

30 сигнал конца КПК осуществляет сброс счетчика 5 мультиплексора данных, сброс адресных счетчиков 24 и 25 и блокировку коммутатора 23 блока 6 адресации (фиг. 4), сброс счетчика 29

-jg блока 9 (фиг. 6), а также устанавливает начальное состояние формирователя 8. Этим же сигналом с выхода элемента ИЛИ 18 блокируются выходы распределителя 2.1 импульсой (г.З).

40 Кроме того, задержанный элементом 32 (фиг.7) сигнал через элемент ИЛИ 19 (фиг. 3) поступает на вход режима блока 1 памяти (фиг.2) и воздействует на коммутатор 12 и мультиплек45 сор 17, подготавливая выборку данных из ЗУ 13 и 16 по адресам, определяемым блоком 6. Момент начала передачи очередного кадра определяется задержкой сигнала конца КПК программируемым элементом 33 задержки, с выхода которого он поступает на вход элемента ИЛИ 20 (фиг.З). Действие этого задержанного сигнала аналогично первоначальному запуску имитатора сигналом по входу Пуск.

Таким образом, имитатор йодготов- лен к передаче нового тестового кадра, содержащего в ЗУ 15 и 16 блока 1- (фиг.2). Запись данных этого.кадра.

50

55

а также запись данных о числе бит в блоке 7 (в регистр 28, фиг,5) и дан- Яых об ошибках КПК, вносимых в блок 9 (регистр 30, фиг.6), осуществляется во время считьгаания первого кадра до момента появления сигнала на выходе элемента 32 задержки (фиг. 7). И наоборот, во время считьшания очередного кадра, содержащегося в ЗУ 15 и 16, производится запись данных следующего кадра в ЗУ 13 и 14 (фиг,2), а также запись данных, сопутствующих этому кадру.

Ф

о р мула изобретения

Имитатор для тестирования компонентов моноканальной локальной вычислительной сети, содержащий блок памяти, перввй адресный вход, информационный вход и вход строба записи которого являются соответственно входами Адрес,Данные, и Запись имитатора, а вход режима соединен с первым.выходом блока управления, вто рой и третий выходы которого соединены соответственно с установочным и тактовым входами формирователя контрольной последовательности кадра, блок вывода данных, первый и второй выходы которого являются соответственно выходами Данные и Управление имитатора, а тактовый вход и вход задания коэффициента пе- ресчета соответственно соединены с выходом генератора импульсов и управляющим входом имитатора, первый режимный вход и вход пуска блока управления являются соответственно входами сигналов Переключение и Пуск имитатора, а установочный вход соединен с установочным входом устройства и установочными входами блока памяти и блока.вывода данных, отличающийся тем, что, с целью.расширения функциональньк возможностей за счет введения дополнительных режимов имитации, в имитатор введены блок адресации, блок счета длины кадра, мультиплексор данных, блок задержки, блок фиксации ошибок и счетчик мультиплексора данных, причем выход генератора импульсов подключен к тактовому вхо

5

0

5

ду блока управления, четвертый, пятый и шестой выходы которого соединены соответственно со счетным входом счетчика мультиплексора данных, тактовым входом блока фиксации ошибок и разрешающим входом блока вывода данных, первый и второй информационные входы и стробирующий вход которого соединены соответственно с выходом мультиплексора данных и первым и вторым выходами блока фикса1 ии ошибок,«первьй и второй информационные входы и вход строба записи которого подключены соответственно к выходу формирователя контрольной последовательности кадра и к входам Данные и Запись имитатора, а установочный вход - к второму выходу блока управления и установочным входам блока адресации и счетчика мультиплексора данных, выходом соединенного с адресным входом мультиплексора данных, информационным входом блока адресации и первым информационньм входом блока счета длины кадра, второй информационный и синхронизирую-, щий входы которого соединены соответственно с первым и вторым выхода- 0 ми блока адресации, а третий информационный вход и вход строба записи - соответственно с входами Данные и Запись га-1итатора, выход блока |Счета длины кадра подключен к второму входу режима блока управления и входам режима выводного блока и формирователя контрольной последовательности кадра, информационным входом соединенного с выходом мультиплексора данных, группа информационных входов которого соединена с группе выходов блока памяти, вторым адресным входом подключенного к первому выходу блока адресации, входы строба конца контрольной последовательности, начала цикла и конца цикла блока управления соединены соответственно с вторьи выходом блока фиксации ошибок и первым и вторым выходами блока задержки, вход и второй выход которого соединены соответственно с вторым выходом блока фиксации ошибок и синхронизирую1цим входом блока вывода данных.

35

40

45

0

JtoMM&s AjAMMiWMUf

S3

SS

57

К

2

:}

лг

п

«4

55

27

9S

29

во

У)

IL

Z9

4-7

J2

1446621

ss

3f

47

IJ

Л7

Фи.7

1 Г

Н

Ъ8

Лан

fHbie

w(,i npae e//ue

I J- .%7fФиг, 8

| Пелипейко В.А | |||

| и др | |||

| Тестовое диагностирование логических структур | |||

| Рига: Зинатне, 1986 | |||

| Патент США 4393498, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Гребенчатая передача | 1916 |

|

SU1983A1 |

Авторы

Даты

1988-12-23—Публикация

1987-06-02—Подача