ных сигналов), коммутатор 3, наборное поле 4, логические элементы 5 и блоки 6 памяти. Пульт 1 содержит генератхф Одиночных импульсов, генератор 8 (непрерывной последовательности импульсов), генератор 9 (нуля), переключатель 10 po/i работ, управляющую клавиатуру 11 и pismCTp 12. Логический элемент 5 содержит коммутаторы t3. 14, логический удел 15 и индикатор 16. Блок

6 содержит коммутаторы 17,18, элемент 19 памяти, индикаторы 20...23, элемент 2ИИЛИ 24 и блок 25 сравнения. Элемент 24 содержит инвертор 26, элементы И 27, 28 и элемент ИЛИ 29. Блок 25 содержит элементы НЕ 30, 31 и элементы И-НЕ 32...37. Индикатары20...23конструктивноОбъединены В узел 38 индикации. Коммутаторы 3,13,14, 17, 18 объединены в наборном поле 4. 2 ил.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ ОБУЧЕНИЯ ОСНОВАМ ВЫЧИСЛИТЕЛЬНОЙ ТЕХНИКИ | 1991 |

|

RU2011230C1 |

| Устройство для обучения основам вычислительной техники | 1990 |

|

SU1781692A1 |

| Устройство для обучения основам вычислительной техники | 1988 |

|

SU1564682A1 |

| Устройство для обучения основам вычислительной техники | 1990 |

|

SU1775728A1 |

| Устройство для обучения основам вычислительной техники | 1986 |

|

SU1394222A1 |

| Устройство для обучения операторов | 1990 |

|

SU1746393A1 |

| СТЕНД ДЛЯ ИЗУЧЕНИЯ СРЕДСТВ ВЫЧИСЛИТЕЛЬНОЙ ТЕХНИКИ | 2002 |

|

RU2237927C2 |

| Устройство для обучения операторов автоматизированных систем управления | 1985 |

|

SU1257692A1 |

| Устройство для обучения | 1988 |

|

SU1663618A1 |

| Устройство для оценки профессиональной пригодности операторов | 1990 |

|

SU1714652A1 |

Изобретение относится к учебно-лабораторному оборудованию и может быть использовано в учебном про^цессе, ^также при моделировании и отладке дискретных устройств, построенных на интегральных микросхемах. Целью изобретения является расширение дидактических возможностей устройства и сокращение затрат времени на анализ дискретного автомата. Устройство для обучения основам вычислительной техники содержит пульт 1 оператора, блок 2 предъявления информации (внешних вход-сос:^..!!:^Ji9 L^.J fj4>&^ О О О

Изобретение относится к учебно-лабораторному оборудованию и может быть использовано в учебном процессе, а также при моделировании и от/шдке дискретных устройств, построенных йа интегральных микросхемах.

Известно устройство для обучения основам вычислительной техники, со/ ржа|цее пульт оператора, счетчик, дешифратор, распределитель импульсов, коммутатор и сдвигающий регистр.

Недостатком такого устройства являются низкие дидактические возможности, так как оно не позволяет наглядно исследовать нерегулярные дискретные устройства, получаемые в результате логического синтеза.

Известна также модулирующая установка, состоящая из генератора одиночных импульсов и генератора непрерывной последовательности импульсов пульта оператора, входного регистра, наборного поля, модулей логических элементов и элементов памяти, а также индикаторов.

Недостатком такого устройства являют ся низкие дидактические возможности за счет отсутствия индикации последующих и предыдущих состояний элементо1в памяти.

Наиболее близким к изобретению является устройство для обучения основам вычислительной техники, содержащее пульт оператора, блок предъявления информации (внешних входных сигналов), коммутатор, наборное поле, логические элементы и блоки памяти. Пульт оператора,содержит генератор одиночных импульсов, генератор непрерывной последовательности импульсов, генератор нуля, переключатель, управляющую клавиатуру и регистр. Логический Цемент содержит два коммутатора, логический узел и индикатор. Блок памяти содержит два коммутатора, элемент памяти, два индикатора и узел прогнозирования, который содержит инвертор, два элемента И и элемент И Л И.

Недостатком та кого устройства являются низкие дидактические возможности, а

также большие затраты времени на анализ синтезированного дискретного автомата.

Цель изобретения - расширение дидактических возможностей и повышение быстродействия устройства с сокращением затрат времени на анализ дискретного автомата.

Поставленная цель достигается тем, что в устройство для обучения основам вычислительной техники, содержащее пульт оператора, первый выход которого соединен с соответствующими входами блока предъявления информации и наборного поля, второй выход с соответствующим входом наборного поля, а выходы группы с соответствующими входами группы блока предъявления информации и с соответствующими входами первой группы наборного поля, входы второй группы и выходы первой группы которого являются соответствующими входами и выходами устройства, элемент памяти, узел индикации и элемент , причем выходы второй группы наборного поля соединены с соответствующими входами элемента памяти, единичный выход которого соединен с первым входом узла индикации и с первым входом наборного поля, а инверсный выход подключен к второму входу наборного поля, выход элемента 2Й-ИЛИ соединен с вторым входом узла индикации и третьим входом наборного поля, г /}ервый, второй, третий и четвертый входы соответственно с единичным и нулевым выходами и с (- и К-входами элемента памяти, введены два элемента НЕ и шесть элементов И-НЕ, причем входы первого и второго элементов НЕ соединены с I- и Квходами элемента памяти соответственно, первые входы первого и четвертого элементов И-НЕ соединены с t- и К-входами элемента памяти соответственно, первые входы рторого и третьего элементов И-НЕ соединены с единичным выходом элемента памяти. Нулевой выход которого подключен к вторым входам второго и четвертого элементов И-НЕ, выходы первого и второго

элементов И-НЕ соединены с первым и вторым входами пятого элемента И-НЕ соответственно, а вы(оды третьего и четвертого элементов И-НЕ подключены к первому и второму Входам шестого элемента И-НЕ соответственно, выходы пятого и шестого элементов И-НЕ соединены с третьим и четвертым входами узла индикации соответственно.

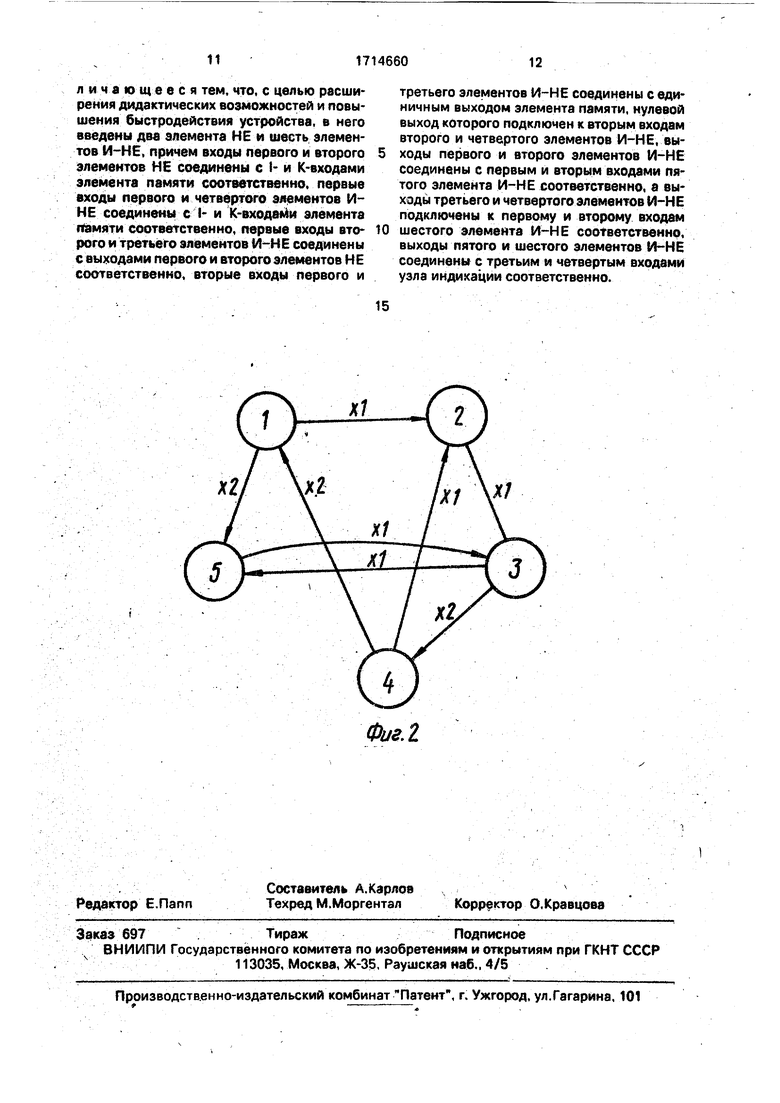

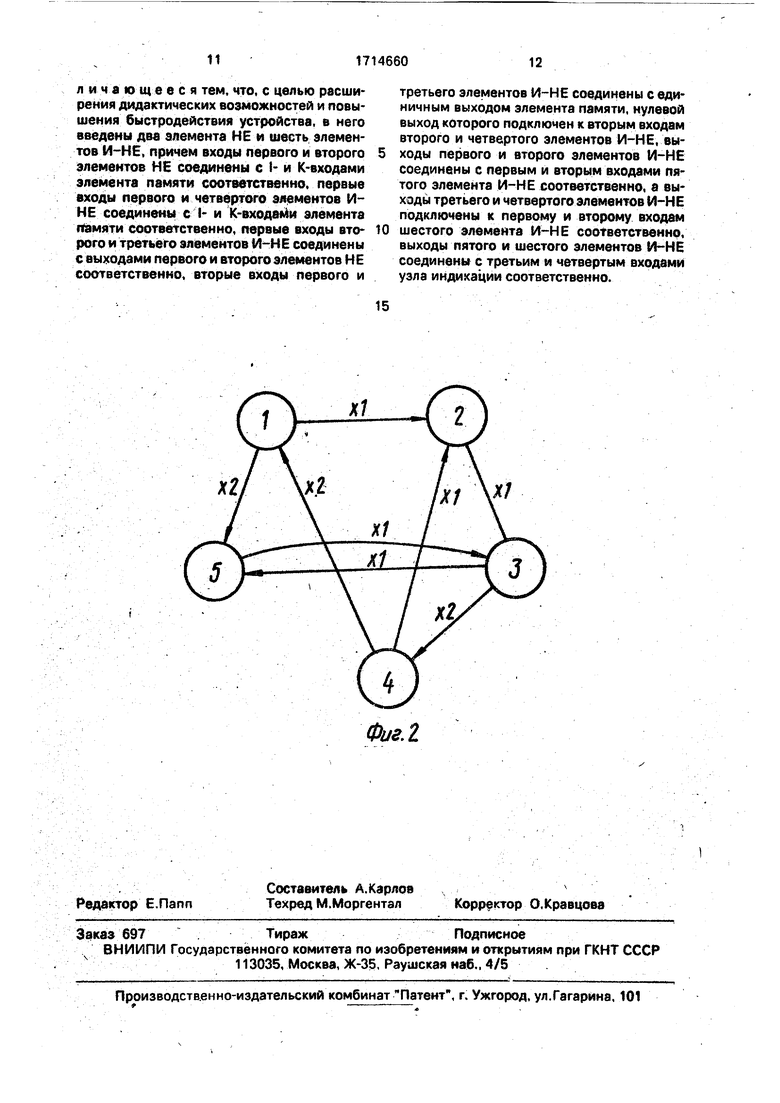

На фиг. 1 изображена функциональная схема предлагаемого устройства для обучения основам вычислительной техники; на фиг. 2 - граф автомата, по условиям задания которого описывается дискретное устройство, синтезированное обучаемым.

Устройство для обучения основам вычислительной техники содержит пульт 1 оператора, блок 2 предъявления информации (внешних входных сигналов), коммутатор 3, наборное поле 4, логические элементы 5 и блоки 6 памяти.

Пульт 1 содержит генератор 7 одиночных импульсов, генератор 8 непрерывной последовательности импульсов, генератор 9 нуля, переключатель 10 рода работ, управляющую клавиатуру 11 и регистр 12.

Логический Элемент 5 содержит коммутаторы 13 и 14, логический узел 15 и индикатор 16.Блок 6 содержит коммутаторы 17 И 18, элемент 19 памяти,индикаторы 2(-23, элемент 2И-ИЛИ 24 и блок 25 сравнения. Злемент24 содержит инвертор 26, Элементы И 27 и 28 и элемент ИЛИ 29. Блок 25 содержит элементы НЕ 30 и 31 и элементы И-НЕ 3237. Индикаторы 20-23 конструктивно обьединены в узел 38 индикации. Коммутаторы 3, 13, 14, 17 и 18 объединены в наборном поле 4.

Пульт 1 оператора предназначен для управления работой устройства и конструктивно выполнен в виде пластикового корпуса.

Блок 2 предъявления информации предназначен для отображения только входных сигналов и сигналов синхронизации, т.е. внешних входных сигналов моделируемых конечных автоматов, и может быть выпол нен, например, на светодиодах АЛС102.

Коммутатор 3 предназначен для коммутации входных сигналов и сигналов синхронизации и может быть выполнен, например, на контактах штепсельных разъемов.

Наборное лоле 4 предназначено для размещения и подачи питания на элементы 5 и блоки б и может быть реализовано на контактах штепсельных разъемов, к которым подключаются вилки блоков 5 и б.

Логические элементы 5 предназначены для размещения коммутаторов, логических

узлов и индикаторов и конструктивно выполнены в виде пластикового корпуса, снабженного, кроме контактов входного и выходного полей, клеммами подачи питания, с помощью -KOTOpbix и производится установка их на наборное поле 4, имеющее специальные гнезда. На верхней крышке модуля изображено условно-графическое изображение Микросхемы.

Блоки б предназначены для размещения коммутаторов 17 и 18. элементов 19 памяти, элемента 24, блока 25 и узла 38 индикации и конструктивно выполнены аналогично логическим элементам 5.

Генератор 7 предназначен для формирования Одиночных импульсов и их подачи на элементы 19 и может быть реализован, например в виде кнопки без фиксации, подключенной к шине -, а выходным кОнтактом,- к входному контакту переключателя 10.

Генератор 8 предназначен для формирования прямоугольных импульсов, амплитудой, равной напряжению логической 1 и

может быть реализован, например, на микросхеме 155ЛАЗ.

Генератор 9 предназначен для установки элементов 19 по входам в состояние, соответствующее коду первой строки таблицы

переходов-выходов и может быть реализр-. ван на ограничительном резисторе, подсоединенном одним концом к шине -, а другим к выходу пульта 1 оператора.

Переключатель 10 предназначен для переключения режима проверки выполнения заданных условий работы синтезированного автомата с ручного на автоматический и обратно и может быть реализован, например, на микротумблере МТ 1.

Управляющая клавиатура 11 предназначена для задания входного сигнала и представляет собой регистр кнопок сфиксацией.

Регистр 12 предназначен для устранения дребезга контактов управляющей клавиатуры 11 и содержит триггеры по числу разрядов управляющей клавиатуры 11,

Коммутатор 13 предназначен для коммутации логических элементов при решении задачи логического синтеза дискретных устройств и может быть реализован, например, на гнездах штепсельных разъемов.

Коммутатор 14 предназначен для коммутации выходов лоп ческих узлов 15 при

наборе функциональной схемы и может

быть реализован, например, на гнездах

штепсельных разъемов.

Логический узел 15 предназнзчеи для набора логического преобразователя

исследуемого дискретного устройства, представляющего собой совокупнЬсть комбинационных бесконтактных дискретных элементов. Собранный логический преобразователь служит для управления элементами памяти дискретного устройства и формирования внешних выходных сигналов. Логический узел может быть реализован, например, на интегральных микросхемах 155ЛА1, 155ЛА2; 155ЛАЗ, 155ЛР1, 155ЛР2ИДР.

Индикатор 16 предназначен для отображения выходного состояния каждого из узлов 15 и может быть реализован, например, на светодиодахАЛС102.

Кс ммутатор 17 предназначен для коммутации входов элементов 19 памяти при наборе разработанной функци19налы1ой схеиы и может быть реализован, например, на гнездах штепсельных разъемов.

Коммутатор 18 предназначен для коммутации выходов текущего и прогнозируемого состояний элементов 19 памяти и может быть реализован, например, на гнездах штепсельных разъемов.

Коммутаторы 3,13, 14,17 и 18 конструктивно могут быть выполнены в виде гнезд и штырей штепсельных разъемов, например, типа 12РБ60-А,В и проводов линии связи, к концам которых припаяны штыри.

Элемент 19 предназначен для реализации разработанной функциональной схемы, В качестве элемента 19 можно использовать, например, 1К-триггер 155ТВ1.

Индикатор 20 предназначен для отображения единичного состояния элементов 19 памяти в текущем такте и может быть р еалиэован, например, на светоДиоде АЛС102,

Индикатор 21 предназ начен для отображения единичного состояния элементов 19 памяти в прогнозируемом (следующем) такте и может быть реализован, например, на еветоДиоДе АЛ С102.

Индикатор 22 предназначен для отображения единичного состояния элементов 19 памяти в предыдущем такте и может быть реализован, например на светодиоде

АЛС102.

Индикатор 23 предназначен для отображения нулевого состояния элeмeнtoв 19 памяти в предыдущем такте и может быть реализован, например, на светодиоде АЛС102.

Элемент 2И-ИЛИ 24 предназначен для прогнозирования состояния элементов 19.

Блок 25 сравнения предназначен для определения состояния элементов 19 памяти в предыдущем такте.

Узел 38 индикации конструктивно o6i eдиняет индикаторы 20-23, отображающие состояния элемента 19 памяти в текущем, следующем и предыдущем тактах,

Соединения осуществляются соединительными проводами, которые на фиг. 1 не показаны,.

Устройство для обучения основам вычислительной техники работает следующим

0 образом.

Обычный режим работы. Обучаемый, решив задачу логического синтеза функциональной схемы по заданным условиям работы, набирает ее на наборном поле 4 с помощью соединительных проводов (не показаны), соединяющих коммутаторы 3, 13,14, 17 и 18 в соответствии с полученной функционально1й схемой.

Для построения математической моде

0 ли синтезированного автомата обучаемый при помощи генератора 9 нуля устанавливает элементы 19 по входам в состояние, соответСтвующее коду первой строки таблицы переходов-выходов. Это состояние в двоич5 ном коде отображается на индикаторах 20. Затем обучаемый подает входные сигналы при помощи управляющей клавиатуры 11, при этом регистр 12 устраняет дребезг контактов клавиатуры и воздействует через

0 блок 2, который отображает двоичный код входного сигнала на внешние входы автомата, подключенные k коммутатору 3. При этом элементы 2И-ИЛИ 24 воспринимают входные и выходные сигналы элементов 19. Инвертор 26 инвертирует сигнал с входа элемента 19, элемент 27 производит операцию логического умножения над сигналами, поступающими с выхода инвертора 26 и выхода элемента 19. Элемент 28 производит

0 операцию логического умножения над сигналами элемента 19. Элемент 29 произврдит операцию логического сложения сигналов, поступающих с выходов элементйв27и28.

5 Реализованная функция принимает значение логического нуля в том случае, если э лемент 19 в последующем такте установится в нулевое состояние, при этом индикатор 21 не горит, а значение логической единицы в противном случае, при этом индикатор 21 горит. Поэтому, считывая информацию по индикаторам 21, сг&учаемый получает двоичну1О информацию, отмечаемую в каждой клетке таблицы переходов-оы5 ходов без дополнительных операций, только путем изменения комбинации входных сигналов. Это позволяет получить математическую модель синтезированного автомата, во время построения кото|Х й обучаемый производит отладку автомата, используя дополнительно индикаторы 16, отображающие выходные состояния каждого из узлоё 15. Затем производится пррвврка выполнения заданных условий работы «синтезированного автомата в синхронном ручном и автоматическом режимах, используя генератор 7 одиночных импульсов, генерато|5 8 и переключатель 10, подавая сигналы синхронизации на входы синхронизации эле ментов 19 памяти с коммутатора 3,

Таким образом, работа предлагаемого устройства происходит аналогично работе известного.

Режим определения предыдущего состояния эл.ементов памяти.

Обучаемый, набрав на наборном поле 4 функциональную Схему разработанного ди скретного устройства и построив его математическую модели в соответствии с обычным режимом работы, подает входные сигналы при помощи управляющей клавиатуры 11, при этом регистр 12 устраняет дребезг контактов клавиатуры и воздействует через блок 2, который отображает двоичный код входного сигнала на внешние входы автомата, подключенные к коммутатору 3. При этом блоки 25 воспринимают их входные и выходные сигналы. Инверторы И-НЕ32 и35 производят операдинэ логического умно кёиия.и инвертирования над сигналами, поступающими с 1-входа и прямого выхода, а также К-входа и инверсного выхода элемента 19 памяти соответственна, элементы ИНЕ 33 и 34 производят операц ию логического умножения и инвертироваййя над сигналами, поступающими с выхода элемента НЕ 30 и инверсного выхода элемента 19 памяти, а также с выхода элемента НЕ 31 и прямого выхода элемента 19 памяти соответственно. Элементы И-НЕ 36 и 37 производят операцию логического yMHOjkeния и инвертирования над сигналами, поступающими с выходов элементов И-НЕ 32 и 33 и И-НЕ 34 и 35 соответстаенно;

Полученная.функция принимает значение логического нуля в том случае, еслив текущем такте элемент 19 памяти находится в нулевом состоянии и на 1- и К-входы подан сигнал логического нуля или же элемент 19 памяти находится в единичном состоянии и на 1-й К-входы подан сигнал логической единицы, при этом индикатор 22 не высвечивается. В то же время индикатор 23 горит, поскольку функция принимает значение логической единицы.,Функция принимает значение логической единицы, если в текущем такте элемент 19 памяти находится в нулевом состоянии и на 1- и К-входы подан ci гнал логической единицы или же элемент 19 памяти находа1

ся в единичном состоянии и на I- и К-входы подан сигнал логического нуля, при этом индикатор 22 высвечивается. В время индикатор 23 не горит, поскЬльку функция принимает значение логического нуля.

Одновременное высвечивание Индикаторов 22 и 23 свидетельствует о том, что 6 предыдущем такте элемент 19 памяти мог находиться как в нулевом, так и единичном состояниях.

И наоборот. Одновременное погасание индикаторов 22 и 23 соответствует выходу из строя элемента 19 памяти.

Считывая информацию ио индикаторам 22 и 23 обучаемый получает двоичную информацию, отмечаемую в каждой клетке таблицы переходов-выходов без дополнительных операций, а Только путем изменения комбинации входных сигналов. Это позволяет получить математическую модель синтезированнЬого автомата, во время построений которой обучаемый производит его отладку, используя дополнительно индикатЬры 20 И 21, а также индикаторы 16, отображающие вь1ходн ые состоя ния каждо го из узлов 15. Затем производится проверка выполнения заданных условий работы синтезированного автомата в синхронном ручном и автоматическом режимах, используя генератор 8 и переключатель 10, п.одавая сигналы синхронизации на входы синхронизации элементов 19 памяти с коммутатора 3.

Формула изобретения

Устройство Для обучения основам вычислительной техники, содержащее пульт оператора, первый выход которого соединен с соответствующими входами блока предъявления информации и наборного поля, второй выход - с соответствующим входом наборнрго лойя, а выходы группы - с соответствующими входами группы блока предъявления информации и с соответствующими входами первой группы наборного поля, входы второй группы и выход1ы первой группы которого являются соответствующи-; мй входами и выходами устройства, элемент памяти, узел индикации и элемент 2И-14ЛИ, причём выходы второй группы наборного поля соединены с соответствующими входами элемента памяти,единичный выход кото рЬго соединен с первым входом узла индикации и с первым входом наборного поля, а нулевой выход подключен к второму входу наборного поля, выход элемента 2 ЛИЛИ соединен с вторым входом узла индикации и третьим входом наборного гюля, а первый, второй, третий и четвертый входы соответственно с единичным и нулевым выходами и I- и К-входами элемента памяти, о тл и ч а ю щ е е с я тем, что, с целью расширения дидактических возможностей и повышения быстродействия устройства, в него введены два элемента НЕ и шесть элементов Й-НЕ, причем входы первого и второго элементов НЕ соединены с t- и К-входами элемента памяти соответственно, первые входы первого и четвертого эл ементов ИНЕ соединены с I- и К-входайи элемента г амяТи соответственно, первые входы второго и третьего элементов соединены с выходами первого и второго элементов НЕ соответственно, вторые входы первого и

третьего элементов И-НЕ соединены с единичным выходом элемента памяти, нулевой выход которого подключен к вторым входам второго и четвертого элементов И-НЕ, выходы первого и второго элементов И-НЕ соединены с первым и вторым входами пятого элемента Й-НЕ соответственно, а выходы третьего и четвертого элементов И-НЕ подключены к первому и второму входам шестого элемента И-НЕ соответственно, выходы пятого и шестого элементов И-НЕ соединены с третьим и четвертым входами узла индикации соответственно.

Фиг. г

| Устройство для обучения основам вычислительнй техники | 1981 |

|

SU1005156A1 |

| Разборный с внутренней печью кипятильник | 1922 |

|

SU9A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| А.Е.Амбросова | |||

| - Харьков | |||

| ^^.'• • ^: • •.; | |||

| •;.-: | |||

| •; ' • , ;Авторское свидетельство СССР № 1394222 | |||

| Разборный с внутренней печью кипятильник | 1922 |

|

SU9A1 |

Авторы

Даты

1992-02-23—Публикация

1990-03-11—Подача