1

(21)4475005/24-24

(22)19.08.88

(46) 15.05.90. Бюл. К 18 (72) В.А.Несмелов, В.И.Назин, С,Ф.Тюрин и В.А.Харитонов

(53)681.3.071 (088.8)

(56)Авторское свидетельство СССР № 1394222, кл. G 09 В 23/48,,1986.

(54)УСТРОЙСТВО ДЛЯ ОБУЧЕНИЯ ОСНОВАМ ВЫЧИСЛИТЕЛЬНОЙ ТЕХНИКИ

(57)Изобретение относится к учебно- лабораторному оборудованию, может быть использовано в учебном процессе, в конструкторских бюро для моделирования и отладки дискретных устройств,

построенных на интегральных микросхемах, и позволяет расширить дидактические возможности и повысить быстродействие устройства за счет уменьшения временных затрат на идентификацию гоночных ситуаций путем введения новой дисциплины - автоматической идентификации гоночных ситуаций. Устройство содержит пульт 1 оператора, блок 2 предъявления информации внешних входных сигналов, коммутатор 3, наборное поле 4, логические элементы 5, блок 6 памяти. Пульт 1 содержит генератор 7 одиночных импульсов, генератор 8 непрерывной последовательности

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для обучения основам вычислительной техники | 1990 |

|

SU1781692A1 |

| Устройство для обучения основам вычислительной техники | 1990 |

|

SU1775728A1 |

| УСТРОЙСТВО ДЛЯ ОБУЧЕНИЯ ОСНОВАМ ВЫЧИСЛИТЕЛЬНОЙ ТЕХНИКИ | 1991 |

|

RU2011230C1 |

| Устройство для обучения основам вычислительной техники | 1990 |

|

SU1714660A1 |

| Устройство для обучения операторов | 1990 |

|

SU1746393A1 |

| Устройство для обучения основам вычислительной техники | 1986 |

|

SU1394222A1 |

| Устройство для обучения | 1983 |

|

SU1273974A1 |

| Устройство для контроля знаний обучаемых | 1981 |

|

SU982063A1 |

| Устройство для тренировки и контроля профессиональных навыков оператора | 1990 |

|

SU1714650A1 |

| Обучающее устройство | 1981 |

|

SU989569A1 |

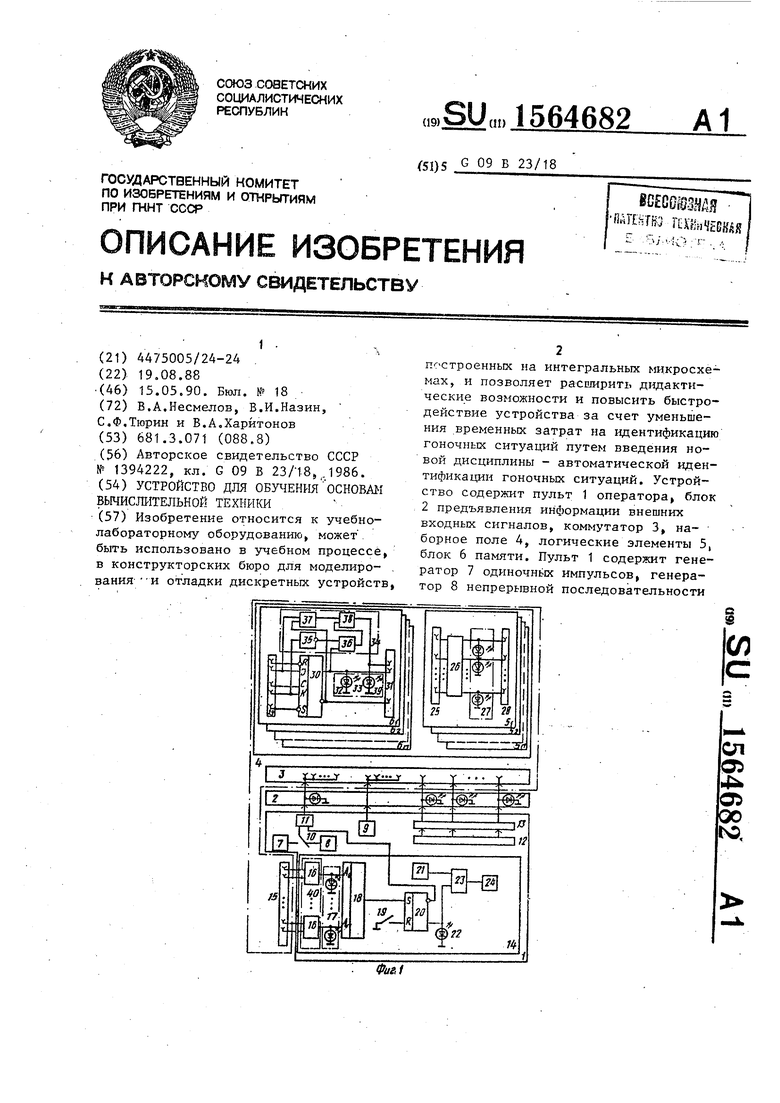

Изобретение относится к учебно-лабораторному оборудованию, может быть использовано в учебном процессе, в конструкторских бюро для моделирования и отладки дискретных устройств, построенных на интегральных микросхемах, и позволяет расширить дидактические возможности и повысить быстродействие устройства за счет уменьшения временных затрат на идентификацию гоночных ситуаций путем введения новой дисциплины - автоматической идентификации гоночных ситуаций. Устройство содержит пульт 1 оператора, блок 2 предъявления информации (внешних входных сигналов), коммутатор 3, наборное поле 4, логические элементы 5, блок 6 памяти. Пульт 1 содержит генератор 7 одиночных импульсов, генератор 8 непрерывной последовательности импульсов, генератор 9 нуля, переключатель 10, элемент И 11, управляющую клавиатуру 12, регистр 13, блок 14 контроля гонок. Блок 14 содержит коммутатор 15, группу элементов 16 сложения по модулю два и группу индикаторов 17, постоянный запоминающий блок 18, переключатель 19, триггер 20, генератор 21 непрерывной последовательности импульсов, индикатор 22, элемент И 23 и блок 24 звуковой сигнализации. Элемент 5 содержит коммутатор 25, логический узел 26, индикатор 27 и коммутатор 28. Блок 6 содержит коммутатор 29, элемент 30 памяти, коммутатор 31, индикаторы 32,33 и узел 34 прогнозирования. Каждый узел 34 содержит инвертор 35, элементы И 36,37, элемент ИЛИ 38. Индикаторы 32 и 33 конструктивно объединены в узел 39 индикации, а элементы 16 - в сумматор 40, 2 ил.

(Л

ел

сь

.Ј 0 00 ГС.

Фи&1

Импульсов, генератор 9 нуты, переключатель 10, элемент И 11, управляющую клавиатуру 12, регистр 13, блок 14 контроля гонок. Блок 14 содержит ком- Мутатор 15, группу элементов 16 ело- жения по модулю два и группу индикаторов 17, постоянный запоминающий блок 18, переключатель 19, триггер 20, генератор 21 непрерывной последо- :зательности импульсов, индикатор 22, элемент И 23 и блок 24 звуковой сигИзобретение относится к учебно- лабораторному оборудованию и может 5ыть использовано в учебном процессе, 1 также в конструкторских бюро для моделирования и отладки дискретных устройств, построенных на интегральных микросхемах.

Целью изобретения является расши- рение дидактических возможностей устройства с сокращением времени на обучение и уменьшением времени идентификации гоночных ситуаций,

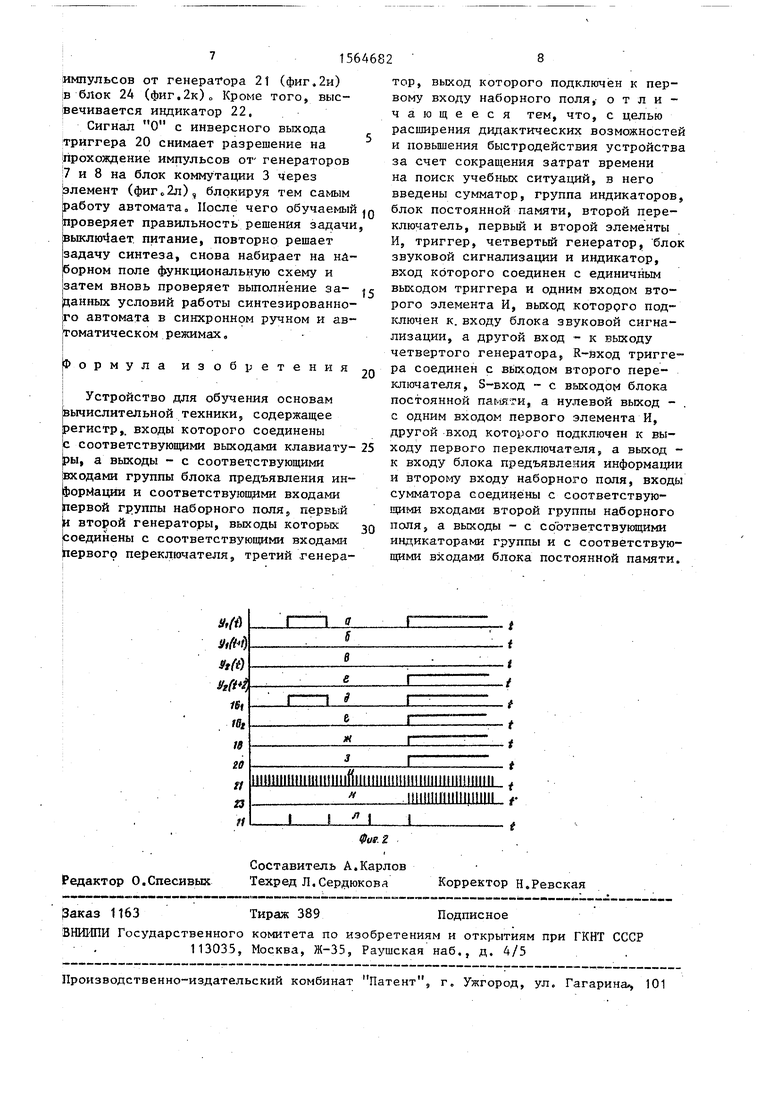

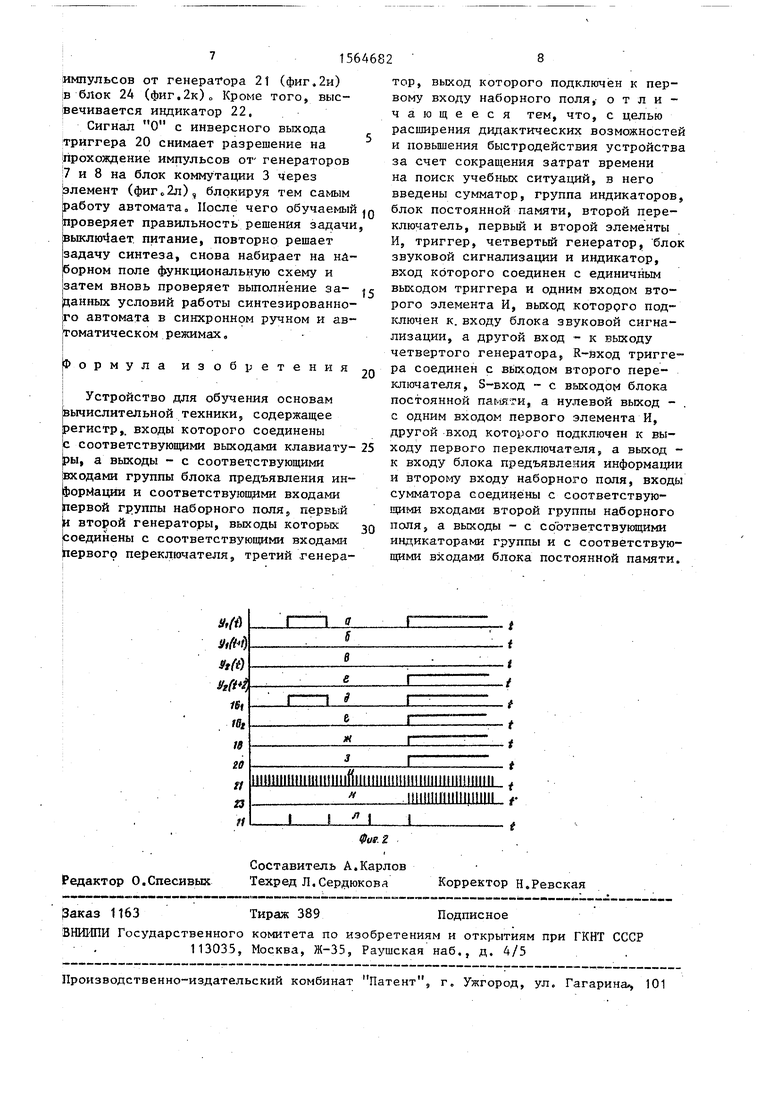

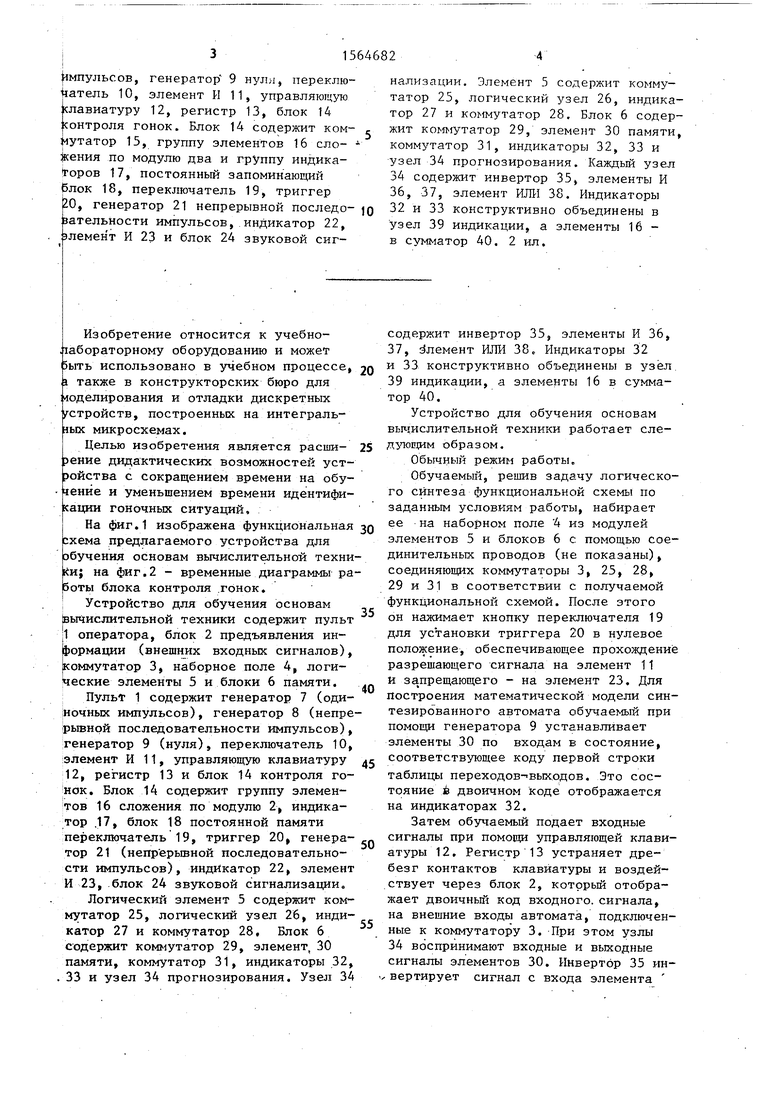

На фиг.1 изображена функциональная схема предлагаемого устройства для обучения основам вычислительной техники; на фиг.2 - временные диаграммы работы блока контроля гонок.

Устройство для обучения основам (вычислительной техники содержит пульт 1 оператора, блок 2 предъявления информации (внешних входных сигналов), рсоммутатор 3, наборное поле 4, логические элементы 5 и блоки 6 памяти.

Пульт 1 содержит генератор 7 (одиночных импульсов), генератор 8 (непрерывной последовательности импульсов), генератор 9 (нуля), переключатель 10, элемент И 11, управляющую клавиатуру 12, регистр 13 и блок 14 контроля гонок. Блок 14 содержит группу элементов 16 сложения по модулю 2, индикатор .17, блок 18 постоянной памяти переключатель 19, триггер 20, генера- тор 21 (непрерывной последовательности импульсов), индикатор 22, элемент И 23, блок 24 звуковой сигнализации.

Логический элемент 5 содержит коммутатор 25, логический узел 26, индикатор 27 и коммутатор 28, Блок 6 содержит коммутатор 29, элемент, 30 памяти, коммутатор 31, индикаторы 32, . 33 и узел 34 прогнозирования. Узел 34

нализации. Элемент 5 содержит коммутатор 25, логический узел 26, индикатор 27 и коммутатор 28. Блок 6 содержит коммутатор 29, элемент 30 памяти, коммутатор 31, индикаторы 32, 33 и узел 34 прогнозирования. Каждый узел 34 содержит инвертор 35, элементы И 36, 37, элемент ИЛИ 38. Индикаторы 32 и 33 конструктивно объединены в узел 39 индикации, а элементы 16 - в сумматор 40. 2 ил.

о

0

5

содержит инвертор 35, элементы И 36, 37, Элемент ИЛИ 38. Индикаторы 32 и 33 конструктивно объединены в узел 39 индикации, а элементы 16 в сумматор 40.

Устройство для обучения основам вычислительной техники работает следующим образом.

Обычный режим работы.

Обучаемый, решив задачу логического синтеза функциональной схемы по заданным условиям работы, набирает ее на наборном поле 4 из модулей элементов 5 и блоков 6 с помощью соединительных проводов (не показаны), соединяющих коммутаторы 3, 25, 28, 29 и 31 в соответствии с получаемой функциональной схемой. После этого он нажимает кнопку переключателя 19 для установки триггера 20 в нулевое положение, обеспечивающее прохождение разрешающего сигнала на элемент 11 и запрещающего - на элемент 23. Для построения математической модели синтезированного автомата обучаемый при помощи генератора 9 устанавливает элементы 30 по входам в состояние, соответствующее коду первой строки таблицы переходов- выходов. Это состояние 6 двоичном коде отображается на индикаторах 32,

Затем обучаемый подает входные сигналы при помощи управляющей клавиатуры 12, Регистр 13 устраняет дребезг контактов клавиатуры и воздействует через блок 2, который отображает двоичный код входного, сигнала, на внешние входы автомата, подключенные к коммутатору 3. При этом узлы 34 воспринимают входные и выходные сигналы элементов 30. Инвертор 35 ин- v вертирует сигнал с входа элемента

515

30, элемент 36 производит операцию логического умножения над сигналами, поступающими с выхода инвертора 35 и выхода элемента 30. Элемент 37 производит операцию логического умножения над сигналами элемента 30. Элемент 38 производит операцию логического сложения сигналов, поступающих с выходов элементов 36 и 37.

Реализованная узлом 34 функция принимает значение О в том случае, если элемент 30 в последующем такте установится в нулевое состояние, при

20

этом индикатор 33 не горит, а значе - (фиг.2а) в нулевое следующее состояние y,(t+1) (фиг.26). В то время, как элемент 30 памяти второго блока 6 (не показан) остается н нулевом состоянии, как в t (фиг.2в), так и t+1 тактах (фиг.2г), которым соответствуют сигналы уг(й) .и у (t+1), а все остальные элементы 30 не меняют своего состояния. Тогда лишь на выходе элемента 161 появляется единичный сиг- 25 нал (фиг.2д), который поступает на вход блока 18, высвечивая при этом соответствующий светодиод индикатора 17. Однако, поскольку на всех остальных входах блока 18 присутствуют сигналы О, то на его выходе присутствует сигнал О (фиг.2ж), поэтому триггер 20 остается в нулевом (исходном) положении (фиг.2з), разрешая прохождение сигналов от генераторов 7 и 8 через переключатель 10 и элемент 11 (фиг.2л) для работы устройства.

Однако, если обучаемый при построении функциональной схемы автомата допустил ошибку, которая при проверке прохождения сигналов приводит к одновременному изменению состояния более чем одного элемента 30, то на выходах соответствующих им элементов 16 (эление 1 - в противном случае, при этом индикатор 33 горит. Поэтому, считывая информацию индикаторов 33, обучаемый получает двоичную информацию, отмечаемую в каждой клетке таблицы переходов-выходов без дополнительных операций, только путем изменения комбинации входных сигналов. Это позволяет получить математическую модель синтезированного автомата, во время построения которой обучаемый производит отладку автомата, используя дополнительно индикаторы 27, отображащие выходные состояния каждого из узлов 26. Затем производится проверка выполнения заданных усло вий работы синтезированного автомата в синхронном ручном и автоматическом режимах, используя генераторы 7, 8 и переключатель 10, подавая сигналы синхронизации через элемент 11 на входы элементов 30 с коммутатора 3.

Режим анализа правильности решения задачи безгоночного кодирования.

Обучаемый, набрав на наборном поле 4 функциональную схему разработанного дискретного устройства с решением задачи безгоночного кодирования и построив его математическую модель в соответствии с обычным режимом работы, соединяет с помощью соедини- тельных проводов (не показаны) первый и второй выходы коммутаторов 31 с соответствующими парами входов коммутатора 15. С первых выходов коммутаторов 31 снимаются сигналы у ;(t +1), соответствующие последующему (прогнозируемому) состоянию триггеров 30, где ,n, а с вторых выходов коммутаторов 31 второй устройства снимаются сигналы yj(t) , соответствующие текущему состоянию триггеров 30.

30

35

40

45

50

55

мент 16 на фиг.1 не показан) появляются сигналы 1 (фиг.2д, е), поступающие на соответствующие входы блока 18 и высвечивающие соответствующие светоДиоды индикатора 17. Блок 18 запрограммирован таким образом, что при поступлении на его входы двух или более единичных сигналов в любой комбинации приводит к появлению на его выходе единичного сигнала (фиг.), который переводит триггер 20 в единичное состояние (фиг.2з).

В этом случае возбуждается прямой выход триггера 20, который подает разрешающий сигнал на второй вход элемента И 23, разрешая прохождение

После чего производится проверка выполнения заданных условий работы синтезированного автомата в синхронном ручном и автоматическом режимах, используя генераторы 7, 8 и переключатель 10, подавая сигналы синхронизации через элемент 11 на входы элементов 30 с коммутатора 3 аналогично работе прототипа (обычный режим работы) .

Допустим элемент 30 первого блока 6 переходит из единичного текущего состояния, соответствующего y.,(t) ,

20

25

25

30

25

35

40

мент 16 на фиг.1 не показан) появляются сигналы 1 (фиг.2д, е), поступающие на соответствующие входы блока 18 и высвечивающие соответствующие светоДиоды индикатора 17. Блок 18 запрограммирован таким образом, что при поступлении на его входы двух или более единичных сигналов в любой комбинации приводит к появлению на его выходе единичного сигнала (фиг.), который переводит триггер 20 в единичное состояние (фиг.2з).

В этом случае возбуждается прямой выход триггера 20, который подает разрешающий сигнал на второй вход элемента И 23, разрешая прохождение

импульсов от генератора 21 (фиг.2и) в блок 24 (фиг.2к)о Кроме того, высвечивается индикатор 22,

Сигнал О с инверсного выхода триггера 20 снимает разрешение на прохождение импульсов от- генераторов 7 и 8 на блок коммутации 3 через элемент (фиг„2л), блокируя тем самым работу автомата. После чего обучаемый 1 проверяет правильность решения задачи, выключает питание, повторно решает задачу синтеза, снова набирает на наборном поле функциональную схему и затем вновь проверяет выполнение за- , данных условий работы синтезированного автомата в синхронном ручном и автоматическом режимах.

формула изобретен и

Устройство для обучения основам вычислительной техники, содержащее регистр,, входы которого соединены с соответствующими выходами клавиату- ры, а выходы - с соответствующими входами группы блока предъявления информации и соответствующими входами первой группы наборного поля, первый и второй генераторы, выходы которых соединены с соответствующими входами первого переключателя9 третий генера0с

0

5 п

тор, выход которого подключен к первому входу наборного поля, отличающееся тем, что, с целью расширения дидактических возможностей и повышения быстродействия устройства за счет сокращения затрат времени на поиск учебных ситуаций, в него введены сумматор, группа индикаторов, блок постоянной памяти, второй переключатель, первый и второй элементы И, триггер, четвертый генератор, блок звуковой сигнализации и индикатор, вход которого соединен с единичным выходом триггера и одним входом второго элемента И, выход которрго подключен к. входу блока звуковой сигнализации, а другой вход - к выходу четвертого генератора, R-вход триггера соединен с выходом второго переключателя, S-БХОД - с выходом блока постоянной памяти, а нулевой выход - с одним входом первого элемента И, другой вход которого подключен к выходу первого переключателя, а выход - к входу блока предъявления информации и второму входу наборного поля, входы сумматора соединены с соответствующими входами второй группы наборного поля} а выходы - с соответствующими индикаторами группы и с соответствующими входами блока постоянной памяти.

Авторы

Даты

1990-05-15—Публикация

1988-08-19—Подача