Область техники

[1] Изобретение относится к микропроцессорной технике, в частности к микропроцессорам с конвейерной обработкой команд.

Предпосылки к созданию изобретения

[2] Традиционный процессор осуществляет обработку команд программы посредством конвейерного процесса, в котором каждая команда последовательно проходит через несколько стадий обработки, таких как выборка, дешифрация, исполнение, обращение к запоминающему устройству и обратная запись результата. В дальнейшем изложении комплекс технических средств, входящих в состав процессора и непосредственно связанных с осуществлением конвейерного процесса, именуется «конвейер». Классический конвейер позволяет осуществлять одновременную обработку нескольких команд, что существенно повышает производительность процессора, при этом каждая команда в определенный момент времени может находиться только на одной из стадий обработки, и на каждой стадии в определенный момент времени может обрабатываться только одна команда.

[3] Однако последовательная обработка команд может прерваться, когда программа содержит команду перехода (далее – вызывающая команда), результатом выполнения которой в зависимости от входного условия может стать как осуществление, так и неосуществление перехода. При осуществлении перехода вслед за вызывающей командой должна быть выполнена команда, сохраняемая в кэш-памяти по адресу, который не является следующим по счету адресом, или в оперативной памяти (далее – вызываемая команда), а при неосуществлении перехода вслед за вызывающей командой должна быть выполнена команда, имеющая в кэш-памяти следующий по счету адрес (далее – последующая команда).

[4] Тем временем решение о том, какая из вызываемой и последующей команд будет загружена в конвейер сразу за вызывающей командой, должно быть принято до выполнения вызывающей команды, а точнее, когда вызывающая команда находится на самой первой стадии конвейера. Ошибка в выборе между вызываемой и последующей командами приводит к тому, что обработка всей альтернативной ветви команд, определяемой выбранной командой, оказывается невостребованной, и конвейер должен приступить к обработке другой альтернативной ветви с самой первой стадии. Очевидно, что данный исход приводит к значительному снижению производительности процессора.

[5] В патентной публикации US 2001037446 A1, 01.11.2001 раскрыт процессор (далее – известный процессор), снабженный предсказателем перехода (далее – известный предсказатель). Известный предсказатель способен предсказывать результат выполнения вызывающей команды на основе состояния насыщающегося счетчика и выполнен с возможностью функционирования в двух режимах. При функционировании в первом режиме известный предсказатель предсказывает результат выполнения вызывающей команды на основе полученной в реальном времени, т.е. динамически изменяющейся истории результатов выполнения вызывающей команды в предположении, что данная история имеет тенденцию к продолжению. Состояние насыщающегося счетчика в этом случае изменяется после каждого осуществления или неосуществления перехода на вызываемую команду, и известный предсказатель предсказывает осуществление перехода на вызываемую команду, когда насыщающийся счетчик находится в одном из своих положительных состояний.

[6] При функционировании во втором режиме известный предсказатель использует характеристическую метку, оставленную компилятором в вызывающей команде и отражающую статическое предсказание результата выполнения вызывающей команды. Данное статическое предсказание сделано на основе истории результатов выполнения вызывающей команды, которая была заранее собрана во время предварительных прогонов программы, и потому остается неизменной. Насыщающийся счетчик при этом изменяет свое состояние после каждого совпадения или несовпадения результата выполнения вызывающей команды с характеристической меткой. Функционируя во втором режиме, известный предсказатель предсказывает осуществление перехода на вызываемую команду, когда насыщающийся счетчик находится в одном из тех своих состояний, которые согласуются с характеристической меткой. Другими словами, во втором режиме известный предсказатель динамически верифицирует статическое предсказание результата выполнения вызывающей команды на основе полученной в реальном времени истории фактов сбывшегося и несбывшегося предсказания в предположении, что данная история имеет тенденцию к продолжению.

[7] Таким образом, в своем первом режиме известный предсказатель осуществляет предсказание результата выполнения вызывающей команды на основе динамически изменяющейся истории без какой-либо верификации, а в своем втором режиме известный предсказатель осуществляет предсказание результата выполнения вызывающей команды на основе динамической верификации той истории, которая остается неизменной вне зависимости от хода выполнения программы и числа реально осуществленных переходов. В связи с этим и в первом, и во втором режимах известный предсказатель допускает значительное число ошибочных предсказаний, что приводит к частым перезагрузкам конвейера, которые становятся причиной снижения производительности процессора и повышения энергопотребления.

[8] Техническая проблема, на решение которой направлено изобретение, состоит в поиске решения, способного повысить производительность процессора и уменьшить его энергопотребление через снижение числа перезагрузок конвейера.

Сущность изобретения

[9] Для решения указанной технической проблемы в качестве изобретения предложен процессор (далее также – предложенный процессор), содержащий конвейер и предсказатель перехода, причем предсказатель перехода способен определять предсказанный результат выполнения вызывающей команды, подлежащей загрузке в конвейер. Предсказатель перехода содержит фактический насыщающийся счетчик и оценочный насыщающийся счетчик. Каждый из фактического насыщающегося счетчика и оценочного насыщающегося счетчика способен находиться в конечном отрицательном состоянии, в начальном отрицательном состоянии, в начальном положительном состоянии и в конечном положительном состоянии. Фактический насыщающийся счетчик способен смещаться на одно состояние в сторону конечного положительного состояния, когда по результату выполнения вызывающей команды осуществляется переход на вызываемую команду, и способен смещаться на одно состояние в сторону конечного отрицательного состояния, когда по результату выполнения вызывающей команды переход на вызываемую команду не осуществляется. Оценочный насыщающийся счетчик способен смещаться на одно состояние в сторону конечного положительного состояния, либо когда результатом выполнения вызывающей команды является осуществление перехода на вызываемую команду, а прежнее состояние фактического насыщающегося счетчика было положительным, либо когда результатом выполнения вызывающей команды является неосуществление перехода на вызываемую команду, а прежнее состояние фактического насыщающегося счетчика было отрицательным. Кроме того, оценочный насыщающийся счетчик способен смещаться на одно состояние в сторону конечного отрицательного состояния либо когда результатом выполнения вызывающей команды является осуществление перехода на вызываемую команду, а прежнее состояние фактического насыщающегося счетчика было отрицательным, либо когда результатом выполнения вызывающей команды является неосуществление перехода на вызываемую команду, а прежнее состояние фактического насыщающегося счетчика было положительным. В качестве предсказанного результата выполнения вызывающей команды предсказатель перехода определяет осуществление перехода на вызываемую команду, либо когда каждый из фактического и оценочного насыщающихся счетчиков находится либо в каком-либо из положительных состояний, либо когда каждый из фактического и оценочного насыщающихся счетчиков находится в каком-либо из отрицательных состояний.

[10] Технический результат изобретения состоит в повышении точности предсказывания перехода, выражающейся в том, что с очень большой, а точнее – с увеличенной относительно известного процессора вероятностью, именно та команда, которая была загружена в конвейер вслед за вызывающей командой, будет подлежать выполнению по результату выполнения вызывающей команды. Благодаря этому снижается число перезагрузок конвейера, вызванных неверным предсказанием результата выполнения вызывающей команды, что способствует увеличению производительности предложенного процессора и снижению энергопотребления.

[11] Причинно-следственная связь между признаками изобретения и техническим результатом заключается в следующем. Фактический насыщающийся счетчик отслеживает динамически изменяющуюся, т.е. актуальную для каждого момента времени и каждого набора входных условий историю переходов, что повышает вероятность продолжения данной истории переходов, а значит и точность предсказания, сделанного в предположении продолжения данной истории переходов. Оценочный насыщающийся счетчик отслеживает динамически изменяющуюся, т.е. актуальную для каждого момента времени историю сбывшихся и несбывшихся предсказаний фактического насыщающегося счетчика, что позволяет обеспечить верификацию предсказаний фактического насыщающегося счетчика путем выявления и исключения потенциально неточного предсказания, а значит повысить точность предсказания следующего перехода.

[12] Следует отметить, что признаки «оценочный насыщающийся счетчик способен смещаться на одно состояние в сторону конечного положительного состояния, когда результатом выполнения вызывающей команды является осуществление перехода на вызываемую команду, а прежнее состояние фактического насыщающегося счетчика было положительным» и «оценочный насыщающийся счетчик способен смещаться на одно состояние в сторону конечного положительного состояния, когда результатом выполнения вызывающей команды является неосуществление перехода на вызываемую команду, а прежнее состояние фактического насыщающегося счетчика было отрицательным» не являются альтернативами, а дополняют друг друга, при этом технический результат достигается только при их совокупности.

[13] Когда фактический насыщающийся счетчик находится в каком-либо из положительных состояний, он предсказывает осуществление перехода на вызываемую команду при следующем выполнении вызывающей команды. Если при следующем выполнении вызывающей команды переход на вызываемую команду действительно выполнен, то предсказание фактического насыщающегося счетчика было верным, и оценочный насыщающийся счетчик смещается на одно состояние в сторону конечного положительного состояния. И наоборот, когда фактический насыщающийся счетчик находится в каком-либо из отрицательных состояний, он предсказывает неосуществление перехода на вызываемую команду при следующем выполнении вызывающей команды. Если при следующем выполнении вызывающей команды переход на вызываемую команду действительно не выполнен, то предсказание фактического насыщающегося счетчика было верным, и оценочный насыщающийся счетчик по-прежнему смещается на одно состояние в сторону конечного положительного состояния. Таким образом, оба варианта отражают одно и то же действие оценочного насыщающегося счетчика при сбывшемся предсказании фактического насыщающегося счетчика.

[14] Кроме того, признаки «оценочный насыщающийся счетчик способен смещаться на одно состояние в сторону конечного отрицательного состояния, когда результатом выполнения вызывающей команды является осуществление перехода на вызываемую команду, а прежнее состояние фактического насыщающегося счетчика было отрицательным» и «оценочный насыщающийся счетчик способен смещаться на одно состояние в сторону конечного отрицательного состояния, когда результатом выполнения вызывающей команды является неосуществление перехода на вызываемую команду, а прежнее состояние фактического насыщающегося счетчика было положительным» также не являются альтернативами, а дополняют друг друга, при этом технический результат достигается только при их совокупности.

[15] Если фактический насыщающийся счетчик находился в каком-либо из положительных состояний, а при следующем выполнении вызывающей команды переход на вызываемую команду не выполнен, то предсказание фактического насыщающегося счетчика было неверным, и оценочный насыщающийся счетчик смещается на одно состояние в сторону конечного отрицательного состояния. И наоборот, если фактический насыщающийся счетчик находился в каком-либо из отрицательных состояний, а при следующем выполнении вызывающей команды переход на вызываемую команду выполнен, то предсказание фактического насыщающегося счетчика было неверным, и оценочный насыщающийся счетчик по-прежнему смещается на одно состояние в сторону конечного отрицательного состояния. Таким образом, оба варианта отражают одно и то же действие оценочного насыщающегося счетчика при несбывшемся предсказании фактического насыщающегося счетчика.

[16] И наконец, признаки «предсказатель перехода определяет осуществление перехода на вызываемую команду, когда каждый из фактического и оценочного насыщающихся счетчиков находится в каком-либо из положительных состояний» и «предсказатель перехода определяет осуществление перехода на вызываемую команду, когда каждый из фактического и оценочного насыщающихся счетчиков находится в каком-либо из отрицательных состояний» также не являются альтернативами, а дополняют друг друга, при этом технический результат достигается только при их совокупности.

[17] Если каждый из фактического насыщающегося счетчика и оценочного насыщающегося счетчика находится в каком-либо из положительных состояний, то оценочный насыщающийся счетчик подтверждает предсказание фактического насыщающегося счетчика об осуществлении перехода, и предсказатель перехода делает обоснованное определение об осуществлении перехода на вызываемую команду при следующем выполнении вызывающей команды. И наоборот, если каждый из фактического насыщающегося счетчика и оценочного насыщающегося счетчика находится в каком-либо из отрицательных состояний, то оценочный насыщающийся счетчик опровергает предсказание фактического насыщающегося счетчика о неосуществлении перехода, и предсказатель перехода делает обоснованное определение об осуществлении перехода на вызываемую команду при следующем выполнении вызывающей команды. Таким образом, оба варианта отражают одно и то же действие предсказателя перехода, когда каждый из фактического насыщающегося счетчика и оценочного насыщающегося счетчика находится в каком-либо из одноименных по отношению друг к другу состояний.

[18] В частном случае изобретения в качестве предсказанного результата выполнения вызывающей команды предсказатель перехода определяет неосуществление перехода на вызываемую команду, либо когда фактический насыщающийся счетчик находится в каком-либо из положительных состояний, а оценочный насыщающийся счетчик находится в каком-либо из отрицательных состояний, либо когда фактический насыщающийся счетчик находится в каком-либо из отрицательных состояний, а оценочный насыщающийся счетчик находится в каком-либо из положительных состояний.

[19] Аналогично описанному выше, признаки «предсказатель перехода определяет неосуществление перехода на вызываемую команду, когда фактический насыщающийся счетчик находится в каком-либо из положительных состояний, а оценочный насыщающийся счетчик находится в каком-либо из отрицательных состояний» и «предсказатель перехода определяет неосуществление перехода на вызываемую команду, когда фактический насыщающийся счетчик находится в каком-либо из отрицательных состояний, а оценочный насыщающийся счетчик находится в каком-либо из положительных состояний» не являются альтернативами, а дополняют друг друга, при этом технический результат достигается только при их совокупности.

[20] Если в момент нахождения фактического насыщающегося счетчика в каком-либо из положительных состояний, оценочный насыщающийся счетчик находится в каком-либо из отрицательных состояний, он опровергает предсказание фактического насыщающегося счетчика об осуществлении перехода, и предсказатель перехода делает обоснованное определение о неосуществлении перехода на вызываемую команду при следующем выполнении вызывающей команды. И наоборот, если в момент нахождения фактического насыщающегося счетчика в каком-либо из отрицательных состояний, оценочный насыщающийся счетчик находится в каком-либо из положительных состояний, он подтверждает предсказание фактического насыщающегося счетчика о неосуществлении перехода, и предсказатель перехода делает обоснованное определение о неосуществлении перехода на вызываемую команду при следующем выполнении вызывающей команды.

[21] В другом частном случае изобретения по результату выполнения вызывающей команды фактический насыщающийся счетчик способен изменять свое состояние только после того, как свое состояние изменил оценочный насыщающийся счетчик. Данное исполнение позволяет после поступления в предсказатель перехода результата выполнения вызывающей команды получать от фактического насыщающегося счетчика как его прежнее состояние, необходимое для изменения состояния оценочного насыщающегося счетчика, так и текущее состояние, необходимое для определения предсказанного результата выполнения вызывающей команды. Благодаря этому отпадает необходимость использования промежуточного регистра, сохраняющего прежнее состояние фактического насыщающегося счетчика, и конструкция предсказателя перехода упрощается.

Краткое описание чертежей

[22] Осуществление изобретения будет пояснено ссылками на фигуры:

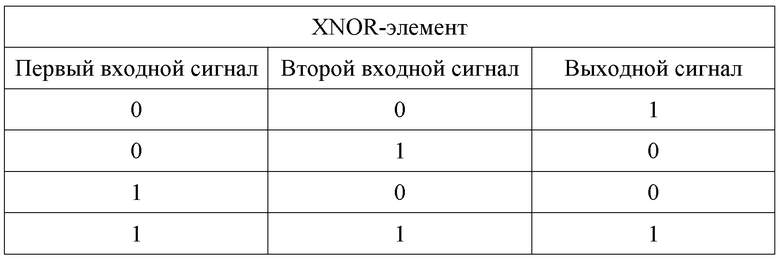

Фиг. 1 - блок-схема предложенного процессора;

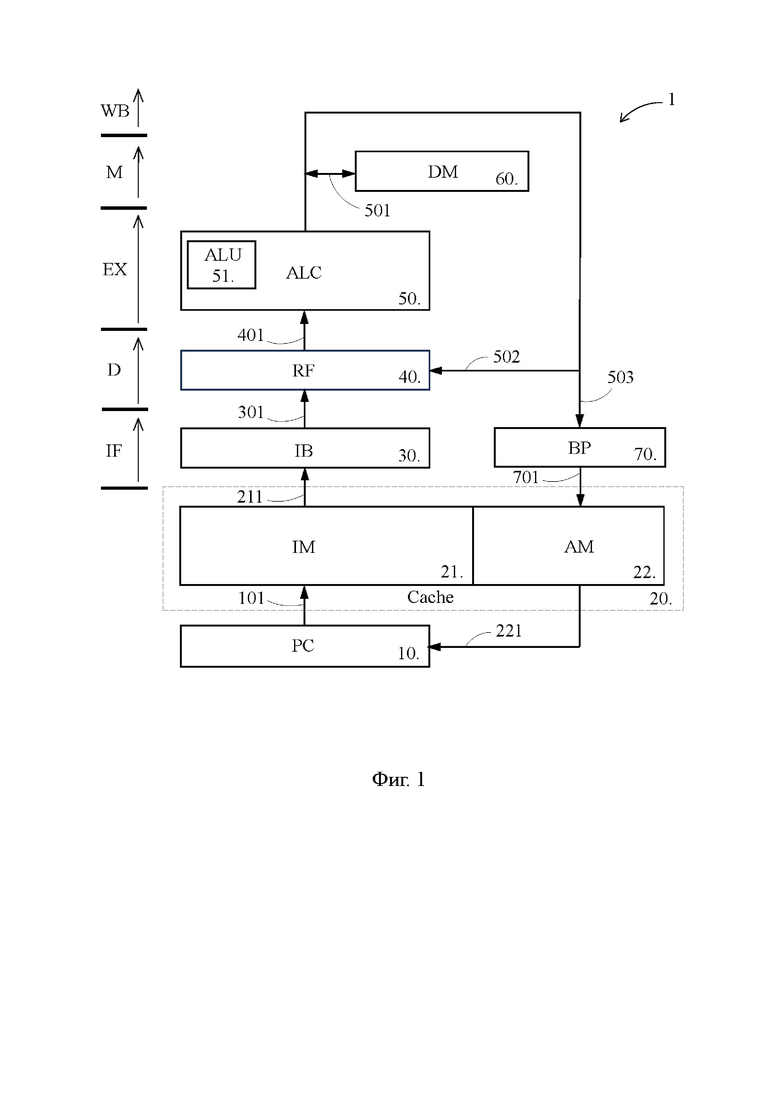

Фиг. 2 - схема алгоритма работы фактического насыщающегося счетчика, используемого в предсказателе перехода предложенного процессора;

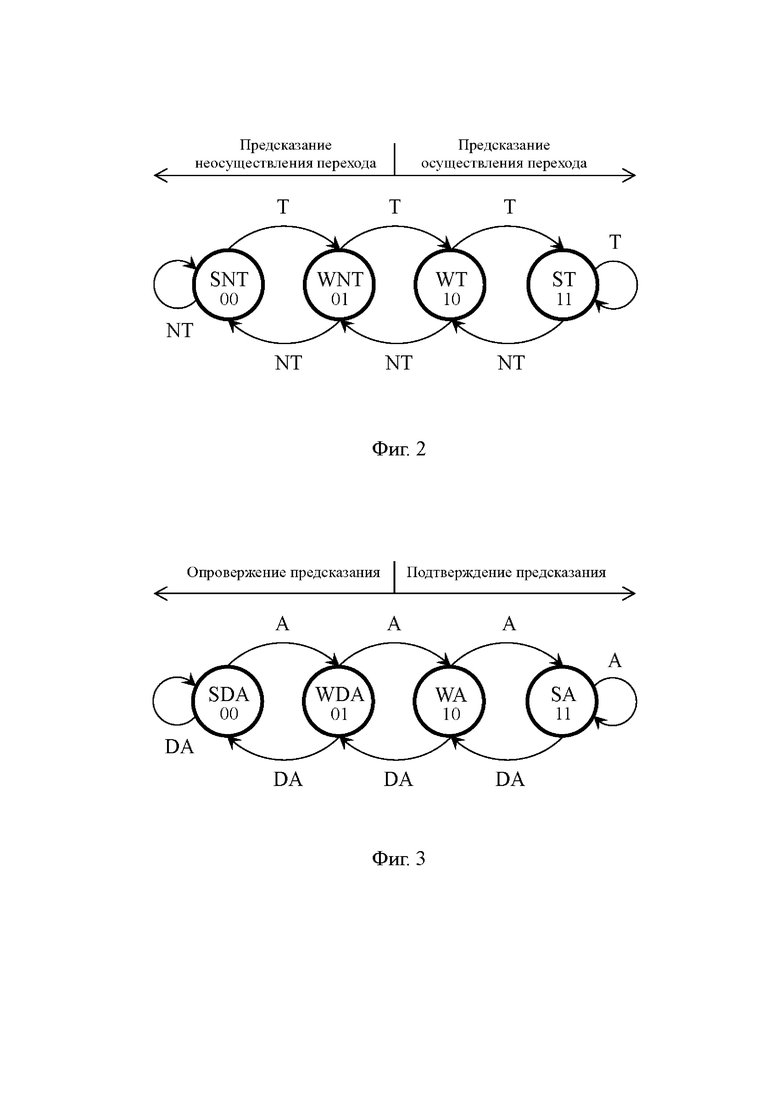

Фиг. 3 - схема алгоритма работы оценочного насыщающегося счетчика, используемого в предсказателе перехода предложенного процессора;

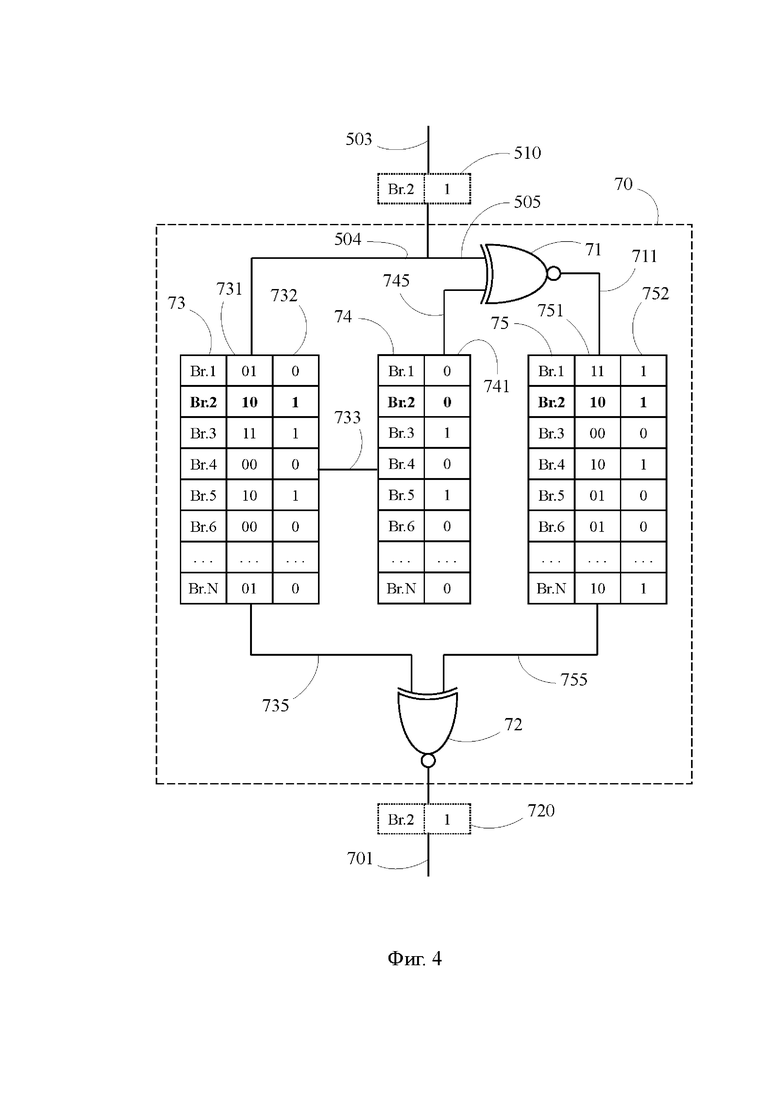

Фиг. 4 - схема предсказателя перехода, входящего в состав предложенного процессора, в одном варианте исполнения;

Фиг. 5 - схема предсказателя перехода, входящего в состав предложенного процессора, в другом варианте исполнения.

[23] Следует отметить, что форма и размеры отдельных элементов, отображенных на фигурах, являются условными и показаны так, чтобы наиболее наглядно проиллюстрировать взаимное расположение элементов предложенного процессора, а также их причинно-следственную связь с техническим результатом. Кроме того, во избежание избыточного усложнения фигур некоторые взаимосвязи элементов, очевидные специалисту в данной области техники, могут быть не отображены. Фигуры также содержат выполненные на английском и русском языках буквенные обозначения и словесные пояснения, которые являются общепринятыми в данной области техники и способствуют более быстрому восприятию фигур специалистом в данной области техники.

Осуществление изобретения

[24] Осуществление изобретения будет показано на наилучших примерах его реализации, которые не являются ограничениями в отношении объема охраняемых прав.

[25] На Фиг. 1 схематично показан процессор 1, который представляет собой предложенный процессор, выполненный согласно предпочтительному варианту осуществления изобретения. Процессор 1 может выступать как самостоятельный процессор или входить в состав более сложного процессора в качестве ядра.

[26] Процессор 1 содержит счетчик 10 команд (PC – program counter), кэш-память 20 управления (Cache), буфер 30 команд (IB - instruction buffer), регистровый файл 40 (RF - register file), арифметико-логический функциональный блок 50 (ALC - arithmetic-logical channel), кэш-память 60 данных (DM - data memory), предсказатель 70 перехода (BP – branch predictor). В состав арифметико-логического функционального блока 50 включено арифметико-логическое устройство 51 (АЛУ, ALU - arithmetic-logical unit).

[27] Далее, в состав процессора 1 входит блок управления (не показан), обеспечивающий выработку и передачу управляющих сигналов на перечисленные выше элементы, а также множество элементов, исполняющих тривиальные функции в конвейерном процессе и являющихся очевидными специалисту в данной области, таких как регистры, мультиплексоры, шины передачи данных и т.п. Некоторые из таких элементов отображены на Фиг. 1 и будут раскрыты по ходу изложения.

[28] Буфер 30 команд, регистровый файл 40, арифметико-логический функциональный блок 50, кэш-память 60 данных представляют собой основные компоненты конвейера, задействованные в соответствующих стадиях конвейерного процесса, которые показаны в левой части Фиг. 1: выборка команды (IF – instruction fetch), дешифрация (D – decode), исполнение (EX – execute), обращение к памяти (M – memory) и обратная запись результата (WB – write back). Вместе с тем конвейерный процесс, реализуемый процессором 1, может содержать гораздо больше стадий, чем указанные стадии IF, D, EX, M, WB. Принципы увеличения числа стадий конвейерного процесса, как правило, основанные на разделении указанных выше стадий на ряд более мелких стадий в целях уменьшения длительности такта, известны специалисту в данной области техники.

[29] Хотя на Фиг. 1 показан лишь один арифметико-логический функциональный блок 50, процессор 1 может иметь по существу любое количество арифметико-логических функциональных блоков 50, а также включать в себя предикатно-логические функциональные блоки (PLC - predicate logical channel), назначение и функционирование которых известны специалисту в данной области. Соответственно, процессор 1 может быть скалярным или суперскалярным процессором, осуществлять выполнение команд в порядке загрузки в конвейер (in-order execution) или в ином порядке (out-of-order execution). Притом что процессор 1 может быть выполнен по существу в любой архитектуре, предпочтительным является выполнение процессора 1 в архитектуре VLIW (Very Long Instruction Word).

[30] Каждая из кэш-памяти 20 управления и кэш-памяти 60 данных представляет собой кэш-память первого уровня, характеризующуюся наиболее быстрым доступом и известную как L1. Кэш-память 60 данных выполнена в виде отдельного устройства, однако, возможно исполнение, когда кэш-память 60 данных и кэш-память 20 управления объединены в одно устройство, в котором память 60 данных представлена в виде раздела.

[31] Кэш-память 20 управления включает в себя: кэш-память 21 команд (IM - instruction memory) и кэш-память 22 целевых адресов (AM – address memory), каждая из которых может быть выполнена либо в виде отдельного устройства, либо в виде раздела единого устройства, как показано на Фиг. 1. Кэш-память 22 целевых адресов сохраняет адреса вызываемых команд, переход на которые предсказан предсказателем 70 перехода для следующего выполнения соответствующих вызывающих команд, при этом сами вызываемые команды сохранены в кэш-памяти 21 команд по этим целевым адресам.

[32] Предсказатель 70 перехода (Фиг. 4) содержит первый XNOR-элемент 71, второй XNOR-элемент 72, массив 73 фактических насыщающихся счетчиков (далее – фактический массив 73), массив 74 прежних предсказаний, массив 75 оценочных насыщающихся счетчиков (далее – оценочный массив 75).

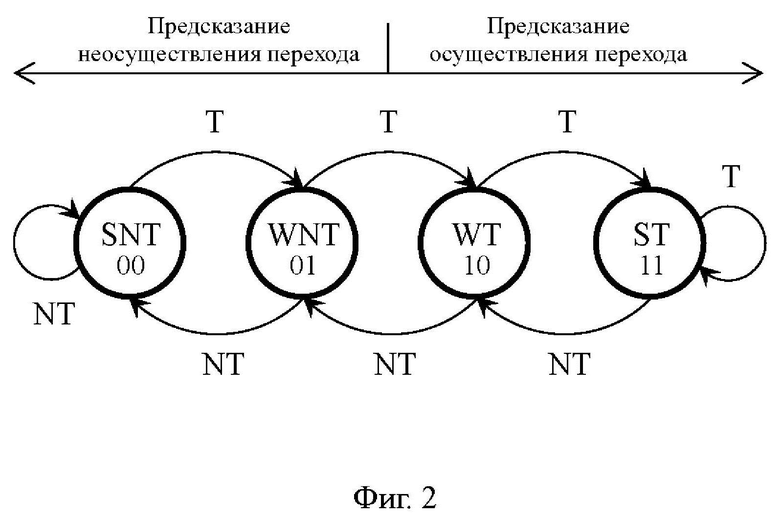

[33] Фактический массив 73 для каждой вызывающей команды Br.1 – Br.N (Branch – команда перехода или вызывающая команда) программы отображает состояние ее фактического насыщающегося счетчика, который функционирует согласно алгоритму, представленному на Фиг. 2. Фактический насыщающийся счетчик способен находиться в конечном отрицательном состоянии SNT (Strong Not Taken – сильная уверенность в неосуществлении перехода), в начальном отрицательном состоянии WNT (Weak Not Taken – слабая уверенность в неосуществлении перехода), в начальном положительном состоянии WT (Weak Taken – слабая уверенность в осуществлении перехода) и в конечном положительном состоянии ST (Strong Taken – сильная уверенность в осуществлении перехода).

[34] Следует отметить, что фактический насыщающийся счетчик помимо конечных и начальных отрицательных и положительных состояний может иметь промежуточные отрицательные и положительные состояния. Притом что в данном изложении функционирование предсказателя 70 перехода показано на примере использования двухбитового фактического насыщающегося счетчика, имеющего четыре состояния, специалист в данной области техники способен экстраполировать особенности работы и преимущества данного фактического насыщающегося счетчика на фактический насыщающийся счетчик с увеличенным числом состояний.

[35] Фактический насыщающийся счетчик предсказывает осуществление перехода на вызываемую команду при следующем выполнении вызывающей команды, когда он находится в каком-либо из положительных состояний WT или ST. И наоборот, фактический насыщающийся счетчик предсказывает неосуществление перехода на вызываемую команду при следующем выполнении вызывающей команды, когда он находится в каком-либо из отрицательных состояний WNT или SNT. Два положительных и два отрицательных состояния фактического насыщающегося счетчика обеспечивают ему разумную инертность в изменении позиции по предсказанию перехода, позволяющую при наличии значимой непрерывной истории сбывшихся предсказаний, сделанных фактическим насыщающимся счетчиком, исключить влияние случайных незначимых событий, способных прервать устоявшуюся тенденцию верных предсказаний.

[36] Когда по результату выполнения вызывающей команды осуществляется переход на вызываемую команду, фактический насыщающийся счетчик смещается на одно состояние в сторону конечного положительного состояния ST или продолжает оставаться в нем, если на момент выполнения вызывающей команды он находился в состоянии ST, что на Фиг. 2 показано стрелками T (Taken – осуществлен переход). И наоборот, когда по результату выполнения вызывающей команды должна быть выполнена последующая команда, т.е. переход на вызываемую команду не осуществляется, фактический насыщающийся счетчик смещается на одно состояние в сторону конечного отрицательного состояния SNT или продолжает оставаться в нем, если на момент выполнения вызывающей команды он находился в состоянии SNT, что на Фиг. 2 показано стрелками NT (Not Taken –переход не осуществлен).

[37] Конструктивно фактический насыщающийся счетчик выполнен в виде двухразрядного регистра, дополненного соответствующей логикой, очевидной специалисту в данной области техники. Указанный двухразрядный регистр способен сохранять двухбитовые значения 00, 01, 10, 11, которые в данном порядке соответствуют описанным выше состояниям SNT, WNT, WT, ST. Таким образом, используемое в контексте настоящего изложение понятие «фактический насыщающийся счетчик способен смещаться на одно состояние в сторону конечного положительного (или отрицательного) состояния» следует понимать как изменение сохраняемого указанным двухразрядным регистром двухбитового значения на двухбитовое значение, которое является следующим по порядку в сторону 11 (или 00).

[38] Как показано на Фиг. 4, фактический массив 73 для каждой вызывающей команды Br.1 – Br.N содержит указанный двухразрядный регистр (колонка 731), который отображает состояния фактического насыщающегося счетчика в виде двухбитовых значений. Для наглядности показанный на Фиг. 4 фактический массив 73 снабжен необязательной колонкой 732, которая для каждой команды Br.1 – Br.N отображает результат предсказания фактического насыщающегося счетчика (1 – Taken, 0 – Not Taken), т.е. по существу копирует первый бит из колонки 731.

[39] Следует также отметить, что фактический массив 73 получает результат выполнения каждой вызывающей команды Br.1 – Br.N от арифметико-логического функционального блока 50 по шинам 503 и 504 в виде «1», если этим результатом является осуществление перехода на вызываемую команду, и в виде «0», если этим результатом является неосуществление перехода на вызываемую команду.

[40] Массив 74 прежних предсказаний в колонке 741 для каждой команды Br.1 – Br.N сохраняет битовые значения, копируемые из колонки 732 фактического массива 73 по шине 733. Состояние колонки 741 отличается от состояния колонки 732 только в течение временного интервала, когда в фактический массив 73 поступила информация о результате выполнения какой-либо вызывающей команды Br, и ее фактический счетчик уже изменил свое состояние, но предсказатель 70 перехода свое предсказание еще не сделал. Назначение массива 74 прежних предсказаний будет раскрыто ниже при описании функционирования предсказателя 70 перехода.

[41] Оценочный массив 75 для каждой вызывающей команды Br.1 – Br.N программы отображает состояние ее оценочного насыщающегося счетчика, который функционирует согласно алгоритму, представленному на Фиг. 3. Оценочный насыщающийся счетчик способен находиться в конечном отрицательном состоянии SDA (Strong Disagree – сильное несогласие с предсказанием фактического насыщающегося счетчика), в начальном отрицательном состоянии WDA (Weak Disagree – слабое несогласие с предсказанием фактического насыщающегося счетчика), в начальном положительном состоянии WA (Weak Agree – слабое согласие с предсказанием фактического насыщающегося счетчика) и в конечном положительном состоянии SA (Strong Agree – сильное согласие с предсказанием фактического насыщающегося счетчика).

[42] Аналогично фактическому насыщающемуся счетчику оценочный насыщающийся счетчик помимо конечных и начальных отрицательных и положительных состояний может иметь промежуточные отрицательные и положительные состояния. Притом что в данном изложении функционирование предсказателя 70 перехода показано на примере использования двухбитового оценочного насыщающегося счетчика, имеющего четыре состояния, специалист в данной области техники способен экстраполировать особенности работы и преимущества данного оценочного насыщающегося счетчика на оценочный насыщающийся счетчик с увеличенным числом состояний.

[43] Следует также отметить, что оценочный насыщающийся счетчик может быть привязан не к вызывающей команде из перечня Br.1–Br.N, как это показано в случае оценочного массива 75, а к ее фактическому насыщающемуся счетчику, что позволяет использовать для одной вызывающей команды два или больше оценочных насыщающихся счетчиков. В этом случае дополнительный оценочный насыщающийся счетчик может верифицировать результат предсказания фактического насыщающегося счетчика по факту наступления иного события, например, по результату выполнения предыдущей вызывающей команды, если между предыдущей и текущей вызывающими командами установлена значимая корреляция. Данное исполнение, согласно которому результат предсказания фактического насыщающегося счетчика верифицируется больше чем одним насыщающимся счетчиком, позволяет еще больше повысить точность предсказания результата выполнения вызывающей команды.

[44] Оценочный насыщающийся счетчик подтверждает предсказание фактического насыщающегося счетчика для следующего выполнения вызывающей команды, когда он находится в каком-либо из положительных состояний WA или SA. И наоборот, оценочный насыщающийся счетчик опровергает предсказание фактического насыщающегося счетчика для следующего выполнения вызывающей команды, когда он находится в каком-либо из отрицательных состояний WDA или SDA. Два положительных и два отрицательных состояния оценочного насыщающегося счетчика обеспечивают ему разумную инертность в изменении позиции по верификации предсказания фактического насыщающегося счетчика, позволяющую при наличии значимой непрерывной истории сбывшихся предсказаний, сделанных предсказателем 70 перехода, исключить влияние случайных незначимых событий, способных прервать устоявшуюся тенденцию точной верификации предсказаний фактического насыщающегося счетчика.

[45] Когда по результату выполнения вызывающей команды определяется, что прежнее предсказание фактического насыщающегося счетчика было верным, то оценочный насыщающийся счетчик смещается на одно состояние в сторону крайнего положительного состояния SA или продолжает оставаться в нем, если на момент выполнения вызывающей команды он находился в состоянии SA, что на Фиг. 3 показано стрелками A (Agree – согласие с предсказанием). И наоборот, когда по результату выполнения вызывающей команды определяется, что прежнее предсказание фактического насыщающегося счетчика было неверным, то оценочный насыщающийся счетчик смещается на одно состояние в сторону крайнего отрицательного состояния SDA или продолжает оставаться в нем, если на момент выполнения вызывающей команды он находился в состоянии SDA, что на Фиг. 3 показано стрелками DA (Disagree – несогласие с предсказанием).

[46] Конструктивно оценочный насыщающийся счетчик выполнен в виде двухразрядного регистра, дополненного соответствующей логикой, очевидной специалисту в данной области техники. Упомянутый двухразрядный регистр способен сохранять двухбитовые значения 00, 01, 10, 11, которые в данном порядке соответствуют описанным выше состояниям SDA, WDA, WA, SA. Таким образом, используемое в контексте настоящего изложение понятие «оценочный насыщающийся счетчик способен смещаться на одно состояние в сторону крайнего положительного (или отрицательного) состояния» следует понимать как изменение сохраняемого упомянутым двухразрядным регистром двухбитового значения на двухбитовое значение, которое является следующим по порядку в сторону 11 (или 00).

[47] Как показано на Фиг. 4, оценочный массив 75 для каждой вызывающей команды Br.1 – Br.N содержит упомянутый двухразрядный регистр (колонка 751), который отображает состояния оценочного насыщающегося счетчика в виде двухбитовых значений. Для наглядности показанный на Фиг. 4 оценочный массив 75 снабжен колонкой 752, которая для каждой команды Br.1 – Br.N отображает результат верификации предсказания фактического насыщающегося счетчика (1 – Agree, 0 – Disagree), т.е. по существу копирует первый бит из колонки 751.

[48] Каждый из первого и второго XNOR-элементов 71 и 72 представляет собой логический элемент «исключающее ИЛИ-НЕ», который получает два входных сигнала и выдает один выходной сигнал, определяемый согласно Таблице:

[49] Первый XNOR-элемент 71 в качестве первого входного сигнала получает от арифметико-логического функционального блока 50 по шинам 503 и 505 результат выполнения вызывающей команды, представленный в виде «1», если переход на вызываемую команду осуществлен, и в виде «0», если переход на вызываемую команду не осуществлен. В качестве второго входного сигнала первый XNOR-элемент 71 получает от массива 74 прежних предсказаний по шине 745 прежнее предсказание результата выполнения вызывающей команды, которое представлено в виде «1», если было предсказано осуществление перехода на вызываемую команду, и в виде «0», если было предсказано неосуществление перехода на вызываемую команду.

[50] Если первый и второй входные сигналы, поступающие в первый XNOR-элемент 71, одинаковы, то первый XNOR-элемент 71 согласно Табл. выдает на оценочный массив 75 по шине 711 выходной сигнал «1», который свидетельствует о сбывшемся предсказании и переводит оценочный насыщающийся счетчик данной вызывающей команды на одно состояние в сторону конечного положительного состояния SA. Если первый и второй входные сигналы, поступающие в первый XNOR-элемент 71, различны, то первый XNOR-элемент 71 согласно Табл. выдает на оценочный массив 75 по шине 711 выходной сигнал «0», который свидетельствует о несбывшемся предсказании и переводит оценочный насыщающийся счетчик данной вызывающей команды на одно состояние в сторону конечного отрицательного состояния SDA.

[51] Второй XNOR-элемент 72 в качестве первого входного сигнала получает от фактического массива 73 по шине 735 полученный на основе фактического насыщающегося счетчика результат предсказания следующего выполнения какой-либо вызывающей команды из Br.1 – Br.N, представленный в виде «1», если этим результатом является предсказанное осуществление перехода на вызываемую команду, и в виде «0», если этим результатом является предсказанное неосуществление перехода на вызываемую команду. В качестве второго входного сигнала второй XNOR-элемент 72 получает от оценочного массива 75 по шине 755 результат верификации предсказания фактического насыщающегося счетчика, представленный в виде «1», если оценочный насыщающийся счетчик подтверждает предсказание фактического насыщающегося счетчика, и в виде «0», если оценочный насыщающийся счетчик опровергает предсказание фактического насыщающегося счетчика.

[52] Если первый и второй входные сигналы, поступающие во второй XNOR-элемент 72, одинаковы, то второй XNOR-элемент 72 согласно Табл. выдает в кэш-память 20 управления по шине 701 выходной сигнал «1», который означает, что предсказатель 70 перехода сделал предсказание об осуществлении перехода на вызываемую команду при следующем выполнении данной вызывающей команды. Соответственно, адрес этой вызываемой команды сохраняется в кэш-памяти 22 целевых адресов в качестве целевого адреса, и когда в следующий раз данная вызывающая команда будет загружена из кэш-памяти 21 команд в буфер 30 команд, вслед за ней из кэш-памяти 21 команд в буфер 30 команд будет загружаться эта вызываемая команда.

[53] Если же первый и второй входные сигналы, поступающие во второй XNOR-элемент 72, различны, то второй XNOR-элемент 72 согласно Табл. выдает в кэш-память 20 управления по шине 701 выходной сигнал «0», который означает, что предсказатель 70 перехода сделал предсказание о неосуществлении перехода на вызываемую команду при следующем выполнении данной вызывающей команды. Соответственно, адрес этой вызываемой команды не сохраняется в кэш-памяти 22 целевых адресов в качестве целевого адреса, и когда в следующий раз данная вызывающая команда будет загружена из кэш-памяти 21 команд в буфер 30 команд, вслед за ней из кэш-памяти 21 команд в буфер 30 команд будет загружаться последующая команда.

[54] Далее функционирование предсказателя 70 перехода проиллюстрировано конкретным примером, в котором предсказатель 70 перехода получает от арифметико-логического функционального блока 50 по шине 503 сигнал 510 об осуществлении перехода на вызываемую команду по результату выполнения вызывающей команды Br.2. Фактический насыщающийся счетчик, соответствующий вызывающей команде Br.2 в фактическом массиве 73 (выделен жирным шрифтом), получает сигнал 510 по шине 504 и переходит на двухбитовое значение 10 (колонка 731), на основании которого результатом предсказания фактического насыщающегося счетчика для следующего выполнения вызывающей команды Br.2 становится осуществление перехода на вызываемую команду (колонка 732). Вслед за этим фактический массив 73 по шине 735 выдает сигнал «1» на второй XNOR-элемент 72.

[55] Обратим внимание, что по результату последнего выполнения вызывающей команды Br.2 (осуществление перехода) фактический насыщающийся счетчик принял двухбитовое значение 10 (колонка 731), а значит предыдущим его двухбитовым значением было 01. Соответственно, прежнее предсказание фактического насыщающегося счетчика состояло в неосуществлении перехода, что сохранено в массиве 74 прежних предсказаний (колонка 741). В результате этого массив 74 прежних предсказаний выдает по шине 745 на первый XNOR-элемент 71 сигнал «0».

[56] Первый XNOR-элемент 71, в свою очередь, получает от арифметико-логического функционального блока 50 по шинам 503 и 505 первый входной сигнал «1» и получает от массива 74 прежних предсказаний по шине 745 второй входной сигнал «0», что означает несбывшееся прежнее предсказание и выдачу выходного сигнала «0», который направляется в оценочный массив 75 по шине 711. Оценочный насыщающийся счетчик вызывающей команды Br.2 переходит на двухбитовое значение 10 (т.е. прежним его значением было 11), сохраняющее подтверждение для текущего предсказания фактического насыщающегося счетчика. В результате этого оценочный массив 75 выдает на второй XNOR-элемент 72 по шине 755 сигнал «1».

[57] Итак, второй XNOR-элемент 72 получает от фактического массива 73 по шине 735 первый входной сигнал «1» и получает от оценочного массива 75 по шине 755 второй входной сигнал «1», в результате чего согласно Табл. выдает выходной сигнал «1». Таким образом, предсказатель 70 перехода делает предсказание об осуществлении перехода при следующем выполнении вызывающей команды Br.2, которое в виде сигнала 720 выдает в кэш-память 20 управления по шине 701 для сохранения адреса соответствующей вызываемой команды в качестве целевого адреса в кэш-памяти 22 целевых адресов. Соответственно, при следующей выборке вызывающей команды Br.2 на стадии IF, вслед за вызывающей командой Br.2 в буфер 30 команд будет загружена эта вызываемая команда.

[58] Как следует из вышеизложенного, предсказатель 70 перехода, содержащий для каждой вызывающей команды фактический и оценочный насыщающиеся счетчики, обеспечивает динамическое предсказание перехода и динамическую верификацию данного предсказания для следующего выполнения вызывающей команды. Данное обстоятельство повышает вероятность того, что именно та команда из вызываемой и последующей команд, которая будет в следующий раз загружена из кэш-памяти 20 управления в буфер 30 команд вслед за вызывающей командой, будет подлежать выполнению по результату выполнения вызывающей команды. В результате этого снижается число перезагрузок конвейера, а значит повышается производительность процессора 1 и уменьшается его энергопотребление.

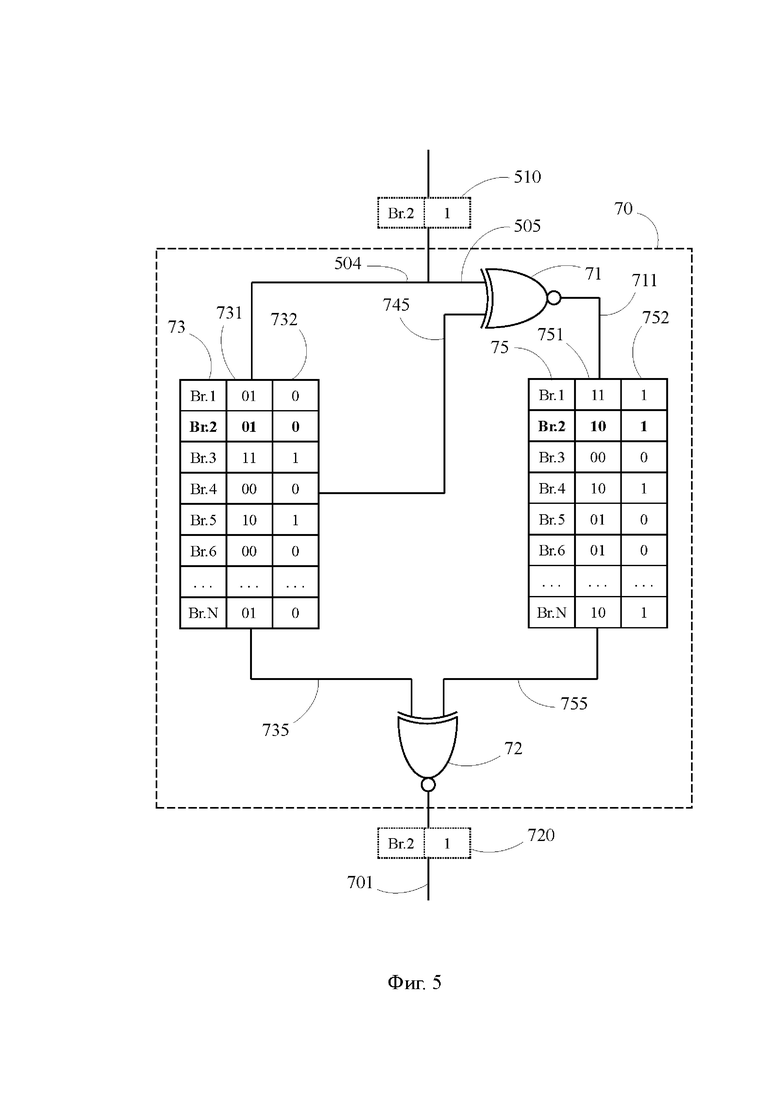

[59] На Фиг. 5 представлен предсказатель 70 перехода в более предпочтительном варианте исполнения, который отличается от представленного на Фиг. 4 тем, что он не содержит массива 74 прежних предсказаний, а фактический массив 73 напрямую соединен с первым XNOR-элементом 71 шиной 745. В данном варианте исполнения предсказателя 70 перехода передача сигнала 510 по шине 505 на первый XNOR-элемент 71 и изменение состояния фактического счетчика вызывающей команды Br.2 в фактическом массиве 73 происходят в разных тактах. Соответственно, сигнал 510 по шине 505 поступает на первый XNOR-элемент 71 одновременно с прежним результатом предсказания «0» фактического счетчика вызывающей команды Br.2, сохраняемым в этом такте в фактическом массиве 73 и передаваемым на первый XNOR-элемент 71 по шине 745.

[60] В следующем такте фактический счетчик вызывающей команды Br.2 в фактическом массиве 73 и оценочный счетчик вызывающей команды Br.2 в оценочном массиве 75 обновляют свое состояние, и новый результат предсказания «1» фактического счетчика вызывающей команды Br.2 одновременно с новым результатом верификации «1» предсказания фактического насыщающегося счетчика поступают на второй XNOR-элемент 72 по шинам 735 и 755. В остальном конструкция и функционирование варианта предсказателя 70 перехода на Фиг. 5 не отличаются от варианта на Фиг. 4.

[61] Процессор 1 работает следующим образом.

На стадии IF конвейерного процесса по сигналу, поступающему в кэш-память 21 команд по шине 101 от счетчика 10 команд и содержащему указание на адрес требуемой команды, кэш-память 21 команд передает требуемую команду (далее – отслеживаемая команда) в виде N-битовой последовательности по шине 211 в буфер 30 команд.

[62] На стадии D происходит расшифровка отслеживаемой команды, в ходе которой из указанной N-битовой последовательности выделяется по меньшей мере первая группа битов, указывающая на код операции, вторая и третья группы битов, указывающие на адреса исходных операндов в регистровом файле 40, и четвертая группа битов, указывающая на адрес для записи результирующего операнда в регистровом файле 40. Первая группа битов при этом передается из буфера 30 команд в блок управления, а вторая, третья и четвертая группы передаются из буфера 30 команд по шине 301 в регистровый файл 40.

[63] На стадии EX в арифметико-логический функциональный блок 50 по шине 401 поступают исходные операнды, прочитанные в регистровом файле 40. Одновременно с этим из блока управления в арифметико-логический функциональный блок 50 поступает сигнал, предписывающий выполнение операции, соответствующей упомянутому коду операции. После выполнения указанной операции над исходными операндами стадия EX завершается, а результат выполнения отслеживаемой команды из арифметико-логического функционального блока 50 по шине 501 направляется в кэш-память 60 данных (стадия M), а затем или вместо этого по шине 502 направляется в регистровый файл 40 (стадия WB), где записывается в качестве результирующего операнда отслеживаемой команды.

[64] Одновременно с направлением результата выполнения отслеживаемой команды по шине 502, результат выполнения отслеживаемой команды из арифметико-логического функционального блока 50 по шине 503 направляется в предсказатель 70 перехода, который игнорирует его, если отслеживаемая команда не является вызывающей командой. Если же предсказатель 70 перехода распознает отслеживаемую команду как вызывающую команду, т.е. команду из перечня Br.1 - Br.N, то он обрабатывает результат выполнения отслеживаемой команды, как это было описано выше, и передает предсказанный результат следующего выполнения отслеживаемой команды по шине 701 в кэш-память 20 управления.

[65] Если предсказанным результатом следующего выполнения отслеживаемой команды является осуществление перехода, то адрес соответствующей вызываемой команды сохраняется в качестве целевого адреса в кэш-памяти 22 целевых адресов, и при следующей выборке отслеживаемой команды на стадии IF вслед за отслеживаемой командой из кэш-памяти 21 команд в буфер 30 команд загружается эта вызываемая команда. Одновременно с выборкой данной вызываемой команды на стадии IF кэш-память 22 целевых адресов по шине 221 передает на счетчик 10 команд сигнал о том, что счет команд далее надо вести с этой вызываемой команды.

[66] Если предсказанным результатом следующего выполнения отслеживаемой команды является неосуществление перехода, то адрес соответствующей вызываемой команды не сохраняется в качестве целевого адреса в кэш-памяти 22 целевых адресов, и при следующей выборке отслеживаемой команды на стадии IF вслед за отслеживаемой командой из кэш-памяти 21 команд в буфер 30 команд будет загружена последующая команда.

| название | год | авторы | номер документа |

|---|---|---|---|

| ПРОЦЕССОР С УСОВЕРШЕНСТВОВАННЫМ ХРАНИЛИЩЕМ ВЫЗЫВАЕМЫХ АДРЕСОВ | 2024 |

|

RU2832273C1 |

| ПРОЦЕССОР С ЗАГРУЗКОЙ КОМАНД В СОСТАВЕ КЭШЛАЙНА И ПРЕДСКАЗАНИЕМ ПЕРЕХОДА | 2024 |

|

RU2828600C1 |

| ЭНЕРГОЭФФЕКТИВНЫЙ МЕХАНИЗМ УПРЕЖДАЮЩЕЙ ВЫБОРКИ ИНСТРУКЦИЙ | 2006 |

|

RU2375745C2 |

| ПРЕДСТАВЛЕНИЕ ПЕРЕХОДОВ ЦИКЛА В РЕГИСТРЕ ПРЕДЫСТОРИИ ПЕРЕХОДОВ С ПОМОЩЬЮ МНОЖЕСТВА БИТ | 2007 |

|

RU2447486C2 |

| VLIW-ПРОЦЕССОР С ДОПОЛНИТЕЛЬНЫМ ПОДГОТОВИТЕЛЬНЫМ КОНВЕЙЕРОМ И ПРЕДСКАЗАТЕЛЕМ ПЕРЕХОДА | 2024 |

|

RU2816094C1 |

| СПОСОБЫ И УСТРОЙСТВО ДЛЯ МОДЕЛИРОВАНИЯ ПОВЕДЕНИЯ ПРЕДСКАЗАНИЯ ПЕРЕХОДОВ ЯВНОГО ВЫЗОВА ПОДПРОГРАММЫ | 2007 |

|

RU2417407C2 |

| СПОСОБЫ И УСТРОЙСТВА ДЛЯ ПРОАКТИВНОГО УПРАВЛЕНИЯ КЭШЕМ АДРЕСОВ ВЕТВЛЕНИЙ | 2007 |

|

RU2421783C2 |

| РЕЖИМ СЛЕЖЕНИЯ В УСТРОЙСТВЕ ОБРАБОТКИ В СИСТЕМАХ ТРАССИРОВКИ КОМАНД | 2013 |

|

RU2635044C2 |

| ОЧИСТКА СЕГМЕНТИРОВАННОГО КОНВЕЙЕРА ДЛЯ НЕВЕРНО ПРЕДСКАЗАННЫХ ПЕРЕХОДОВ | 2008 |

|

RU2427889C2 |

| УСТРОЙСТВО ДИНАМИЧЕСКОГО ПРЕДСКАЗАНИЯ КОМАНД УСЛОВНОГО ПЕРЕХОДА МИКРОПРОЦЕССОРА | 2012 |

|

RU2503996C1 |

Изобретение относится к микропроцессорам с конвейерной обработкой команд. Технический результат заключается в повышении производительности и снижении энергопотребления процессора. Технический результат достигается за счет того, что процессор содержит конвейер и предсказатель перехода, причем предсказатель перехода способен определять результат выполнения вызывающей команды, подлежащей загрузке в конвейер, и содержит фактический и оценочный насыщающийся счетчики, каждый из которых способен находиться в отрицательном и положительном начальном и конечном состояниях, при этом фактический счетчик смещается в сторону положительного состояния, когда по результату выполнения вызывающей команды осуществляется переход на вызываемую команду, и в сторону отрицательного состояния, когда переход на вызываемую команду не осуществляется, а оценочный счетчик способен смещаться в сторону положительного состояния, либо когда результатом выполнения вызывающей команды является переход на вызываемую команду, а прежнее состояние фактического счетчика было положительным, либо когда результатом выполнения вызывающей команды является неосуществление перехода на вызываемую команду, а прежнее состояние фактического счетчика было отрицательным. 2 з.п. ф-лы, 5 ил.

1. Процессор, который содержит конвейер и предсказатель перехода, причем предсказатель перехода способен определять предсказанный результат выполнения вызывающей команды, подлежащей загрузке в конвейер, при этом

предсказатель перехода содержит фактический насыщающийся счетчик и оценочный насыщающийся счетчик, причем каждый из фактического насыщающегося счетчика и оценочного насыщающегося счетчика способен находиться в конечном отрицательном состоянии, в начальном отрицательном состоянии, в начальном положительном состоянии и в конечном положительном состоянии, причем

фактический насыщающийся счетчик способен смещаться на одно состояние в сторону конечного положительного состояния, когда по результату выполнения вызывающей команды осуществляется переход на вызываемую команду, и способен смещаться на одно состояние в сторону конечного отрицательного состояния, когда по результату выполнения вызывающей команды переход на вызываемую команду не осуществляется, при этом

оценочный насыщающийся счетчик способен смещаться на одно состояние в сторону конечного положительного состояния либо когда результатом выполнения вызывающей команды является осуществление перехода на вызываемую команду, а прежнее состояние фактического насыщающегося счетчика было положительным, либо когда результатом выполнения вызывающей команды является неосуществление перехода на вызываемую команду, а прежнее состояние фактического насыщающегося счетчика было отрицательным, и кроме того,

оценочный насыщающийся счетчик способен смещаться на одно состояние в сторону конечного отрицательного состояния либо когда результатом выполнения вызывающей команды является осуществление перехода на вызываемую команду, а прежнее состояние фактического насыщающегося счетчика было отрицательным, либо когда результатом выполнения вызывающей команды является неосуществление перехода на вызываемую команду, а прежнее состояние фактического насыщающегося счетчика было положительным, при этом

в качестве предсказанного результата выполнения вызывающей команды предсказатель перехода определяет осуществление перехода на вызываемую команду, либо когда каждый из фактического и оценочного насыщающихся счетчиков находится либо в каком-либо из положительных состояний, либо когда каждый из фактического и оценочного насыщающихся счетчиков находится в каком-либо из отрицательных состояний.

2. Процессор по п. 1, в котором в качестве предсказанного результата выполнения вызывающей команды предсказатель перехода определяет неосуществление перехода на вызываемую команду, либо когда фактический насыщающийся счетчик находится в каком-либо из положительных состояний, а оценочный насыщающийся счетчик находится в каком-либо из отрицательных состояний, либо когда фактический насыщающийся счетчик находится в каком-либо из отрицательных состояний, а оценочный насыщающийся счетчик находится в каком-либо из положительных состояний.

3. Процессор по п. 1, в котором по результату выполнения вызывающей команды фактический насыщающийся счетчик способен изменять свое состояние после того, как свое состояние изменил оценочный насыщающийся счетчик.

| VLIW-ПРОЦЕССОР С ДОПОЛНИТЕЛЬНЫМ ПОДГОТОВИТЕЛЬНЫМ КОНВЕЙЕРОМ И ПРЕДСКАЗАТЕЛЕМ ПЕРЕХОДА | 2024 |

|

RU2816094C1 |

| VLIW-ПРОЦЕССОР С УЛУЧШЕННОЙ ПРОИЗВОДИТЕЛЬНОСТЬЮ ПРИ ЗАДЕРЖКЕ ОБНОВЛЕНИЯ ОПЕРАНДОВ | 2023 |

|

RU2816092C1 |

| US 20180181400 A1, 28.06.2018 | |||

| ПРОЦЕССОР С ЗАГРУЗКОЙ КОМАНД В СОСТАВЕ КЭШЛАЙНА И ПРЕДСКАЗАНИЕМ ПЕРЕХОДА | 2024 |

|

RU2828600C1 |

| US 10768936 B2, 08.09.2020. | |||

Авторы

Даты

2024-12-24—Публикация

2024-05-18—Подача