Изобретение относится к вычислительной технике и может быть использовано в специализированных вычислительных ЭВМ, например векторных процессорах и вычислительных системах с микропрограммным управлением.

Цель изобретения - сокращение объема блока памяти микрокоманд за счет исключения поля адреса микрокоманды.

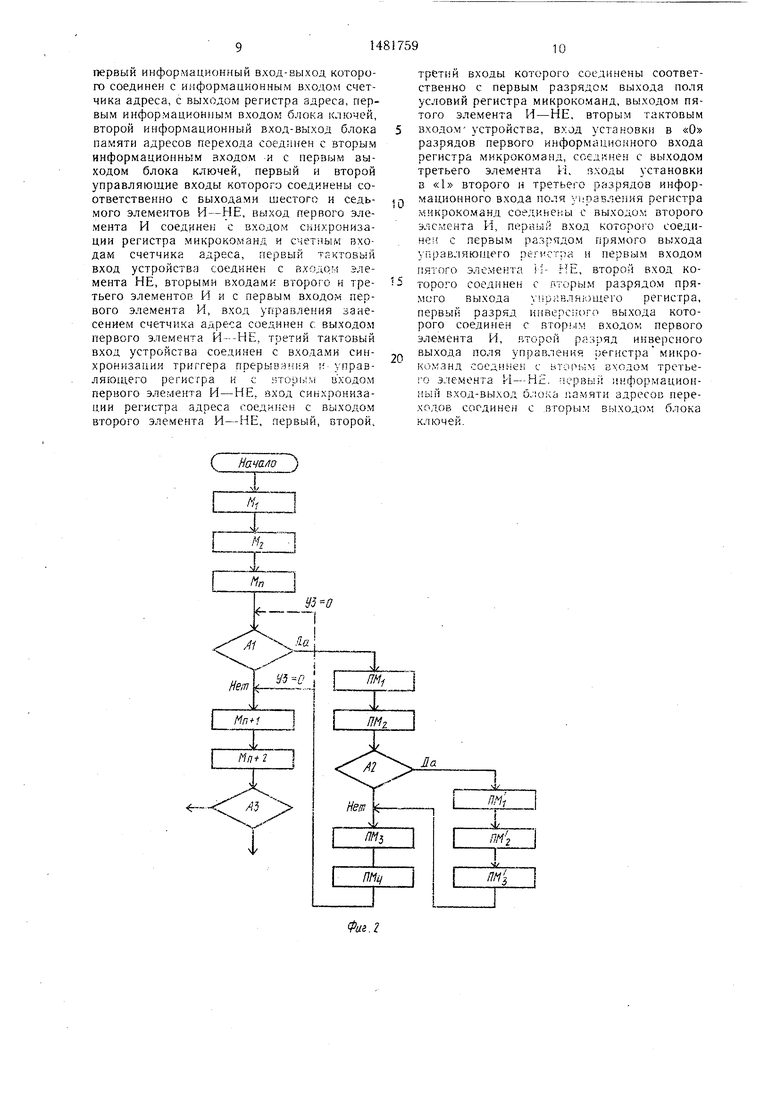

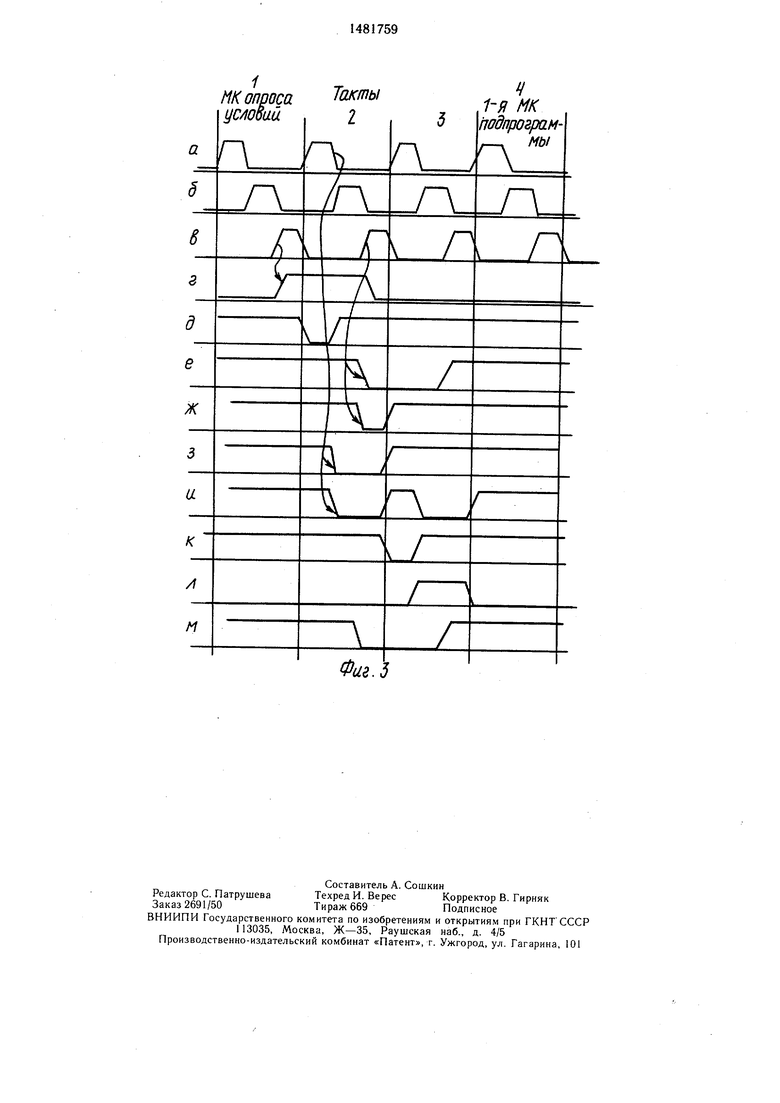

На фиг. I приведена функциональная схема устройства; на фиг. 2 - пример алго- ритма микропрограммы с переходами; на фиг. 3 - временная диаграмма работы устройства во время прерывания по условию.

Микропрограммное устройство (фиг. 1) содержит счетчик 1 адреса микрокоманд, регистр 2 адреса, блок 3 памяти микрокоманд, регистр 4 микрокоманд, управляющий регистр 5, мультиплексор 6 логических условий, триггер 7 прерывания, мультиплексор 8 младших разрядов адреса, блок 9 памяти адресов переходов, блок 10 ключей с тристабильным выходом, первый элемент И 11, первый 12, второй 13 элементы И - НЕ, второй 14, третий 15 элементы И, элемент НЕ 16, четвертый 17, пятый 18 элементы И, третий 19, четвертый 20, пятый 21, шестой 22, седьмой 23 элементы И-НЕ, первый 24, второй 25, третий 26 тактовые входы, вход 27 значений логических условий устройства, выход 28 микрокоманды устройства.

В формате микрокоманды отсутствует поле адреса перехода. Адреса переходов занимают несколько слов оперативной памяти процессора, причем адреса этих слов закодированы соответственно коду поля условий микрокоманды. Таким образом, номер условия является косвенным адресом перехода. Такая организация позволяет значительно сократить объем микрокоманд.

Ветвления в микропрограмме, предусмотренные управляющим алгоритмом, а также условные и безусловные переходы выполняются по команде «Запись СК. Команда возникает аппаратно по сигнал у «Прерывание при выполнении микрокоманды с контролируемыми логическими условиями. Для выполнения в линейных частях программы, для вызова программ и для безусловных переходов микрокоманда «Запись СК устанавливается программно.

Работа устройства рассматривается на примере выполнения алгоритма микропрограммы, показанного на фиг. 2.

Устройство работает следующим образом.

В блоке 3 памяти микрокоманд записан набор управляющих программ векторного процессора. Выбор каждой очередной микрокоманды из блока памяти происходит по адресному счетчику 1, на счетный вход которого поступают тактовые импульсы ТИ| с входа 24 устройства (фиг. 3 а). По этим же тактовым импульсам происходит занесение выбранной микрокоманды с выхода 3 в регистр 4 микрокоманд, выходы которого управляют работой векторного процессора. Регистр 2 адреса в каждом такте копирует содержимое счетчика 1 по тактовым импульсам ТИ2 - вход 25 устройства (фиг. 3 б).

Естественный порядок следования микрокоманд (Ml, M2,...,Mi,, фиг. 2) нарушается при наличии условного перехода в микропрограмме (А1, фиг. 2).

Четыре старших разряда микрокоманды составляют поле условий УО-УЗ. Если в программе необходимо выполнить переход по условию, то в микрокоманде условного перехода (А1, фиг. 2) установлены разряды поля условий на опрос соответствующих признаков. Если при исполнении микрокоманды опрашиваемый признак возник, то после данной микрокоманды следует команда перехода, занимающая 2 такта - возникает прерывание текущей микропрограммы. Переход на нужную команду или вызов подпрограммы осуществляется по сиг- налу «Прерывание, возникающему на выходе мультиплексора 6. На его управляющие входы поступают разряды поля условий микрокоманды, а на информационные входы - опрашиваемые признаки, возникающие при работе векторного процессора - вход 27.

Адреса переходов (адреса вызова подпрограмм и возврата в основную программу) хранятся в запоминающем устройстве 9. Причем оно может быть совмещено с основной оперативной памятью, например векторного процессора, в составе которого используется это устройство, содержащей данные для вычислений. В микрокоманде содержится поле адреса этой памяти. 4 младших разряда поля адреса микрокоманды АО-A3 используются для вызова адресов переходов из блока 9 памяти. Таким образом, в конкретном примере 16 младших слов оперативной памяти процессора используется для хранения адресов переходов. Оперативная память векторного процессора оперирует словами двойной длины - 32 разряда, шина данных процессора делится на две - младшая часть (от 0 по 15 разряд) и старшая (от 16 по 31 разряд). Причем старшая и младшая часть шины могут при необходимости меняться местами. Это обстоятельство удобно использовать для команды переходов - адрес вызова подпрограммы хранится в старшей части ячейки блока 9 памяти, а адрес возврата запоминает- ся в младшей части той же ячейки. Счетчик 1 адреса, регистр 2 адреса подключены к старшей части шины. Переключение старшей и младшей части осуществляется ключами 10 под управлением элементов И-НЕ 22, 23.

Рассмотрим как выполняется переход по условию. Сигнал «Прерывание возникает на выходе мультиплексора 6 в такте (1) выполнения микрокоманды условного перехода (А1, фиг. 2). Этот сигнал запоминается в триггере 7 (фиг. 3 г) по тактовому импульсу 26. Триггер 7 управляет переключением мультиплексора 8 на второй вход - разряды УО-УЗ копируются в разряды АО-A3 поля адреса вначале следующего такта (2) по тактовому импульсу 24. Кроме того, под управлением 7 в еле- дующем такте (2) на элементе И 15 пропускается тактовый импульс 24 на R-вход регистра 4 микрокоманд (фиг. 3 д). Следовательно, во втором такте регистр микрокоманд обнулится, а в разрядах поля адреса оперативной памяти установится адрес вызова команды перехода (команда перехода для обработки данного прерывания хранится в блоке 9 памяти по адресу, закодированному также как поле опроса соответствующего признака).

По данному состоянию регистра микрокоманд во 2-м такте возникает команда записи в счетчик адреса микрокоманд 1 содержимого старшей части, прочитанной по адресу АО-A3 ячейки блока 9 памяти - в счетчик 1 заносится адрес подпрограммы, вызванной в данном случае.

Управляют этим четыре разряда поля управления регистра микрокоманд 4 - разряды первый «Пр. СК (признак счетчика команд), второй - «Ст. (старшие разряды шины), третий - «Зап. (запись в память 9) и четвертый - «Мл. (младшие разряды шины).

Инверсные выходы разрядов «Пр. СК и «Зап. формируют на выходе элемента И 18 команду «3. СК (запись счетчика команд), которая по тактовым импульсам ТИ - вход 26 (фиг. 3 в) запоминается в пер- вом разряде управляющего регистра 5. С выхода 18 команда «3. СК поступает на элемент И-НЕ 12, на второй вход которого поступают тактовые импульсы ТИ. Выход 12 (фиг. 3 ж) управляет входом занесения счетчика 1. В счетчик заносится содержимое старшей части ячейки блока 9 памяти, выбранной по адресу, установленному в разрядах АО-A3 (память 9 включена на чтение - на вход управления записью подан единичный потенциал с инверсного выхода разряда «Зап.). Выбор памяти 9 осуществляется по тактовым сигналам ТИ|, вход 24, обратной полярности. Инверсные выходы разрядов «Ст. и «Мл. регистра 4 формируют на выходах элементов И-НЕ 19 и 20 по тактовым импульсам THi, поступающим с выхода инвертора 16, сигналы выбора старшей (фиг. 3 з) и младшей (фиг. 3 и) частей блока 9 памяти соот- ветственно. Ключи 10 переключения старшей и младшей частей шины в этом такте (2) не работают.

,. 5

V

5

0

5 5

0

5

0

Команда «3. СК с инверсного4 выхода первого разряда регистра 5 (фиг. 3 е) блокирует на элементе И 11 поступление тактовых импульсов ТИ: - входа 24 на счетный вход счетчика и вход синхронизации регистра 4 микрокоманд, а с прямого выхода разрешает прохождение ТИ| через элемент И 14 (фиг. 3 к) на S-вход разрядов «Ст. и «Зап.. Под воздействием 14 в третьем такте на прямых выходах разрядов «Ст. и «Зап. устанавливается единичный потенциал. Блок 9 памяти включается на запись (на инзерснос выходе разряда «Зап. регистра 4 - ). выбранной оказывается только младшая часть памяти (фиг. 3 и). Ключи 10 переключают старшую часть шины данных, поступающую на первый информационный вход, в младшую (первый его выход подключен к младшей части шины) под управлением элемента И-НЕ 22 (на элементе 22 собраны прямые выходы разрядов «Ст. и «Зап. регистра 4). Одновременно на вход разрешения выходов регистра адреса 2 подается сигнал выборки с выхода элемента И 17 (фиг. 3 л), на котором собраны инверсный выход разряда «Пр. СК, оставшийся в единичном состоянии с 2-го такта, прямой выход разряда «Зап., установившийся в .единичное состояние в 3-м такте и тактовый импульс THi с выхода 16. Следовательно, в 3-м такте происходит запись содержимого регистра адреса 2 в младшую часть выбранной ячейки блока 9 памяти - запоминается текущий адрес прерванной программы, т.е. адрес возврата.

Регистр 2 адреса служит для хранения адреса последней микрокоманды перед переходом, адреса возврата. Если в микрокоманде опроса условии (А1, фиг. 2) разряд УЗ регистра микрокоманд установлен в нуль, то в данном такте (1) блокируется поступление тактового импульса с входа 25 на вход синхронизации регистра 2 на элементе И-НЕ 13. В такте 2 разряд УЗ установлен в нуль по сбросу - также блокируется вход синхронизации. В такте 3 блокировка осуществляется элементом И 21 (фиг. 3 м), на котором собраны команды «3. СК и «Ст. с прямых выходов регистра 5. Следовательно, к моменту записи содержимого регистра 2 в блок 9 памяти в нем сохранился адрес последней микрокоманды перед переходом. В следующем такте (4) выполняется первая микрокоманда (ПМ1, фиг. 2) вызванной подпрограммы.

Последней командой каждой подпрограммы является команда возврата - «З.СК, разряды АО-A3 которой закодированы также, как и разряды УО - УЗ команды вызова. Она отличается от команды вызова «3. СК тем, что разряд «Ст. в микрокоманде установлен равным единице. На прямом выходе разряда «Ст. и инверсном разряда «Зап. регистра 4 появляется единичный потенциал, срабатывает элемент И-НЕ 23, который управляет мультиплексором 10 для переключения младшей части шины данных, поступающей на его второй информационный вход, в старшую (второй выход подключен к старшей части шины), содержимое младшей части ячейки памяти заносится в счетчик 1. В счетчике команд восстанавливается текущий адрес прерванной программы. В следующем такте автомата- чески устанавливается команда «С. СК, которая при возврате логического смысла не имеет, но в этом такте снята блокировка входа синхронизации регистра 2 с выхода элемента 21 (выход второго разряда регистра 5 равен нулю) - регистр 2 кони- рует состояние счетчика 1 (адрес возврата). Эго необходимо при повторных вызовах подпрограммы, если произошел возврат на команду условного перс ко, : Пооч .а: осуществляется либо на комьнд, вызвавшую прерывание (А1, фж. 2), либо i;a следую- щей за ней (M,,fl, фиг. 2) и зависимости от состояния разряда УЗ, соответственно нуль или единица, в микрокоманде опроса условий (А1, фиг. 2).

В подпрограмме также можег быть микрокоманда перехода (А2, фиг. 2). При выполнении условий микрокоманды А2 осуществляется вызов подпрограммы следующего уровня аналогичным способом. Выполняются микрокоманды подпрограммы ПМ1...ПМЗ, затем происходит возврат в под- программ) первого уровня -- выполняются микрокоманды ПМЗ, ПМ4, далее происходит возврат в основную программу на микрокоманду и т.д.

Возможность возврата из подпрограммы па микрокоманду, вызвавшую прерывание, обеспечивает выполнение циклов микропрограммы. При такой организации команд условных переходов облегчен процесс программирования.

Формула изобретения

Микропрограммное устройство управления, содержащее блок памяти микрокоманд регистр адреса, регистр микрокоманд, мультиплексор логических условий, причем выход поля микрокоманды блока памяти микрокоманд соединен с первым информационным входом регистра микрокоманд, вход логических условий устройства соединен с информационным входом мультиплексора логических условий, все выходы регистра микро- команд соединены с группой выходов устройства, выход поля условий регистра микрокоманд соединен с управляющим входом мультиплексора логических условий, отличающееся тем, что, с целью сокращения объема блока памяти микрокоманд за счет исключения поля адреса микрокоманды, в него введены счетчик адреса микрокоманд, блок памяти адресов переходов, блок клю5,, 5 0

5 0

5

0

.с 5

чей, управляющий регистр, триггер прерывания, мультиплексор младших разрядов адреса, с первого по пятый элементы И, с первого по седьмой элементы И-НЕ, элемент НЕ, причем информационный выход счетчика адреса соединен с информационным входом регистра адреса и адресным входом блока памяти микрокоманд, выход поля младших разрядов адреса оперативной памяти которого соединен с первым информационным входом мультиплексора младших разрядов адреса, второй информационный вход которого соединен с выходом поля условий регистра микрокоманд и с управляющим входом мультиплексора логических условий, выход которого соединен с информационным входом триггера прерывания, выход которого соединен с первым входом третьего элемента И и с управляющим входом мультиплексора младших разрядов адреса, выход которого соединен с вторым информационным входом регистра микрокоманд, выход поля младших разрядов адреса которого соединен с адресным входом блока памяти адресов переходов, инверсный выход первого разряда поля управления регистра микрокоманд соединен с первыми входами четвертого и пятого элементов И, выход пятого элемента И соединен с первым входом первого элемента И-НЕ и с первым информационным входом управляющего регистра, инверсный выход второго разряда поля управления регистра микрокоманд соединен с вторым информационным входом управляющего регистра, прямой выход третьего разряда поля управления регистра микрокоманд соединен с первым входом шестого элемента И-НЕ и с вторым входом, четвертого элемента И, инверсный выход третьего разряда поля управления регистра микрокоманд соединен с входом управления записью блока памяти адресов переходов, первым входом седьмого элемента И-НЕ и с вторым входом пятого элемента И, второй вход седьмого элемента И-НЕ соединен с вторым входом шестого элемента И-НЕ и прямым выходом второго разряда поля управления регистра микрокоманд, инверсный выход которого соединен с вторым информационным входом управляющего регистра и первым входом третьего элемента И - НЕ, инверсный выход четвертого разряда поля управления регистра микрокоманд соединен с первым входом четвертого элемента И-НЕ, второй вход которого соединен с вторым входом третьего элемента И-НЕ, третьим входом четвертого элемента И и с выходом элемента НЕ, выход четвертого элемента И соединен с входом разрешения управления третьим состоянием perncfpa адреса, выходы третьего и четвертого элементов И - НЕ соединены соответственно с первым и вторым входами выборки блока памяти адресов переходов,

первый информационный вход-выход которого соединен с информационным входом счетчика адреса, с выходом регистра адреса, первым информационным входом блока ключей, второй информационный вход-выход блока памяти адресов перехода соединен с вторым информационным входом и с первым выходом блока ключей, первый и второй управляющие входы которого соединены соответственно с выходами шестого и седьмого элементов И-НЕ, выход первого элемента И соединен с входом синхронизации регистра микрокоманд и счетным входам счетчика адреса, первый тактовый вход устройства соединен с входом элемента НЕ, вторыми входами второго и третьего элементов И и с первым входом первого элемента И, вход управления занесением счетчика адреса соединен с выходом первого элемента И--НЕ, третий тактовый вход устройства соединен с входами синхронизации триггера прерывания и управляющего регистра и с вторым входом первого элемента И-НЕ, вход синхронизации регистра адреса соединен с выходом второго элемента И-НЕ, первый, второй.

0

,,

третий входы которого соединены соответственно с первым разрядом выхода поля условий регистра микрокоманд, выходом пятого элемента И-НЕ, вторым тактовым входом- устройства, вход установки в «О разрядов первого информационного входа регистра микрокоманд, соединен с выходом третьего элемента И, зходы установки в «1 второго и третьего разрядов информационного входа поля управления регистра микрокоманд соединены с выходом второго элемента И, первый вход которого соединен с первым разрядом прямого выхода управляющего регистра и первым входом пятого элемента И- НЕ, второй вход которого соединен с вторым разрядом прямого выхода управляющего регистра, первый разряд инверсного выхода которого соединен с вторым входом первого элемента И, второй разряд инверсного выхода поля управления регистра микрокоманд соедине;; с вторым входом третьего элемента И-HiЈ. первый информационный вход-выход блока памяти адресов переходов соединен с вторым выходом блока ключей.

| название | год | авторы | номер документа |

|---|---|---|---|

| Процессор с микропрограммным управлением | 1983 |

|

SU1149273A1 |

| Микропрограммное устройство сопряжения | 1989 |

|

SU1700560A1 |

| Устройство микропрограммного управления | 1988 |

|

SU1536380A1 |

| Устройство для сопряжения двух магистралей | 1986 |

|

SU1348874A1 |

| Процессор программируемого контроллера | 1988 |

|

SU1550515A2 |

| Микропрограммное устройство управления | 1983 |

|

SU1156073A1 |

| Процессор для мультипроцессорной системы | 1985 |

|

SU1295410A1 |

| Микропрограммное устройство управления | 1988 |

|

SU1619265A1 |

| Микропрограммное устройство управления | 1987 |

|

SU1490676A1 |

| Процессор программируемого контроллера | 1985 |

|

SU1406595A1 |

Изобретение относится к вычислительной технике и может быть использовано в специализированных вычислительных ЭВМ и вычислительных системах с микропрограммным управлением. Целью изобретения является сокращение объема блока памяти микрокоманд за счет исключения поля адреса микрокоманды. Устройство содержит счетчик 1 адреса микрокоманд, регистр 2 адреса, блок памяти 3 микрокоманд, регистр 4 микрокоманд, управляющий регистр 5, мультиплексор 6 логических условий, триггер 7 прерывания, мультиплексор 8 младших разрядов адреса, блок памяти 9 адресов переходов, блок ключей 10 с тристабильным выходом, первый 11 элемент И, первый 12 и второй 13 элементы И-НЕ, второй 14 и третий 15 элементы И, элемент НЕ 16, четвертый 17 и пятый 18 элементы И, третий 19, четвертый 20, пятый 21, шестой 22 и седьмой 23 элементы И-НЕ. СУЩНОСТЬ ИЗОБРЕТЕНИЯ ЗАКЛЮЧАЕТСЯ В СЛЕДУЮЩЕМ. В ФОРМАТЕ МИКРОКОМАНДЫ ОТСУТСТВУЕТ ПОЛЕ АДРЕСА ПЕРЕХОДА. АДРЕСА ПЕРЕХОДОВ ЗАНИМАЮТ НЕСКОЛЬКО СЛОВ ОПЕРАТИВНОЙ ПАМЯТИ ПРОЦЕССОРА, ПРИЧЕМ АДРЕСА ЭТИХ СЛОВ ЗАКОДИРОВАНЫ СООТВЕТСТВЕННО КОДУ ПОЛЯ УСЛОВИЙ МИКРОКОМАНДЫ. ТАКИМ ОБРАЗОМ, НОМЕР УСЛОВИЯ ЯВЛЯЕТСЯ КОСВЕННЫМ АДРЕСОМ ПЕРЕХОДА. ТАКАЯ ОРГАНИЗАЦИЯ ПОЗВОЛЯЕТ ЗНАЧИТЕЛЬНО СОКРАТИТЬ ОБЪЕМ ПАМЯТИ МИКРОКОМАНД. ВЕТВЛЕНИЯ В МИКРОПРОГРАММЕ, ПРЕДУСМОТРЕННЫЕ УПРАВЛЯЮЩИМ АЛГОРИТМОМ, А ТАКЖЕ УСЛОВНЫЕ И БЕЗУСЛОВНЫЕ ПЕРЕХОДЫ ВЫПОЛНЯЮТСЯ ПО КОМАНДЕ "ЗАПИСЬ СК". КОМАНДА ВОЗНИКАЕТ АППАРАТНО ПО СИГНАЛУ "ПРЕРЫВАНИЕ" ПРИ ВЫПОЛНЕНИИ МИКРОКОМАНДЫ С КОНТРОЛИРУЕМЫМИ ЛОГИЧЕСКИМИ УСЛОВИЯМИ. ДЛЯ ВЫПОЛНЕНИЯ ВЕТВЛЕНИЯ В ЛИНЕЙНЫХ ЧАСТЯХ ПРОГРАММЫ, ДЛЯ ВЫЗОВА ПОДПРОГРАММ И ДЛЯ БЕЗУСЛОВНЫХ ПЕРЕХОДОВ МИКРОКОМАНДА "ЗАПИСЬ СК" УСТАНАВЛИВАЕТСЯ ПРОГРАММНО. 3 ИЛ.

(Начало)

Мп+ г

/И

V

I

ППц

МК опроса

Такты

Фиг. 5

Ч 1-я МК

| Микропрограммное устройство управления с контролем переходов | 1981 |

|

SU1018118A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Микропрограммное устройство управления с контролем | 1985 |

|

SU1267414A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1989-05-23—Публикация

1986-12-12—Подача