Изобретение относится к области цифровой вычислительной техники и может быть использовано в процессорных устройствах ЭВМ и в устройствах цифровой автоматики.

Известны способы и устройства выполнения ЭВО, содержащие триггерные регистры, построенные на основе RS-триггеров, логические элементы И, ИЛИ, НЕ и входы управления работой устройств. Варианты выполнения ЭВО (прием кода, сложение по модулю 2, логическое умножение, логическое сложение, инвертирование, сдвиг кода и др.) рассмотрены в книге М.А. Карцева. Арифметика цифровых машин. М., Наука, 1969 г. стр.264÷278 (Л1). Основными недостатками способов и устройств выполнения ЭВО, приведенных в Л1, является применение двух триггерных регистров для реализации операций, что требует больших аппаратурных затрат, а также требуется, как минимум, два временных такта для приема второго слагаемого или сомножителя и один временной такт для выполнения самой элементарной операции. Известны также способы и устройства выполнения ЭВО на основе устройств с одним триггерным регистром (например, патенты RU №2287849, RU №2419200).

Ближайшим прототипом предлагаемым способам и устройству (СУ) является устройство, выполненное по патенту RU 2288501 С1, в котором реализовано выполнение основных ЭВО с использованием одного RS-триггера, но ряд операций (инвертирование, сдвиг кода, логическое сложение, логическое умножение) выполняется за два временных такта, что снижает быстродействие работы устройства.

Предлагаемые СУ устраняют недостатки известных устройств и прототипа и обеспечивают выполнение основных ЭВО за один временной такт, при этом одновременно выполняется операция выдачи результата операции в другие регистры без временной задержки и независимо от момента переключения RS-триггера.

Целью предлагаемых СУ является повышение быстродействия вычислений за счет выполнения каждой операции за один временной такт с одновременной выдачей информации в другие регистры при минимальных затратах оборудования. Для этого предложены способы выполнения ЭВО приема кода, сложения по модулю два, инвертирования кода триггерного регистра, сдвига кода влево, логического сложения, логического умножения, выполняемых за один временной такт с одновременной выдачей результата операции в другие регистры и устройства. Особенностью способов выполнения ЭВО является выработка условий установки RS-триггеров каждого разряда в «1» или в «0» в зависимости от выполняемой операции и значений кодов Ai, Bi. При этом совмещаются во времени выполнение приема кода с информационных входов, выполнение конкретной ЭВО, выдача результата операции на информационные выходы и занесение результата в RS-тригтеры, что обеспечивает сокращение времени выполнения каждой операции не менее чем в три раза по сравнению с известными способами выполнения аналогичных операций. Кроме того, предлагаемые способы позволяют выполнять ЭВО на основе оборудования только одного RS-тригтера, семи элементов И, пяти элементов ИЛИ и четырех элементов НЕ, при суммарном числе входов всех элементов, равном 39.

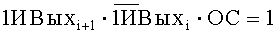

Для реализации способов выполнения ЭВО предложено устройство, построенное на основе n-разрядного триггерного регистра, отличающееся тем, что каждый двоичный разряд содержит один RS-триггер Ai, информационный вход ИВх, по которому поступает второе слагаемое или второй сомножитель, первый информационный выход 1ИВых, второй информационный выход 2ИВых, первый вход управления парафазным приемом кода, второй вход управления сдвигом кода влево, третий вход управления выполнением операции инвертирования всех триггеров регистра; четвертый вход управления приемом кода с инвертированием триггера Ai при Bi=1; пятый вход управления первым тактирующим импульсом 1ТИ, шестой вход управления вторым тактирующим импульсом 2ТИ; содержит первую группу элементов И, ИЛИ, НЕ, обеспечивающих выработку потенциалов управления формированием импульсов установки «0» или «1» триггера tRi, tsi, при этом первый вход управления подключен к первому входу первого элемента И, второй вход которого соединен с информационным входом Bi, выход первого элемента И через первый элемент ИЛИ подключен к входам второго и третьего элементов ИЛИ, выход третьего элемента ИЛИ соединен с входом первого элемента НЕ, выход которого связан с входом четвертого элемента ИЛИ, первый вход второго элемента И соединен с вторым входом управления, второй его вход связан с первым информационным выходом i-1-го разряда, выход второго элемента И подключен к второму входу первого элемента ИЛИ, третий вход второго элемента ИЛИ соединен с третьим входом управления, второй вход третьего элемента ИЛИ соединен с четвертым входом управления, первый вход седьмого элемента И подключен к четвертому входу управления, его второй вход соединен с информационным входом Bi, выход седьмого элемента И связан с входами четвертого и второго элементов ИЛИ, выходы которых соединены с вторыми входами четвертого и третьего элементов И соответственно, третьи входы упомянутых элементов И соединены с входом и выходом второго элемента НЕ, вход этого элемента подключен к выходу шестого элемента И, выход которого является первым информационным выходом i-го разряда 1ИВыхi, первые входы третьего и четвертого элементов И подключены к пятому и шестому входам управления тактирующими импульсами соответственно. Содержит вторую группу элементов И, НЕ, обеспечивающих формирование единичного tsi и нулевого tRi импульсов установки RS-триггера. При этом выходы четвертого и третьего элементов И через четвертый и третий элементы НЕ подключены к нулевому и единичному входам RS-триггера соответственно, при этом третьи входы четвертого и третьего элементов И связаны с входом и выходом второго элемента НЕ, вход этого элемента НЕ соединен с выходом шестого элемента И, содержит третью группу элементов ИЛИ, И, обеспечивающих задержку выдачи сигнала с единичного выхода RS-триггера на время длительности тактирующих импульсов, при этом первый вход пятого элемента ИЛИ соединен с единичным выходом RS-триггера, второй его вход соединен с выходом четвертого элемента И, выход пятого элемента ИЛИ подключен к первому входу шестого элемента И, второй вход которого соединен с выходом третьего элемента НЕ, выход шестого элемента И является первым информационным выходом i-го разряда 1ИВх и соединен с входом второго элемента НЕ, содержит четвертую группу элементов ИЛИ, И, обеспечивающих выдачу результата выполнения операции i-го разряда на второй информационный выход, при этом первый вход шестого элемента ИЛИ соединен с выходом третьего элемента И, второй вход шестого элемента ИЛИ подключен к единичному выходу RS-триггера, выход шестого элемента ИЛИ подключен к первому входу пятого элемента И, его второй вход соединен с выходом четвертого элемента НЕ, выход пятого элемента И является вторым информационным выходом i-го разряда, который используется для выдачи результатов операции в другие регистры без временной задержки на время длительности тактирующих импульсов. Предлагаемое устройство позволяет расширить перечень выполняемых ЭВО, повысить быстродействие их выполнения при минимальных затратах оборудования. Для пояснения принципа работы СУ на рисунке приведена функциональная схема одного разряда предлагаемого устройства. На рисунке приняты следующие обозначения: элементы И 1-7, элементы ИЛИ 8-13, элементы НЕ 14-17, информационный вход (ИВх) - 24, первый и второй информационные выходы 1ИВых, 2ИВых - 25, 26, первый вход управления (ВУ) парафазным приемом кода с информационных входов - 18, второй ВУ выполнением сдвига кода влево - 21, третий ВУ инвертированием всех триггеров регистра 20, четвертый ВУ выполнением приема кода с инвертированием Ai при Bi=1 - 19, первый и второй входы тактирующих импульсов 1ТИ, 2ТИ - 22, 23, информационная связь i-го разряда с i+1-м разрядом - 27, RS-триггер (Tr) или Ai - 28. Логические элементы одного разряда условно разделены на четыре группы. Первая группа - И 1, 2, 7, ИЛИ 1-4, НЕ 1. Вторая группа - И3, 4, НЕ 15, 16, 17. Третья группа - ИЛИ 11, И 5. Четвертая группа - ИЛИ 10, И6.

Предлагаемое устройство выполнено следующим образом. В каждом ряде первый и второй входы И1 соединены с ВУ18 и ИВх24. Выход И1 через ИЛИ 8, 9 соединен с вторым входом И3. Выход ИЛИ 8 через ИЛИ 12 подключен к входу НЕ 14, выход которого через ИЛИ 13 соединен с вторым входом И4. Первые входы И7, ИЛИ 12 связаны с ВУ 19. Второй вход И7 подключен к входу 24. Выход И7 соединен с входами ИЛИ 9, 13. Третьи входы И3, 4 связаны с входами 22 и 23. Первые входы элементов И4, 3 подключены к входу и выходу НЕ 15 соответственно. Вход НЕ 15 подключен к выходу И6 и к входу И2 i+1-го разряда. Выход И4 подключен к входам ИЛИ 10, НЕ 17. Выход НЕ 17 соединен с И5 и с нулевым входом Tr28. Выход ИЛИ10 подключен к первому входу И6, второй его вход связан с выходом НЕ 16. Выход И6 является первым информационным выходом 1-го разряда 25. Выход И3 соединен с входами ИЛИ 11, НЕ 16. Выход НЕ 16 подключен к единичному входу Тг28. Вторые входы ИЛИ 10, 11 связаны с единичным выходом Tr28. Выход ИЛИ 11 подключен к входу И5, выход которого является вторым информационным выходом i-того разряда 26.

Рассмотрим работу устройства при выполнении ЭВО.

В исходном состоянии (в статике) на ВУ 18-23 отсутствуют высокие потенциалы, с выхода НЕ 14 на вход И4 поступает высокий потенциал. Если Tr28 хранит код «0» на выходах 25, 26 отсутствуют высокие потенциалы, если в Tr28 занесен код «1» - на выходах 25 и 26 присутствуют высокие потенциалы, на входах НЕ 15 и И4 также будут высокие потенциалы, разрешающие работу И4 и запрещающие работу И3. При поступлении на ВУ23 тактирующего импульса Tr28 будет установлен в «0».

1. Операция приема кода (ОПК).

Для выполнения (ОПК) на ВУ18 подают высокий потенциал, разрешающий прием кода В. В случае высокого потенциала на ВУ24, что соответствует Bi=1, высокий потенциал с И1, через ИЛИ 8, 9 поступает на второй вход И3. При выполнении условия

В том случае, если Bi=0, Ai=1 на выходе И1, ИЛИ 8,9 не будет высокого потенциала, разрешающего работу И3. В то же время высокий потенциал с выхода НЕ14 через ИЛИ 13 поступит на второй вход И4 и разрешит его работу. При поступлении сигнала на ВУ 23 на выходе И4 будет сформирован импульс установки Ai в «0» tRi, который поступит через ИЛИ 10, И6 на выход 25 и сохранит условия формирования tRi. Одновременно tRi поступит на вход НЕ 17. Инверсное значение tRi запретит выдачу информации на выход 26 и установит Ai в «0». Результат ОПК будет храниться в триггерах А, прямой код регистра будет выдаваться на выходы 25 и 26,

Операция инвертирования кода (ОИК).

До выполнения ОИК каждый Tr28 хранит код «0» или «1». Если Tr28 хранит код «1», то высокий потенциал с единичного выхода Tr28 по цепи элементов ИЛИ 10, И6 поступает на первый информационный выход 25. При этом упомянутый потенциал поступает на входы И4, НЕ 15. Этим разрешается работа И4 и запрещается работа И3. При выполнении ОИК на ВУ20 подается высокий потенциал, разрешающий работу И3. Одновременно на ВУ 22, 23 подаются тактирующие импульсы 1ТИ, 2ТИ, разрешающие работу И3, 4. При выполнении условия Ai·НЕ14·ВУ23=1 на выходе И4 вырабатывается импульс установки «0» Tr28 tRi. Упомянутый импульс через НЕ 17 поступает на нулевой вход Tr28, т.е. выполняет инвертирование кода и запрещает выдачу информации на выход 26 на время длительности импульса tRi. Одновременно tRi поступает на входы ИЛИ10, И6, чем обеспечивается сохранение значения высокого потенциала на выходах И6 и на входах И4, НЕ 15. При выполнении условия Ai·ВУ20·ВУ22=1 на выходе И3 вырабатывается импульс установки Tr28 в «1» tsi. Упомянутый импульс через НЕ 16 поступает на единичный вход Tr28, т.е. выполняет инвертирование кода триггера и запрещает выдачу информации на вход 25 на время длительности импульса tsi. Одновременно tsi поступает на входы ИЛИ 11, И5, чем обеспечивается выдача «будущего» единичного значения Tr28, независимо от времени переключения этого триггера, и поступает на второй информационный выход 26. На этом ОИК завершается. Результат операции хранится в регистре А, время выполнения операции равно одному временному такту, равному длительности тактирующих импульсов.

2. Операция сдвига кода (ОСК) влево.

Операция позволяет сдвинуть код, хранящийся в регистре А, на один разряд влево за один временной такт (время такта равно длительности тактирующих импульсов 1ТИ, 2ТИ). Для выполнения ОСК на ВУ21 подается высокий потенциал. При Ai-1=1 на выходе И2 i-го разряда вырабатывается высокий потенциал, который через ИЛИ8, 9 поступит на второй вход И3. Одновременно высокий потенциал с выхода И2 по цепи элементов ИЛИ 8, 12, НЕ 14, ИЛИ 13 запрещает работу И4. Тактирующий импульс, поступивший по входу 22 на вход И3, выработает на выходе элемента И3 импульс установки Ai в «1» tsi. Одновременно tsi по цепи элементов ИЛИ 11, И5 поступит на выход 26. Инверсным значением tsi запрещается выдача информации на выход 25, чем обеспечивается сохранение высокого потенциала на выходе НЕ 15, необходимого для обеспечения надежной работы переключения Tr28. При Ai=Ai-1=«1» или «0» Tr28 сохраняет свое состояние.

3. Операция сложения по модулю два (ОСМ2).

Для выполнения операции на ВУ 19 подается высокий потенциал, разрешающий прием кода с информационного входа 24. Одновременно, сигнал ВУ 19 через ИЛИ 12 поступает на вход НЕ 14 и исключает влияние этого элемента на формирование потенциала управления элемента И4. При Bi=1 на выходе И7 вырабатывается потенциал разрешения работы И4, 3.

При поступлении на третьи входы И4, 3 тактирующих импульсов с входов 22, 23 при Ai=1 с выхода И4 вырабатывается импульс установки Tr28 в «0», а при Ai=0 с выхода И3 вырабатывается импульс установки Tr28 в «1». Таким образом, состояние Tr28 i-го разряда будет проинвертировано при Bi=1.

Работа устройства по одновременному выполнению выдачи результата операции рассмотрена при описании работы выполнения инвертирования кода (п.2).

4. Операция логического сложения (ОЛС).

Для выполнения ОЛС на ВУ18 подают высокий потенциал и принимают информацию с входа 24. При Bi=1 сигнал с выхода И1 поступает через элементы ИЛИ 8, 9 на второй вход И3. При нулевом значении Tr28 на выходе НЕ 15 будет высокий потенциал. Тактирующий импульс, поступивший по входу 22, поступит на третий вход И3 и выработает импульс установки Tr28 в «1» tsi. Одновременно tsi через ИЛИ11, И5 поступит на выход 26. Инверсное значение tsi поступит на вход И6 и запретит на время длительности импульса возможное появление высокого потенциала на выход И6. Результат ОЛС будет храниться в регистре А. На информационные выходы 25 и 26 будет выдаваться прямой код ОЛС. Таким образом, при выполнении операции одновременно за один временной такт выполняется три элементарных операции: прием кода с информационного входа ОЛС и выдача кода на первый и второй информационные выходы, причем в ходе выполнения операции на выход 25 сигнал выдается с временной задержкой, равной длительности тактирующего импульса, а на выход 26 сигнал выдается без задержки. Для выполнения операции ОЛС не требуется дополнительного оборудования по сравнению с оборудованием базовой операции инвертирования кода регистра.

5. Операция логического умножения (ОЛУ).

Для выполнения ОЛУ на ВУ 18 подают высокий потенциал и разрешают прием информации с входа 24. При Ai=1 и Bi=0 с выхода HE14 через ИЛИ 13 на второй вход И4 поступает высокий потенциал, на первый вход этого элемента поступает высокий потенциал с выхода Tr28, на третий вход упомянутого элемента И подают тактирующий импульс с входа 23. При выполнении условия ВУ23·НЕ14·Аi=1 на выходе И4 вырабатывается импульс установки Tr28 в «0» tRi. Выработанный импульс через ИЛИ 10 поступает на вход И6 и «сохраняет» потенциал Tr28, т.е. обеспечивает задержку сигнала на выходе И6 на время, равное длительности tRi. Одновременно сигнал с выхода НЕ 17 поступает на вход И5 и запрещает выдачу информации на второй информационный выход 26, т.е. результат операции ОЛУ выдается в другие регистры и устройства без временной задержки на время длительности tRi. В случае Ai=Bi значение Ai сохраняется. Операция выполняется за один временной такт, для ее выполнения не требуется дополнительного оборудования по сравнению с оборудованием базовой операции инвертирования. Одновременно выполняется операция выдачи результата ОЛУ в другие регистры и устройства.

Таким образом, предлагаемые способы и устройство позволяют выполнить каждую из основных ЭВО за один временной такт, что обеспечит повышение быстродействия работы устройства в 3-4 раза. При этом используется только один регистр, каждый разряд которого построен на основе одного Rs-триггера, четырех элементов НЕ, семи элементов И и шести элементов ИЛИ. При этом выполнение элементарных операций логического умножения, логического сложения, установки «0» и «1» всех триггеров не требует дополнительного оборудования.

| название | год | авторы | номер документа |

|---|---|---|---|

| СПОСОБ И УСТРОЙСТВО ВЫПОЛНЕНИЯ АРИФМЕТИЧЕСКИХ И ЛОГИЧЕСКИХ ОПЕРАЦИЙ | 2005 |

|

RU2295751C2 |

| СПОСОБЫ ВЫПОЛНЕНИЯ ЭЛЕМЕНТАРНЫХ ВЫЧИСЛИТЕЛЬНЫХ ОПЕРАЦИЙ (ЭВО) И УСТРОЙСТВО ИХ ОСУЩЕСТВЛЕНИЯ | 2013 |

|

RU2553221C2 |

| СЧЕТЧИК ИМПУЛЬСОВ (СИ) | 2015 |

|

RU2579524C1 |

| СПОСОБ И УСТРОЙСТВО ВЫЧИТАНИЯ ДВОИЧНЫХ КОДОВ | 2010 |

|

RU2410746C1 |

| СЧЕТЧИК ИМПУЛЬСОВ | 2005 |

|

RU2284654C2 |

| СПОСОБ И УСТРОЙСТВО ВЫПОЛНЕНИЯ ВЫЧИСЛИТЕЛЬНЫХ ОПЕРАЦИЙ ПРИ МИНИМАЛЬНЫХ ЗАТРАТАХ ОБОРУДОВАНИЯ | 2005 |

|

RU2287849C1 |

| РЕВЕРСИВНЫЙ РЕГИСТР СДВИГА ВЛАСОВА | 2006 |

|

RU2309536C1 |

| КОМБИНАЦИОННО-НАКАПЛИВАЮЩИЙ СУММАТОР | 2006 |

|

RU2306596C1 |

| СПОСОБ И УСТРОЙСТВО СЛОЖЕНИЯ ДВОИЧНЫХ КОДОВ | 2013 |

|

RU2537046C2 |

| НАКАПЛИВАЮЩИЙ СУММАТОР | 2005 |

|

RU2288501C1 |

Изобретение относится к области цифровой вычислительной техники и устройствам цифровой автоматики. Техническим результатом является повышение быстродействия выполнения ЭВО при минимальных затратах оборудования. Устройство содержит в каждом двоичном разряде один RS-триггер, семь логических элементов И, пять элементов ИЛИ, четыре элемента НЕ, информационный вход, первый и второй информационные выходы, шесть входов управления. Способ и устройство для его реализации обеспечивают выполнение таких логических операций, как прием кода в триггеры регистра, инвертирование кода всех триггеров регистра, операция сдвига принятого кода влево, операция сложения по модулю два, логическое сложение двух двоичных кодов, логическое умножение 7. н.п. ф-лы, 1 ил.

1. Способ выполнения элементарной вычислительной операции приема кода в триггерный регистр, отличающийся тем, что код первого числа хранят в триггерном регистре А, каждый разряд которого содержит один RS-триггер Ai, информационный вход ИВх, первый и второй информационные выходы 1ИВых, 2ИВых, первый и второй входы тактирующих импульсов 1ТИ, 2ТИ, первый вход управления парафазным приемом кода с ИВх, второй вход управления приемом кода с инвертированием Ai при Bi=1, элементы И, ИЛИ, НЕ; код второго числа В принимают в регистр А с информационных входов, при этом прием выполняют парафазным кодом или с инвертированием триггеров А, в случае выполнения операции приема числа парафазным кодом разрешают прием кода В с ИВх, при Bi=1 и Ai=0 формируют потенциал разрешения выработки импульса установки Ai в «1» tsi, формируют первый и второй тактирующие импульсы 1ТИ, 2ТИ и устанавливают триггер Ai в «1», одновременно выработанным импульсом tsi разрешают выдачу принимаемого кода на второй информационный выход 2ИВых, инверсным значением tsi запрещают выдачу кода на первый информационный выход 1ИВых, чем обеспечивают выдачу принимаемого кода Bi на 2ИВых и в другие регистры и устройства без временной задержки сигнала и сохраняют условия формирования tsi независимо от момента переключения Ai в «1», т.е. обеспечивают «задержку» сигнала 1ИВых на время длительности импульса tsi, при Bi=0, Ai=1 разрешают выработку импульса установки Ai в «0» tRi, которым искусственно поддерживают высокий потенциал на первом информационном выходе, инверсным значением импульса tRi запрещают выдачу кода Ai на второй информационный выход, т.е. выдают результат операции без временной задержки.

2. Способ выполнения ЭВО инвертирования кода всех триггеров регистра, отличающийся тем, что каждый разряд регистра выполнен на одном RS-триггере Ai, содержит третий вход управления ВУ операцией инвертирования кода, первый и второй входы тактирующих импульсов 1ТИ, 2ТИ, первый и второй информационные выходы 1ИВых, 2ИВых, при этом до начала выполнения операции прямой код Ai выдают на 1ИВых и 2ИВых, при 1ИВых=Ai=1 разрешают формирование импульса установки Ai в «0» tRi и запрещают формирование импульса установки Ai в «1» tsi, в ходе выполнения операции инвертирования третьим потенциалом ВУ операцией инвертирования разрешают формирование импульса tsi, активируют первый и второй тактирующие импульсы, при Ai=0 вырабатывают tsi, которым выдают прямой код результата операции на 2ИВых, инверсным значением tsi запрещают выдачу информации по 1ИВых и устанавливают триггер Ai в «1», при Ai=1 вырабатывают импульс tRi, которым «поддерживают» высокий потенциал на 1ИВых, инверсным сигналом tRi устанавливают Ai в «0» и запрещают выдачу результата операции на 2ИВых, операцию выполняют за один временной такт, при этом совмещают во времени инвертирование и выдачу результата операции на второй информационный выход.

3. Способ выполнения элементарной вычислительной операции сдвига кода влево, отличающийся тем, что сдвигаемый код хранят в n-разрядном триггерном регистре, каждый разряд которого содержит RS-триггер, вход управления выполнением операции сдвига ОС, первый и второй входы тактирующих импульсов 1ТИ, 2ТИ, первый и второй информационные выходы 1ИВыхi, 2ИВыхi; при этом до начала выполнения операции прямой код RS-триггера выдают на 1ИВыхi и 2ИВыхi, при 1ИВыхi=1 разрешают формирование импульса установки RS-триггера tRi в «0», запрещают формирование импульса установки RS-триггера tsi в «1» и управляют выработкой потенциала сдвига кода в i+1-м разряде; в ходе выполнения операции сдвига кода влево на один разряд за один временной такт потенциалом ОС разрешают прием информации с выхода 1ИВыхi в i+1-й разряд парафазным кодом, т.е. при 1ИВыхi=1 разрешают выработку сигнала tsi+1 и запрещают выработку сигнала tRi+1, при 1ИВыхi=0 разрешают выработку tRi+1 и запрещают выработку tsi+1, одновременно импульсы 1ТИ и 2ТИ, если выполняется условие

4. Способ выполнения элементарной вычислительной операции сложения по модулю два, при котором код первого слагаемого хранят в триггерном регистре А, код второго слагаемого принимают с информационных входов ИВх, отличающийся тем, что каждый двоичный разряд содержит один RS-триггер Ai, информационный вход ИВхi, первый и второй информационные выходы 1ИВыхi, 2ИВыхi, первый и второй входы тактирующих импульсов 1ТИ, 2ТИ, вход управления выполнением операции сложения по модулю два, до начала выполнения операции код триггера Ai выдают на 1ИВыхi и 2ИВыхi, при этом потенциалом с 1ИВыхi разрешают работу элемента И, выработки импульса установки Ai в «0» и запрещают работу элемента И выработки импульса установки Ai в «1», в ходе выполнения операции одновременно разрешают прием кода Bi с информационного входа по счетному входу Ai, формируют первый и второй тактирующие импульсы 1ТИ, 2ТИ, при выполнении условия Аi·Bi·2ТИ=1 формируют импульс установки Ai в «0» tRi, выработанным импульсом имитируют задержку потенциала Ai=1, подключая tRi через элементы ИЛИ, И к первому информационному выходу, одновременно инверсным значением tRi запрещают выдачу результата операции на второй информационный выход; при значении Ai=0 потенциал с выхода 1ИВыхi инвертируют и разрешают выработку импульса установки Ai в «1», при этом импульс tsi через элементы ИЛИ, И подключают к второму информационному выходу 2ИВыхi, чем обеспечивают выдачу результата выполнения операции в другие регистры и устройства без временной задержки на время тактирующего импульса 1ТИ, результат выполнения операции сложения по модулю два хранят в регистре А и выдают его по информационным выходам в другие регистры и устройства, при этом код 1ИВыхi равен коду 2ИВыхi.

5. Способ выполнения элементарной операции логического сложения двух двоичных кодов, при этом код первого слагаемого хранят в триггерном регистре А, код второго слагаемого В принимают с информационных входов, отличающийся тем, что каждый двоичный разряд содержит один RS-триггер Ai, первый и второй информационные выходы 1ИВых, 2ИВых, первый и второй тактирующие импульсы 1ТИ, 2ТИ, логические элементы И, ИЛИ, НЕ, до начала выполнения операции прямой код триггера Ai выдают на 1ИВыхi и 2ИВыхi информационные выходы, в ходе выполнения операции при Ai=0 разрешают формирование импульса установки Ai в «1» tsi, разрешают прием кода второго слагаемого В, при Bi=1 разрешают формирование tsi, формируют первый тактирующий импульс 1ТИ, при выполнении условия Ai·Bi·1ТИ=1, на выходе третьего элемента И формируют tsi, одновременно импульсом tsi выдают результаты на 2ИВыхi, инверсным сигналом tsi запрещают выдачу информации на 1ИВыхi и устанавливают триггер Ai в «1», результат операции логического сложения хранят в регистре А и выдают его на 1ИВых и 2ИВых, при этом на информационном выходе 1ИВых результат операции появляется с временной задержкой на время длительности tsi, на 2ИВыхi результат выполнения операции логического сложения выдают без временной задержки на время длительности tsi

6. Способ выполнения элементарной вычислительной операции логического умножения, отличающийся тем, что код первого сомножителя хранят в триггерном регистре А, код второго сомножителя В принимают с информационных входов, каждый разряд регистра содержит один RS-триггер Ai, первый вход управления парафазным приемом кода, первый и второй входы тактирующих импульсов 1ТИ, 2ТИ, первый и второй информационные выходы 1ИВых, 2ИВых; до начала выполнения операции на первый и второй информационные выходы выдают прямой код триггера Ai, при Ai=1 разрешают работу элемента И формирования импульса установки триггера Ai в «0» tsi, в ходе выполнения операции разрешают прием парафазным кодом второго сомножителя В, при Bi=0 высокий потенциал с выхода первого элемента НЕ поступает на второй вход элемента И формирования tRi, на третий вход упомянутого элемента И подключают второй тактирующий импульс, при выполнении соотношения

7. Устройство выполнения элементарных вычислительных операций, построенное на основе n-разрядного триггерного регистра, элементов И, ИЛИ, НЕ, отличающееся тем, что каждый двоичный разряд содержит один RS-триггер Ai, информационный вход ИВх, по которому поступает второй сомножитель Bi, первый информационный выход 1ИВых, второй информационный выход 2ИВых, первый вход управления парафазным приемом кода, второй вход управления сдвигом кода влево, третий вход управления выполнением операции инвертирования всех триггеров устройства; четвертый вход управления приемом кода с инвертированием триггера Ai при Bi=1; пятый вход управления первым тактирующим импульсом 1ТИ, шестой вход управления вторым тактирующим импульсом 2ТИ, содержит первую группу элементов И, ИЛИ, НЕ, обеспечивающих выработку потенциалов управления формированием импульсов установки «0» или «1» триггера tRi, tsi, при этом первый вход управления подключен к первому входу первого элемента И, второй вход которого соединен с информационным входом ИВх, выход первого элемента И через первый элемент ИЛИ подключен к входам второго и третьего элементов ИЛИ, выход третьего элемента ИЛИ соединен с входом первого элемента НЕ, выход которого связан с входом четвертого элемента ИЛИ, первый вход второго элемента И соединен с вторым входом управления, второй его вход связан с первым информационным выходом i-1-го разряда, выход второго элемента И подключен к второму входу первого элемента ИЛИ, третий вход второго элемента ИЛИ соединен с третьим входом управления, второй вход третьего элемента ИЛИ соединен с четвертым входом управления, первый вход седьмого элемента И подключен к четвертому входу управления, его второй вход соединен с информационным входом ИВх, выход седьмого элемента И связан с входами четвертого и второго элементов ИЛИ, выходы которых соединены с вторыми входами четвертого и третьего элементов И соответственно, третьи входы упомянутых элементов И соединены с входом и выходом второго элемента НЕ, вход этого элемента подключен к выходу шестого элемента И, выход которого является первым информационным выходом i-го разряда 1ИВыхi, первые входы третьего и четвертого элементов И подключены к пятому и шестому входам управления тактирующими импульсами соответственно; содержит вторую группу элементов И, НЕ, обеспечивающих формирование единичного tsi и нулевого tRi импульсов установки RS-триггера, при этом выходы четвертого и третьего элементов И через четвертый и третий элементы НЕ подключены к нулевому и единичному входам RS-триггера соответственно, вход второго элемента НЕ соединен с выходом шестого элемента И; содержит третью группу элементов ИЛИ, И, обеспечивающих задержку выдачи сигнала с единичного выхода RS-триггера на время длительности тактирующих импульсов, при этом первый вход пятого элемента ИЛИ соединен с единичным выходом RS-триггера, второй его вход соединен с выходом четвертого элемента И, выход пятого элемента ИЛИ подключен к первому входу шестого элемента И, второй вход которого соединен с выходом третьего элемента НЕ, выход шестого элемента И является первым информационным выходом i-го разряда 1ИВыхi и соединен с входом второго элемента НЕ; содержит четвертую группу элементов ИЛИ, И, обеспечивающих выдачу результата выполнения операции i-го разряда на второй информационный выход 2ИВыхi, при этом первый вход шестого элемента ИЛИ соединен с выходом третьего элемента И, второй вход шестого элемента ИЛИ подключен к единичному выходу RS-тригтера, выход шестого элемента ИЛИ подключен к первому входу пятого элемента И, его второй вход соединен с выходом четвертого элемента НЕ, выход пятого элемента И является вторым информационным выходом i-го разряда 2ИВыхi, который используется для выдачи результатов операции в другие регистры без временной задержки на время длительности тактирующих импульсов.

| НАКАПЛИВАЮЩИЙ СУММАТОР | 2005 |

|

RU2288501C1 |

| СУММАТОР КОМБИНАЦИОННО-НАКАПЛИВАЮЩЕГО ТИПА | 2004 |

|

RU2262736C1 |

| Способ приготовления лака | 1924 |

|

SU2011A1 |

| УНИВЕРСАЛЬНАЯ ТРАНСФОРМИРУЕМАЯ ОПАЛУБКА ДЛЯ ИЗГОТОВЛЕНИЯ ПРОТЯЖЕННЫХ СТРОИТЕЛЬНЫХ КОНСТРУКЦИЙ, ПРОТЯЖЕННАЯ СТРОИТЕЛЬНАЯ КОНСТРУКЦИЯ, РИГЕЛЬ И БОЛЬШЕПРОЛЕТНАЯ БАЛКА, ИЗГОТОВЛЕННЫЕ В ЭТОЙ ТРАНСФОРМИРУЕМОЙ ОПАЛУБКЕ | 2005 |

|

RU2289006C1 |

| JP H06149542 A, 27.05.1994 | |||

| Способ приготовления мыла | 1923 |

|

SU2004A1 |

Авторы

Даты

2014-01-27—Публикация

2012-03-29—Подача