Изобретение относится к области вычислительной техники и может быть использовано в процессорах ЭВМ и в устройствах цифровой автоматики. Известны способы и устройства сложения двоичных кодов, заключающиеся в последовательном выполнении элементарных операций (ЭО) приема слагаемых в триггерные регистры, первого сложения по модулю два, формирование переноса в каждом разряде и выполнения второго сложения по модулю два. Способы и устройство суммирования двоичных кодов детально рассмотрены в кн.: Карцев М.А. «Арифметика цифровых машин», М., изд-во «Наука», 1969 г., стр.247-252, рис.2.45 и Дроздов Е.А. и др. «Электронные вычислительные машины Единой системы», М., изд-во «Машиностроение», 1981 г., стр.76-80. Общим недостатком известных способов и устройств является необходимость использования трех регистров, выполненных на основе RS-триггеров, и затрат не менее четырех-пяти временных тактов для выполнения операции сложения. Это определяет быстродействие работы и затраты оборудования для построения устройства. Наиболее близким, принятым за прототип, является суммирующее устройство, приведенное в кн.: Шигин А.Г. «Цифровые вычислительные машины», М., изд-во «Энергия», 1971 г., стр.220-223, рис.9.31. Недостатком прототипа является наличие линий задержки сигналов на входе первых триггеров, а суммарное время задержки сигнала переноса равняется Т3=2nτ (n - число двоичных разрядов, 2 τ - временная задержка элементов И, ИЛИ цепи переноса одного разряда). Предложенные способ и устройство устраняют отмеченные недостатки.

Целью изобретения является повышение быстродействия выполнения операции сложения за счет снижения времени формирования сигнала переноса и при минимальных затратах оборудования, исчисляемого суммарным числом входов логических элементов И, ИЛИ, НЕ, на основе которых построен каждый разряд устройства.

Для этого предложен способ, заключающийся в совмещении выполнения ЭО приема второго слагаемого, первого сложения по модулю два, формирования поразрядного

Также предложено устройство сложения двоичных кодов, содержащее первый и второй регистры А и В, каждый разряд устройства содержит первый и второй RS-триггеры, информационный вход, первый вход управления приемом второго слагаемого в регистр В, второй вход управления выполнением первого сложения по модулю два, третий вход управления выполнением второго сложения по модулю два, при этом упомянутые входы управления подключены к первым входам первого, второго, третьего элементов И, соответственно, выход первого элемента И соединен с единичным входом второго RS-триггера, выходы второго и третьего элементов И подключены к первому и второму входам первого элемента ИЛИ, выход которого подключен к первым входам четвертого и пятого элемента И, вторые входы первого - третьего элементов И соединены с информационным входом, единичным выходом второго триггера и входом переноса из младшего разряда

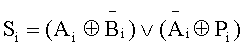

Для пояснения работы на Фиг.1 приведена функциональная схема двух разрядов устройства и приняты следующие обозначения: элементы И 1-8; элементы ИЛИ 9-11; элементы НЕ 12-14; RS-триггеры (Tr) 15, 16; информационный вход (ИВ) 17; вход управление (ВУ) приемом второго слагаемого 18; ВУ первым сложением по модулю два 19; ВУ выполнением вторым сложением по модулю два 20; ВУ формированием имитационного переноса 21; выход переноса из младшего разряда (Pi-1) 22.

Устройство сложения выполнено следующим образом. Информационный вход 17 подключен к И 1, второй вход его соединен с ВУ 18. Выход И 1 соединен с единичным входом Tr 16 и ИЛИ 9. Выход Tr 16 соединен с входами И 2, 6. Вторые входы И 2, 3 подключены к ВУ 19, 20 соответственно. Выходы И 2, 3 через ИЛИ 9 соединены с первыми входами И 4, 5. Вторые входы И 4, 5 соединены с входом и выходом НЕ 12, выходы И 4, 5 через НЕ 13, 14 подключены к нулевому и единичному входам Tr 15 соответственно. Выход И 4 через ИЛИ 10 соединен с первым входом И 8. Единичный выход Тг 15 такта через ИЛИ 10 соединен с И 8. Второй вход И 8 связан с выходом НЕ 14. Выход И 8 соединен с входами НЕ 12 и И 7. Второй вход И 7 связан с выходом ИЛИ 11 младшего разряда. Выходы И 6, 7 подключены к входам ИЛИ 11. К третьему входу ИЛИ 11 подключен ВУ 21.

Рассмотрим работу устройства при выполнении операции сложения. В исходном состоянии, до начала выполнения операции (в статике) в Tr 15 хранится код первого числа А, как результат выполнения предыдущей операции. Tr 16 установлен в нуль или прием в него осуществляется парафазным кодом. На ВУ 18-21 отсутствуют высокие потенциалы.

Операция сложения выполняется за два временных такта (tl, t2). По t1 одновременно выполняют прием кода с ИВ в Tr 16. Для этого на ВУ 18 подают высокий потенциал, разрешающий проходить сигналу с ИВ через И 1 на единичный вход Tr 16 и через ИЛИ 9 на счетный вход Tr 15. Таким образом выполняются ЭО приема кода и первое сложение по модулю два. После переключения Tr 15, 16 на выходе И 6 вырабатывается потенциал поразрядного переноса

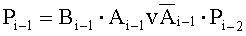

По второму временному такту, после снятия высокого потенциала с ВУ 21, в цепи переносов каждого разряда остаются потенциалы только реальных переносов, сформированных во время t1, и определяемых согласно соотношения

Таким образом, предложенные способ и устройство позволяют выполнять операцию сложения, исключив влияние числа разрядов на быстродействие выполнения этой операции, и при минимальных затратах оборудования (два RS-триггера, 8 элементов И, три элемента ИЛИ и три элемента НЕ). При этом устройство может выполнять ЭО инвертирования кода регистра А, сложение кодов по модулю два за один временной такт t1 без увеличения аппаратурных затрат.

| название | год | авторы | номер документа |

|---|---|---|---|

| СПОСОБЫ ВЫПОЛНЕНИЯ ЭЛЕМЕНТАРНЫХ ВЫЧИСЛИТЕЛЬНЫХ ОПЕРАЦИЙ (ЭВО) И УСТРОЙСТВО ИХ ОСУЩЕСТВЛЕНИЯ | 2013 |

|

RU2553221C2 |

| СПОСОБ И УСТРОЙСТВО ВЫПОЛНЕНИЯ ВЫЧИСЛИТЕЛЬНЫХ ОПЕРАЦИЙ ПРИ МИНИМАЛЬНЫХ ЗАТРАТАХ ОБОРУДОВАНИЯ | 2005 |

|

RU2287849C1 |

| СПОСОБ И УСТРОЙСТВО ВЫПОЛНЕНИЯ АРИФМЕТИЧЕСКИХ И ЛОГИЧЕСКИХ ОПЕРАЦИЙ | 2005 |

|

RU2295751C2 |

| УСТРОЙСТВО СУММИРОВАНИЯ ДВОИЧНЫХ КОДОВ | 2008 |

|

RU2381547C2 |

| СПОСОБ И УСТРОЙСТВО УМНОЖЕНИЯ ДВОИЧНО-ДЕСЯТИЧНЫХ КОДОВ | 2009 |

|

RU2410745C1 |

| СПОСОБ И УСТРОЙСТВО СЛОЖЕНИЯ ДВОИЧНЫХ КОДОВ | 2008 |

|

RU2388041C2 |

| РЕВЕРСИВНЫЙ РЕГИСТР СДВИГА ВЛАСОВА | 2006 |

|

RU2309536C1 |

| СУММАТОР НАКАПЛИВАЮЩЕГО ТИПА | 2003 |

|

RU2269153C2 |

| СУММАТОР НАКАПЛИВАЮЩЕГО ТИПА | 2003 |

|

RU2261469C1 |

| НАКАПЛИВАЮЩИЙ СУММАТОР | 2005 |

|

RU2288501C1 |

Изобретение относится к области цифровой вычислительной техники и автоматики и может быть использовано для сложения двоичных кодов. Техническим результатом является повышение быстродействия. Устройство содержит в каждом разряде два RS-триггера, восемь элементов И, три элемента ИЛИ, три элемента НЕ. 2 н.п. ф-лы, 1 ил.

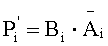

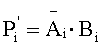

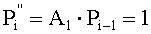

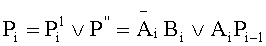

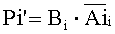

1. Способ сложения двоичных кодов, при котором первое слагаемое хранят в регистре А, второе слагаемое принимают в регистр В с информационных входов, отличающийся тем, что по первому временному такту t1 в каждом разряде одновременно выполняют элементарные операции приема второго слагаемого Bi, первое сложение по модулю два кода Ai с кодом, принимаемым в Bi, формирование потенциала поразрядного переноса, равного  , формирование потенциала сквозного переноса, равного Pi′′=Ai·Рi-1, по t1 также вырабатывается имитационный перенос Pi′′′ в каждом двоичном разряде за счет подачи высокого потенциала по t1 на ВУ 21 и на третий вход ИЛИ 11, что позволяет сформировать потенциал переноса в самом старшем разряде устройства и сохранять этот потенциал после окончания действия сигнала формирования P′′′ при наличии поразрядного потенциала переноса

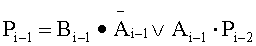

, формирование потенциала сквозного переноса, равного Pi′′=Ai·Рi-1, по t1 также вырабатывается имитационный перенос Pi′′′ в каждом двоичном разряде за счет подачи высокого потенциала по t1 на ВУ 21 и на третий вход ИЛИ 11, что позволяет сформировать потенциал переноса в самом старшем разряде устройства и сохранять этот потенциал после окончания действия сигнала формирования P′′′ при наличии поразрядного потенциала переноса  в первом, самом младшем разряде, и при наличии единичных значений потенциалов триггеров с второго до самого старшего разрядов регистра А, т.е. А2=А3=…Аn=1, эта особенность предлагаемого способа и устройства позволяет исключить последовательное формирование сквозных переносов Р′′ в каждом разряде и позволяет довести максимальное время задержки сигнала переноса, равное,Тmax=2nτ в известных устройствах, до Tmax=t1 в предлагаемом устройстве, по второму временному такту t2 выполняют второе сложение по модулю два кода Ai и сигнала переноса Рi-1, поступившего из младшего разряда, и равного

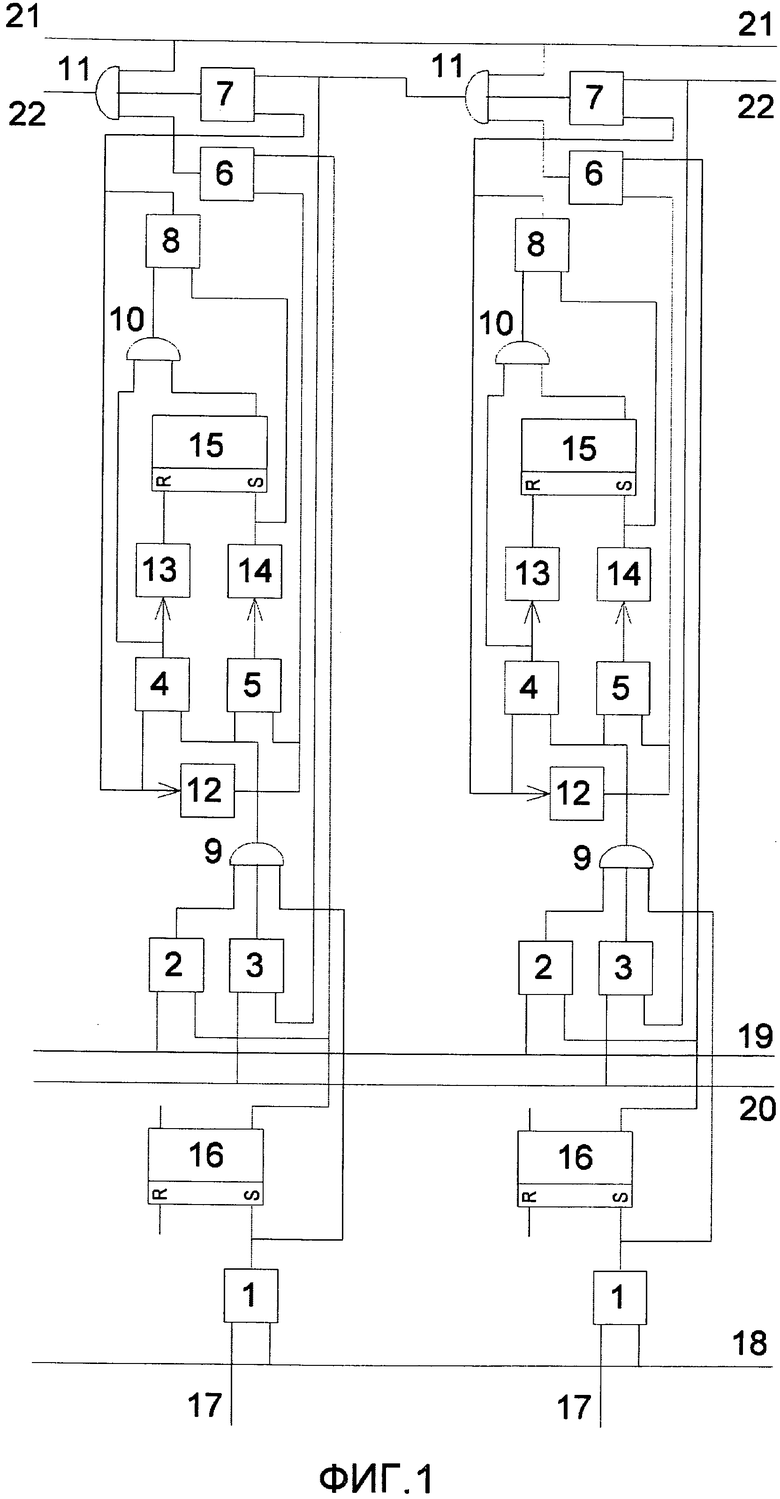

в первом, самом младшем разряде, и при наличии единичных значений потенциалов триггеров с второго до самого старшего разрядов регистра А, т.е. А2=А3=…Аn=1, эта особенность предлагаемого способа и устройства позволяет исключить последовательное формирование сквозных переносов Р′′ в каждом разряде и позволяет довести максимальное время задержки сигнала переноса, равное,Тmax=2nτ в известных устройствах, до Tmax=t1 в предлагаемом устройстве, по второму временному такту t2 выполняют второе сложение по модулю два кода Ai и сигнала переноса Рi-1, поступившего из младшего разряда, и равного  , на этом операцию сложения кодов A и B завершают, результат сложения хранят в регистре А.

, на этом операцию сложения кодов A и B завершают, результат сложения хранят в регистре А.

2. Устройство сложения двоичных кодов, содержащее первый и второй регистры A и B, каждый разряд устройства содержит первый и второй RS-триггеры, информационный вход, первый вход управления приемом второго слагаемого в регистр B, второй вход управления выполнением первого сложения по модулю два, третий вход управления выполнением второго сложения по модулю два, при этом упомянутые входы управления подключены к первым входам первого, второго и третьего элементов И, соответственно, выход первого элемента И соединен с единичным входом второго RS-триггера, выходы второго и третьего элементов И подключены к первому и второму входам первого элемента ИЛИ, выход которого подключен к первым входам четвертого и пятого элемента И, вторые входы первого - третьего элементов И соединены с информационным входом, единичным выходом второго триггера и входом переноса из младшего разряда Рi-1 соответственно, вторые входы шестого и седьмого элементов И подключены к единичному выходу второго RS-триггера и к входу переноса из младшего разряда соответственно, отличающееся тем, что выход первого элемента И соединен с третьим входом первого элемента ИЛИ, вторые входы четвертого и пятого элементов И соединены с входом и выходом первого элемента НЕ, выходы упомянутых элементов И через второй и третий элементы НЕ соединены с нулевым и единичным входами первого RS-триггера, выход четвертого элемента И соединен с первым входом второго элемента ИЛИ, второй вход которого подключен к единичному выходу первого RS-триггера, выход второго элемента ИЛИ соединен с первым входом восьмого элемента И, второй вход которого подключен к выходу третьего элемента НЕ, выход восьмого элемента И связан с входом первого элемента НЕ и с первым входом седьмого элемента И, выход первого элемента НЕ подключен к первому входу шестого элемента И, выходы шестого и седьмого элементов И подключены к первому и второму входам третьего элемента ИЛИ, в каждый разряд устройства введен четвертый вход управления формированием имитационного переноса, подключенный к третьему входу третьего элемента ИЛИ, выход которого является сигналом переноса в старший разряд.

| СПОСОБ И УСТРОЙСТВО СЛОЖЕНИЯ ДВОИЧНЫХ КОДОВ | 2008 |

|

RU2388041C2 |

| УСТРОЙСТВО СУММИРОВАНИЯ ДВОИЧНЫХ КОДОВ | 2008 |

|

RU2381547C2 |

| RU 23308073 C2 , 10.10.2007 | |||

| US 2002091744 A1 11.07.2002 | |||

| JP 6149542 A, 27.05.1994 | |||

| US 4931981 A, 05.06.1990 | |||

Авторы

Даты

2014-12-27—Публикация

2013-03-29—Подача