Изобретение относится к области цифровой вычислительной техники и может быть использовано в процессорных устройствах ЭВМ и в устройствах цифровой автоматики. Известны способы и устройства выполнения арифметических и логических операций, заключающиеся в последовательном выполнении элементарных операций (ЭО) приема слагаемых, формирования в каждом разряде результата выполнения операций и занесения полученного результата в триггеры регистра результата или в триггеры одного из регистров слагаемых, при этом устройство, реализующее способ, выполнено на основе логических элементов И, ИЛИ, НЕ и содержит в каждом разряде три RS-триггера, сумматор комбинационного типа на три входа и логические элементы для выполнения вспомогательных операций. Различные варианты построения таких объектов устройств рассмотрены в книге А.Г. Шигина «Цифровые вычислительные машины», М., Энергия, 1971 г., страница 217, рисунок 9-26 и в книге М.А.Карцева «Арифметика цифровых машин» издательство «Наука», 1969 г., страница 139-190. Недостатком известных объектов является наличие трех RS-триггеров в каждом разряде, что определяет время выполнения операций сложения, объем оборудования и стоимость устройства в целом. Кроме того, общим недостатком известных способов и устройств является построение отдельных логических схем для выполнения операций логического сложения, логического умножения, сдвига кода влево и вправо, что также увеличивает аппаратурные затраты, потребления электропитания и стоимость устройства.

Наиболее близкими принятыми за прототип, являются сумматор (далее - объект) по а.с. 538365. Он устраняет некоторые недостатки известных объектов, т.к. содержит в каждом разряде только два RS-триггера, но не позволяет совмещать во времени выполнение операций сложения и сдвига частичных произведений.

Целью изобретения является повышение быстродействия работы объекта, расширение перечня выполняемых арифметических и логических операций. Для чего предложены способ, заключающийся в последовательном выполнении элементарных операций приема второго слагаемого во второй регистр, при этом первое слагаемое хранится в первом регистре как результат выполнения предыдущей операции, выдачи кодов первого и второго регистра на входы суммирующих схем каждого разряда, формирование результата суммирования слагаемых с учетом переноса из младшего разряда и занесение суммы в первый регистр, отличающийся тем, что при выполнении операций сложения по первому временному такту выполняют прием кода второго слагаемого во второй регистр и сдвиг кода первого слагаемого, хранящегося в первом регистре на один разряд влево, по второму такту выдают коды слагаемых на входы суммирующих схем и формируют сигналы переносов и сумм в каждом разряде, по третьему такту одновременно выполняют занесение суммы в триггеры первого слагаемого со сдвигом на один разряд вправо и выдачу суммы на информационные выходы; при выполнении операции сложения по модулю два выполняют в той же последовательности те же элементарные операции, что при выполнении операции сложения, но запрещают распространение сквозного переноса во всех разрядах; при выполнении операции логического сложения выполняют операцию сложения, но запрещают формирование поразрядного переноса во всех разрядах; при выполнении операции логического умножения выполняют операцию сложения, при этом формируют потенциал сквозного переноса во всех разрядах по времени второго и третьего временных тактов; при выполнении операции инвертирования кода первого слагаемого по первому временному такту сдвигают код влево на один разряд, по второму такту выдают код первого слагаемого на входы суммирующих схем, формируют вход сквозного переноса и запрещают выход этого переноса в каждом разряде, по третьему такту заносят сформированную сумму в триггеры первого слагаемого со сдвигом на один разряд вправо и выдают ее на информационные выходы; при выполнении отдельной операции сдвига кода влево подключают выходы триггеров i-2-го разряда к входам суммирующих схем i-того разряда на время всей операции и по времени каждого импульса сдвига заносят результат суммирования i-того разряда в триггеры i-1-го разряда первого слагаемого и выдают этот код на информационные выходы; при выполнении отдельной операции сдвига кода вправо подключают выходы триггеров первого слагаемого к входам суммирующих схем на время выполнения всей операции сдвига и по времени каждого импульса сдвига заносят результат суммирования i-того разряда в триггеры первого слагаемого со сдвигом на один разряд вправо и выдают этот код на информационные выходы; при выполнении отдельной операции выдачи результата операции на информационные выходы подключают последовательно или в определенной комбинации к входам суммирующих схем выходы триггеров слагаемых или входы управления выполнением элементарных операций и подают исполнительный импульс на входы элементов выдачи кода, и устройство выполнения арифметических и логических операций, содержащее в каждом разряде первый и второй RS-триггеры, первый, второй, третий, четвертый, пятый, шестой и седьмой элементы И, первый, второй, третий и четвертый элементы ИЛИ, первый и второй элементы НЕ, вход управления выдачей кода из второго регистра и вход управления приемом кода в первый регистр и информационный вход, и выход, при этом информационный вход подключен к S-входу второго триггера, единичный выход второго триггера соединен с первым входом первого элемента И, второй его вход соединен с входом управления выдачей кода из второго регистра, выход этого элемента И соединен с первыми входами первого элемента ИЛИ и второго элемента И, выход второго элемента И подключен к первым входам второго элемента ИЛИ и четвертого элемента И, второй вход четвертого элемента И связан с вторым входом второго элемента ИЛИ и с входом переноса из младшего разряда, выход первого элемента ИЛИ соединен с вторыми входами третьего элемента И и четвертого элемента ИЛИ, выход третьего элемента И является входом переноса в старший разряд, выход четвертого элемента И подключен к первому входу третьего элемента ИЛИ, выход первого элемента НЕ соединен с вторым входом третьего элемента ИЛИ, выходы третьего и четвертого элемента ИЛИ связаны с первым и вторым входами пятого элемента И, выход которого соединен с первым входом седьмого элемента И и входом второго элемента НЕ, выход этого элемента НЕ подключен к первому входу шестого элемента И, вторые входы шестого и седьмого элементов И связаны с входом управления приемом кода в первый регистр, отличающееся тем, что в каждый разряд устройства введены восьмой, девятый, десятый и одиннадцатый элементы И, третий элемент НЕ, вход управления выдачей результата операции на информационный выход, вход управления сдвигом кода влево, входы управления сквозным переносом, вход управление поразрядным переносом, входы управления формированием сквозного переноса, вход управления выдачей кода из первого регистра, единичный выход первого триггера соединен с первым входом одиннадцатого элемента И, второй его вход связан с входом управления выдачей кода из первого триггера, а выход упомянутого элемента И соединен с вторыми входами первого элемента ИЛИ и второго элемента И, выходы первого и второго элементов ИЛИ соединены с первым и вторым входами десятого элемента И, его выход через первый элемент НЕ связан с вторым входом третьего элемента ИЛИ, выход второго элемента ИЛИ соединен с первым входом четвертого элемента ИЛИ, первый вход девятого элемента И i+1-го разряда соединен с единичным выходом первого триггера i-1-го разряда, второй вход упомянутого элемента И связан с входом управления сдвигом кода влево, а его выход соединен с четвертым входом четвертого элемента ИЛИ, первый вход восьмого элемента И подключены к выходу пятого элемента И, второй вход связан с входом управления выдачей результата операции на информационный выход, а выход восьмого элемента И является информационным выходом i-того разряда, выход шестого элемента И через третий элемент НЕ соединен с третьим входом пятого элемента И, выход шестого элемента И i-того разряда соединен с R-входом первого триггера i-1-го разряда, выход седьмого элемента И соединен с третьими входами третьего и четвертого элементов ИЛИ i-того разряда и с S-входом первого триггера i-1-го разряда, кроме того, вход управления сквозным переносом соединен с третьим входом третьего элемента И, вход управления поразрядным переносом подключен к третьему входу второго элемента И, входы управления формированием сквозного переноса связаны с третьими входами первого и второго элементов ИЛИ, а вход управления выдачей кода из первого регистра подключен к второму входу одиннадцатого элемента И.

Предлагаемый объект позволяет повысить быстродействие выполнения операции сложения и выдачи результата на информационный выход за счет совмещения времени выполнения, повысить быстродействие операции умножения за счет совмещения во времени операций сложения и сдвига кода, обеспечивает широкий перечень выполнения арифметических и логических операций (сложение кода со сдвигом вправо, сдвиг кода первого слагаемого вправо и влево на один разряд за каждый такт сдвига, инвертирование кода первого регистра, сложение по модулю два, логическое сложение, логическое умножение, выдачу кода первого или второго регистра на информационный выход, выдачу результата выполняемой операции на информационный выход и ряд других вспомогательных операций).

Отметим основные отличительные признаки объекта и покажем что позволяет получить каждый из этих признаков.

1. Совмещение во времени выполнения элементарных операций (ЭО) приема кода второго слагаемого (сомножителя), сдвига кода первого слагаемого влево и выдачи результата сложения на информационный выход обеспечивает сокращение времени выполняемых операций.

2. Вход управления сквозным переносом во всех разрядах объекта позволяет обеспечить выполнение ЭО логического сложения и сложения по модулю два.

3. Формирование сигнала переноса во всех разрядах объекта позволяет выполнить ЭО инвертирования кода первого слагаемого и логического умножения.

4. Введение десятого элемента И с соответствующими связями обеспечивает выполнение ЭО сложения по модулю два.

5. Девятый элементы И с соответствующими связями обеспечивают выполнение сдвига кода влево, а связи с выходов шестого и седьмого элементов И i-того разряда с R и S входами i-1-го разряда обеспечивают сдвиг кода вправо.

6. Восьмой элемент И обеспечивает выдачу результата операции на информационный выход.

7. Наличие связей с выхода шестого элемента И через третий элемент НЕ с выходом пятого элемента И и с выхода седьмого элемента И с входами третьего и четвертого элемента ИЛИ позволяют исключить из состава оборудования каждого разряда один RS-триггер.

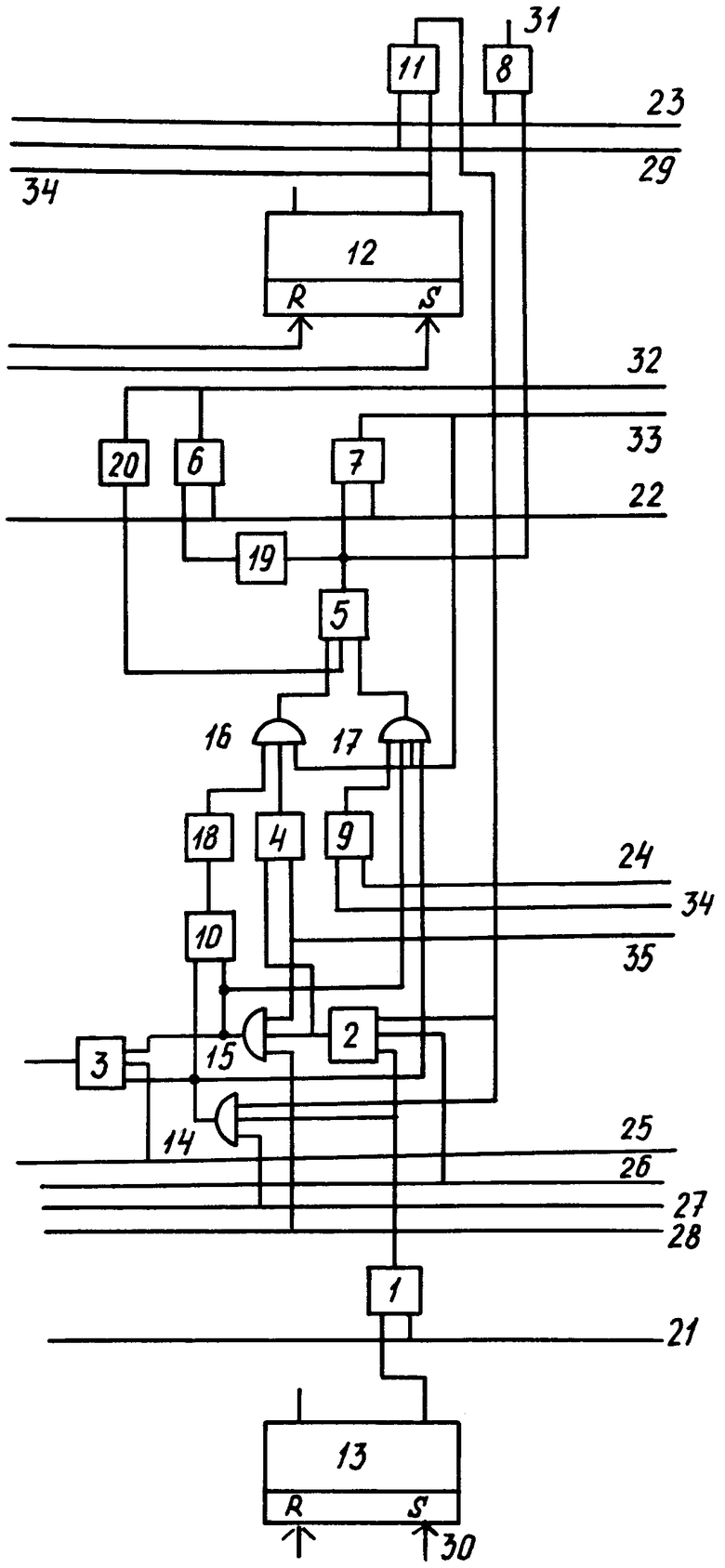

Для пояснения принципа работы объекта на чертеже приведена функциональная схема одного двоичного разряда. Каждый разряд содержит логические элементы И 1-11, RS-триггеры 12, 13, элементы ИЛИ 14-17, элементы НЕ 18-20, вход управления выдачей кода из второго регистра 21, вход управления (ВУ) приемом кода в первый регистр 22, ВУ выдачей результата операции на информационной выход 23, ВУ сдвигом кода влево 24, ВУ сквозным переносом 25, ВУ поразрядным переносом 26, ВУ формированием сквозного переноса 27 и 28, ВУ выдачей кода из первого регистра 29, информационной вход 30, информационной выход 31, R-вход триггера 12-32, S-вход триггера 12-33, единичный выход триггера 12 i-2-го разряда 34, вход переноса из младшего разряда 35, выход переноса из i-того разряда 36.

Рассмотрим работу объекта при выполнении арифметических и логических операции. В исходном состоянии (в статике) триггеры 12 и 13 установлены в нуль, на всех входах управления 21-25, 27-29, на R и S-входах триггеров, на входах и выходах переносов отсутствуют высокие потенциалы, а на ВУ 26 присутствует высокий потенциал. С выходов элементов НЕ 18-20 на входы ИЛИ 16, И6, И5 поступают высокие потенциалы.

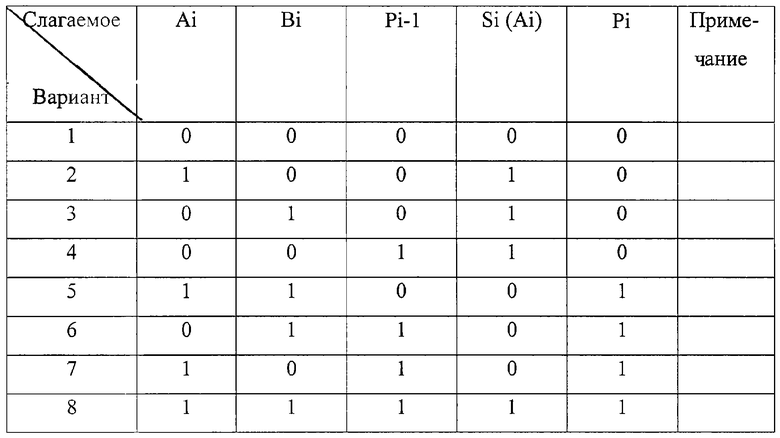

1. Операция сложения. Операция сложения выполняется за три временных такта (t1, t2, t3). По t1 одновременно выполняются ЭО приема второго слагаемого в триггеры 13 и сдвиг кода влево первого слагаемого, хранящегося в триггерах 12. Для выполнения этих ЭО на вход 30 поступает импульс, соответствующий коду единице i-того разряда, а на ВУ 24 подается высокий потенциал, разрешающий сдвиг кода влево. Если в триггере 12 i-1-го разряда хранится код единицы, то высокий потенциал с выхода И9 i+1-го разряда по цепи элементов ИЛИ17, И5 поступит на вход И7. Исполнительный импульс по цепи ВУ 22, И7 поступит на S-вход триггера 12 i-го разряда и установит его в единицу. Одновременно через ИЛИ 16, 17 этот же импульс поступает на входы И5 и поддерживает на его выходе высокий потенциал. По t2 формируются потенциалы сквозного переноса и результат суммирования кодов двух слагаемых. Для этого на ВУ 21, 29 и 25 подаются высокие потенциалы, разрешающие работу ИЗ и выдачу значений кодов триггеров 12, 13 на входы суммирующих схем. Как известно, для полных сумматоров, суммирующих первое слагаемое (Ai), второе слагаемое (Bi) и перенос из младшего разряда (Pi-1) может быть восемь комбинаций из трех слагаемых (см. Табл.1). Для выполнения 2, 3 и 4 вариантов высокий потенциал, соответствующий коду 1, приходит по цепям элементов И11, ИЛИ14, ИЛИ17, И5, (2 вар.), И1, ИЛИ14, 17, И5 (3 вар.) и по цепи вход 35, ИЛИ15, 17, И5. (4 вар.)

По t3 выполняется ЭО занесения суммы в триггеры 12 с одновременным сдвигом этого кода на один разряд вправо. Так как на выходах НЕ 18, 20 присутствуют высокие потенциалы, то с выхода И5 i-того разряда, после прихода исполнительного импульса по цепи ВУ 22, И7, на S-вход триггера 12 i-1-го разряда поступит импульс, который установит упомянутый триггер в единицу. При выполнении вариантов суммирования 5, 6 и 7 высокие потенциалы с выходов И1, 11 по цепи И2, ИЛИ 15 и через ИЛИ 14 поступят на входы И3, И10, тем самым будет сформирован перенос в старший разряд и запрещена работа И5, т.к. с выхода НЕ18 через ИЛИ 16 на вход И5 не будет поступать высокий потенциал. По t3 исполнительный импульс по цепи ВУ 22, И6 i-того разряда поступит на R-вход триггера 12 i-1-го разряда и установит его в нуль. При этом исполнительный импульс в i-том разряде с выхода И6, через НЕ 20 запретит прохождение управляющих сигналов через И5, т.е. сохранится условие прохождения исполнительного импульса ВУ22 только через И6, независимо от переключения триггеров 12 i-того и i-1-го разрядов и изменения управляющих потенциалов на первом и втором входах И5. При выполнении восьмого варианта значений Ai, Bi и Pi-1 высокие потенциалы с единичных выходов триггеров 12, 13 и с входа 35 по t2 сформируют на выходах И3, 5 рассматриваемого разряда высокие потенциалы, соответствующие коду единицы, т.к. высокие потенциалы с выходов И2, ИЛИ14 поступят на входы И3, 4. При этом выход И3 выработает потенциал переноса в старший разряд, а выходы И4, ИЛИ 14, 15 через ИЛИ16, 17 поступят на входы И5 и сформируют на его выходе высокий потенциал. По t3 исполнительный импульс по цепи ВУ 22, И7 поступит на входы ИЛИ16, 17 i-того разряда и по входу 33 на S-вход триггера 12 i-1-го разряда. На время длительности импульса, поступающего по ВУ 22 на второй вход И7, условия управления первым входом этого элемента не будут меняться, т.к. сигнал с выхода И7 через ИЛИ16, 17 поступит на первый и второй входы И5 и далее через НЕ 19 на первый вход И6 с выхода И5 сигнал поступит на выход И8. Одновременно по t3 может быть выполнена операция выдачи суммы на информационный выход через И8. Для этого на ВУ 23 подается исполнительный импульс. Таким образом, в ходе выполнения операции сложения одновременно выполняются операции сдвига кода вправо и выдача кода из объекта, что позволяет повысить быстродействие работы объекта. Известны устройства, в которых совмещаются ЭО занесение кода суммы в триггер и сдвиг этого кода на один разряд вправо, но для выполнения этих операций требуется три временных такта (формирование переносов, суммы, занесение суммы во второй регистр и занесение суммы в третий регистр) и три RS-триггера в каждом разряде. В предлагаемом устройстве для выполнения операции сложения и сдвига суммы требуется два временных такта и два RS- триггера. Следовательно, имеет место повышения быстродействия операции умножения на 30% и снижения аппаратурных затрат.

2. Операция сдвига кода вправо. Эта операция выполняется как в составе операций сложения, так и самостоятельно. Для ее выполнения требуется два временных такта (t1 и t2) при сдвиге на один двоичный разряд. При этом на ВУ 29 на время выполнения всей операции подается высокий потенциал. Код второго слагаемого на схемы суммирования не выдается, а потенциалы переноса не вырабатываются, т.е. Bi=0, Pi=0. Если в триггере 12 i-того разряда хранится код единицы, то высокий потенциал по цепи И 11, ИЛИ 14, 17 поступает на вход И5. На другие входы этого элемента с выходов НЕ 18, 20 также поступают высокие потенциалы. С выхода И5 на вход И7 поступит высокий потенциал. По первому такту исполнительный импульс с ВУ 22 через И7 i-того разряда поступит на S-вход триггера 12 i-1-го разряда и установит его в единицу. Одновременно этот же импульс с выхода И7 через ИЛИ 16, 17 поступит на первый и второй входы И5 и будет разрешать прохождение импульса на S-вход младшего разряда независимо от переключения триггеров 12. Второй такт (пауза между импульсами) используется для подготовки логических элементов к очередному сдвигу кода еще на один разряд вправо. После выполнения заданного числа сдвигов поступление импульсов на ВУ22 прекращается, с ВУ 29 снимается высокий потенциал. Операция закончена. Заметим, что при необходимости сдвигаемый код может выдаваться на информационный выход 31. Для выполнения ЭО сдвига вправо не требуется дополнительного оборудования.

3. Операция сдвига кода влево. Операция выполняется как в составе практически всех арифметических и логических операций, так и самостоятельно при выполнении операций нормализации кода или умножения его на 2, 4, 8 и т.д. Сдвиг кода на один разряд влево выполняется за два временных такта t1 и t2. Принцип работы объекта рассмотрен при описании выполнения операции сложения.

4. Операция инвертирования. Выполняется за два временных такта t1 и t2. Будем считать, что сдвиг кода влево на один разряд выполняется на подготовительном этапе. Для выполнения инвертирования на ВУ 28, 29 подаются высокие потенциалы. Если триггер 12 хранит код единицы, то высокий потенциал по цепи И11, ИЛИ14 поступит на первый вход И10, на второй вход этого элемента поступит высокий потенциал с ВУ 28. Высокий потенциал с И10 поступит на вход НЕ 18 и через ИЛИ 16 запретит работу И5. На первом входе И7 будет низкий потенциал, а на входе НЕ 19 и входе И6 - высокий. Исполнительный импульс, поступивший на входы И6, 7 с ВУ 22 через И6, HЕ20 запретит работу И5 на время длительности этого импульса. Одновременно импульс с выхода И6 i-того разряда поступит на R-вход триггера i- 1-го разряда и установит его в нуль. Таким образом будет выполнено инвертирование кода и сдвига его на один разряд вправо (При выполнении последующих операций сдвиг кода влево на один разряд будет выполнен на этапе подготовки этой операции). Операция инвертирования кода потребует дополнительно только одного входа логического элемента ИЛИ.

5. Операция сложения по модулю два. Выполняется за счет последовательного выполняется ЭО приема второго слагаемого, сдвига первого слагаемого влево (t1), сложения по модулю два и сдвига результата сложения вправо на один разряд (t3). (первые два ЭО рассмотрены в п.1). Для выполнения сложения по модулю два на ВУ 21, 29 подаются высокие потенциалы. Если триггеры 12, 13 хранят код единицы, то высокий потенциал с выхода И10 через НЕ 18 запретит работу И5. Исполнительный импульс по цепи ВУ 22, И6 подтвердит запрет работы И5 в i-том разряде и поступит на R-вход триггера 12 i-1-го разряда, т.е. будет выполнено инвертирование и сдвиг кода вправо. При значении кода одного из слагаемых равным единице, выполнение операции сводится к выполнению пп.2, 3 табл.1, рассмотренных при описании операции сложения (п.1). Для выполнения этой операции требуется дополнительное оборудование - один элемент И на два входа.

6. Операция логического сложения. Для ее выполнения на ВУ 21, 29 подаются высокие потенциалы, а с ВУ 26 снимается высокий потенциал. Потенциалы с единичных триггеров 12, 13 по цепи И1, 11, ИЛИ 14, 17, И5 поступают на вход И7. Исполнительный импульс, поступивший по ВУ 22, проходит на входы ИЛИ16, 17 и сохраняет условия разрешения работы И7. Этот же импульс поступает на S-вход триггера 12 младшего разряда. Для выполнения операции логического сложения требуется дополнительно только один вход элемента И. (ЭО приема, выдачи и сдвига кодов рассмотрены в п.1)

7. Операция логического умножения. Для ее выполнения на ВУ 21, 25, 27, 28, и 29 подаются высокие потенциалы. В тех разрядах, в которых Ai=Bi=1, с выхода И2 на первый вход И4 поступит высокий потенциал. На второй вход И4 также приходит высокий потенциал переноса, сформированной во всех младших разрядах. Высокие потенциалы с выходов И4, ИЛИ 14 через ИЛИ 16, 17 поступят па первый и второй входы И5 и сформируют на его выходе высокий потенциал, разрешающий прохождение исполнительного импульса с ВУ 22 через И7 на входы ИЛИ 16, 17 i-того разряда и на S-вход i-1-го разряда.

Триггер 12 i-1-го разряда будет установлен в единицу. При всех остальных значениях Ai и Bi на выходе И5 будет низкий потенциал, а на выходе НЕ19 высокий. Исполнительный импульс по цепи ВУ22, И6, НЕ20 запретит работу И5 на время длительности этого импульса и поступит на R-вход триггера 12 i-1-го разряда. Таким образом, в триггеры 12 i-i-го разряда будет занесен результат логического умножения кодов сомножителей, ранее хранившихся в триггерах 12, 13 i-того разряда. Для реализации этой операции требуется дополнительно только один вход элемента ИЛИ. (ЭО приема, выдачи и сдвига кодов рассмотрены в п.1)

8. Операция выдачи результата на информационный выход. Эта операция имеет ряд модификаций: выдача кода результата операции в ходе ее выполнения по t3, т.е. еще до завершения выполнения операции, выдача кода триггеров 12 или 13, выдача кода триггеров 12 на информационный выход с одновременным сдвигом на два разряда влево, выдача результата любой операции с сохранением значения первого слагаемого (заметим, что при выполнении такой модификации выдачи сдвиг кода вправо не производится). Все эти модификации выдачи кода существенно расширяют функциональные возможности объекта, повышают быстродействие выполнения ряда вычислительных алгоритмов, требуя для их выполнения дополнительно только одного элемента И на два входа, эти операции выполняются за счет комбинаций включения или выключения ВУ 21, 22, 23, 24, 29.

Таким образом, предложенные способ и устройство для выполнения арифметических и логических операций обеспечивают упрощение объекта за счет исключения одного RS-триггера в каждом разряде, повышают быстродействие выполнения операций сложения (умножения) с трех до двух тактов, т.е. на 30% расширяют функциональную гибкость объекта за счет новых вариантов выполнения ЭО выдачи и сдвига кода. Указанные преимущества обеспечиваются при минимальных затратах оборудования. Так в прототипе для выполнения того же перечня операций требуется около 67 входов логических элементов. В предложенном объекте требуется всего 59 входов, т.е. приблизительно на 12% меньше.

| название | год | авторы | номер документа |

|---|---|---|---|

| СПОСОБЫ ВЫПОЛНЕНИЯ ЭЛЕМЕНТАРНЫХ ВЫЧИСЛИТЕЛЬНЫХ ОПЕРАЦИЙ (ЭВО) И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2012 |

|

RU2505850C2 |

| СПОСОБ И УСТРОЙСТВО ВЫПОЛНЕНИЯ ВЫЧИСЛИТЕЛЬНЫХ ОПЕРАЦИЙ ПРИ МИНИМАЛЬНЫХ ЗАТРАТАХ ОБОРУДОВАНИЯ | 2005 |

|

RU2287849C1 |

| СПОСОБ И УСТРОЙСТВО СУММИРОВАНИЯ | 2005 |

|

RU2308073C2 |

| НАКАПЛИВАЮЩИЙ СУММАТОР | 2005 |

|

RU2288501C1 |

| СПОСОБЫ ВЫПОЛНЕНИЯ ЭЛЕМЕНТАРНЫХ ВЫЧИСЛИТЕЛЬНЫХ ОПЕРАЦИЙ (ЭВО) И УСТРОЙСТВО ИХ ОСУЩЕСТВЛЕНИЯ | 2013 |

|

RU2553221C2 |

| СПОСОБ И УСТРОЙСТВО УМНОЖЕНИЯ ДВОИЧНО-ДЕСЯТИЧНЫХ КОДОВ | 2009 |

|

RU2410745C1 |

| СУММАТОР КОМБИНАЦИОННОГО ТИПА | 2004 |

|

RU2275676C1 |

| СПОСОБ И УСТРОЙСТВО СЛОЖЕНИЯ ДВОИЧНЫХ КОДОВ | 2013 |

|

RU2537046C2 |

| СУММАТОР НАКАПЛИВАЮЩЕГО ТИПА | 2003 |

|

RU2269153C2 |

| СПОСОБ И УСТРОЙСТВО СУММИРОВАНИЯ ДВОИЧНО-ДЕСЯТИЧНЫХ ЧИСЕЛ | 2007 |

|

RU2402803C2 |

Изобретение относится к области вычислительной техники и может быть использовано в процессорах ЭВМ и в устройствах цифровой автоматики. Техническим результатом является повышение быстродействия выполнения операций, расширений перечня выполняемых операций при минимальных затратах оборудования. Указанный результат достигается за счет того, что устройство в каждом разряде содержит логические элементы И (1-11), два RS-триггера (12, 13), логические элементы ИЛИ (14-17), логические элементы НЕ (18-20), девять входов управления, информационный вход и выход. 2 н.п. ф-лы, 1 ил., 1 табл.

| Двухтактный п-разрядный сумматор накапливающего типа | 1974 |

|

SU538365A1 |

| Микропроцессорный модуль | 1979 |

|

SU894714A1 |

| ЛОГИЧЕСКИЙ БЛОК АРИФМЕТИЧЕСКОГО УСТРОЙСТВА | 0 |

|

SU241108A1 |

| JP 8097709 A, 12.04.1996. | |||

Авторы

Даты

2007-03-20—Публикация

2005-05-17—Подача