Изобретение относится к вычислительной технике и может быть использовано для построения средств автоматики, функциональных узлов систем управления и др.

Известны параллельные счетчики единичных сигналов (см., например, патент РФ 2256211, кл. G06F 7/38, 2005 г.), которые содержат логические элементы и формируют двоичный код числа единичных сигналов входного кортежа (x1, …, x8), где xq∈{0,1}.

К причине, препятствующей достижению указанного ниже технического результата при использовании известных параллельных счетчиков единичных сигналов, относятся большие аппаратурные затраты и низкое быстродействие, обусловленные соответственно тем, что, в частности, упомянутый аналог содержит двадцать два элемента И, двадцать два элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, и максимальное время задержки распространения сигнала в нем равно 10τЛЭ, где τЛЭ есть время задержки логического элемента.

Наиболее близким устройством того же назначения к заявленному изобретению по совокупности признаков является принятый за прототип параллельный счетчик единичных сигналов (патент РФ 2260204, кл. G06F5/00, 2005 г.), который содержит логические элементы и формирует двоичный код числа единичных сигналов входного кортежа (x1, …, x8), где xq∈{0,1}.

К причине, препятствующей достижению указанного ниже технического результата при использовании прототипа, относятся большие аппаратурные затраты и низкое быстродействие, обусловленные соответственно тем, что прототип содержит тринадцать элементов И, семнадцать элементов ИСКЛЮЧАЮЩЕЕ ИЛИ и максимальное время задержки распространения сигнала в нем равно 9τЛЭ, где τЛЭ есть время задержки логического элемента.

Техническим результатом изобретения является уменьшение аппаратурных затрат и повышение быстродействия при сохранении функциональных возможностей прототипа.

Указанный технический результат при осуществлении изобретения достигается тем, что в параллельном счетчике единичных сигналов, содержащем шестнадцать элементов ИСКЛЮЧАЮЩЕЕ ИЛИ и двенадцать элементов И, первый и второй входы r-го (r∈{1, …, 7, 9, …, 12}) элемента ИСКЛЮЧАЮЩЕЕ ИЛИ соединены соответственно с первым и вторым входами r-го элемента И, а первые входы четвертого, шестого и выход двенадцатого элементов И подключены соответственно к пятому, седьмому входам параллельного счетчика единичных сигналов и первому входу шестнадцатого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, особенность заключается в том, что первый и второй входы восьмого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ соединены соответственно с первым и вторым входами восьмого элемента И, первый, второй входы i-го  и первый, второй входы j-го

и первый, второй входы j-го  элементов И подключены соответственно к выходам (i+2)-го, (i+4)-го элементов ИСКЛЮЧАЮЩЕЕ ИЛИ и выходам (j-4)-го, (j-2)-го элементов И, выходы i-го, j-го элементов ИСКЛЮЧАЮЩЕЕ ИЛИ и выходы i-го, j-го элементов И соединены соответственно с i-ым входом девятого, вторым входом (j+7)-го и первым входом (i+13)-го, (j-6)-м входом одиннадцатого элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, выходы (i+13)-го, (i+9)-го, тринадцатого элементов ИСКЛЮЧАЮЩЕЕ ИЛИ и выход (i+8)-го элемента И подключены соответственно к i-му входу десятого, вторым входам (i+11)-го, шестнадцатого и первому входу (i+11)-го элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, а выходы девятого, двенадцатого, шестнадцатого элементов ИСКЛЮЧАЮЩЕЕ ИЛИ и выход одиннадцатого элемента И являются соответственно первым, вторым, третьим и четвертым выходами параллельного счетчика единичных сигналов, первый, третий и второй, четвертый, шестой, восьмой входы которого соединены соответственно с первыми входами третьего, пятого и вторыми входами третьего, пятого, четвертого, шестого элементов И.

элементов И подключены соответственно к выходам (i+2)-го, (i+4)-го элементов ИСКЛЮЧАЮЩЕЕ ИЛИ и выходам (j-4)-го, (j-2)-го элементов И, выходы i-го, j-го элементов ИСКЛЮЧАЮЩЕЕ ИЛИ и выходы i-го, j-го элементов И соединены соответственно с i-ым входом девятого, вторым входом (j+7)-го и первым входом (i+13)-го, (j-6)-м входом одиннадцатого элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, выходы (i+13)-го, (i+9)-го, тринадцатого элементов ИСКЛЮЧАЮЩЕЕ ИЛИ и выход (i+8)-го элемента И подключены соответственно к i-му входу десятого, вторым входам (i+11)-го, шестнадцатого и первому входу (i+11)-го элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, а выходы девятого, двенадцатого, шестнадцатого элементов ИСКЛЮЧАЮЩЕЕ ИЛИ и выход одиннадцатого элемента И являются соответственно первым, вторым, третьим и четвертым выходами параллельного счетчика единичных сигналов, первый, третий и второй, четвертый, шестой, восьмой входы которого соединены соответственно с первыми входами третьего, пятого и вторыми входами третьего, пятого, четвертого, шестого элементов И.

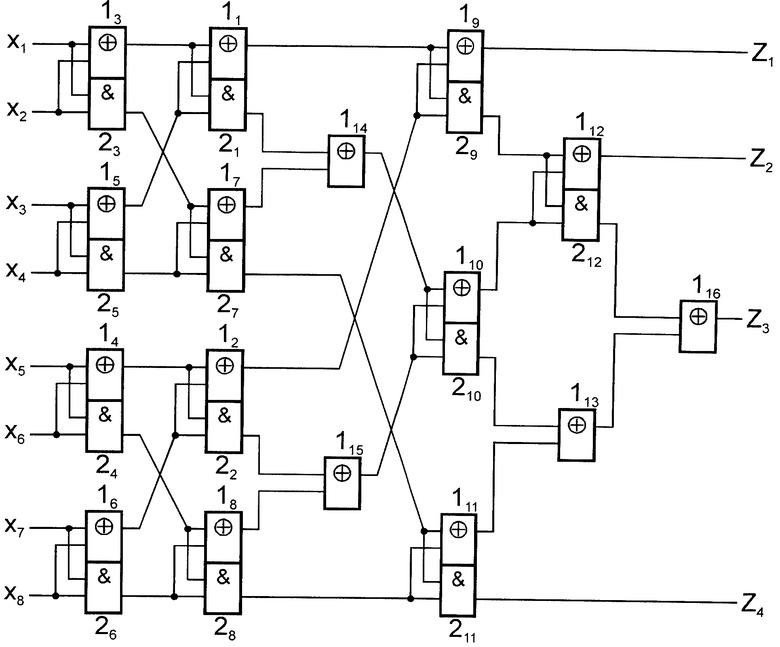

На чертеже представлена схема предлагаемого параллельного счетчика единичных сигналов.

Параллельный счетчик единичных сигналов содержит элементы ИСКЛЮЧАЮЩЕЕ ИЛИ 11, …, 116 и элементы И 21, …., 212, причем первый и второй входы элемента 1r

соединены соответственно с первым и вторым входами элемента 2r, первый, второй входы элемента 2i

соединены соответственно с первым и вторым входами элемента 2r, первый, второй входы элемента 2i  и первый, второй входы элемента 2j

и первый, второй входы элемента 2j  подключены соответственно к выходам элементов 1i+2, 1i+4 и 2j-4, 2j-2, выходы элементов 1i, 1j и 2i, 2j соединены соответственно с i-м входом элемента 19, вторым входом элемента 1j+7 и первым входом элемента 1i+13, (j-6)- м входом элемента 111, выходы элементов 1i+13, 1i+9, 113 и 2i+8, 212 подключены соответственно к i-му входу элемента 110, вторым входам элементов 1i+11, 116 и первым входам элементов 1i+11, 116, а выходы элементов 19, l12, 116 и 211 являются соответственно первым, вторым, третьим и четвертым выходами параллельного счетчика единичных сигналов, первый, третий, пятый, седьмой и второй, четвертый, шестой, восьмой входы которого соединены соответственно с первыми входами элементов 13, 15, 14, 16 и вторыми входами элементов 23, 25, 24, 26.

подключены соответственно к выходам элементов 1i+2, 1i+4 и 2j-4, 2j-2, выходы элементов 1i, 1j и 2i, 2j соединены соответственно с i-м входом элемента 19, вторым входом элемента 1j+7 и первым входом элемента 1i+13, (j-6)- м входом элемента 111, выходы элементов 1i+13, 1i+9, 113 и 2i+8, 212 подключены соответственно к i-му входу элемента 110, вторым входам элементов 1i+11, 116 и первым входам элементов 1i+11, 116, а выходы элементов 19, l12, 116 и 211 являются соответственно первым, вторым, третьим и четвертым выходами параллельного счетчика единичных сигналов, первый, третий, пятый, седьмой и второй, четвертый, шестой, восьмой входы которого соединены соответственно с первыми входами элементов 13, 15, 14, 16 и вторыми входами элементов 23, 25, 24, 26.

Работа предлагаемого параллельного счетчика единичных сигналов осуществляется следующим образом. На его первый, …, восьмой входы подаются соответственно подлежащие обработке сигналы x1, …, x8∈{0,1}. Тогда сигналы Z1, …, Z4 (см. чертеж) будут определяться выражениями

Z1=х1⊕x2⊕х3⊕х4⊕х5⊕х6⊕x7⊕x8,

Z2=(x1⊕x2⊕x3⊕х4)(х5⊕x6⊕х7⊕х8)⊕x1x2⊕x1x3⊕x1x4⊕x2x3⊕х2х4⊕х3х4⊕х5х6⊕x5x7⊕х5х8⊕х6х7⊕x6x8⊕x7x8,

Z3=(x1⊕x2⊕х3⊕x4)(x5⊕x6⊕x7⊕x8)(x1x2⊕x1x3⊕x1x4⊕х2х3⊕x2x4⊕x3x4⊕x5x6⊕x5x7⊕x5x8⊕x6x7⊕x6x8⊕x7x8)⊕(x1x2⊕x1x3⊕x1x4⊕x2x3⊕x2x4⊕x3x4)(x5x6⊕х5х7⊕х5х8⊕x6x⊕x6x8⊕x7x8),

Z4=x1x2x3x4x5x6x7x8,

где символами ⊕ и . обозначены соответственно операции ИСКЛЮЧАЮЩЕЕ ИЛИ и И. Раскрыв скобки и упростив предпоследнее равенство с помощью соотношения y⊕y=0 (y∈{0,1}), получим

где  ; m=2g-1; xk1, …, xkm∈{x1, …, x8}, 1≤k1<…<km≤8;

; m=2g-1; xk1, …, xkm∈{x1, …, x8}, 1≤k1<…<km≤8;  есть количество неповторяющихся конъюнкций xk1…xkm, определяемое как число сочетаний из 8 по m. Таким образом, на выходах предлагаемого счетчика имеем Z1=β0, Z2=β1, Z3=β2, Z4=β3, где β3β2β1β0 есть двоичный код числа единичных сигналов в кортеже (x1, …, x8). При этом максимальное время задержки распространения сигнала в предлагаемом счетчике равно 6τЛЭ (τЛЭ - время задержки логического элемента).

есть количество неповторяющихся конъюнкций xk1…xkm, определяемое как число сочетаний из 8 по m. Таким образом, на выходах предлагаемого счетчика имеем Z1=β0, Z2=β1, Z3=β2, Z4=β3, где β3β2β1β0 есть двоичный код числа единичных сигналов в кортеже (x1, …, x8). При этом максимальное время задержки распространения сигнала в предлагаемом счетчике равно 6τЛЭ (τЛЭ - время задержки логического элемента).

Вышеизложенные сведения позволяют сделать вывод, что предлагаемый параллельный счетчик единичных сигналов обладает функциональными возможностями прототипа, меньшими по сравнению с ним аппаратурными затратами и более высоким быстродействием.

| название | год | авторы | номер документа |

|---|---|---|---|

| ПАРАЛЛЕЛЬНЫЙ СЧЕТЧИК ЕДИНИЧНЫХ СИГНАЛОВ | 2005 |

|

RU2284655C1 |

| ЛОГИЧЕСКИЙ МОДУЛЬ | 2019 |

|

RU2718209C1 |

| ИДЕНТИФИКАТОР ЧИСЛА ЕДИНИЧНЫХ СИГНАЛОВ | 2005 |

|

RU2277260C1 |

| УСТРОЙСТВО СОРТИРОВКИ ДВОИЧНЫХ ЧИСЕЛ | 2007 |

|

RU2383052C2 |

| ЛОГИЧЕСКИЙ ВЫЧИСЛИТЕЛЬ | 2005 |

|

RU2294009C1 |

| ЛОГИЧЕСКИЙ ВЫЧИСЛИТЕЛЬ | 2004 |

|

RU2276399C1 |

| УСТРОЙСТВО СОРТИРОВКИ ДВОИЧНЫХ ЧИСЕЛ | 2011 |

|

RU2445678C1 |

| УСТРОЙСТВО СОРТИРОВКИ ДВОИЧНЫХ ЧИСЕЛ | 2005 |

|

RU2300136C1 |

| ПАРАЛЛЕЛЬНЫЙ СЧЕТЧИК ЕДИНИЧНЫХ СИГНАЛОВ | 2004 |

|

RU2260204C1 |

| ЛОГИЧЕСКИЙ ПРЕОБРАЗОВАТЕЛЬ | 2013 |

|

RU2518669C1 |

Изобретение относится к вычислительной технике и может быть использовано в системах цифровой вычислительной техники как средство предварительной обработки дискретной информации. Техническим результатом является уменьшение аппаратурных затрат и повышение быстродействия. Устройство содержит шестнадцать элементов ИСКЛЮЧАЮЩЕЕ ИЛИ и двенадцать элементов И. 1 ил.

Параллельный счетчик единичных сигналов, содержащий шестнадцать элементов ИСКЛЮЧАЮЩЕЕ ИЛИ и двенадцать элементов И, причем первый и второй входы r-го (r∈{1, …, 7, 9, …, 12}) элемента ИСКЛЮЧАЮЩЕЕ ИЛИ соединены соответственно с первым и вторым входами r-го элемента И, а первые входы четвертого, шестого и выход двенадцатого элементов И подключены соответственно к пятому, седьмому входам параллельного счетчика единичных сигналов и первому входу шестнадцатого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, отличающийся тем, что первый и второй входы восьмого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ соединены соответственно с первым и вторым входами восьмого элемента И, первый, второй входы i-го

| ПАРАЛЛЕЛЬНЫЙ СЧЕТЧИК ЕДИНИЧНЫХ СИГНАЛОВ | 2004 |

|

RU2260204C1 |

| ИДЕНТИФИКАТОР ЧИСЛА ЕДИНИЧНЫХ СИГНАЛОВ | 2004 |

|

RU2256211C1 |

| ПАРАЛЛЕЛЬНЫЙ СЧЕТЧИК ЕДИНИЧНЫХ СИГНАЛОВ | 2005 |

|

RU2284655C1 |

| УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ КОЛИЧЕСТВА ЕДИНИЦ (НУЛЕЙ) В ДВОИЧНОМ ЧИСЛЕ | 2011 |

|

RU2446442C1 |

| US 2004223580 A1, 11.11.2004 | |||

| US 5339447 A, 16.08.1994 | |||

| WO 2007002802 A1, 04.01.2007 | |||

Авторы

Даты

2014-06-10—Публикация

2013-02-01—Подача