Изобретение относится к вычислительной технике и может быть использовано для построения средств автоматики, функциональных узлов систем управления и др.

Известны идентификаторы числа единичных сигналов (см., например, рис.2 в статье Музыченко О.Н. Однородные и регулярные структуры для реализации симметричных функций алгебры логики. // Автоматика и телемеханика. 1998. №4. С.152-165), которые идентифицируют число единичных сигналов входного кортежа (х1,... ,х8), где хq∈{0,1} (по мере наращивания числа единичных сигналов в кортеже (х1,... ,х8) по выходам упомянутых идентификаторов сверху вниз продвигается “ртутный столбик” из логических единиц).

К причине, препятствующей достижению указанного ниже технического результата при использовании известных идентификаторов числа единичных сигналов, относится сложная структура, поскольку эти идентификаторы имеют восемь выходов.

Наиболее близким устройством того же назначения к заявленному изобретению по совокупности признаков является принятый за прототип идентификатор числа единичных сигналов (см. рис.8.12 на стр.479 в книге Шевкопляс Б.В. Микропроцессорные структуры. Инженерные решения: Справочник. М.: Радио и связь, 1990), содержащий двадцать две ячейки, каждая из которых содержит два входа, два выхода, элемент “И”, и идентифицирующий число единичных сигналов входного кортежа (х1,... ,х8), где xq∈{0,1}.

К причине, препятствующей достижению указанного ниже технического результата при использовании прототипа, относится сложная структура, поскольку прототип имеет восемь выходов.

Техническим результатом изобретения является упрощение структуры за счет уменьшения количества выходов в два раза.

Указанный технический результат при осуществлении изобретения достигается тем, что в идентификаторе числа единичных сигналов, содержащем двадцать две ячейки, каждая из которых содержит два входа, два выхода и элемент “И”, подключенный первым, вторым входами и выходом соответственно к ее первому, второму входам и первому выходу, все ячейки сгруппированы в матрицу из четырех строк и семи столбцов так, что i-ая  строка и j-ый

строка и j-ый  столбец содержат соответственно 8-i и j ячеек, в i-ой

столбец содержат соответственно 8-i и j ячеек, в i-ой  строке второй выход каждой предыдущей ячейки и второй выход последней ячейки соединены соответственно с вторым входом последующей ячейки и i-ым выходом идентификатора числа единичных сигналов, а в j-ом

строке второй выход каждой предыдущей ячейки и второй выход последней ячейки соединены соответственно с вторым входом последующей ячейки и i-ым выходом идентификатора числа единичных сигналов, а в j-ом  столбце первый выход каждой предыдущей ячейки и первый вход первой ячейки соединены соответственно с первым входом последующей ячейки j-ым входом идентификатора числа единичных сигналов, первый выход j-ой ячейки j-го

столбце первый выход каждой предыдущей ячейки и первый вход первой ячейки соединены соответственно с первым входом последующей ячейки j-ым входом идентификатора числа единичных сигналов, первый выход j-ой ячейки j-го  столбца подключен к второму входу (j+1)-ой ячейки (j+1)-го столбца, а второй вход первой ячейки первого столбца - к восьмому входу идентификатора числа единичных сигналов, особенность заключается в том, что в каждую ячейку введен элемент “исключающее ИЛИ”, подсоединенный первым, вторым входами и выходом соответственно к ее первому, второму входам и второму выходу.

столбца подключен к второму входу (j+1)-ой ячейки (j+1)-го столбца, а второй вход первой ячейки первого столбца - к восьмому входу идентификатора числа единичных сигналов, особенность заключается в том, что в каждую ячейку введен элемент “исключающее ИЛИ”, подсоединенный первым, вторым входами и выходом соответственно к ее первому, второму входам и второму выходу.

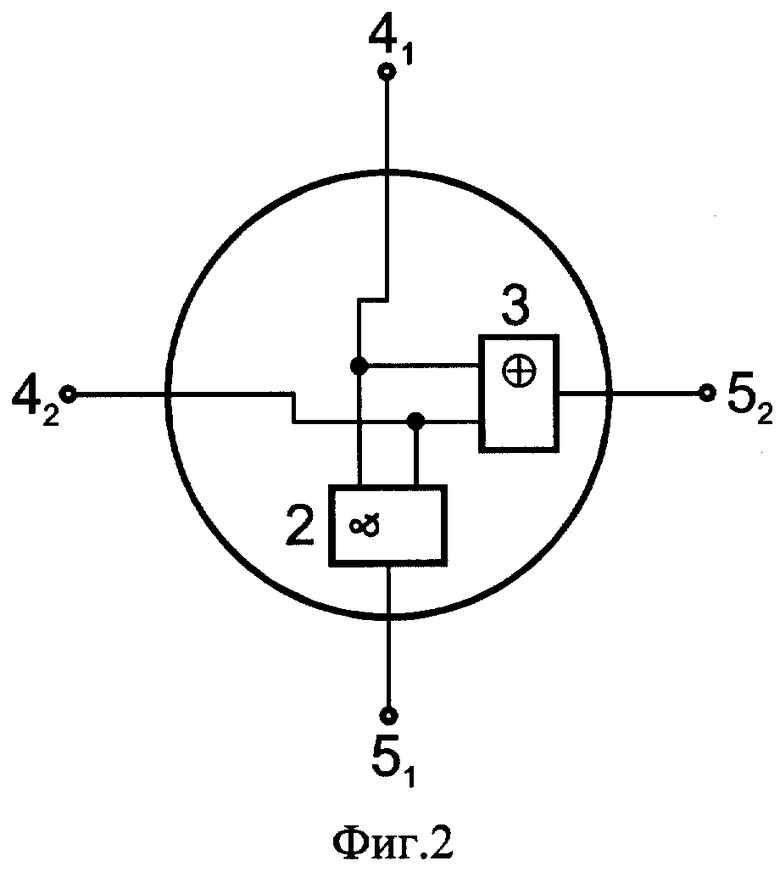

На фиг.1 и 2 представлены соответственно схема предлагаемого идентификатора числа единичных сигналов и схема ячейки, использованной при построении указанного идентификатора.

Идентификатор числа единичных сигналов содержит двадцать две ячейки 111,... ,147. Каждая ячейка содержит элемент “И” 2, элемент “исключающее ИЛИ” 3, первый и второй входы 41 и 42, первый и второй выходы 51 и 52, причем вход 41, вход 42 и выходы 51, 52 образованы соответственно объединенными первыми, объединенными вторыми входами элементов 2, 3 и выходом элемента 2, выходом элемента 3. Все ячейки сгруппированы в матрицу из четырех строк и семи столбцов так, что i-ая  строка и j-ый

строка и j-ый  столбец содержат соответственно 8-i и j ячеек, в i-ой

столбец содержат соответственно 8-i и j ячеек, в i-ой  строке выход 52 каждой предыдущей ячейки и выход 52 ячейки 1i7 соединены соответственно с входом 42 последующей ячейки и i-ым выходом идентификатора числа единичных сигналов, а в j-ом

строке выход 52 каждой предыдущей ячейки и выход 52 ячейки 1i7 соединены соответственно с входом 42 последующей ячейки и i-ым выходом идентификатора числа единичных сигналов, а в j-ом  столбце выход 51 каждой предыдущей ячейки и вход 41 ячейки 11j соединены соответственно с входом 41 последующей ячейки и j-ым входом идентификатора числа единичных сигналов, выход 51 ячейки 1ij

столбце выход 51 каждой предыдущей ячейки и вход 41 ячейки 11j соединены соответственно с входом 41 последующей ячейки и j-ым входом идентификатора числа единичных сигналов, выход 51 ячейки 1ij подключен к входу 42 ячейки 1(i+1)(j+1), а вход 42 ячейки 111 - к восьмому входу идентификатора числа единичных сигналов.

подключен к входу 42 ячейки 1(i+1)(j+1), а вход 42 ячейки 111 - к восьмому входу идентификатора числа единичных сигналов.

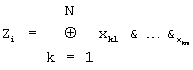

Работа предлагаемого идентификатора числа единичных сигналов осуществляется следующим образом. На его первый,..., восьмой входы подаются соответственно сигналы х1,... ,х8 ∈{0,1). Тогда сигнал на его i-ом  выходе будет определяться выражением

выходе будет определяться выражением

,

,

где символами ⊕ и & обозначены соответственно операции “ИСКЛЮЧАЮЩЕЕ ИЛИ” и “И”; m=2i-1; хk1,... ,хkm ∈{x1,... ,x8} (1≤ k1<... <km≤ 8);  есть количество неповторяющихся конъюнкций хk1 &... & хkm, определяемое как число сочетаний из 8 по m. В частности, имеем Z1=х1 ⊕ ... ⊕ х8,

есть количество неповторяющихся конъюнкций хk1 &... & хkm, определяемое как число сочетаний из 8 по m. В частности, имеем Z1=х1 ⊕ ... ⊕ х8,

Z2=x1 & x2 ⊕ ... ⊕ x1 & x8 ⊕ x2 & x3 ⊕ ... ⊕ x2 & x8 ⊕

⊕ x3 & x4 ⊕ ... ⊕ x3 & x8 ⊕ x4 & x5 ⊕ ... ⊕ x4 & x8 ⊕ x5 & x6 ⊕ ... ⊕ x5 & x8 ⊕

⊕ x6 & x7 ⊕ x6 & x8 ⊕ x7 & x8.

Таким образом, получим  где

где  есть двоичный код числа единичных сигналов в кортеже (x1,... ,x8).

есть двоичный код числа единичных сигналов в кортеже (x1,... ,x8).

Вышеизложенные сведения позволяют сделать вывод, что предлагаемое устройство обеспечивает идентификацию числа единичных сигналов входного кортежа (x1,... ,x8) и обладает более простой по сравнению с прототипом структурой, так как имеет только четыре выхода.

| название | год | авторы | номер документа |

|---|---|---|---|

| ПАРАЛЛЕЛЬНЫЙ СЧЕТЧИК ЕДИНИЧНЫХ СИГНАЛОВ | 2004 |

|

RU2260204C1 |

| РАНГОВЫЙ ИДЕНТИФИКАТОР | 2001 |

|

RU2192664C1 |

| ПАРАЛЛЕЛЬНЫЙ СЧЕТЧИК ЕДИНИЧНЫХ СИГНАЛОВ | 2013 |

|

RU2518641C1 |

| СУММАТОР ЕДИНИЧНЫХ СИГНАЛОВ | 2004 |

|

RU2260836C1 |

| КОММУТАЦИОННО-ЛОГИЧЕСКИЙ ПРОЦЕССОР | 1999 |

|

RU2166795C1 |

| РЕЛЯТОРНЫЙ КОММУТАТОР АНАЛОГОВЫХ СИГНАЛОВ С АДРЕСНЫМ УПРАВЛЕНИЕМ | 2004 |

|

RU2256220C1 |

| РЕЛЯТОРНЫЙ ИДЕНТИФИКАТОР | 2001 |

|

RU2194304C1 |

| Устройство для выдачи сообщений | 1989 |

|

SU1709367A1 |

| УСТРОЙСТВО ДЛЯ ВЫДАЧИ СООБЩЕНИЙ | 1992 |

|

RU2032936C1 |

| Устройство для выделения контура бинарного изображения | 1989 |

|

SU1661805A2 |

Изобретение относится к вычислительной технике и может быть использовано для построения средств автоматики, функциональных узлов систем управления. Техническим результатом изобретения является упрощение структуры идентификатора за счет уменьшения количества выходов в два раза. Указанный результат достигается за счет того, что идентификатор содержит двадцать две ячейки, каждая из которых содержит два входа, два выхода, элементы “И” и “ИСКЛЮЧАЮЩЕЕ ИЛИ”, причем все ячейки сгруппированы в матрицу из четырех строк и семи столбцов так, что i-ая (i=1,4) строка и j-ый (j=1,4) столбец содержат соответственно 8-i и j ячеек. 2 ил.

Идентификатор числа единичных сигналов, содержащий двадцать две ячейки, каждая из которых содержит два входа, два выхода и элемент И, подключенный первым, вторым входами и выходом соответственно к ее первому, второму входам и первому выходу, причем все ячейки сгруппированы в матрицу из четырех строк и семи столбцов так, что i-я (i=1,4) строка и j-й (j=1,4) столбец содержат соответственно 8-i и j ячеек, в i-й (i=1,4) строке второй выход каждой предыдущей ячейки и второй выход последней ячейки соединены соответственно со вторым входом последующей ячейки и i-м выходом идентификатора числа единичных сигналов, а в j-м (j=1,7) столбце первый выход каждой предыдущей ячейки и первый вход первой ячейки соединены соответственно с первым входом последующей ячейки и j-м входом идентификатора числа единичных сигналов, первый выход j-й ячейки j-гo (j=1,3) столбца подключен к второму входу (j+1)-й ячейки (j+1)-гo столбца, а второй вход первой ячейки первого столбца - к восьмому входу идентификатора числа единичных сигналов, отличающийся тем, что в каждую ячейку введен элемент Исключающее ИЛИ, подсоединенный первым, вторым входами и выходом соответственно к ее первому, второму входам и второму выходу.

| ШЕВКОПЛЯС Б.В | |||

| Микропроцессорные структуры | |||

| Инженерные решения: Справочник | |||

| М.: Радио и связь, 1990, с.479, рис.8.12 | |||

| Устройство для подсчета количества единиц в двоичном числе | 1990 |

|

SU1795455A1 |

| Устройство для подсчета числа единиц | 1989 |

|

SU1667083A1 |

| Устройство для контроля количества единиц двоичного кода по модулю К | 1986 |

|

SU1401464A2 |

Авторы

Даты

2005-07-10—Публикация

2004-03-12—Подача