Данное изобретение относится к вычислительной технике и автоматике, может быть использовано в ответственной аппаратуре, имеющей повышенные требования к надежности и не имеющей доступа для ремонта, например для космических аппаратов.

Известно устройство для вывода информации, реализующее способ исправления информации на параллельной магистрали путем тройной записи, со смещением информации на один разряд в каждом следующем повторении с последующим поразрядным мажорированием и содержащее дешифратор адреса, адресные входы которого являются адресными входами устройства; первый, второй и третий n-разрядные параллельные регистры, информационные входы которых объедены поразрядно и являются информационными входами устройства; группу n мажоритарных элементов, n-канальный коммутатор, число коммутируемых входов которого определяется количеством информационных входов устройства, а выходы которого являются информационными выходами устройства; счетчик на три, элемент «НЕ», элемент задержки, первые входы группы мажоритарных элементов соединены с соответствующими информационными выходами первого регистра, вход элемента задержки объединен с входом «запись» третьего регистра, выход дешифратора адреса соединен через элемент «НЕ» с входом «сброс» счетчика, первый выход которого соединен с входом «запись» первого регистра, второй выход соединен с входом «запись» второго регистра, третий выход соединен с объединенными входом «запись» третьего регистра и входом элемента задержки, вход «Запись» устройства соединен со счетным входом счетчика, вторые входы группы мажоритарных элементов соединены с соответствующими информационными выходами второго регистра со смещением на один разряд относительно первого регистра, третьи входы группы мажоритарных элементов соединены с соответствующими информационными выходами третьего регистра со смещением на один разряд относительно второго регистра, выходы группы мажоритарных элементов соединены с соответствующими входами n-канального коммутатора, управляющий вход которого подключен к выходу элемента задержки (патент РФ 2451323, G06F 3/00, G06F 13/38, G06F 11/16).

Недостатком данного устройства является невозможность исправлять (парировать) групповые ошибки (отказы в двух и более рядом расположенных разрядах магистрали) и не позволяет определять номера сбойных или отказавших разрядов.

Известно также устройство обнаружения и коррекции ошибок в параллельной магистрали с помощью мажорирования, реализующее способ тройной передачи цифровой информации через параллельную магистраль, в котором первая передача осуществляется без изменений, вторая в инверсном коде, третья с циклическим смещением информации влево (вправо) с обратным восстановлением на приемной стороне, а именно первая посылка остается без изменений, вторая посылка инвертируется, третья циклически смещается вправо (влево), с последующим мажорированием информации. Устройство состоит из трех регистров, входных управляемых ключей, группы элементов «НЕ» и блока мажоритарной логики, причем третий регистр имеет рециркуляционный путь (выход соединен с входом), т.е. регистр сдвига (Европейский патент EP 0177690 G06F 11/18, фиг.3 - принятый в качестве прототипа).

Недостатком данного устройства является недостаточное быстродействие. Задержка готовности информации на выходе устройства зависит от времени сдвига информации в третьем регистре. Устройство позволяет корректировать максимальное количество групповых ошибок (отказов), определяемое как n/2 (где n - число разрядов передаваемой информации), таким образом, время задержки готовности информации на выходе устройства за счет сдвига информации в третьем регистре увеличится на: tзад.=Tтакт.×n/2, где Tтакт. - период частоты сдвига. Кроме того, устройство позволяет определить только факт наличия сбоя или отказа, но не позволяет определять номера отказавших разрядов.

Целью изобретения является повышение быстродействия и надежности при передаче цифровой информации через параллельную магистраль. А также определять разряды магистрали, в которых присутствует неисправность.

Указанная цель достигается тем, что в устройство, содержащее первый, второй и третий n-разрядные параллельные регистры с входом «запись», группу элементов «НЕ» (n элементов «НЕ»), блок мажоритарной логики, информационные входы регистров поразрядно объединены и являются информационным входом устройства, выходы второго регистра соединены с входами группы элементов «НЕ», введены n элементов «исключающее ИЛИ», первая и вторая группа элементов «И», элемент задержки, вход которого объединен с входом «запись» третьего регистра, блок мажоритарной логики выполнен на n мажоритарных элементах, первые входы которых соединены с соответствующими информационными выходами первого регистра, вторые входы соединены с соответствующими выходами элементов «НЕ», а третьи входы соединены с соответствующими информационными выходами третьего регистра со смещением на n/2 разряд относительно первого регистра, первые входы элементов «исключающее ИЛИ» объединены с первыми входами второй группы элементов «И» и подключены к выходам соответствующих мажоритарных элементов, вторые входы элементов «исключающее ИЛИ» объединены с первыми входами соответствующих мажоритарных элементов, а выходы соединены с первыми входами второй группы элементов «И», вторые входы которых объединены и являются входом разрешения съема сигналов «ошибка» устройства, выходы второй группы элементов «И» являются выходами «ошибка» соответствующих разрядов устройства, вторые входы первой группы элементов «И» объединены и подключены к выходу элемента задержки, а выходы являются информационными выходами устройства.

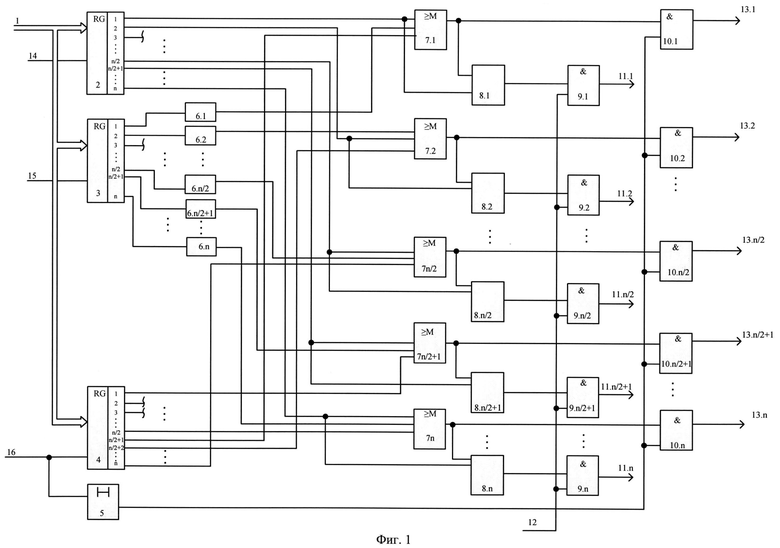

На чертеже представлена функциональная схема устройства для обнаружения и коррекции ошибок в параллельной магистрали.

Устройство обнаружения и коррекции ошибок в параллельной магистрали содержит информационный вход 1, который соединяется с параллельной магистралью; первый 2, второй 3, третий 4 регистры; элемент задержки 5; группу элементов «НЕ» 6.1-6.n; группу мажоритарных элементов 7.1-7.n; группу элементов «исключающее ИЛИ» 8.1-8.n, первую группу элементов «И» 9.1-9.n; вторую группу элементов «И» 10.1-10.n; поразрядные выходы «ошибка» устройства 11.1-11.n; вход разрешения съема сигналов «ошибка» устройства 12; информационные выходы устройства 13.1-13.n; входы записи первого 14, второго 15, третьего 16 регистров.

Данное устройство реализует приемную часть способа исправления информации на параллельной магистрали путем тройной записи, в котором первая передача осуществляется без изменений, вторая в инверсном коде, третья со смещением на n/2 бит (где n - число разрядов передаваемой информации) влево (вправо) с обратным восстановлением на приемной стороне, а именно первая посылка остается без изменений, вторая посылка инвертируется, третья циклически смещается на n/2 бит вправо (влево), с последующим мажорированием информации. Таким образом, например для n=8, информация первого разряда будет передаваться первый раз в первом разряде, во второй раз также в первом разряде, но с инверсией, в третий раз в пятом разряде. Информация второго разряда будет передаваться первый раз во втором разряде, во второй раз также во втором разряде, но с инверсией, в третий раз в шестом разряде, и так далее. Передающая часть способа выполняется программно в контроллере параллельной магистрали.

Устройство работает следующим образом.

При подаче питания на устройство регистры 2-4 обнуляются, цепи обнуления условно не показаны. Обнуление регистров также может быть выполнено через магистраль тройной записью нулевой информации по шине данных.

При поступлении на вход 14 сигнала «запись» первого регистра данные с информационного входа 1 устройства записываются в первый регистр 2. При поступлении на вход 15 сигнала «запись» на второй регистр инвертированные данные с информационного входа 1 устройства записываются во второй регистр 3. При поступлении на вход 16 сигнала «запись» на третий регистр 4 данные (смещенные на n/2 бита относительно предыдущих данных) с информационного входа 1 устройства записываются в третий регистр 4. Информация с выходов первого регистра 2 и третьего регистра 4, а второго регистра 3 через группу элементов «НЕ» 6.1-6.n поступает на соответствующие входы группы мажоритарных элементов 7.1-7.n. Группа элементов «исключающее ИЛИ» 8.1-8.n поразрядно сравнивает информацию на первом входе мажоритарных элементов с информацией на выходе мажоритарных элементов группы мажоритарных элементов 7.1-7.n, если она совпадает, то формируется сигнал логического «0», если нет - то формируется сигнал логической «1». Далее данная информация через первую группу элементов «И» 9.1-9.n при наличии разрешающего сигнала на входе разрешения съема сигналов «ошибка» 12 поступает на поразрядные выходы «ошибка» устройства 11.1-11.n.Сигнал с входа 16 через время, определяемое элементом задержки 5, открывает элементы «И» 10.1-10.n для прохождения поразрядно промажорированной информации в группе мажоритарных элементов 7.1-7.n на информационные выходы 13.1-13.n устройства. Элемент задержки 5 обеспечивает время завершения переходных процессов в регистре 4 и в мажоритарных элементах 7.1-7.n. Поясним работу устройства при наличии неисправностей в шине данных на примере 16-ти разрядного двоичного кода.

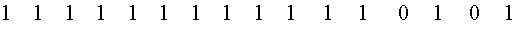

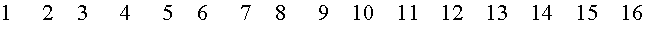

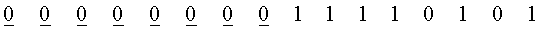

Пусть необходимо передать код:

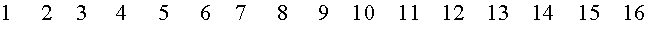

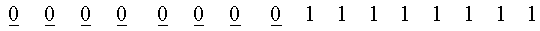

Допустим что в первых 8-и разрядах шины данных неисправность постоянный «0», тогда записанная информация в первый регистр 2 будет содержать ложный «0» в первых 8-и разрядах:

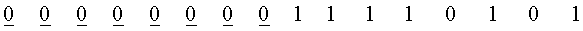

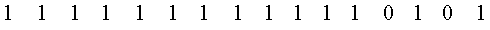

Записанная информация во второй регистр 3 (инвертированная) не будет содержать ложной информации, т.к. она будет совпадать с «0» в неисправных разрядах:

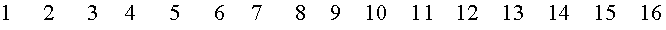

Записанная информация в третий регистр 4 (смещенная на n/2 разряда вправо относительно информации в первом регистре 2) будет иметь вид:

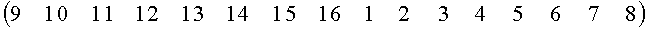

В скобках показан номер передаваемого разряда, из чего видно, что информация первого разряда передается в девятом, второго разряда в десятом и т.д. На входах мажоритарных элементов 7.1-7.n информация по разрядно имеет вид:

на входах 1

на входах 2

на входах 3

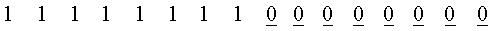

В мажоритарных элементах 7.1-7.n информация мажорируется «2 из 3» и по большинству в одноименных разрядах принимает вид:

В результате независимо от неисправности в первых 8-и разрядах типа постоянный «0» информация на информационных выходах 13.1-13.n устройства передана верно.

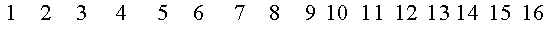

В то же время на входах элементов «исключающее ИЛИ» 8.1-8.n присутствует информация:

В результате на выходе элементов «исключающее ИЛИ» согласно логике работы элемента будет следующая информация:

Данная информация показывает, что в разрядах с 1 по 8 имеется неисправность, которая парирована устройством, а при наличии разрешающего сигнала на входе 12 эта информация может быть считана с выходов 11.1-11.n устройства.

Таким образом, данное устройство позволяет парировать отказы разрядов в шине данных параллельной магистрали, тем самым повысить отказоустойчивость. Количество исправленных разрядов i будет определяться:

i=n/2

Аналогичным образом возможно парировать отказы разрядов и в шине адреса параллельной магистрали.

Данное устройство предполагается использовать в аппаратуре управления космических аппаратов с конструктивным исполнением на ПЛИС. Опытный образец выполнен на интегральных микросхемах серии 1526, элемент задержки выполнен на RC цепочке.

Предложенное устройство позволит передавать цифровую информацию через параллельную магистраль при наличии групповых отказов (n/2, где n - число разрядов передаваемой информации), без временной задержки на циклический сдвиг, тем самым повысить быстродействие. А также определять разряды магистрали, в которых присутствует неисправность или сбои.

Из известных автору источников информации и патентных материалов не известна совокупность признаков, сходных с совокупностью признаков заявляемого объекта.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ ВЫВОДА ИНФОРМАЦИИ | 2011 |

|

RU2451323C1 |

| ОТКАЗОУСТОЙЧИВАЯ СИСТЕМА УПРАВЛЕНИЯ | 2021 |

|

RU2763092C1 |

| Запоминающее устройство с коррекцией групповых ошибок | 1987 |

|

SU1481863A1 |

| ТРЕХКАНАЛЬНАЯ РЕЗЕРВИРОВАННАЯ МИКРОПРОЦЕССОРНАЯ СИСТЕМА | 1987 |

|

SU1494761A1 |

| Устройство для ввода-вывода информации | 1989 |

|

SU1615694A2 |

| СПОСОБ ПЕРЕДАЧИ ЦИФРОВОЙ ИНФОРМАЦИИ ЧЕРЕЗ ПАРАЛЛЕЛЬНУЮ МАГИСТРАЛЬ | 2011 |

|

RU2465632C1 |

| Устройство для приема последовательного кода | 1986 |

|

SU1390625A2 |

| Устройство для коррекции ошибок внешней памяти | 1989 |

|

SU1662011A1 |

| СПОСОБ ПЕРЕДАЧИ ЦИФРОВОЙ ИНФОРМАЦИИ ЧЕРЕЗ ПАРАЛЛЕЛЬНУЮ МАГИСТРАЛЬ | 2009 |

|

RU2413283C2 |

| УСТРОЙСТВО СЧИТЫВАНИЯ ИНФОРМАЦИИ ДЛЯ ТРАНСПОРТНОГО СРЕДСТВА | 1994 |

|

RU2083411C1 |

Данное изобретение относится к вычислительной технике и автоматике. Технический результат заключается в повышении быстродействия и надежности при передаче цифровой информации через параллельную магистраль. Технический результат достигается за счет устройства, которое реализует приемную часть способа исправления информации на параллельной магистрали путем тройной записи, в котором первая передача осуществляется без изменений, вторая в инверсном коде, третья со смещением на n/2 бит (где n - число разрядов передаваемой информации) влево (вправо) с обратным восстановлением на приемной стороне, а именно: первая посылка остается без изменений, вторая посылка инвертируется, третья циклически смещается на n/2 бит вправо (влево), с последующим мажорированием информации. В устройство содержащее первый, второй и третий n-разрядные параллельные регистры с входом «запись», группу элементов «НЕ» (n элементов «НЕ»), блок мажоритарной логики, информационные входы регистров поразрядно объединены и являются информационным входом устройства, выходы второго регистра соединены с входами группы элементов «НЕ», введены n элементов «исключающее ИЛИ», первая и вторая группа элементов «И», элемент задержки, блок мажоритарной логики выполнен на n мажоритарных элементах. 1 ил.

Устройство для обнаружения и коррекции ошибок в параллельной магистрали с помощью мажорирования, содержащее первый, второй и третий n-разрядные параллельные регистры с входом «запись», группу элементов «НЕ» (n-элементов «НЕ»), блок мажоритарной логики, информационные входы регистров поразрядно объединены и являются информационным входом устройства, выходы второго регистра соединены с входами группы элементов «НЕ», отличающееся тем, что в него введены n-элементов «исключающее ИЛИ», первая и вторая группа элементов «И», элемент задержки; блок мажоритарной логики выполнен на n-мажоритарных элементах, первые входы которых объединены со вторыми входами элементов «исключающее ИЛИ» и соединены с соответствующими информационными выходами первого регистра, вторые входы соединены с соответствующими выходами элементов «НЕ», а третьи входы соединены с соответствующими информационными выходами третьего регистра со смещением на n/2 разряд относительно первого регистра; первые входы элементов «исключающее ИЛИ» объединены с первыми входами соответствующих элементов «И» второй группы элементов «И» и подключены к выходам соответствующих мажоритарных элементов, а выходы соединены с первыми входами соответствующих элементов «И» первой группы элементов «И», вторые входы которых объединены и являются входом разрешения выдачи информации о неисправности устройства («ошибка»); выходы элементов «И» первой группы элементов «И» являются выходами «ошибка» устройства; выходы элементов И второй группы элементов «И» являются информационными выходами устройства, вторые входы которых объединены и подключены к выходу элемента задержки, вход которого объединен с входом «запись» третьего регистра.

| ДИФФЕРЕНЦИРУЮЩЕЕ УСТРОЙСТВО ДЛЯ ПОЛУЧЕНИЯ ПРОИЗВОДНОЙ В ДИСКРЕТНЫХ СИСТЕМАХ | 0 |

|

SU177690A1 |

| Изложница с суживающимся книзу сечением и с вертикально перемещающимся днищем | 1924 |

|

SU2012A1 |

| ОТКАЗОУСТОЙЧИВОЕ ОПЕРАТИВНОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 2001 |

|

RU2211492C2 |

| Способ получения красителей ряда дитензниренхинона | 1936 |

|

SU51427A1 |

| Устройство для контроля цифровых узлов | 1989 |

|

SU1645958A2 |

Авторы

Даты

2014-08-10—Публикация

2013-07-12—Подача