Данное изобретение относится к вычислительной технике и автоматике, может быть использовано в ответственной аппаратуре, имеющей повышенные требования к надежности и не имеющей доступа для ремонта, например для космических аппаратов.

Известно устройство для вывода цифровой информации с параллельной магистрали, содержащее регистр, элемент И, элемент задержки, дешифратор адреса, блок сравнения, информационные входы регистра являются информационными входами устройства, а выходы соединены с входами блока сопряжения (магистральные усилители), выходы которого являются информационными выходами устройства, вход записи регистра соединен с выходом дешифратора, входы которого являются адресными входами устройства, первая группа входов блока сравнения соединена с информационными входами регистра, вторая группа входов блока сравнения соединена с выходами блока сопряжения, а выход соединен с первым входом элемента И, выход которого является управляющим выходом устройства, второй вход элемента И соединен с выходом элемента задержки, вход которого соединен с выходом дешифратора (А.С. №1608631, G06F 3/00, автор В.В.Виноградов).

Данное устройство имеет недостаточную сбоеустойчивость и надежность. А именно при наличии сбоев на информационных входах устройства в момент записи в регистр будет занесена сбойная информация, следовательно, и на информационных выходах устройства будет сбойная информация, а если на момент сравнения информация на информационных входах устройства восстановится, то информация, записанная в регистр и на информационных выходах устройства будет разная, следовательно, информация на информационных выходах устройства будет пропущена.

Кроме того, при наличии неисправности на параллельной магистрали или на информационных входах устройства информация на выходе устройства будет искажаться.

Наиболее близким к предлагаемому по технической сущности является устройство для вывода информации, содержащее дешифратор адреса, блок сравнения, элемент задержки, первый и второй элементы И, элемент ИЛИ, блок сопряжения, первый, второй и третий регистры, группу мажоритарных элементов, число которых определяется количеством разрядов информационного входа устройства, информационные входы устройства соединены с информационными входами регистров и с первой группой входов блока сравнения, вторая группа входов которой соединена с выходами блока сопряжения, которые являются информационными выходами устройства, выход «Равно» блока сравнения соединен с первым входом первого элемента И, выход которого является управляющим выходом устройства, а выходы «Больше» и «Меньше» блока сравнения соединены со входами элемента ИЛИ, выход которого соединен с первым входом второго элемента И, вторые входы первого и второго элемента И соединены с выходом элемента задержки, выход второго элемента И является выходом «Неисправность» устройства, информационные выходы первого регистра соединены с первыми входами мажоритарных элементов, информационные выходы второго регистра соединены со вторыми входами мажоритарных элементов, информационные выходы третьего регистра соединены с третьими входами мажоритарных элементов, выходы которых соединены с входами блока сопряжения, адресные входы дешифратора являются адресными входами устройства, первый выход дешифратора соединен с входом «запись» первого регистра, второй выход дешифратора адреса соединен с входом «запись» второго регистра, третий выход дешифратора адреса соединен с входом «запись» третьего регистра и с входом элемента задержки (Патент РФ №2411568, G06F 3/00, автор Капустин А.Н.).

Данное устройство имеет недостаток - при наличии неисправности на параллельной магистрали информация будет искажаться на выходе устройства. А именно невозможность передачи цифровой информации с параллельной магистрали без искажения при наличии одного или более отказов типа постоянный логический 0 или логическая 1 в разрядах шины данных магистрали. Например, при наличии в первом разряде магистрали неисправности типа постоянный «0» переданная информация будет содержать ложный «0» в первом разряде при каждом из трех повторений и ложный «0» будет оставаться после мажорирования в мажоритарном элементе, таким образом, данное устройство не может передать достоверную информацию с параллельной магистрали при наличии отказа.

Целью изобретения является устранение указанного недостатка.

Поставленная цель достигается тем, что в устройство, содержащее три n-разрядных параллельных регистра, у которых соответствующие информационные входы объединены и являются информационными входами устройства, n мажоритарных элементов, дешифратор, вход которого является адресным входом устройства, элемент задержки, введены n-канальный коммутатор, состоящий из n элементов И, счетчик на три, элемент НЕ, первые входы мажоритарных элементов соединены с соответствующими информационными выходами первого регистра, вторые входы мажоритарных элементов соединены с соответствующими информационными выходами второго регистра со смещением на один бит относительно первого регистра, а третьи входы мажоритарных элементов соединены с соответствующими информационными выходами третьего регистра со смещением на один бит относительно второго регистра, выходы мажоритарных элементов соединены с соответствующими входами n-канального коммутатора, управляющий вход которого соединен с выходом элемента задержки, выходы n-канального коммутатора являются информационными выходами устройства, выход дешифратора через инвертор соединен с входом «Сброс» счетчика, счетный вход счетчика является входом «Запись» устройства, первый выход счетчика соединен с входом «запись» первого регистра, второй выход счетчика соединен с входом «запись» второго регистра, третий выход счетчика соединен с объединенными входом «запись» третьего регистра и входом элемента задержки.

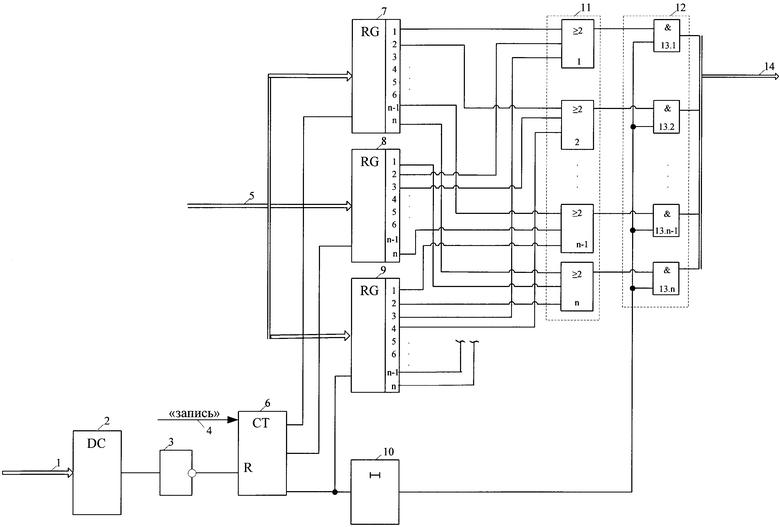

На чертеже представлена функциональная схема устройства для вывода цифровой информации.

Устройство для вывода цифровой информации содержит адресные входы 1, дешифратор адреса 2, элемент НЕ 3, вход «запись» устройства 4, информационные входы устройства 5, счетчик на три 6, первый 7, второй 8, третий 9 регистры, элемент задержки 10, группу мажоритарных элементов 11.1-11.n по числу разрядов регистров, n-канальный коммутатор 12, состоящий из элементов И 13.1-13.n, информационные выходы 14 устройства.

Данное устройство реализует способ исправления информации на параллельной магистрали путем тройной записи, со смещением информации на один разряд в каждом следующем повторении с последующим поразрядным мажорированием. Таким образом, информация первого разряда будет передаваться первый раз в первом разряде, во второй раз во втором разряде, в третий раз в третьем разряде. Информация второго разряда будет передаваться первый раз во втором разряде, во второй раз в третьем разряде, в третий раз в четвертом разряде, и так далее.

Параллельная магистраль состоит из шины данных, шины адреса, строба записи, порядок работы магистрали следующий: сначала устанавливается адрес на шине адреса, затем данные на шине данных (или одновременно с адресом) и далее строб записи.

Устройство работает следующим образом.

При подаче питания на устройство счетчик 6 и регистры 7-9 обнуляются, цепи обнуления условно не показаны. Обнуление регистров также может быть выполнено через магистраль тройной записью нулевой информации по шине данных.

При поступлении соответствующего адреса на адресный вход 1 устройства дешифратор адреса 2 через элемент НЕ 3 снимает запрещающий сигнал с входа «Сброс» счетчика 6, по первому счетному импульсу с входа «запись» 4 устройства на первом выходе счетчика 6 устанавливается логическая «1», которая записывает данные с информационных входов 5 устройства в первый регистр 7, по второму счетному импульсу на втором выходе счетчика 6 устанавливается логическая «1», которая записывает данные с информационных входов 5 устройства (смещенные на один бит относительно предыдущих данных) во второй регистр 8, по третьему счетному импульсу на третьем выходе счетчика 6 устанавливается логическая «1», которая записывает данные с информационных входов 5 устройства (смещенные на один бит относительно предыдущих данных) в третий регистр 9 и через время, определяемое элементом задержки 10, открывает элементы И 13.1-13.n n-канального коммутатора 12 для прохождения поразрядно промажорированной информации в группе мажоритарных элементов 11.1-11.n на информационные выходы 14 устройства. После снятия сигналов с адресного входа 1 устройства дешифратор адреса 2 через элемент НЕ 3 устанавливает запрещающий сигнал на вход «Сброс» счетчика 6, который обнуляет счетчик и через время, определяемое элементом задержки 10, закрывает элементы И 13.1-13.n, тем самым снимает информацию с информационных выходов 14 устройства. Элемент задержки 10 обеспечивает время завершения переходных процессов в регистре 9 и в мажоритарных элементах 11.1-11.n.

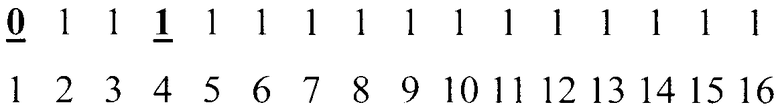

Поясним работу устройства при наличии неисправностей в шине данных на примере 16-разрядного двоичного кода. Пусть необходимо передать код:

Допустим в первом разряде шины данных неисправность постоянный «0», в четвертом разряде неисправность постоянная «1», тогда записанная информация в первый регистр 7 будет содержать ложный «0» в первом разряде и ложная «1» в четвертом разряде:

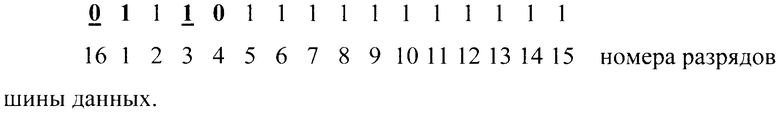

Записанная информация во второй регистр 8 (смещенная на один разряд вправо относительно информации в регистре 7) будет содержать ложный «0» в шестнадцатом разряде, а ложная «1» в третьем разряде, которая не искажает принятую информацию:

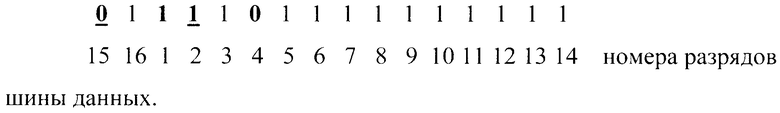

Записанная информация в третий регистр 9 (смещенная на один разряд вправо относительно информации в регистре 8) будет содержать ложный «0» в пятнадцатом разряде и ложную «1» во втором разряде, которая не искажает принятую информацию:

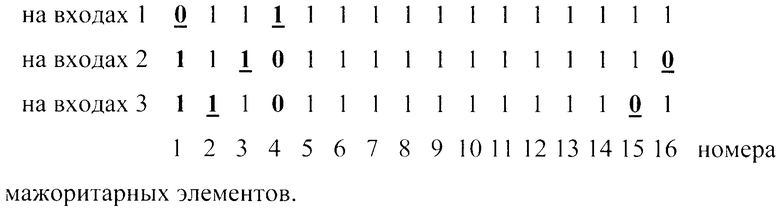

На входах мажоритарных элементтов 11.1-11.n информация поразрядно имеет вид:

В мажоритарных элементах информация мажорируется «2 из 3» и по большинству в одноименных разрядах принимает вид:

В результате независимо от неисправности первого и четвертого разряда информация на информационных выходах устройства 13 передана верно.

Таким образом, данное устройство позволяет парировать отказы разрядов в шине данных параллельной магистрали, тем самым повысить отказоустойчивость. Количество исправленных разрядов N будет определяться:

N=j/m,

где j - число разрядов в передаваемой информации, m - число входов мажоритарного устройства. В приведенном примере одновременное наличие неисправностей в 1, 4, 7, 10, 13 (или 2, 5, 8, 11, 14, или 3, 6, 9, 12, 15 и т.д.) разрядах может быть парировано.

Данное устройство предполагается использовать в аппаратуре управления космических аппаратов. Опытный образец выполнен на интегральных микросхемах серии 1526, элемент задержки выполнен на RC цепочке.

Данное устройство, кроме того, может быть использовано как устройство исправления информации в параллельной шине на запись, для чего необходимо установить формирователь выходного сигнала «запись», запускающийся от выходного сигнала с элемента задержки.

Из известных авторам источников информации и патентных материалов не известна совокупность признаков, сходных с совокупностью признаков заявляемого объекта.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ОБНАРУЖЕНИЯ И КОРРЕКЦИИ ОШИБОК В ПАРАЛЛЕЛЬНОЙ МАГИСТРАЛИ | 2013 |

|

RU2524854C1 |

| Устройство для приема последовательного кода | 1986 |

|

SU1390625A2 |

| Мультиплексное устройство для обмена информацией | 1983 |

|

SU1157546A1 |

| УСТРОЙСТВО ДЛЯ ВЫВОДА ИНФОРМАЦИИ | 2009 |

|

RU2411568C2 |

| Устройство для сопряжения двух вычислительных машин | 1987 |

|

SU1474665A1 |

| Устройство для сопряжения ЭВМ с разноскоростными группами внешних устройств | 1990 |

|

SU1837302A1 |

| Трехканальная резервированная микропроцессорная система | 1985 |

|

SU1378287A1 |

| Устройство для управления режимамиОбМЕНА РЕзЕРВиРОВАННОй СиСТЕМы | 1979 |

|

SU849216A1 |

| Устройство для имитации неисправностей | 1987 |

|

SU1444775A1 |

| Устройство для сопряжения разнотипных вычислительных машин | 1986 |

|

SU1381526A2 |

Изобретение относится к вычислительной технике и автоматике, может быть использовано в аппаратуре, имеющей повышенные требования к надежности и не имеющей доступа для ремонта, например для космических аппаратов. Техническим результатом является повышение отказоустойчивости устройства для вывода информации. В устройство вывода информации введены n-канальный коммутатор, число коммутируемых входов которого определяется количеством информационных входов устройства, а выходы которого являются информационными выходами устройства, счетчик на три, элемент НЕ, выход дешифратора адреса соединен через элемент НЕ с входом «сброс» счетчика, первый выход которого соединен с входом «запись» первого регистра, второй выход соединен с входом «запись» второго регистра, третий выход соединен с объединенными входом «запись» третьего регистра и входом элемента задержки, вход «Запись» устройства соединен со счетным входом счетчика, вторые входы группы мажоритарных элементов соединены с соответствующими информационными выходами второго регистра со смещением на один разряд относительно первого регистра, третьи входы группы мажоритарных элементов соединены с соответствующими информационными выходами третьего регистра со смещением на один разряд относительно второго регистра, выходы группы мажоритарных элементов соединены с соответствующими входами n-канального коммутатора, управляющий вход которого подключен к выходу элемента задержки. 1 з.п. ф-лы, 1 ил.

1. Устройство для вывода информации, содержащее дешифратор адреса, адресные входы которого являются адресными входами устройства, первый, второй и третий n-разрядные параллельные регистры, информационные входы которых объединены поразрядно и являются информационными входами устройства, группу мажоритарных элементов, число которых определяется количеством информационных входов устройства, первые входы группы мажоритарных элементов соединены с соответствующими информационными выходами первого регистра, элемент задержки, вход которого объединен с входом «запись» третьего регистра, отличающееся тем, что в него введены n-канальный коммутатор, число коммутируемых входов которого определяется количеством информационных входов устройства, а выходы которого являются информационными выходами устройства, счетчик на три, элемент НЕ, выход дешифратора адреса соединен через элемент НЕ с входом «сброс» счетчика, первый выход которого соединен с входом «запись» первого регистра, второй выход соединен с входом «запись» второго регистра, третий выход соединен с объединенными входом «запись» третьего регистра и входом элемента задержки, вход «запись» устройства соединен со счетным входом счетчика, вторые входы группы мажоритарных элементов соединены с соответствующими информационными выходами второго регистра со смещением на один разряд относительно первого регистра, третьи входы группы мажоритарных элементов соединены с соответствующими информационными выходами третьего регистра со смещением на один разряд относительно второго регистра, выходы группы мажоритарных элементов соединены с соответствующими входами n-канального коммутатора, управляющий вход которого подключен к выходу элемента задержки.

2. Устройство по п.1, отличающееся тем, что n-канальный коммутатор выполнен в виде группы элементов И, первые входы которых являются входами коммутатора, вторые входы объединены и являются управляющим входом коммутатора, а выходы - соответственно выходами коммутатора.

| УСТРОЙСТВО ДЛЯ ВЫВОДА ИНФОРМАЦИИ | 2009 |

|

RU2411568C2 |

| Устройство для вывода информации | 1988 |

|

SU1608631A1 |

| МИКРОПРОЦЕССОР ВВОДА-ВЫВОДА ИНФОРМАЦИИ | 1992 |

|

RU2042182C1 |

| JP 2007148900 А, 29.11.2005. | |||

Авторы

Даты

2012-05-20—Публикация

2011-03-31—Подача