Одним из основных компонентов бортовых систем автоматизированного и автоматического управления кораблями, авиационными объектами, изделиями ракетно-космической техники (РКТ) и мобильными робототехническими комплексами (РТК) является подсистема инерциальной навигации (ПИН). Традиционно, опираясь на богатый опыт создания нескольких поколений самолетов и баллистических ракет, как коммерческого, так и оборонного назначения ПИН реализуются на основе механических гиростабилизированных платформ (ГСП), теоретические основы расчета и проектирования достаточно хорошо проработаны, внедрены в производство, апробированы и даже являются учебным курсом в вышей школе (см., например, Лысов А.Н. «Теория расчета и проектирования гироскопических стабилизаторов». Курс лекций. Южно-уральский государственный университет, 2005, или Пельноп Д.С. «Гироскопические системы». Изд. Высшая школа, 1971, или К. Магнус «Гироскопия. Теория и применение». Изд. Мир, пер с нем. 1974).

ГСП хорошо себя зарекомендовали и широко применяются в бортовых корабельных, ракетно-космических и авиационных системах управления. (см. Ягодкин В.В., Хлебников Г.А. «Гироскопические приборы баллистических ракет» Изд. МО ССР. 1967, или Бороздин В.Н. «Гироскопические приборы и устройства систем управления» М.: Машиностроение, 1990).

Основным достоинством ГСП является долговременное удержание базовой пространственной ориентации, по крайней мере, трех ортогональных плоскостей, относительно которых снимаются показания акселерометров, датчиков углового перемещения и положения изделия, в приборном отсеке которого эти ГСП жестко закреплены. Перед началом работы изделия (объекта управления) производят привязку осей ГСП к базовым координатам начальной точки движения, например приводят одну из плоскостей ГСП в плоскость местного горизонта, вторую - в плоскость движения объекта (для ракет это плоскость траектории и углового перемещения по тангажу (углу тангажа), а третью плоскость оставляют для улов вращения (крена)). Это качество ГСП - сохранять длительное время за счет силовой стабилизации с опорой на гироскопы первоначально выставленную ориентацию является очень важным, так как позволяет бортовой цифровой вычислительной системе (БЦВС) по информации датчиков ГСП определять достаточно просто координаты и параметры движения объекта управления при приемлемых вычислительных ресурсах БЦВС, задачей которой является сведение отклонений углового положения изделия (объекта) от выставленных пред стартом (приведенных) осей ГСП к нулевому значению, Задача является не очень сложной и на заре создания систем управления изделий РКТ ее успешно решали относительно простые аналоговые решающие устройства, опираясь на замечательное свойство ГСП - сохранять заданную перед стартом пространственную ориентацию базовых плоскостей. Поэтому ГСП до появления бортовых цифровых вычислительных машин (БЦВМ) и БЦВС были основным элементом систем управления.

Однако ГСП не свободны от недостатков, основным из которых является узкий диапазон угловых изменений положения изделия относительно базовых осей ГСП, находящихся в кардановых подвесах, что связано с особенностями конструктивной реализации платформ, при которой снятие информации с датчиков и передача управляющих сигналов на двигатели силовой стабилизации ведется по проводам, собранным в жгуты. Жгуты обладают значительной упругостью, работают как паразитные пружины, вызывая отклонения, и, что особенно неприятно, ограничивают диапазон перемещения корпуса ГСП, а, следовательно, и изделия, с которым корпус жестко связан. Ограничение диапазона углового перемещения изделия совершенно неприемлемо для высокоманевренных объектов, которыми являются быстроходные катера, самолеты, космические челноки, а также мобильные РТК. Этот недостаток частично компенсируют для ряда объектов. В частности для баллистических ракет перед стартом проводят выставку одной из плоскостей ГСП в плоскость стрельбы, второй - в плоскость местного горизонта, а БЦВС системы управления постоянно определяет отклонения каждой плоскости изделия от базовой плоскости движения и сводит отклонения к нулевому значению. Однако этот прием совершенно не пригоден для самолетов и мобильных роботов, направление движения которых может достаточно часто меняться экипажем и оператором в зависимости от окружающей обстановки и выполняемой на данный момент работы. Возникает задача исключить карданные подвесы и жгуты, ограничивающие угловое перемещение объекта. Кроме того существенным недостатком механических ГСП является их большие масса, габариты, энергопотребление и невысокая надежность, так как отказ любого конструктивного узла или электронного элемента в системе силовой стабилизации приводит к отказу как ГСП, так и системы управления в целом. Это совершенно неприемлемо для авиационных систем и изделий РКТ, к которым предъявляется достаточно жесткое формальное требование - сохранять работоспособность при возникновении одной любой возможной неисправности в аппаратуре системы управления.

Для исключения ограничений по угловому перемещению объекта были созданы бесплатформенные инерциальные навигационные системы (БИНС), в которых базовая ориентация не опирается на гироскопы и двигатели силовой стабилизации, а вычисляется математически ботовыми вычислителями путем практически непрерывного обсчета информации датчиков угловой скорости (ДУС), в качестве которых могут использоваться кольцевые лазеры, образующие совместно с вычислительным устройством лазерный «гироскоп» (см., например, Бычков С.И., Лукьянов Д.П., Бакаляр А.И. «Лазерный гироскоп». Изд. Сов. Радио, 1975). Однако в последние годы применяют ДУС на основе оптического волокна, намотанного в виде катушки, ось которой располагают по оси ориентации объекта (см. Филатов Ю.В. «Волоконно-оптический гироскоп». Изд. СПб ГЭТУ ЛЭТИ. 2003). Такое построение БИНС требует очень высокой производительности БЦВС, а именно высокой скорости приема и обработки входной информации ДУС, поступающей в виде частоты, и быстрого вычисления тригонометрических функций в матричных вычислениях (в частности при перемножении матриц). Эти задачи не могут быть решены в требуемое время современными БЦВМ с традиционной архитектурой, опирающейся на процессоры с подключенными к ним запоминающими устройствами, особенно вычислителями с Неймановской архитектурой. Необходима разработка специализированной архитектуры вычислительных устройств, ориентированной на решение задач БИНС, что само по себе является достаточно сложной самостоятельной задачей. Удовлетворительное решение этой задачи на данное время не известно. Дополнительно к ряду объектов РКТ, а также РТК, предназначенных для ликвидации аварий, типа Чернобыльской или тушения пожаров на лесных, нефтяных и газовых промыслах, предъявляется требование работоспособности в экстремальных условиях и полях ионизирующего излучения. Экстремальность условий определяют широкий диапазон изменения температуры окружающей среды от -60 до +125 градусов по Цельсию и механические воздействия в виде ударов и широкополосной вибрации. Ионизирующие воздействия как непрерывные, так и импульсные обусловлены излучением космического пространства, фоном загрязненной местности, вспышками на Солнце и направленным противодействием.

Теория работы и принципы проектирования БИНС созданы и используются в учебных курсах (см. например, Бранец В.Н. «Лекции по теории бесплатформенных навигационных систем». Учеб. пособие. Изд. МФТИ, 2009). Имеются уже и промышленные изделия, выпускаемые в частности НПЦАП, г. Москва.

Однако пути решения задач обеспечения работоспособности БИНС в случае возникновении одиночных отказов при работе аппаратуры в экстремальных условиях и полях ионизирующего излучения в известных источниках не освещены и на практике не решены.

Достаточно полно решение задачи создания БИНС предложено в изобретении (см. «БИНС» патент RU №230385 С2//C01C 21/16), которое может быть взято за прототип.

Эта известная БИНС содержит три акселерометра и два ДУС, подключенные к вычислительному устройству. Кроме того в состав системы входят два имитатора для обеспечения предстартовой выставки БИНС, один из которых подключен к вычислительному устройству, а второй к свободному гироскопу.

Как видно из материалов данного изобретения, создателям этой БИНС не удалось исключить механические гироскопы. Это, по нашему мнению, связано с ограниченной производительностью вычислительного устройства, не имеющего средств ускорения вычислений тригонометрических функций, являющихся элементами матрицы, приведенной в материалах данного патента и обрабатываемой входящим в состав БИНС вычислительным устройством, от которого требуется высокая производительность, так как цикл вычислений и формирования трехмерной инерциальной системы угловых координат по информации, приведенной в материалах этого патента, ряда источников, опыта ряда предприятий Роскосмоса и нашего опыта создания систем автоматического управления высокоманевренными объектами не должен превышать 1 миллисекунды, что трудновыполнимо вычислительными устройствами с традиционной архитектурой. Кроме того данная известная система содержит только два датчика угловых скоростей, что недостаточно для формирования трехмерной инерциальной системы координат, которую обеспечивали хорошо зарекомендовавшие себя ГСП.

С другой стороны известная система содержит три акселерометра, причем не для резервирования, а для обеспечения функционирования, что является избыточным, так как для управления подвижными объектами достаточно одного акселерометра, жестко связанного с конструкцией объекта управления и расположенного так, чтобы его ось чувствительности совпадала с одной из базовых осей объекта, например с осью тяги маршевого двигателя (двигателей).

Кроме того отказ одного элемента в любом из компонентов системы приводит к ее неработоспособности, а это означает невыполнение предъявляемого к системам автоматического управления авиационными объектами и изделиями РКТ жесткого формального требования - сохранять работоспособность при возникновении одной возможной неисправности в любой из подсистем, что существенно ограничивает возможность применения данной БИНС в указанных системах управления, ко многим из которых кроме того предъявляется требование работы а экстремальных условиях и в полях ионизирующего излучения космического пространства и загрязненной местности при установке систем управления в РТК, предназначенные для ликвидации аварий, типа Чернобыльской.

Естественно, что все эти требования распространяются и на БИНС при их использовании в составе систем управления. Известная, по указанному патенту, БИНС этим требованиям не удовлетворяет, что существенно ограничивает область ее применения.

С целью расширения состава систем управления высокоманевренными наземными, водными и авиационными объектами, изделиями РКТ и РТК, работающими в экстремальных условиях и полях ионизирующего излучения и возможности использования в них БИНС предлагается БИНС повышенной надежности. Далее по тексту просто БИНС или система.

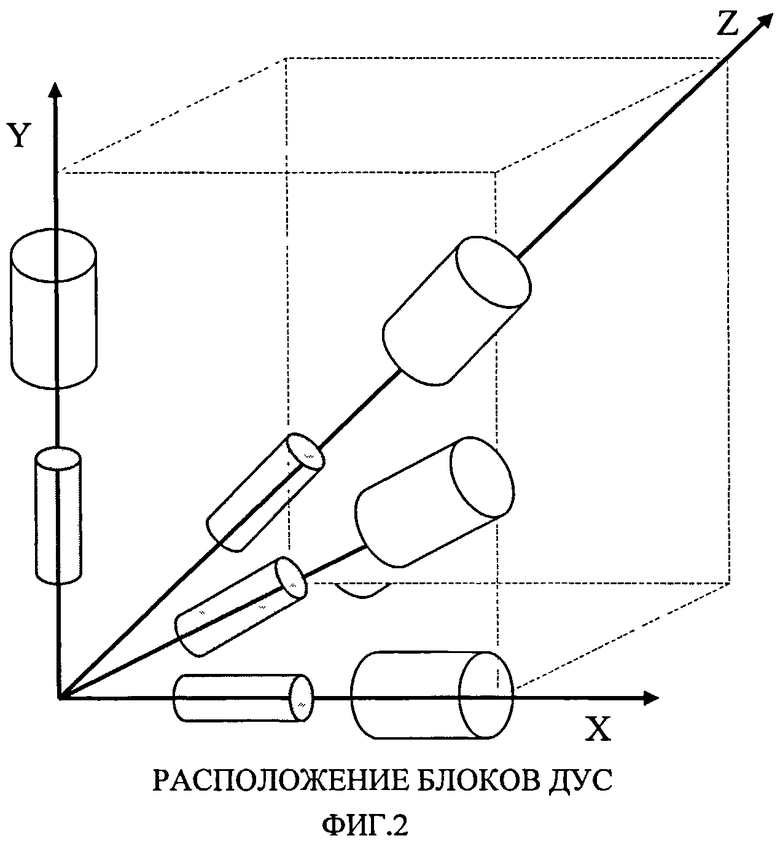

БИНС содержит объединенные в жесткую конструкцию четыре блока датчиков угловой скорости (ДУС), оси чувствительности трех из которых расположены ортогонально друг другу по смежным ребрам куба, исходящим из общей точки, а ось четвертого блока совпадает с диагональю этого куба, идущей из общей точки трех ребер

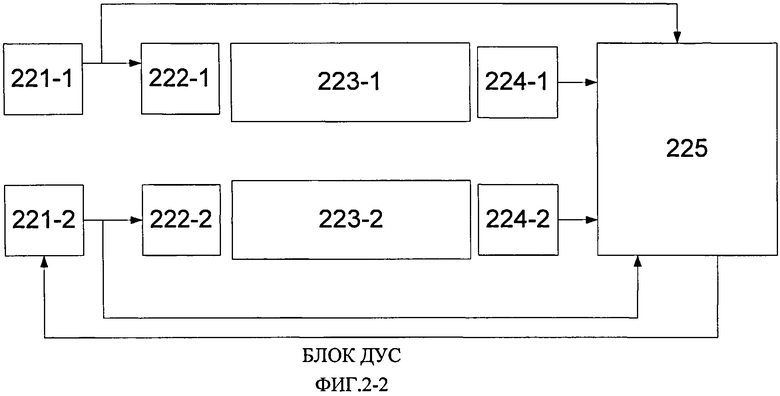

Каждый блок ДУС содержит чувствительный элемент (ЧЭ) грубого отсчета и ЧЭ точного отсчета расположенные на одной оси. Каждый ЧЭ этого датчика содержит перестраиваемый генератор частоты, подключенный выходом к передатчику оптическому и специализированному вычислительному устройству ЧЭ (СВУ ЧЭ), вход-выход которого является входом-выходом блока подключенным к соответствующему входу-выходу входящей в состав системы бортовой цифровой вычислительной системы (БЦВС). Выход передатчика оптического подключен к входу волокна оптического, выполненного в виде катушки, ось которой является осью чувствительности соответствующих ЧЭ и ДУС. К выходу волокна подключен приемник оптический, подключенный выходом к СВУЧЭ.

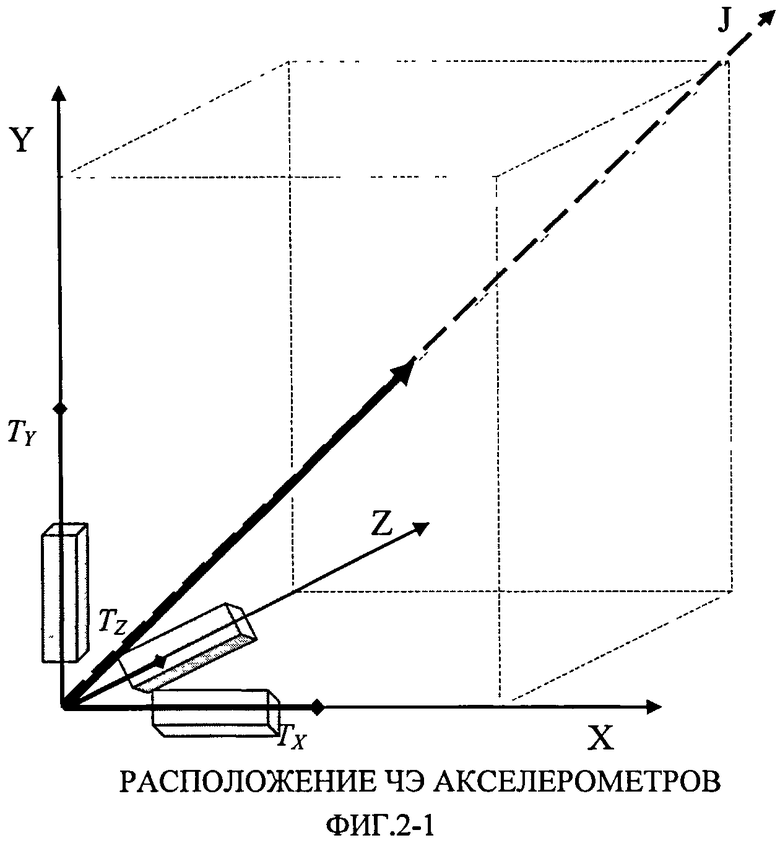

Кроме того система содержит трехканальный блок акселерометров (БА), конструктивно жестко связанный с конструкцией объекта управления с точной привязкой (фактически совпадающей с осями ДУС) осей чувствительности входящих в его состав трех чувствительных элементов акселерометра (ЧЭАК) первого, второго и третьего к осям блоков ДУС. Выход каждого ЧЭАК через свой соответственно первый, второй и третий акселерометрические динамические счетчики (АДС) подключены к входам специализированного вычислительного устройства акселерометра (СВУАК), вход-выход которого является входом-выходом канала ускорения и линейной скорости блока и подключен к одноименному входу-выходу БЦВМ.

Каждый ЧЭАК выполнен как генератор импульсов с кварцевым резонатором, являющимся чувствительным элементом. Основной (рабочий) срез кварцевого кристалла совпадает с осью чувствительности акселерометра. Оси акселерометров расположены по трем граням куба с общей вершиной (аналогично осям ДУС), а диагональ этого куба совпадает с основной осью изделия (осью тяги маршевого двигателя (двигателей)). Такое построение позволяет при правильной работе всех каналов блока использовать избыточную информацию для повышения точности, а при отказе одного из каналов его отказ обнаруживается СВУАК и БЦВМ. В результате используется информация одного из исправных каналов или их усреднено-взвешенное значение.

К входам БЦВМ кроме блока акселерометров подключены также входы-выходы блоков ДУС, а магистральные мультиплексные связи БЦВМ подключены к БЦВС верхнего уровня, с входящей в состав ее состав аппаратурой спутниковой навигации.

Кроме того предлагаемая БИНС содержит собственную подсистему электропитания (ПЭП), установочный вход которой подключен к установочному выходу БЦВМ, а синхронизирующие выходы и выходы постоянного и импульсного питания подключены соответствующим входам БЦВМ и других компонентов системы

БЦВМ реализована как многомашинная система с иерархическим управлением, в которой к трехканальному системному модулю через переключатель каналов (ПК) и дублированную общесистемную магистраль подключено несколько (n) вычислительных модулей (ВМ) и несколько (m) модулей связи (МС) для обмена по магистральным мультиплексным линиям, а также подключенные к общесистемной магистрали матричный вычислитель, таймер и запоминающее устройство с санкционированным доступом (ЗУСД). Кроме того в ее состав БЦВМ входит датчик внешнего воздействия (ДВВ), подключенный выходом к формирователю сигнала (ФС), подключенного выходом к блокирующему входу ЗУСД. Выходы каждого канала системного модуля подключены к входам ПК и блока контроля и управления (БКУ), выходы которого подключены к управляющим входам ПК.

Подсистема электропитания содержит первый и второй первичные источники энергии, подключенные выходами соответственно к первому и второму входам первого коммутатора и первой группе входов блока управления и контроля (БУК). Выходы первого коммутатора подключены к входам первого и второго аккумуляторов, выходы которых подключены ко второй группе входов БУК и соответственно к первому и второму входам второго коммутатора, выход которого подключен к силовому входу источника вторичного электропитания (ИВЭП), установочный вход которого объединен с установочным БУК и входом формирователя синхроимпульсов (ФСИ) и подключен к установочному выходу БЦВМ. Три управляющих выхода ФСИ являются одноименными входами ИВЭП, выходы постоянного и импульсного питания которого являются одноименными выходами ИВЭП и ПЭП в целом. К управляющим входам первого и второго коммутаторов подключены соответственно первая и вторая группа выходов БУК.

ИВЭП содержит модуль постоянного питания (МПП), установочный вход которого является одноименным входом ИВЭП и модуль импульсного питания (МИЛ), три управляющих входа которого являются одноименными входами ИВЭП, подключенными к ФСИ. Силовой вход модулей является силовым входом модулей, выходы постоянного и импульсного питания которых являются одноименными выходами ИВЭП и ПЭП в целом.

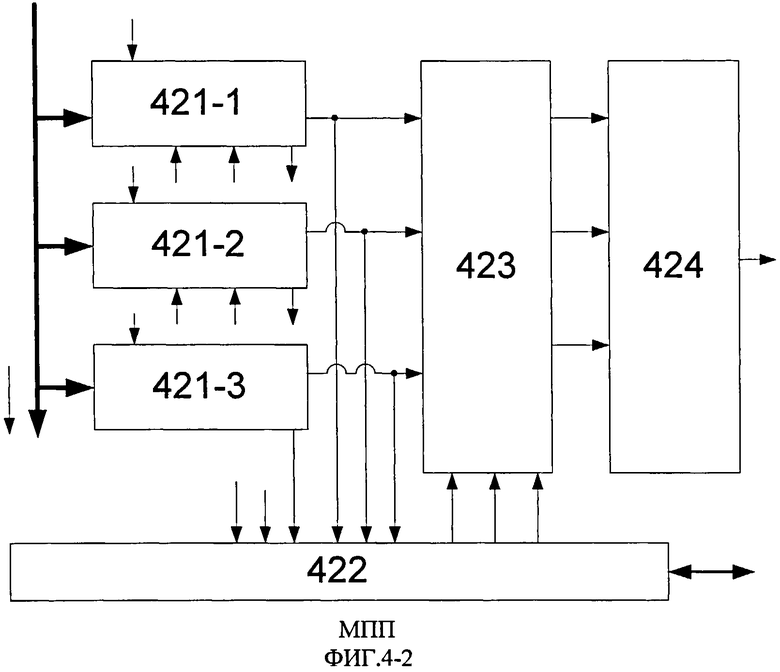

МПП содержит три идентичных конвертора (три канала), силовой и установочный вход каждого из которых является одноименным входом модуля и ИВЭП, а выходы конверторов подключены к контрольным входам модуля управления и контроля (МУК), к частотным входам которого подключены частотные выходы конверторов. Кроме того выходы конверторов к контрольным входам МУК и через блок отключения (БО) подключены и к входам блока выравнивания (БВ), выход которого является выходом ММП и выходом постоянного питания ИВЭП и подключен к дополнительному контрольному входу МУК, выходы которого подключены к управляющим входам БО.

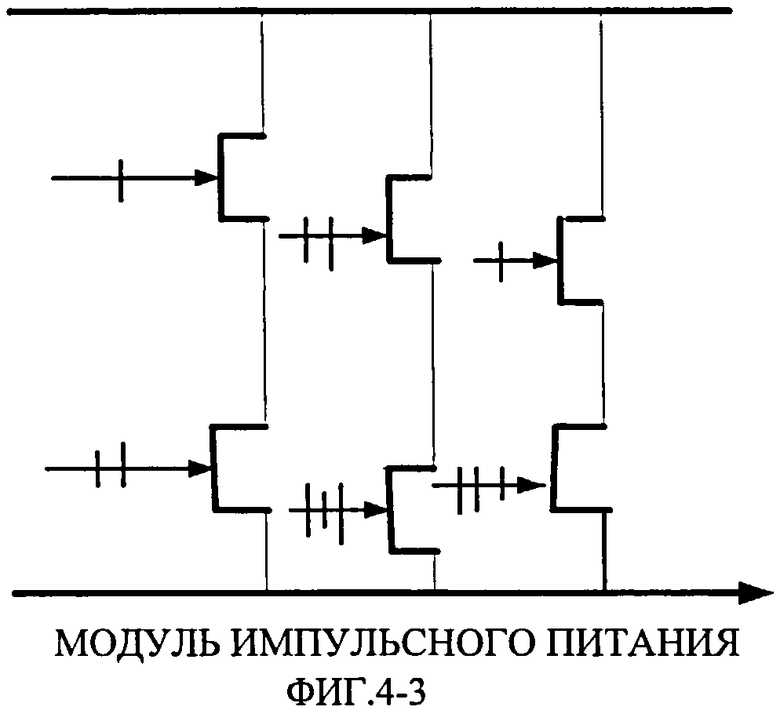

МИЛ содержит три идентичные ветви, объединенные с каждой из сторон. Одна их сторон является силовым входом, вторая - выходом. В каждой ветви установлены два последовательно соединенных полевых транзистора, а три входных управляющих сигнала разведены таким образом, что каждый из них подключен к затворам двух транзисторов, установленных в разных ветвях, образуя выборку «2 из 3».

Конвертор содержит последовательно включенные фильтр, вход которого является силовым входом конвертора, защитный диод, трансформатор с включенным в первичную обмотку транзистором-прерывателем, выпрямляющий диод во вторичной обмотке и выходной фильтр, выход которого является выходом конвертора и подключен к входу преобразователя напряжения в частоту. Выход этого преобразователя подключен к входу элемента развязки, выход которого является частотным выходом конвертора и подключен к входу частотно-импульсного модулятора (ЧИМ), установочный вход которого является установочным входом конвертора, а выход подключен к базе транзистора-прерывателя.

ДВВ выполнен как блокинг-генератор, к базе транзистора которого подключен обратносмещенный диод.

Формирователь сигнала содержит стабильный задающий генератор, подключенный выходом к входу таймерного счетчика. Выходы этого счетчика через таймерный дешифратор подключены к сбрасывающему входу триггера запрета, вход которого является входом формирователя, подключенным к ДВВ, и объединен с запускающим входом таймерного счетчика и входом логического элемента. Выход этого элемента является выходом формирователя, а к его запрещающему входу подключен выход дешифратора кода, подключенного входами к регистру кода санкционированного доступа, вход которого является установочным входом формирователя.

ЗУСД содержит первый и второй накопители, блокирующий вход которых является блокирующим входом запоминающего устройства, подключенным к выходу формирователя сигнала. К каждому накопителю первому и второму через свою соответственно первую и вторую временную двунаправленную связь подключен соответственно первый и второй сумматоры меток времени, входы которых являются входом метки времени запоминающего устройства. Кроме того к каждому накопителю первому и второму через свою соответственно первую и вторую массивную двунаправленную связь подключены соответственно первый и второй сумматоры массивов, вход - выход каждого их которых подключен к двунаправленной магистрали запоминающего устройства, к которой кроме того подключены информационные входы-выходы накопителей.

Каждый накопитель ЗУСД содержит энергонезависимый модуль памяти, параллельно шинам записи которого включен полевой транзистор со встроенным каналом, к базе которого подключен входной сигнал блокировки.

ВМ содержит блок процессора, к которому через первую и вторую двунаправленную связи подключены соответственно блок памяти и блок связи с магистралью, а установочный выход блока связи подключен к установочному входу блока синхронизации, выходы которого подключены к соответствующим входам всех блоков модуля.

МС содержит процессор, к которому через внутреннюю магистраль подключены запоминающее устройство и устройство связи по магистрали, входы-выходы которого являются входами-выходами модуля, а установочный выход устройства связи по магистрали подключен к установочному входу устройства синхронизации, выходы которого подключены к синхровходам процессора и устройств модуля. Вход-выход процессора через кодирующее-декодирующее устройство подключен к цифровому входу- выходу приемно-передающего устройства, вход-выход которого является мультиплексным магистральным входом выходом модуля связи.

Матричный вычислитель содержит матричный блок микропрограммного управления (МБМУ) со встроенным синхронизатором, подключенный установочным входом к матричному блоку связи по магистрали, два входа-выхода которого подключены к шинам системной магистрали.

Входы МБМУ подключены к управляющим входам первой и второй матриц нейропроцессоров (МНП), к которых каждый элемент матрицы является нейропроцессором, вычисляющим свою тригонометрическую функцию, например, sinx (cosx) или их произведение или алгебраическую функцию типа обратной величины, корня заданной степени и т.п.

Обе МНП через магистраль подключены к матричному блоку связи по магистрали и к арифметико-логическому устройству, вычисляющего сумму входных величин, как элемента результирующей матрицы произведения первой и второй МНП, элементы которой считываются в магистраль через матричный блок связи по магистрали.

Таймер содержит первый и второй формирователи точных интервалов, и дополнительный формирователь контрольного интервала. Выходы всех формирователей подключены к блоку выбора формирователя, а входы-выходы всех формирователей подключены к таймерному блоку связи по магистрали, два входа-выхода которого с другой стороны подключены к шинами системной магистрали БЦВМ.

Блок синхронизации, устройство синхронизации и синхронизатор выполнены аналогично друг другу и каждый содержит перестраиваемый генератор импульсов. Установочный вход генератора является установочным входом блока (устройства), а выход подключен к входу сдвигающего регистра, выход последнего разряда которого подключен к запускающему входу первого разряда этого регистра, а все выходы регистра являются синхронизирующими выходами блока (устройства).

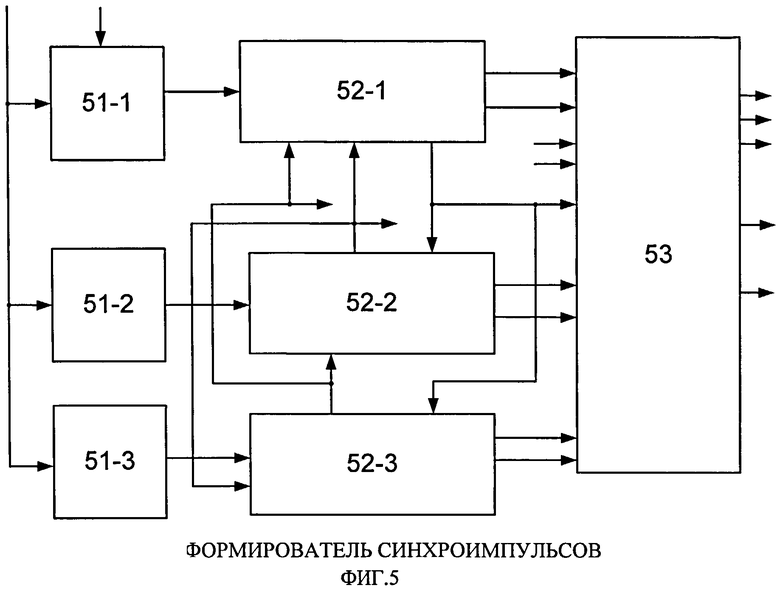

ФСИ содержит три генератора импульсов, первый второй и третий. Выход каждого из генераторов подключен к входу своего, соответственно первого второго и третьего блоков фазирования. Фазирующий выход каждого из блоков подключен к фазирующим входам двух других блоков и фазирующим входам блока мажоритации, к синхронизирующим входам которого подключены синхронизирующие выходы блоков фазирования. При этом выходы блока мажоритации являются выходами метки времени, трех управляющих сигналов и синхроимпульсов блока фазирования и ФСИ в целом.

Перестраиваемый генератор импульсов содержит группу последовательно включенных инверторов, выходы которых подключены к входам первого мультиплексора, выход которого является выходом генератора и подключен к входу первого инвертора группы и входу первого счетчика частоты. Выходы этого счетчика подключены к первым входам первой схемы сравнения, ко вторым входам которой подключены выходы первого регистра кода частоты. У этой схемы сравнения инкрементный и декрементный выходы подключены к одноименным входам первого счетчика кода частоты, выходы которого подключены к управляющим входам первого мультиплексора. При этом установочные входы первого регистра кода частоты и первого счетчика кода частоты являются установочным входом генератора.

Перестраиваемый генератор импульсов и генератор импульсов выполнены идентично друг другу.

Блок фазирования содержит элемент И, первый вход которого является входом блока, подключенным к выходу генератора импульсов, а выход элемента подключен к входу сдвигового регистра и входу выполненного на динамических триггерах динамического счетчика, выходы которого через дешифратор подключены к запускающему входу триггера останова, выход которого является фазирующим выходом блока и подключен ко второму входу элемента И, и первому входу мажоритарного элемента, ко второму и третьему входам которого подключены выходы триггеров привязки, стробирующий вход которых объединен с первым входом элемента И, а входы являются входами фазирования блока. Выход мажоритарного элемента подключен к входу триггера пуска, выход которого подключен к сбрасывающему входу триггера останова.

При этом четные и нечетные разряды сдвигового регистра подключены соответственно к запускающим и сбрасывающим входам триггеров формирователей, выходы которых являются синхронизирующими выходами блока и ФСИ в целом.

ЧИМ содержит несколько (n) последовательно включенных инверторов, выходы которых подключены к входам второго мультиплексора. Выход этого мультиплексора подключен к входу первого инвертора. Кроме того, модулятор содержит второй счетчик частоты, вход которого является входом модулятора, подключенного к выходу элемента развязки. Выходы второго счетчика частоты подключены к первым входам второй схемы сравнения, ко вторым входам которой подключены выходы второго регистра кода частоты. При этом инкрементный и декрементный выходы второй схемы сравнения подключены к одноименным входам второго счетчика кода частоты, выходы которого подключены к управляющим входам второго мультиплексора. Установочные входы второго регистра кода частоты и второго счетчика кода частоты являются установочным входом модулятора.

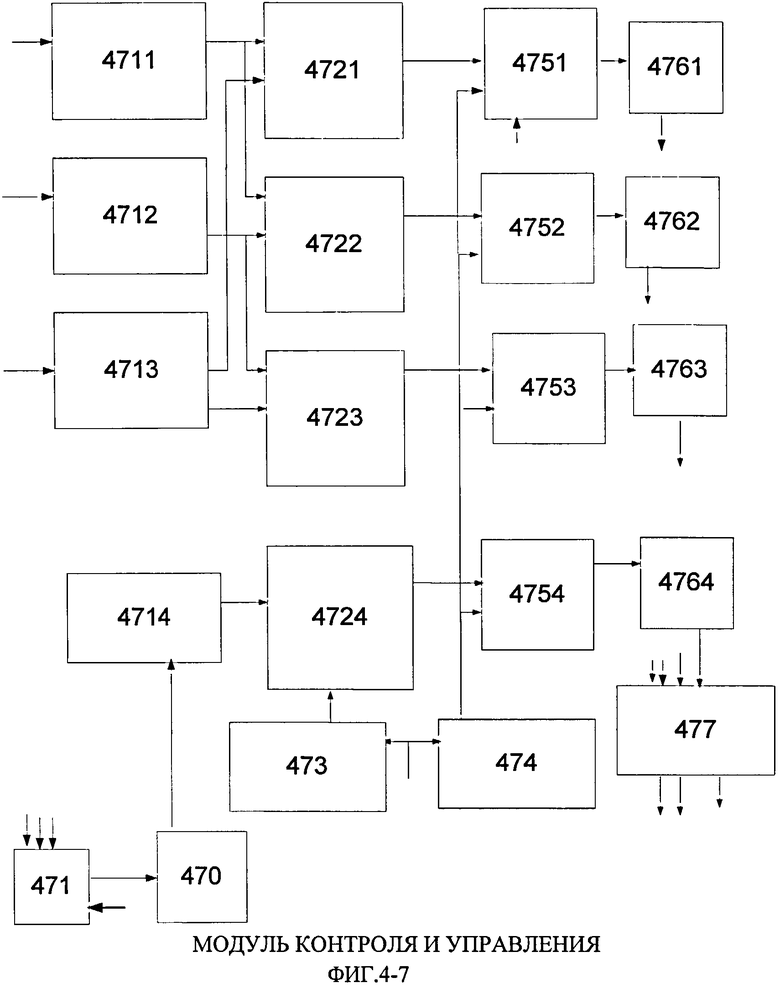

Модуль контроля и управления содержит первый, второй, третий и четвертый частотные счетчики. Входы первых трех из них являются частотными входами модуля и подключены к частотным выходам соответственно первого, второго и третьего конверторов. Вход четвертого счетчика подключен к выходу устройства преобразования напряжения в частоту, к входу которого подключен выход аналогового мультиплексора. К входам аналогового мультиплексора подключены выходы всех конверторов, а к дополнительному входу подключен выход блока выравнивания. Выход первого счетчика подключен к первым входам первого и второго сумматоров, выход второго счетчика подключен ко второму входу первого сумматора и первым входам второго и третьего сумматоров, а выход третьего счетчика подключен ко вторым входам первого и третьего сумматоров. Выход четвертого счетчика подключен к первому входу четвертого сумматора, ко второму входу которого подключен выход регистра кода, вход которого является установочным входом модуля и объединен с входом регистра допуска. Выход регистра допуска подключен к первым входам первой, второй, третьей и четвертой схем совпадения, ко вторым входам которых подключены выходы соответственно первого, второго, третьего и четвертого сумматоров. При этом выход каждой схемы совпадения первой, второй, третьей и четвертой подключен к входу своего триггера неисправности, соответственно первого второго, третьего и четвертого, выходы которых подключены к входам группы логических схем, выходы которой являются выходами модуля.

Датчик внешнего воздействия выполнен как блокинг-генератор, к базе транзистора которого подключен обратносмещенный диод.

Формирователь сигнала содержит задающий генератор, подключенный выходом к интервальному счетчику, выходы которого через интервальный дешифратор подключены к сбрасывающему входу триггера блокировки, запускающий вход которого объединен с разрешающим входом интервального счетчика, входом логического элемента и является входом формирователя, подключенного к выходу датчика внешнего воздействия. Выход этого элемента является выходом формирователя, установочный вход которого подключен к входу регистра санкционированного кода, выходы которого через санкционированный дешифратор подключены к запрещающему входу логического элемента.

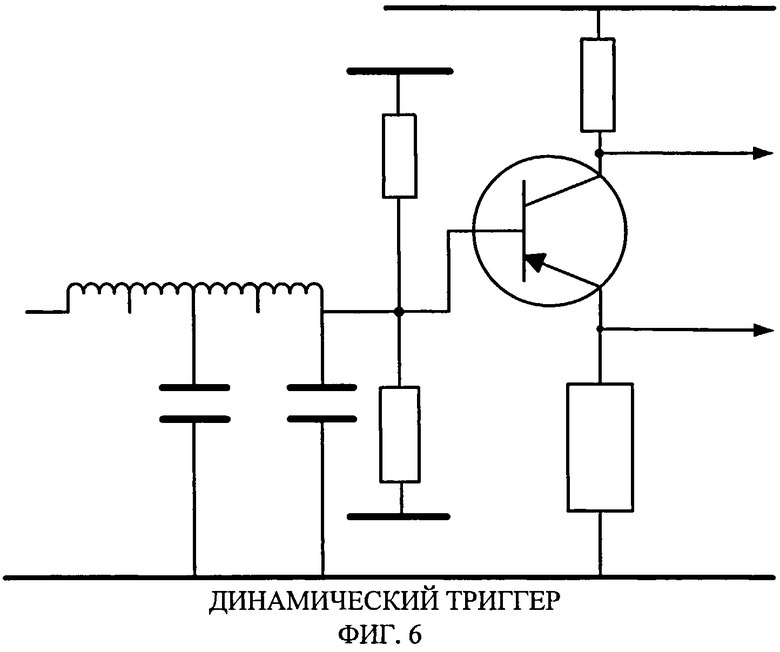

Динамический триггер выполнен как транзисторный усилитель, к базе транзистора которого подключен резисторный делитель, задающий рабочую точку, и выполняющая роль элемента памяти LC цепь. Индуктивность этой цепи имеет рабочую обмотку и намотанную поверх рабочей компенсационную. Концы компенсационной обмотки для подавления внешних электромагнитных наводок закорочены

Чертежи, содержащие состав системы и входящих компонентов приведены на фигурах с 1-ой по 8.

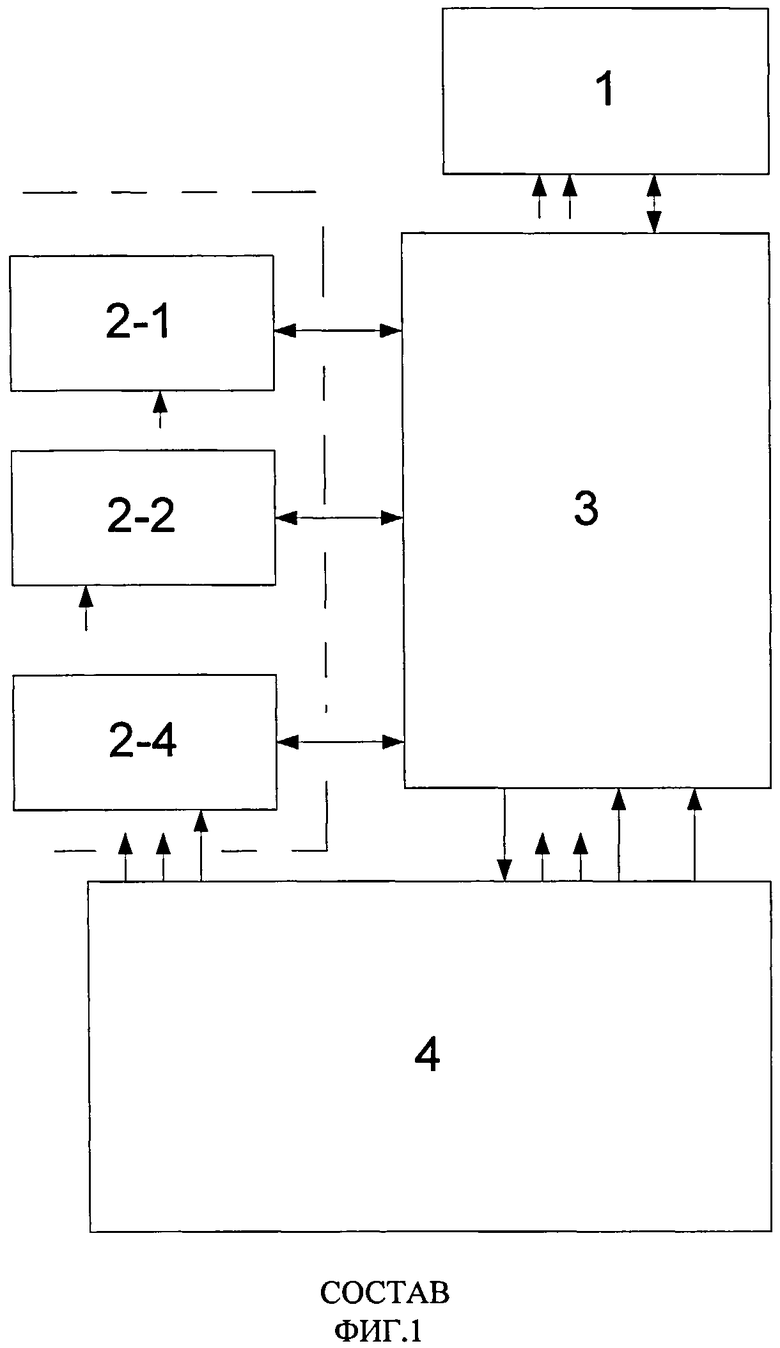

Состав системы приведен на фигуре 1. Здесь цифрой 1 обозначен блок акселерометров, цифрами с 2-1 по 2-4 обозначены блоки ДУС. Цифрой 3 обозначена БЦВМ и цифрой 4 обозначена подсистема электропитания.

На фигуре 2 приведено расположение блоков ДУС, а на фигуре 2-1 приведено расположение ЧЭ акселерометров.

На фигуре 2-2 приведен блок ДУС, где цифрами 221-1 и 221-2 обозначены соответственно генераторы частоты грубого и точного отсчета, цифрами 222-1 и 222-2 обозначены соответственно передатчики оптические грубого и точного отсчета, цифрами 223-1 и 223-2 обозначены оптические волокна, соответственно грубого и точного отсчета. Цифрами 224-1 и 224-2 приемники оптические соответственно грубого и точного отсчета и цифрой 225 обозначено СВУ ДУС.

На фигуре 2-3 приведен блок акселерометров. Здесь цифрами от 230-1 до 230-3 обозначены кварцевые задающие генераторы первого, второго и третьего канала акселерометров, цифрами от 231-1 до 231-3 обозначены соответствующие каждому каналу АДС и цифрой 232 обозначено СВУАК.

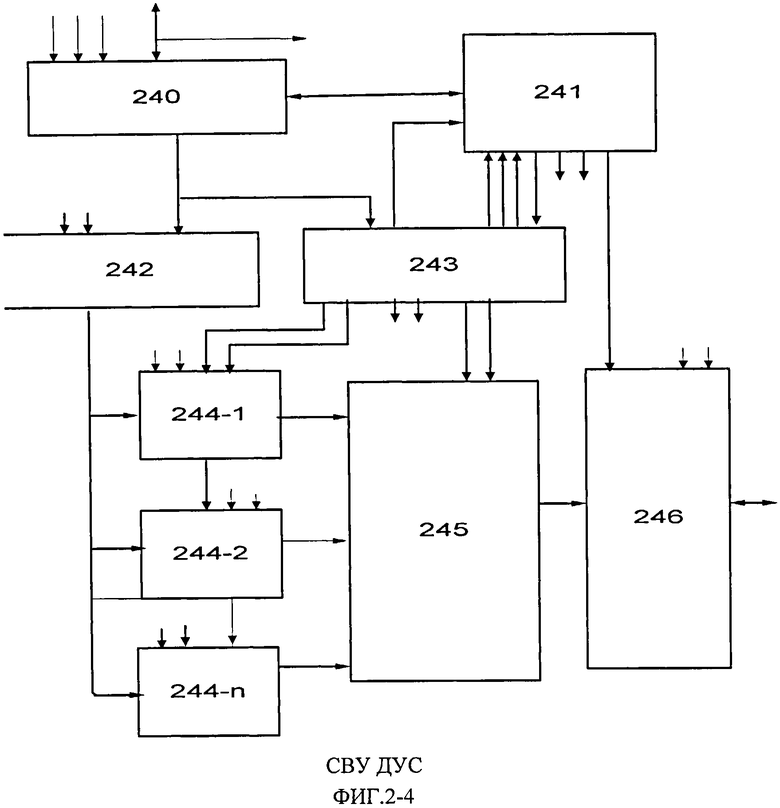

На фигуре 2-4 приведено СВУ ДУС. Здесь цифрой 240 обозначен микропроцессор, цифрой 241 - первое специализированное запоминающее устройство, цифрой 242 обозначен первый буферный регистр, цифрой 243 обозначен первый блок микропрограммного управления. Цифрами от 244-1 до 244-n обозначены умножители. Цифрой 245 обозначено арифметико-логическое устройство и цифрой 246 обозначено устройство связи.

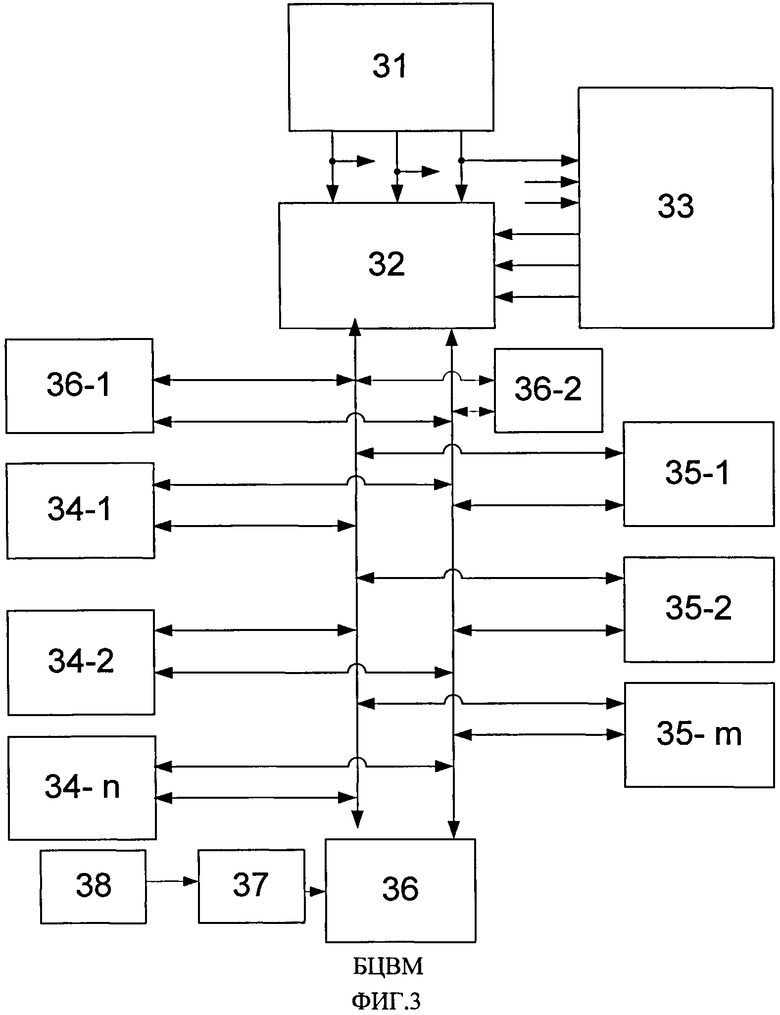

На фигуре 3 приведена БЦВМ. Здесь цифрами 31 обозначен системный модуль, цифрами 32 - переключатель каналов. Цифрами 33 обозначен БКУ. Цифрами от 34-1 до 34-n обозначены вычислительные модули. Цифрами от 35-1 до 35-m обозначены модули связи. Цифрами 36 обозначено ЗУСД, цифрами 36-1 и 36-2 обозначены соответственно таймер и матричный вычислитель. Цифрами 37 обозначен формирователь сигнала и цифрами 38 обозначен ДВВ.

ЗУСД приведено на фигуре 3-1, где цифрами 311 и 312 обозначены соответственно первый и второй накопители. Цифрами 313-1 и 313-2 обозначены соответственно первый и второй сумматоры метки времени, а цифрами 314-1 и 314-2 обозначены соответственно первый и второй сумматоры массивов.

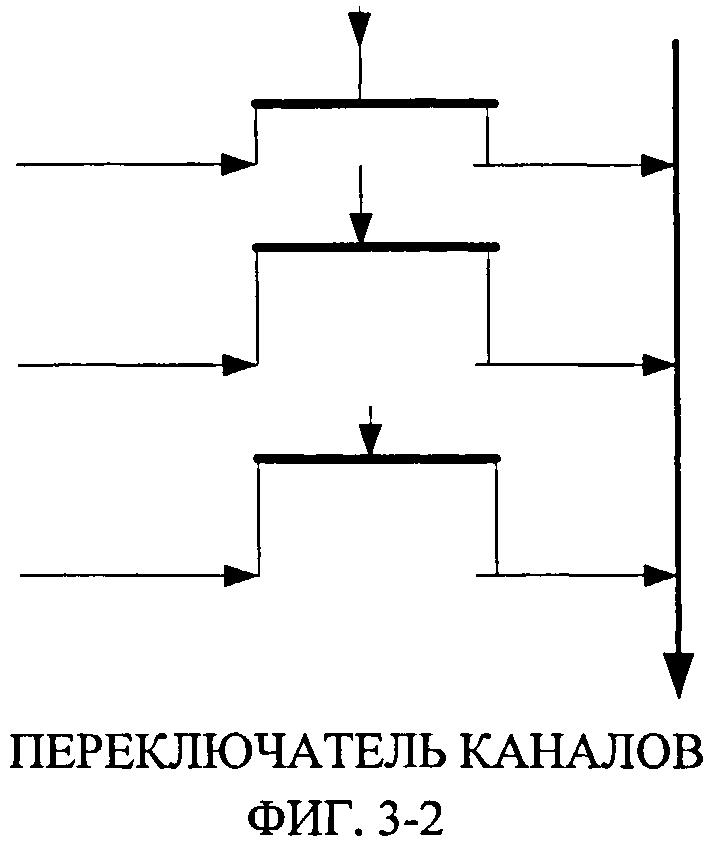

Переключатель каналов приведен на фигуре 3-2.

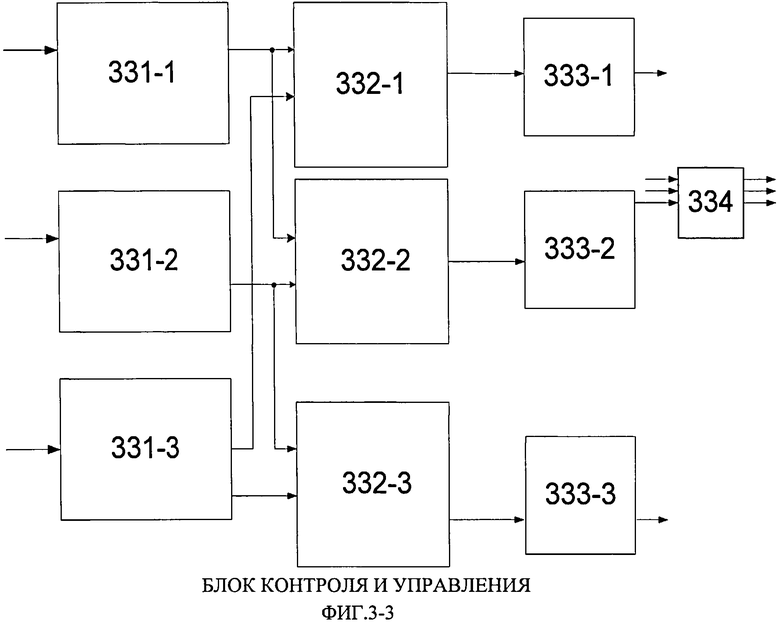

На фигуре 3-3 приведен блок контроля и управления, где цифрами от 331-1 до 331-3 обозначены соответственно первый, второй и третий входные регистры. Цифрами от 332-1 до 332-3 обозначены соответственно первый, второй и третий узлы сравнения. Цифрами от 333-1 до 333-3 обозначены соответственно триггеры ошибок и цифрой 334 обозначены логические схемы.

Вычислительный модуль приведен на фигуре 3-4. Здесь цифрами 340 обозначен блок процессора, цифрами 341 - блок ЗУ, цифрами 342 обозначен блок синхронизации и цифрами 343 обозначен блок связи.

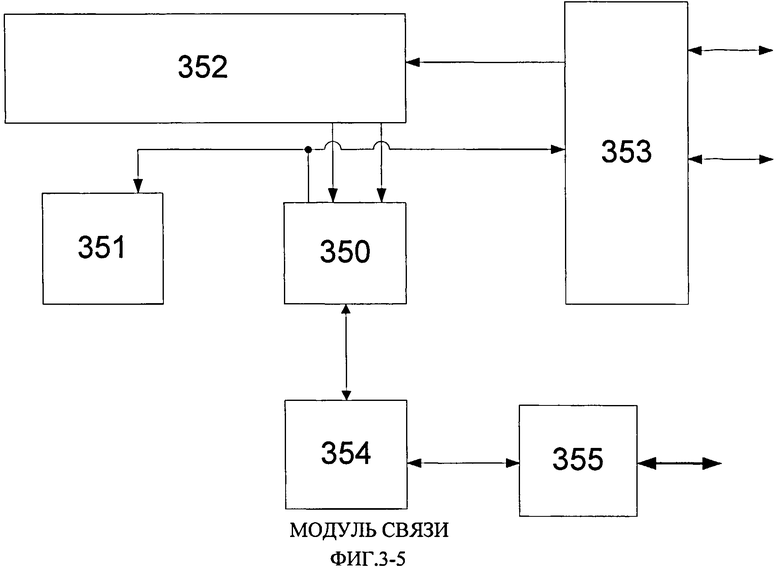

Модуль связи приведен на фигуре 3-5. Здесь цифрами 350 обозначен процессор, цифрами 351 - запоминающее устройство, цифрами 352 обозначено устройство синхронизации. Устройство связи обозначено цифрами 353 и цифрами 354 и 355 обозначены соответственно кодирующее-декодирующее устройство и приемно-передающее устройство.

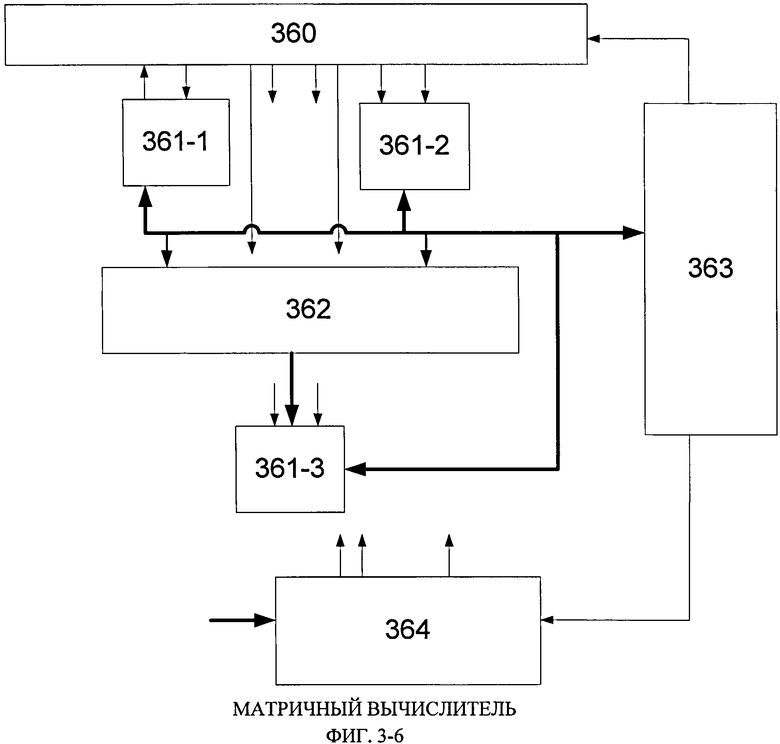

На фигуре 3-6 приведен матричный вычислитель. Здесь цифрами 360 обозначен матричный блок микропрограммного управления. Цифрами 361-1 и 361-2 обозначены соответственно первый и второй матричные блоки нейропроцессоров, цифрами 361-3 обозначено матричное запоминающее устройство и цифрами 362 и 363 обозначены соответственно матричное арифметико-логическое устройство и матричный блок связи по магистрали. Цифрами 364 обозначен блок синхронизации

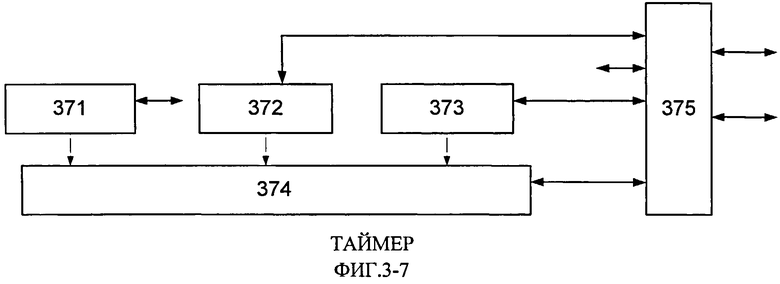

На фигуре 3-7 приведен таймер. Здесь цифрами 371, 372 и 373 обозначены соответственно первый, второй и контрольный формирователи интервалов. Цифрами 374 - устройство сравнения и цифрами 375 обозначено устройство связи по магистрали.

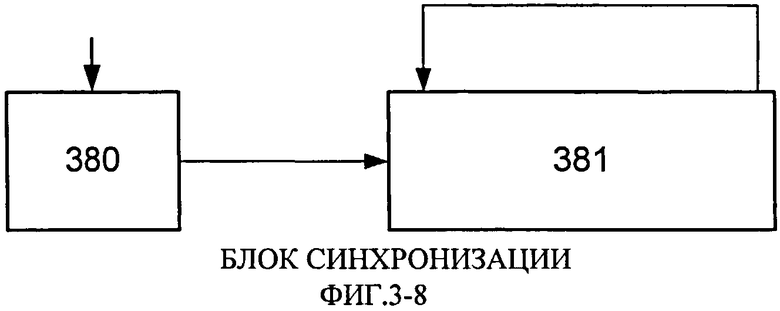

На фигуре 3-8 приведен блок синхронизации, где цифрами 380 и 381 обозначены соответственно перестраиваемый генератор импульсов и сдвиговый регистр.

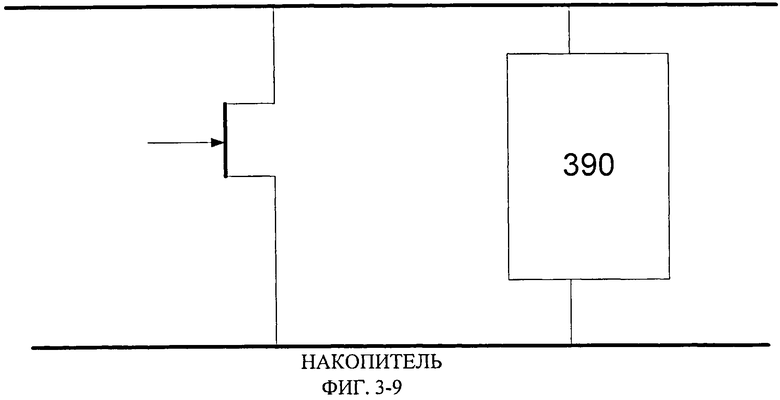

На фигуре 3-9 приведен накопитель, где цифрами 390 обозначен энергонезависимый модуль памяти.

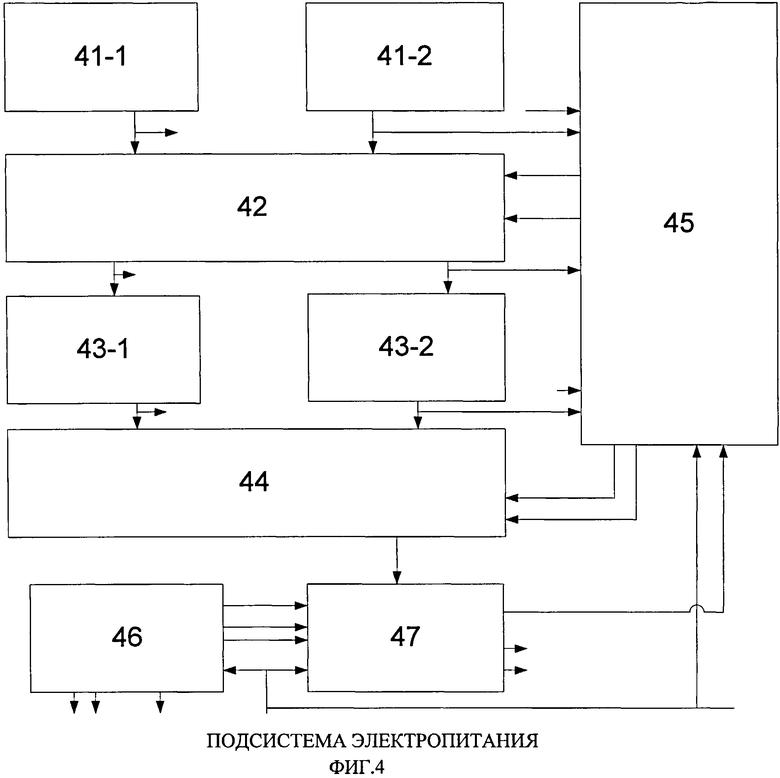

На фигуре 4 приведена ПЭП, Здесь цифрами 41-1 и 41-2 обозначены соответственно первый и второй первичные источники. Цифрами 42 обозначен первый коммутатор, Цифрами 43-1 и 43-2 обозначены соответственно первый и второй аккумуляторы, цифрами 44 обозначен второй коммутатор, цифрами 45 - БУК и цифрами 46 и 47 обозначены соответственно ФСИ и ИВЭП.

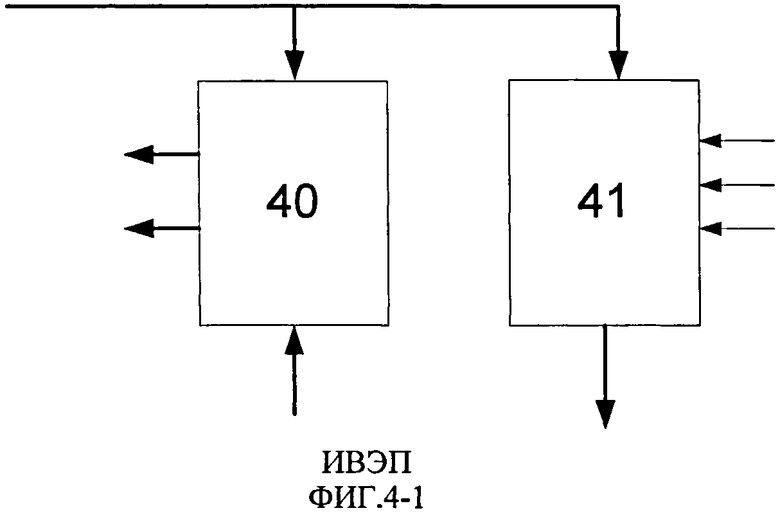

На фигуре 4-1 приведен ИВЭП, где цифрами 40 и 41 обозначены соответственно МПП и МИЛ.

МПП приведен на фигуре 4-2. Здесь цифрами 421-1, 421-2 и 421-3 обозначены первый, второй и третий конверторы, цифрами 422 - МКУ и цифрами 423 и 424 обозначены соответственно блок отключения и блок выравнивания.

МИЛ приведен на фигуре 4-3.

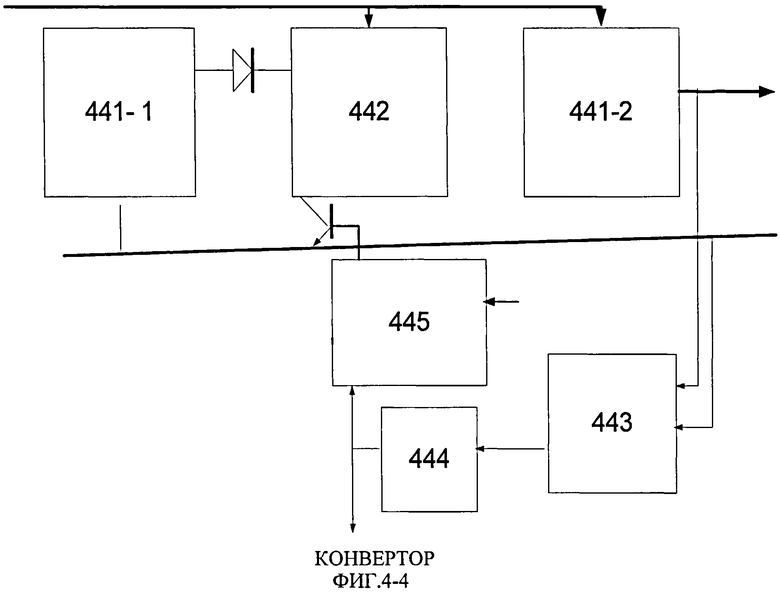

На фигуре 4-4 приведен конвертор. Здесь цифрами 441-1 и 441-2 обозначены соответственно фильтр и выходной фильтр. Цифрами 442 обозначен трансформатор, цифрами 443 обозначен преобразователь напряжения в частоту, цифрами 444 - элемент развязки и цифрами 445 обозначен ЧИМ.

ЧИМ приведен на фигуре 4-5. Здесь цифрами 451 обозначена группа инверторов, цифрами 452 - второй мультиплексор. Цифрами 453 обозначен второй счетчик кода частоты, цифрами 454 - второй счетчик частоты и цифрами 455 и 456 обозначены соответственно вторая схема сравнения и второй регистр кода частоты.

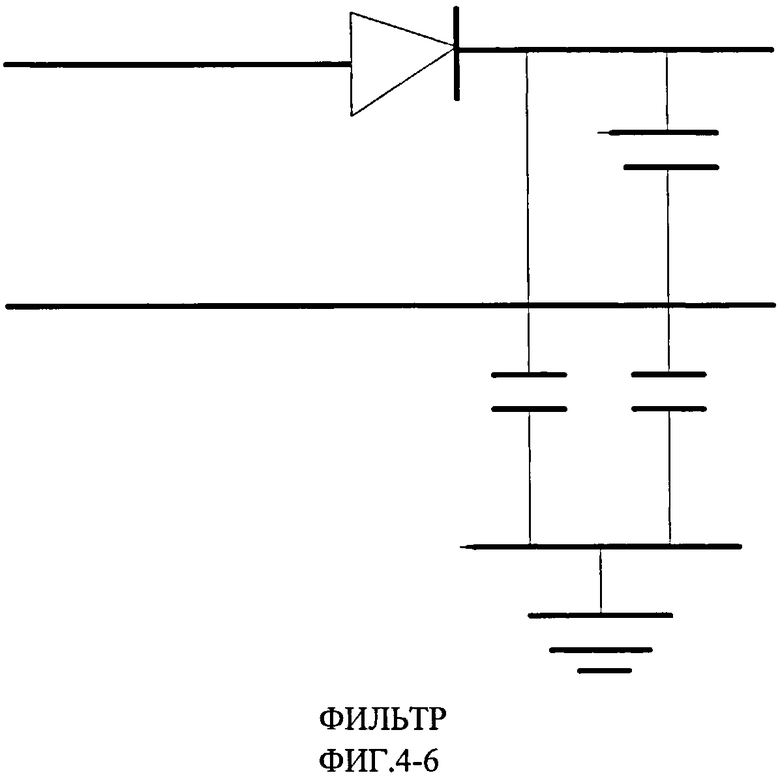

Фильтр приведен на фигуре 4-6.

На фигуре 4-7 приведен МКУ. Здесь цифрами 470 обозначено устройство преобразования напряжения в частоту, цифрами 471 - аналоговый мультиплексор. Цифрами от 4711 до 4714 обозначены, соответственно первый, второй, третий и четвертый счетчики частоты. Цифрами от 4721 до 4724 обозначены, соответственно первый второй, третий и четвертый сумматоры. Цифрами 473 и 474 обозначены, соответственно регистр кода и регистр допуска. Цифрами от 4751 до 4754 обозначены, соответственно первая, вторая третья и четвертая схемы совпадения. Цифрами от 4761 до 4764 обозначены соответственно первый, второй, третий и четвертый триггеры неисправности и цифрами 477 обозначена группа логических схем.

На фигуре 5 приведен ФСИ, где цифрами 51-1, 51-2 и 51-3 обозначены, соответственно первый, второй и третий генераторы импульсов. Цифрами 52-1, 52-2 и 52-3 обозначены соответственно первый, второй и третий блоки фазирования и цифрами 53 обозначен блок мажоритации.

Перестраиваемый генератор импульсов приведен на фигуре 5-1, где цифрами 510 обозначены n инверторов, цифрами 511 - первый мультиплексор. Цифрами 512 обозначен первый счетчик кода частоты. Цифрами 513 обозначена первая схема сравнения. Цифрами 514 и 515 обозначены соответственно первый счетчик частоты и первый регистр кода частоты.

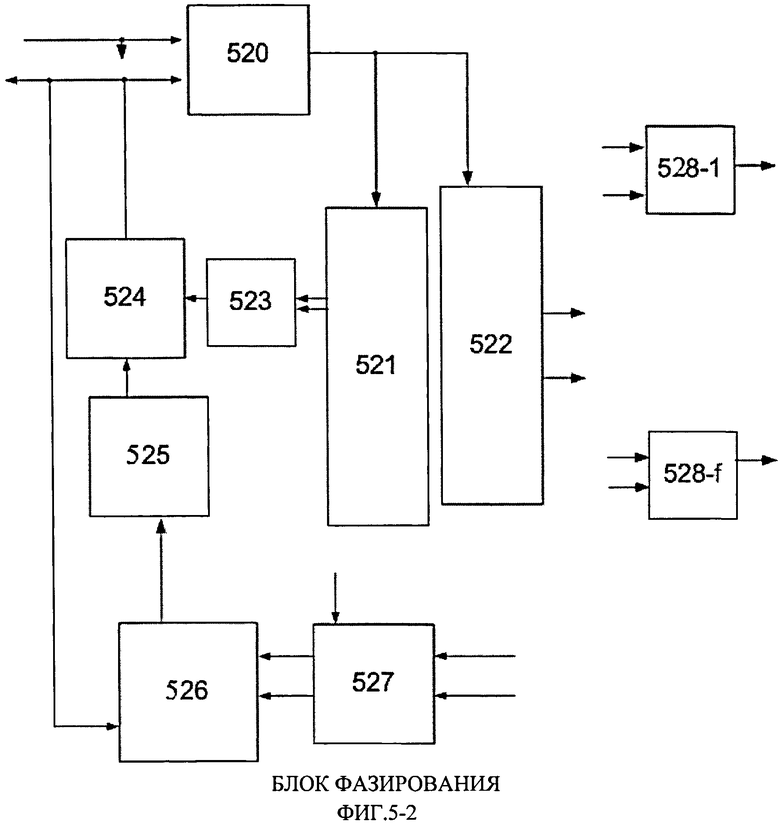

Блок фазирования приведен на фигуре 5-2. Здесь цифрами 520 обозначен элемент И, цифрами 521 и 522 обозначены соответственно динамический счетчик и сдвиговый регистр. Цифрами 523 обозначен дешифратор, цифрами 524 - триггер останова и цифрами 525 - триггер пуска. Цифрами 526 и 527 обозначены соответственно элемент мажоритации и триггеры привязки и цифрами от 528-1 до 528-f обозначены триггеры формирователи.

Динамический триггер приведен на фигуре 6.

Датчик внешнего воздействия приведен на фигуре 7.

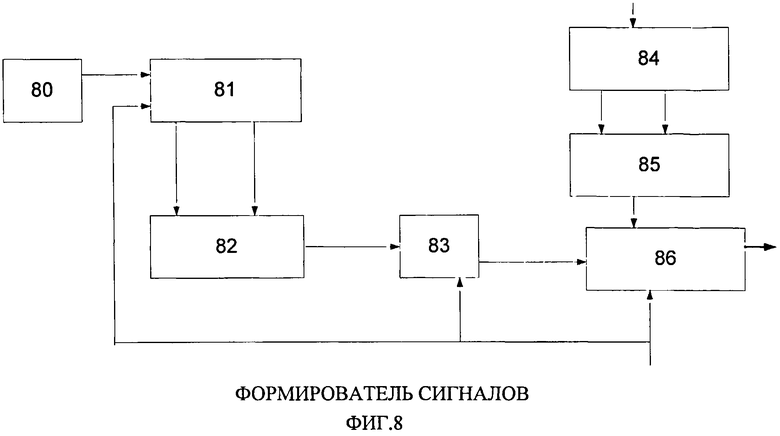

Формирователь сигналов приведен на фигуре 8. Здесь цифрами 80 обозначен задающий генератор, цифрами 81 - интервальный счетчик, цифрами 82 обозначен интервальный дешифратор, цифрой 83 обозначен триггер запрета, цифрами 84 и 85 обозначены соответственно регистр кода и дешифратор кода и цифрами 86 обозначен логический элемент.

Система может быть реализована следующим образом:

ЧЭ ДУС реализуется на основе перестраиваемого задающего генератора, выполненного в виде БИС на основе БМК сер. 537ХМ2 изготавливаемого в производстве АО «Ангстрем». В качестве передатчика оптического используется передатчик типа HFBR2522Z или его аналог.

Волокно оптическое можно использовать типа HFBR-RNS 003 и HFBR-RU 100 или их аналоги.

В качестве приемника оптического используется приемник HFBR-1522Z или его аналог.

СВУ реализуются в виде изготавливаемой в производстве НПОА многокристальной сборки специализированных БИС на основе БМК сер. 5516, 5517 и 537, изготавливаемых в производстве АО «Ангстрем».

ЧЭАК изготавливается на основе кварцевого задающего генератора, изготавливаемого в производстве НПОА и многокристальной сборки, изготавливаемой также в производстве НПОА с использованием специализированных БИС на основе БМК сер. 1556 и 1557 и БИС запоминающих устройств сер. 1620, изготавливаемых АО «Ангстрем».

В ПЭП в качестве первичных источников энергии используются химические источники тока (ампульные батареи или созданные в последнее время радиоизотопные теплоэлектрогенераторы (РИТЕГ)). Коммутаторы реализуются на основе полевых транзисторов большой мощности.

БУК, БКУ, МКУ реализуется на специализированных БИС на основе БМК сер. 1556 и 1567.

ИВЭП реализуется на дискретных элементах и планарных трансформаторах, изготавливаемых в производстве НПОА. Для реализации преобразователя напряжения в частоту и устройства преобразования напряжения в частоту используется микросхема 1108ПП1 или ADFC32 фирмы Analog Devisee или их аналоги.

БЦВМ реализуется в виде многокристальных сборок, изготавливаемых в производстве НПОА на основе БИС микропроцессорного комплекта сер. 1825 и 1620, дополненных БИС на основе БМК сер. 1556 и 1557, изготавливаемых АО «Ангстрем».

ДВВ и динамический триггер реализуются на основе транзистора типа П16, с дискретными элементами (резисторы и конденсаторы) и моточные изделиями, изготавливаемыми в производстве НПОА.

Формирователь сигнала реализуется в виде БИС на основе БМК сер. 1556. ЗУСД реализуется на дискретных элементах и цилиндрических тонких магнитных пленках, дополненных электроникой на основе бескорпусных элементов, транзисторов, резисторов и конденсаторов, устанавливаемых в многокристальные сборки, изготавливаемые в НПОА.

Система работает следующим образом:

Перед началом работы по командам, поступающим из БЦВС верхнего уровня, задействуются первичные источники энергии и вводятся исходные данные (рабочее (полетное) задание) в БЦВМ системы. БЦВМ в свою очередь задает режим работы введением уставок во все СВУ, ФСИ и ИВЭП.

В процессе работы системный модуль периодически переводит вычислительные модули и модули связи в режим тестовых проверок, по результатам которых определяется наличие в них катастрофических отказов и работоспособность модулей на текущей частоте перестраиваемых генераторов импульсов их блоков синхронизации и устройств синхронизации. Если модули работоспособны, то уставки на код частоты генератора изменяются в сторону увеличения до нахождения предельно возможного быстродействия при текущем наборе дозы от ионизирующего излучения. В противном случае частота снижается. Этими действиями системного модуля помимо контроля и выбора исправных модулей для решения задач обеспечивается подбор частоты синхронизации модулей, соответствующей текущему быстродействию входящих в их состав полупроводниковых элементов. Это позволяет продлить работоспособность модулей при деградации параметров полупроводниковых элементов при наборе большой дозы от ионизирующего излучения и повысить производительность БЦВМ на начальном этапе наборе дозы. Аналогичные действия выполняет БЦВМ по отношению к СВУ, входящим в состав блоков ДУС и блока акселерометров, для чего в составе входящих в них блоков микропрограммного управления введены перестраиваемые генераторы импульсов (частоты).

Таким образом, введение в состав системы четырех блоков ДУС с собственным специализированным вычислительным устройством, работающим как предпроцессор в многомашинной магистрально-модульной БЦВМ позволяет не только реализовать полноценную трехкоординатную инерциальную систему, в которой при исправной работе всех блоков ДУС обеспечивается повышение точности вычислений системы координат, а при отказе одного из блоков три оставшиеся блока обеспечивают БЦВМ информацией, достаточной для точного вычисления и поддержания трехкоординатной инерциальной системы. Наличие трех независимых ЧЭ в блоке акселерометров позволяет при их правильной работе повысить точность вычислений ускорений, скорости перемещения и пространственных координат центра масс изделия (объекта), а при возникновении отказов в одном из ЧЭ блока акселерометров используется информация оставшихся исправными ЧЭ, вплоть до последнего исправного ЧЭ, для выбора которого БЦВС верхнего уровня проводит тестовые маневры объекта, позволяющие достоверно (с определенной вероятностью) выбрать работоспособный ЧЭ блока.

Наличие ЗУСД с ДВВ и формирователем сигнала блокировки позволяет восстановить работоспособность БЦВМ а с ее помощью и всех СВУ после сбоев, вызванных тяжелыми заряженными частицами космического пространства, вспышками на солнце и даже направленном противодействии, а использование качественных радиационно-стойких элементов серий 1825, 1620, 1556, 1557 и 537ХМ2 с перестройкой быстродействия вычислителей обеспечивает радиационную стойкость при длительной работе в полях ионизирующего излучения космического пространства и загрязненной местности.

Наличие резерва всех основных компонентов системы с организацией оперативного аппаратурного контроля и периодических тестовых проверок обеспечивают сохранение работоспособности системы при возникновении одной возможной неисправности, вызванной фактором времени или попаданием высокоэнергетической тяжелой заряженной частицы в активную зону полупроводника в любом из элементов системы, а введение перестройки частоты задающих генераторов позволяет нейтрализовать или использовать для повышения производительности параметрические уходы цифровых БИС, вызванные изменением параметров полупроводниковых структур из-за дозовых накоплений от действия ионизирующего излучения.

БИНС

1 СОСТАВ

2 РАСПОЛОЖЕНИЕ БЛОКОВ ДУС

2-1 РАСПОЛОЖЕНИЕ АК

2-2 БЛОК ДУС=ЧЭГО+ЧЭ ТО

2-3 БЛОК АКСЕЛ=З КЗГ+З АДС+СВУ АК

2-4 СВУ ДУС

3 БЦВМ

3-1 ЗУСД//3-11 НАКОПИТЕЛЬ

3-2 ПК

3-3 БКУ

3-4 ВМ

3-5 МС

3-6 МАТР ВЫЧИСЛ

3-7 ТАЙМЕР

4 ПЭП

4-1 ИВЭП

4-2 МПП

4-3 МИП

4-4 КОНВЕРТОР

4-5 ЧИМ

4-6 ФИЛЬТР

4-7 БУК

5 ФСИ

5-1 ГИ

5-2 БЛ. ФАЗИР

6 ДТ

7 ДВВ

8 ФС

| название | год | авторы | номер документа |

|---|---|---|---|

| СИСТЕМА АСТРОНАВИГАЦИИ | 2013 |

|

RU2548927C1 |

| НЕЙРОВЫЧИСЛИТЕЛЬ | 2013 |

|

RU2553098C2 |

| СИСТЕМА УПРАВЛЕНИЯ КОСМИЧЕСКОГО АППАРАТА | 2013 |

|

RU2560204C2 |

| МАГИСТРАЛЬНО-МОДУЛЬНАЯ ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 2013 |

|

RU2564626C2 |

| ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 2013 |

|

RU2536434C2 |

| СБОЕУСТОЙЧИВАЯ ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 2013 |

|

RU2541839C2 |

| СИСТЕМА АВТОМАТИЧЕСКОГО УПРАВЛЕНИЯ | 2013 |

|

RU2534955C1 |

| ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО БИНС | 2011 |

|

RU2469376C1 |

| КОНТРОЛЛЕР ПЕРЕДАЧИ ДАННЫХ | 2013 |

|

RU2514135C1 |

| МОДЕЛИРУЮЩИЙ КОАП | 2013 |

|

RU2516703C1 |

Изобретение относится к системам автоматического управления (САУ) и может быть использовано в САУ, работающих в экстремальных условиях и полях ионизирующего излучения. Технический результат - расширение функциональных возможностей. Для этого бесплатформенная инерциальная навигационная система (БИНС) содержит блок акселерометров из трех акселерометров (АК), размещенных по осям, совпадающим с гранями условного куба, исходящими из одной вершины, причем диагональ этого куба, исходящая из той же вершины совпадает с основной осью объекта управления (осью тяги двигателя). Выходы всех акселерометров подключены к входам специализированного вычислительного устройства (СВУ), результаты обработки информации всех АК передаются из него в бортовую цифровую вычислительную машину (БЦВМ), которая осуществляет обработку информации СВУ блока датчиков угловой скорости. СВУ содержит четыре датчика угловой скорости (ДУС), оси чувствительности трех из которых расположены по осям, совпадающим с гранями куба, исходящими из одной вершины, а ось четвертого совпадает с диагональю этого куба. При этом система содержит подсистему электропитания (ПЭП), которая выполнена в резервированном варианте со встроенным блоком контроля работы ее блоков и управлением резервом. 29 з.п. ф-лы, 30 ил.

1. Бесплатформенная инерциальная система, содержащая датчик угловой скорости с чувствительным элементом точного отсчета и три акселерометра, отличающаяся тем, что акселерометры объединены в блок акселерометров, подключенный входом-выходом к бортовой цифровой вычислительной машине, а на ось чувствительности датчика угловой скорости к чувствительному элементу точного отсчета установлен чувствительный элемент грубого отсчета, составившие вместе с подключенными к каждому чувствительному элементу счетчиками частоты соответственно точного и грубого отсчета датчик угловой скорости, расположенный по оси, совпадающей с одной из граней условного куба, на двух других осях, совпадающих с двумя другими, смежными гранями куба, исходящими из одной вершины куба, установлено еще по одному датчику угловой скорости, а четвертый датчик угловой скорости расположен на оси, совпадающей с диагональю условного куба, причем выходы всех счетчиков подключены к входам специализированного вычислительного устройства угловой скорости, составляющего совместно с датчиками угловой скорости блок датчиков угловой скорости, подключенный входом-выходом к бортовой цифровой вычислительной машине, входы питания и синхронизации которой, а также входы питания и синхронизации блока акселерометров и блока датчиков угловой скорости подключены к одноименным выходам подсистемы электропитания, установочный вход которой подключен к выходу бортовой цифровой вычислительной машины.

2. Система по п. 1, отличающаяся тем, что блок датчиков угловой скорости содержит четыре датчика угловой скорости, подключенные выходами к входам специализированного вычислительного устройства угловой скорости, вход-выход которого является входом-выходом блока, при этом оси чувствительности трех датчиков расположены по осям, совпадающим с тремя ортогональными гранями условного куба, исходящими из одной вершины, а ось чувствительности четвертого датчика совпадает с диагональю условного куба, исходящей из той же вершины

3. Система по п. 1, отличающаяся тем, что блок акселерометров содержит первый, второй и третий акселерометры, оси чувствительности каждого из которых совпадают с одной из трех исходящих из одной вершины ортогональных граней условного куба, исходящая из той же вершины диагональ которого совпадает с основной осью (осью тяги двигателя) объекта управления, на который установлена система, причем выход каждого акселерометра подключен к входу специализированного вычислительного устройства акселерометров, вход-выход которого является выходом блока.

4. Система по п. 1, отличающаяся тем, что подсистема электропитания содержит первый и второй источники первичной энергии, выходы которых подключены к первой группе входов блока управления и контроля, первому и второму входам первого коммутатора, выход которого подключен к входам первого и второго аккумуляторов, подключенных выходами ко второй группе входов блока управления и контроля и к первому и ко второму входам второго коммутатора, выход которого подключен к силовому входу источника вторичного электропитания, установочный вход которого объединен с входом формирователя синхроимпульсов и совместно с установочным входом блока управления и контроля является установочным входом подсистемы, причем первая и вторая группы выходов блока управления и контроля подключены соответственно к управляющим входам первого и второго коммутаторов, а выходы постоянного и импульсного питания источника вторичного электропитания являются одноименными выходами подсистемы.

5. Система по п. 1, отличающаяся тем, что бортовая цифровая вычислительная машина содержит трехканальный системный модуль, выход каждого канала которого подключен к входу блока контроля и управления и входам переключателя каналов, управляющие входы которого подключены к выходам блока контроля и управления, а выходы являются выходами дублированной системной магистрали, к которой подключено несколько (n) вычислительных модулей и несколько (m) модулей связи, магистральные входы-выходы которых являются одноименными входами выходами машины, у которой одна из шин магистрали содержит установочный выход машины, у которой к системной магистрали подключены также таймер, матричный вычислитель и запоминающее устройство с санкционированным доступом, блокирующий вход которого подключен к выходу формирователя сигнала, установочный вход которого подключен к установочному выходу, а вход подключен к выходу датчика внешнего воздействия.

6. Система по п. 2, отличающаяся тем, что датчик угловой скорости содержит чувствительный элемент грубого отсчета и чувствительный элемент точного отсчета, выход каждого из которых подключен к своему счетчику, выход которого является выходом датчика.

7. Система по п. 2, отличающаяся тем, что специализированное вычислительное устройство датчика угловой скорости содержит первый микропроцессор, входы и вход-выход которого являются входами и входом-выходом устройства, а через первую двунаправленную связь к нему подключен первый блок специализированного запоминающего устройства, выход первого микропроцессора подключен к входам первого блока микропрограммного управления и первого буферного регистра, подключенного выходами к входам n последовательно соединенных шинами переноса умножителей, подключенных выходами к входам сумматора, подключенного выходом к блоку связи, вход-выход которого объединен с входом-выходом первого микропроцессора, а к его управляющим входам подключены выходы блока микропрограммного управления, подключенные также к управляющим входам остальных блоков устройства.

8. Система по п. 3, отличающаяся тем, что каждый акселерометр содержит кварцевый задающий генератор, рабочий скол кристалла кварца которого является осью чувствительности акселерометра, а вход генератора подключен к входу акселерометрического динамического счетчика, выход которого является выходом акселерометра.

9. Система по п. 3, отличающаяся тем, что специализированное вычислительное устройство акселерометров содержит второй микропроцессор, входы и вход-выход которого являются входами и входом-выходом устройства, а через первую двунаправленную связь к нему подключено второе специализированное запоминающее устройство, причем выход второго микропроцессора подключен к входам второго блока микропрограммного управления и второго буферного регистра, выход которого подключен к входу умножителя, подключенного выходом к входу арифметико-логического блока, подключенного выходом к входу блока связи, вход-выход которого объединен с входом-выходом второго микропроцессора, а через вторую двунаправленную связь блок связи подключен ко второму специализированному запоминающему блоку, к управляющим входам которого и управляющим входам остальных блоков подключены выходы второго блока микропрограммного управления.

10. Система по п. 4, отличающаяся тем, что источник вторичного электропитания содержит модуль постоянного питания и модуль импульсного питания, силовой вход которых, установочный вход и три управляющих входа являются одноименными входами источника, а их выходы постоянного и импульсного питания - одноименными выходами источника.

11. Система по п. 4, отличающаяся тем, что формирователь синхроимпульсов содержит первый, второй и третий генераторы импульсов, выход каждого из которых подключен к входу своего соответственно первого, второго и третьего блоков фазирования, фазирующий выход каждого из которых подключен к фазирующим входам двух других блоков и входу блока мажоритации, к остальным входам которого подключены синхронизирующие выходы блоков фазирования, а выходы блока мажоритации являются выходами метки времени, трех управляющих сигналов и синхронизирующими выходами блока и формирователя.

12. Система по п. 5, отличающаяся тем, что блок контроля и управления содержит первый, второй и третий входные регистры, выход первого из которых подключен к первым входу первой и третьей схем совпадения, выход второго подключен ко второму входу первой схемы совпадения и первому входу второй и схемы совпадения, а выход третьего регистра подключен ко вторым входам второй и третьей схем совпадения, причем выход каждой схемы совпадения, первой, второй и третьей через свой соответственно первый, второй и третий триггеры-формирователи подключен к входу логического формирователя, выходы которого являются выходами блока.

13. Система по п. 5, отличающаяся тем, что переключатель каналов содержит три полевых транзистора, исток каждого из которых является одним из входов, стоки объединены и являются выходами, а каждый управляющий вход подключен к затвору соответствующего транзистора.

14. Система по п. 5 отличающаяся тем, что запоминающее устройство санкционированного доступа содержит первый и второй накопители, блокирующий вход каждого из которых является одноименным входом запоминающего устройства, а к каждому накопителю, первому и второму через первую и вторую временные связи подключены соответственно первый и второй сумматоры метки времени, входы которых являются входом метки времени запоминающего устройства, а через первую и вторую массивные связи к каждому из накопителей подключены соответственно первый и второй сумматоры массивов, подключенные через свои двунаправленные шины к магистральной шине связи запоминающего устройства, к которой подключены также и накопители.

15. Система по п. 5, отличающаяся тем, что датчик внешнего воздействия выполнен как блокинг-генератор, к базе транзистора которого подключен обратносмещенный диод.

16. Система по п. 5 отличающаяся тем, что формирователь сигнала содержит задающий генератор, подключенный выходом к входу интервального счетчика, подключенного выходами через дешифратор к сбрасывающему входу триггера блокировки, запускающий вход которого является входом формирователя и объединен с запускающим входом интервального счетчика и входом логического блокирующего элемента, выход которого является выходом формирователя, вход подключен к выходу триггера блокировки, а к его запрещающему входу через дешифратор кода подключены выходы регистра санкционированного кода, вход которого является установочным входом формирователя.

17. Система по п. 5, отличающаяся тем, что матричный вычислитель содержит первую и вторую матрицы нейропроцессоров, подключенных через матричную магистраль к арифметико-логическому устройству, матричному запоминающему устройству и матричному блоку связи по магистрали, два входа-выхода которого являются входами-выходами вычислителя, подключенными к системной магистрали, причем выход арифметико-логического устройства подключен к входу матричного запоминающего устройства, а установочный выход блока связи по магистрали подключен к установочному входу матричного блока микропрограммного управления, выходы которого подключены к управляющим входам всех компонентов матричного вычислителя.

18. Система по п. 5, отличающаяся тем, что таймер содержит первый и второй формирователи интервалов и контрольный формирователь интервала, выходы которых подключены к входам блока контроля, причем входы-выходы всех формирователей интервала подключены к таймерному блоку связи по магистрали, два магистральных входа-выхода которого являются входами-выходами таймера, подключенными к системной магистрали.

19. Система по п. 10, отличающаяся тем, что модуль постоянного питания содержит три конвертора, силовой и установочный входы которых являются одноименными входами модуля, их частотные выходы подключены к частотным входам блока сравнения и управления, выходы подключены к контрольным входам блока сравнения и управления и через блок отключения - к блоку выравнивания, причем управляющие входы блока отключения подключены к выходам блока сравнения и управления, а выход блока выравнивания является выходом модуля и подключен к дополнительному контрольному входу блока управления и контроля.

20. Система по п. 11, отличающаяся тем, что генератор импульсов содержит группу последовательно включенных инверторов, подключенных выходами к входам первого мультиплексора, выход которого является выходом генератора и подключен к входу первого инвертора и входу первого счетчика частоты, выходы которого подключены к первым входам первого устройства сравнения, ко вторым входам которого подключены выходы регистра кода частоты, а инкрементный и декрементный выходы устройства сравнения подключены к одноименным входам счетчика кода частоты, выходы которого подключены к управляющим входам первого мультиплексора, причем установочные входы регистра кода частоты и счетчика кода частоты являются установочным входом генератора.

21. Система по п. 11, отличающаяся тем, что блок фазирования содержит элемент И, первый вход которого является входом блока, а выход подключен к входу сдвигового регистра и входу выполненного на динамических триггерах динамического счетчика, подключенного через дешифратор к запускающему входу триггера останова, выход которого является фазирующим выходом блока и подключен ко второму входу элемента И и первому входу элемента мажоритации, выход которого подключен к входу триггера пуска, подключенного выходом к сбрасывающему входу триггера останова, а ко второму и третьему входам элемента мажоритации подключены выходы триггеров привязки, входы которых являются фазирующими входами блока, у которого выходы четных и нечетных разрядов сдвигового регистра подключены соответственно к запускающим и сбрасывающим входам формирователей, выходы которых являются синхронизирующими выходами блока.

22. Система по п. 10, отличающаяся тем, что модуль импульсного питания содержит три ветви, объединенные с двух сторон, первая из которых является входом силового питания, вторая - выходом, причем в каждой ветви последовательно включены два полевых транзистора, а три входных управляющих сигнала разведены таким образом, что каждый из них подключен к затворам двух транзисторов, установленных в разных ветвях, образуя выборку «2 из 3».

23. Система по п. 14, отличающаяся тем, что накопитель содержит энергонезависимый элемент памяти, параллельно шинам записи которого установлен полевой транзистор со встроенным каналом, к затвору которого подключен сигнал блокировки

24. Система по п. 19, отличающаяся тем, что конвертор содержит последовательно включенные входной фильтр, защитный диод, трансформатор с включенным в первичную обмотку транзистором-прерывателем, выпрямляющий диод во вторичной обмотке и выходной фильтр, выход которого является выходом конвертора и подключен к входу преобразователя напряжения в частоту, подключенного выходом к входу элемента развязки, выход которого является частотным выходом конвертора и подключен к входу частотно-импульсного модулятора, установочный вход которого является установочным входом конвертора, а выход подключен к базе транзистора-прерывателя.

25. Система по п. 19, отличающаяся тем, что блок отключения содержит три полевых транзистора, истоки которых являются входами, стоки - выходами, а каждый из входных управляющих сигналов подключен к затвору одного из транзисторов.

26. Система по п. 19, отличающаяся тем, что блок выравнивания содержит три идентичные цепи, в каждой из которых последовательно включены резистор и диод, причем первый вывод резистора является вводом, второй подключен к катоду своего диода цепи, а катоды диодов объединены и являются выходом блока.

27. Система по п. 19, отличающаяся тем, что блок сравнения и управления содержит первый, второй, третий и четвертый частотные счетчики, у которых выходы первых трех являются частотными входами блока, а вход четвертого подключен к выходу схемы преобразования напряжения в частоту, к входу которого подключен выход аналогового мультиплексора, контрольные входы которого и дополнительный контрольный вход являются одноименными входами блока, при этом выход первого частотного счетчика подключен к первому входу первого сумматора, выход второго подключен ко второму входу первого сумматора и первым входам второго и третьего сумматоров, выход третьего счетчика подключен ко вторым входам первого и третьего сумматоров, а выход четвертого счетчика подключен к первому входу четвертого сумматора, ко второму входу которого подключен выход регистра кода, установочный вход которого является установочным входом блока и объединен с установочным входом регистра допуска, выход которого подключен к первым входам первого, второго, третьего и четвертого элементов совпадения, выход каждого из которых подключен к входу группы логических элементов, выход которой является выходом блока.

28. Система по п. 24, отличающаяся тем, что входной фильтр содержит в плюсовой шине диод, анод которого является входом, а катод - выходом, между которым и минусовой шиной установлен низкочастотный конденсатор, а каждая из шин, и плюсовая, и минусовая, через свой высокочастотный конденсатор подключена к шине земли.

29. Система по п. 24, отличающаяся тем, что частотно-импульсный модулятор содержит группу последовательно соединенных инверторов, подключенных выходами к входам второго мультиплексора, выход которого подключен к входу первого инвертора и является выходом модулятора, вход которого является входом второго счетчика частоты, подключенного выходами к первым входам второй схемы сравнения, ко вторым входам которой подключены выходы второго регистра кода частоты, а инкрементный и декрементный выходы второй схемы сравнения подключены к одноименным входам второго счетчика кода частоты, подключенного выходами к управляющим входам второго мультиплексора, а установочный вход этого счетчика, как и установочный вход второго регистра кода частоты, является установочным входом модулятора

30. Система по п. 21, отличающаяся тем, что динамический триггер реализован как транзисторный усилитель, к базе транзистора которого помимо резисторного делителя подключена выполняющая роль элемента памяти LC цепь, индуктивность которой содержит рабочую обмотку и намотанную поверх нее встречно-компенсационную, концы которой закорочены.

| НАВИГАЦИОННЫЙ КОМПЛЕКС, УСТРОЙСТВО ВЫЧИСЛЕНИЯ СКОРОСТИ И КООРДИНАТ, БЕСПЛАТФОРМЕННАЯ ИНЕРЦИАЛЬНАЯ КУРСОВЕРТИКАЛЬ, СПОСОБ КОРРЕКЦИИ ИНЕРЦИАЛЬНЫХ ДАТЧИКОВ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2007 |

|

RU2373498C2 |

| СПОСОБ И УСТРОЙСТВО ОТОБРАЖЕНИЯ ПРОСТРАНСТВЕННЫХ ОБЪЕКТОВ | 1998 |

|

RU2143718C1 |

| УСТРОЙСТВО, СПОСОБ И ПРОГРАММА ОБРАБОТКИ ИЗОБРАЖЕНИЯ | 2009 |

|

RU2469403C2 |

| Устройство для умножения чисел в модулярной системе счисления | 1989 |

|

SU1667065A1 |

| EP 1177529 В1, 02.02.2005 | |||

| US 5596339 А1, 21.01.1997 | |||

Авторы

Даты

2015-09-20—Публикация

2013-07-18—Подача