Изобретение относится к логическим элементам микросхем с наноразмерными проектными нормами для высоконадежной вычислительной техники и может быть использовано в элементах управления микропроцессорных микросхем и элементах считывания запоминающих устройств.

Наиболее близкой по технической сущности и достигаемому результату является триггер комплементарной металл-оксид-полупроводниковой структуры микросхемы, состоящий из пар NMOП и РМОП транзисторов, соединенных между собой, с шиной источника питания, линиями управления и выходными линиями и размещенных на кристалле интегральной микросхемы (см. Wang W., Gong Н. Edge triggered pulse latch design with delayed latching edge for radiation hardened application // IEEE Trans. Nucl. Science. 2004. V.51. №6. P.3616-3630).

Недостатком описанного триггера является недостаточная помехоустойчивость и сниженная радиационная стойкость транзисторов триггера к воздействию одиночных ядерных частиц.

Техническим результатом, ожидаемым от использования изобретения, является повышение сбоеустойчивости к воздействию одиночных ядерных частиц без избыточного увеличения площади, занимаемой триггером на кристалле.

Указанный технический результат достигается тем, что в триггере комплементарной металл-оксид-полупроводниковой структуры микросхемы, состоящем из пар NМОП и РМОП транзисторов, соединенных между собой, с шиной источника питания, линиями управления и выходными линиями и размещенных на кристалле интегральной микросхемы, согласно изобретению транзисторы объединены в два блока, каждый из которых содержит две группы из двух NМОП транзисторов и двух РМОП транзисторов, стоки РМОП транзисторов в каждой группе соединены с затвором первого NМОП транзистора в группе, сток которого соединен с затвором первого из двух РМОП транзисторов, а исток со стоком второго NМОП транзистора в этой группе, сток первого РМОП транзистора первой группы блока соединен со стоком первого NМОП транзистора второй группы этого блока, причем два блока транзисторов размещены на кристалле интегральной микросхемы один от другого на расстоянии, равном или больше порогового расстояния, для исключения одновременного воздействия одиночной ядерной частицы на оба блока транзисторов с уровнем больше порогового.

Указанная совокупность признаков позволяет снизить вероятность сбоя состояния триггера при воздействии одиночной ядерной частицы при одновременном снижении площади, занимаемой триггером на кристалле.

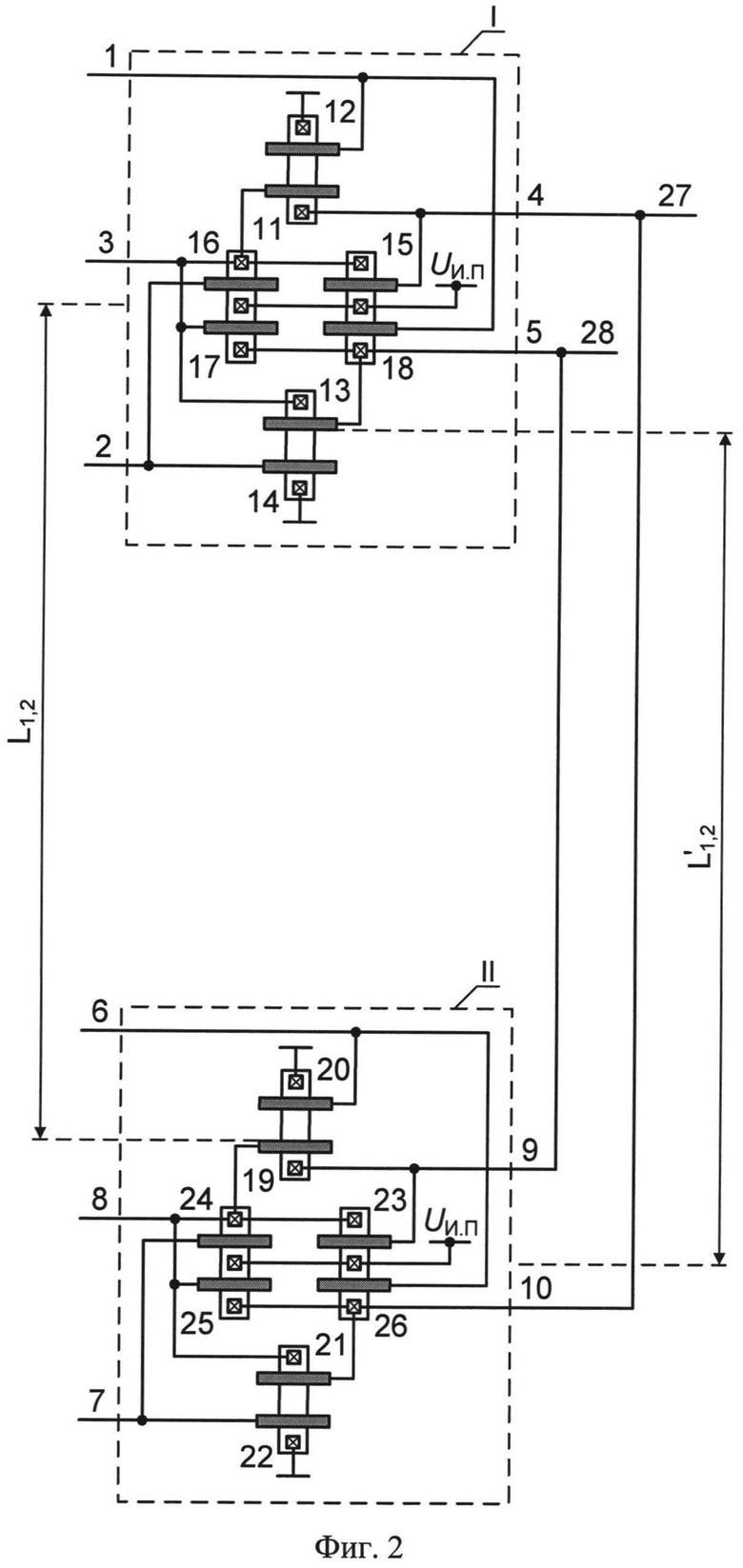

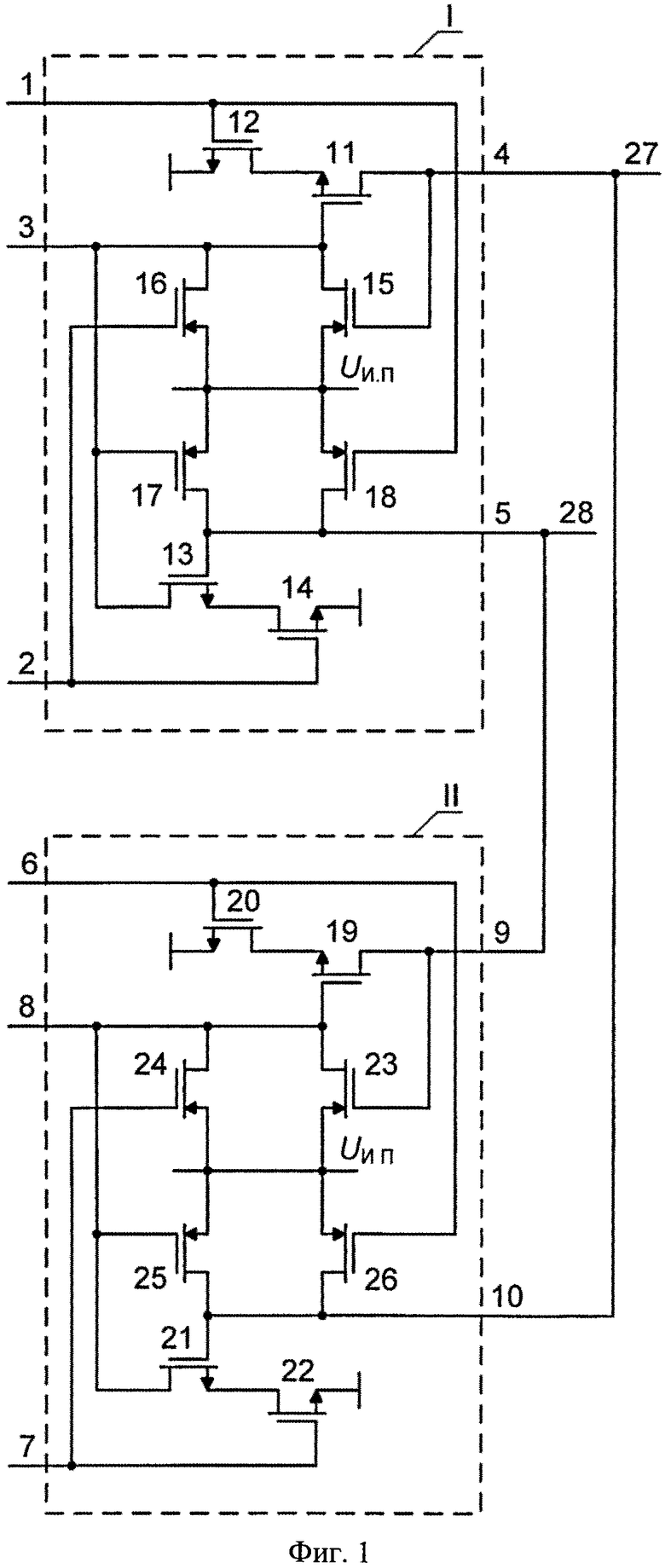

Изобретение поясняется чертежами, где на фиг.1 изображена электрическая принципиальная схема триггера, на фиг.2 изображена схема взаимного расположения транзисторов в блоках триггера и блоков относительно друг друга.

Триггер содержит два блока I, II транзисторов, первый блок I имеет пять выводов 1, 2, 3, 4, 5, второй блок II имеет пять выводов 6, 7, 8, 9, 10. В состав первого блока I входят четыре NМОП транзистора 11, 12, 13, 14 и четыре РМОП транзистора 15, 16, 17, 18, в состав второго блока II входят четыре NМОП транзистора 19, 20, 21, 22 и четыре РМОП транзистора 23, 24, 25, 26. Выводы 3 и 8 блоков I и II являются двумя прямыми выходами триггера, вывод 27, объединяющий выводы 4 и 10 блоков I и II, и вывод 28, объединяющий выводы 5 и 9 блоков I и II, являются двумя инверсными выходами триггера, выводы 1, 2, 6, 7 являются входами управления триггера.

Транзисторы 11, 12, 15, 16 образуют первую группу транзисторов первого блока I, транзисторы 13, 14, 17, 18 образуют вторую группу транзисторов первого блока I, транзисторы 19, 20, 23, 24 образуют первую группу второго блока II, транзисторы 21, 22, 25, 26 образуют вторую группу второго блока II.

Расстояние между двумя блоками транзисторов должно быть равным или больше порогового и определяется из выражения:

L1,2≥LПОР={(πQТР2SСБ2Dn,p/(8ΔlТР))(RВЫХ.ОТКР·λНλВЫХ/UПЕР)}1/3×tgθ,

где QТР2 - заряд, образованный на отрезке трека ΔlТР, наиболее близкого ко второму блоку II транзисторов;

SСБ2=ΔlСБ2×wСБ2 - площадь сбора заряда во втором блоке II транзисторов;

ΔlСБ2 - размер области сбора заряда в одном направлении с направлением трека, а

wСБ2 - в поперечном направлении;

Dn,p - коэффициент амбиполярной диффузии носителей заряда;

ΔlТР - длина отрезка трека, из области которого диффундируют неравновесные носители во второй блок II транзисторов;

RВЫХ.ОТКР - выходное сопротивление (усредненное значение) открытого МОП транзистора, соединенного его собственным стоком со стоком транзистора, собирающего заряд во втором блоке II транзисторов;

UПЕР - напряжение переключения транзистора второго блока II триггера;

θ - угол наклона трека частицы относительно нормали к поверхности кристалла; λН=(τН/τСП)a, a=τН/(τСП-τН).

Постоянные времени нарастания τН и спада τСП импульса фототока, образованного диффузией заряда от трека частицы, зависят от постоянной времени диффузии неравновесных носителей τD из области трека до собирающей заряд области второго блока II транзисторов ячейки и их связь известна (см. Fulkerson D.E. A physics-based engineering methodology for calculating soft error rates of bulk CMOS and SiGe heterojunction bipolar transistor integrated circuits // IEEE Trans. Nucl. Science. 2010. Vol.57. №1. pp.348):

τСП=τD=4r2/(π2Dn,р) и τН=τСП/9,

где Dn,р - коэффициент амбиполярной диффузии носителей заряда.

Коэффициент λВЫХ определяется как λВЫХ=(τВЫХ/τСП)a, a=τВЫХ/(τСП-τВЫХ), где τВЫХ=RВЫХ.ОТКР.2×CУЗЛА - постоянная времени перезаряда узла триггера; CУЗЛА - емкость узла, заряд QПЕР на которой образует импульс помехи с амплитудой, переключающей триггер.

Заряд QTР2 следует из выражения:

QТР2=q×LET×ρSi×ΔlТР/Eр,n,

где LET - линейные потери энергии частицей;

q - заряд электрона;

ΔlТР - длина отрезка трека, из области которого диффундируют неравновесные носители;

ρSi - плотность кремния;

Eр,n - энергия образования одной электронно-дырочной пары.

Описанное устройство может работать в одном из двух режимов: хранение и запись данных.

В режиме хранения на выходах 3, 8, 27, 28 триггера сохраняются установленные при записи логические уровни сигналов “0” и “1” с дублированием одного логического уровня данных на выводах 3 и 8, а другого на выводах 27, 28. Триггер в режиме хранения может находиться в двух устойчивых состояниях: в одном состоянии на двух выходах 3 и 8 уровни сигнала “0”, а на двух других выходах 27, 28 - уровни “1”. В другом устойчивом состоянии триггера логические уровни сигналов на этих выходах меняются.

В режиме записи под действием управляющих сигналов на выводах 1, 2, 6, 7 триггер устанавливается в одно из двух устойчивых состояний. Изменить состояние триггера при записи можно, только подавая два сигнала управления с уровнями логических “0” на выводы 2 и 7 в режиме, когда на выходах 3 и 8 находятся логические сигналы с уровнями “0”, а на выходах 27, 28 находятся логические сигналы с уровнями “1”. В этом случае управляющие сигналы на выводах 2 и 7 переключают состояние триггера, замыкая цепь положительной обратной связи в триггере. Аналогично изменить состояние триггера, когда на выходах 3 и 8 находятся логические сигналы с уровнями “1”, а на выходах 27, 28 находятся логические сигналы с уровнями “0”, можно, только подавая два сигнала управления с уровнями логических “0” на выводы 1 и 6.

Снижение площади, занимаемой триггером на кристалле, обеспечивается близким расположением всех транзисторов в блоках и снижением до двух шин связей между блоками.

При воздействии на триггер одиночной ядерной частицы, когда трек частицы направлен от запертого транзистора одного блока I к запертому транзистору другого блока II, происходит образование вдоль трека частицы неравновесных носителей заряда, которые диффундируют к транзисторам, где выводятся в виде фототоков через стоковые электроды запертых транзисторов и перезаряжают емкости этих узлов, вызывая импульсы напряжения помехи, которые могут произвести сбой состояния триггера при превышении порога переключения.

Критичным для оценки стойкости триггера является сбой состояния в режиме хранения. Сбой логического состояния триггера может произойти при воздействии частицы одновременно на два МОП транзистора триггера, находящихся в запертом состоянии, исключая воздействия на следующие пары транзисторов 11 и 15, 13 и 17, 19 и 23, 21 и 25 в их запертом состоянии, при котором происходит размыкание обратной связи в триггере, что и сохраняет исходное логическое состояние триггера.

Сбой исходного состояния триггера возможен только при одновременном воздействии одиночной частицы на пару запертых транзисторов, один из которых относится к блоку I транзисторов, а второй к блоку II транзисторов. В одном из двух логических состояний триггера (см. фиг.1 и фиг.2) это пары транзисторов - 11 и 19, 11 и 23, 15 и 19, 15 и 23, а для другого логического состояния триггера следующие пары: 17 и 25, 17 и 21, 13 и 25, 13 и 21.

Пример реализации изобретения

Изобретение может быть реализовано в тактируемых одно- и двухступенчатых триггерах, использованных в блоке управления регистрового файла КМОП микропроцессорной системы с проектной нормой 65 нм. Эскизное изображение конструкции триггера приведено на фиг.2.

В одном логическом состоянии триггера на фиг.2 заперты транзисторы 11, 15 блока I и транзисторы 19, 23 блока II, расположенные в верхних половинах блоков I и II на фиг 2. В другом логическом состоянии заперты транзисторы 13, 17 блока 1 и транзисторы 21, 25 блока II триггера, расположенные в нижних половинах блоков I и II на фиг 2. На фиг.2 отмечены расстояния между двумя группами запертых транзисторов для одного логического состояния триггера L1,2 и для другого L′1,2. Эти расстояния для приведенного размещения транзисторов одинаковы L1,2=L′1,2 и определяют сбоеустойчивость триггера в двух его логических состояниях.

Для достижения технического результата - повышения сбоеустойчивости триггера при воздействии одиночных ядерных частиц блоки I и II транзисторов триггера (см. фиг.2) разнесены на расстояние L1,2=2,5 мкм.

Сбоеустойчивость триггера при воздействии одиночных ядерных частиц обусловлена предложенным разделением транзисторов триггера на два блока и разнесением их на кристалле микросхемы на расстояние, равное или больше порогового расстояния, исключающего одновременное воздействие одиночной ядерной частицы на оба блока I и II транзисторов с уровнем больше порогового.

Сбой состояния триггера при одновременном воздействии частицы на два обратно смещенных транзистора из разных блоков I и II триггера, например на транзисторы 11 и 23, возможен, когда на каждый из этих транзисторов выводятся заряды больше порогового значения для каждого транзистора QПОР, в результате чего амплитуда импульса помехи на соответствующем узле превышает пороговое значения переключения, например, UПЕР=0,25-0.5 В для триггеров по проектной норме КМОП 65 нм и UПЕР=0,1-0,15 В для триггеров по проектной норме КМОП 28 нм. Если же запертым транзистором блока II от импульса фототока на емкость узла выводится заряд QСБ меньше порогового заряда переключения QСБ<QПОР, то независимо от значения заряда, собранного другим запертым транзистором в блоке I, сбоя триггера не происходит, поскольку импульс помехи в блоке II имеет амплитуду меньше напряжения порога переключения. Критичными при оценке сбоеустойчивости триггера являются воздействия частицы, когда ее трек проходит в направлении от одного блока I к другому блоку II (см. фиг.2) и под малым углом к поверхности полупроводникового кристалла микросхемы, что соответствует углам наклона трека частицы относительно нормали к поверхности кристалла θ≥60°, причем трек частицы проходит через область обратно смещенного pn перехода сток-подложка запертого транзистора в блоке I, например транзистора 11 (см. фиг.2), непосредственно воздействуя на этот транзистор, а на второй из пары запертых транзисторов, который относится к блоку II и одновременно подвергается воздействию частицы, например транзистор 23, действует заряд неосновных носителей, диффундирующих к нему от ближайшей к нему области трека частицы. Для исключения сбоя триггера расстояние L1,2=L′1,2 между парами чувствительных МОП транзисторов из двух блоков I и II должно быть равно или больше порогового значения LПОР.

В таблице 1 приведены результаты моделирования пороговых расстояний LПОР в зависимости от параметров воздействующей частицы для триггера по проектной норме КМОП 65 нм, обеспечивающих стойкость к воздействию одиночных ядерных частиц с линейными потерями 40 и 60 МэВ·cм2/мг для углов падения одиночной частицы θ=60° и 75° в зависимости от параметров транзисторов: IС.НАС=67-107 мкА, RВЫХ.ОТКР=4.1-7.3 кОм при CУЗЛА=4 фФ.

Моделирование показало, что описанный триггер по проектной норме КМОП 65 нм обеспечивает бессбойную работу при воздействии одиночных частиц с углами наклона трека 60° и значениями линейных потерь энергии LET=60 МэВ×см2/мг при расстоянии между блоками L1,2≥LПОР=1.57 мкм и с углами 75° при линейных потерях энергии LET=40 МэВ×см2/мг при обеспечении расстоянии между блоками L1,2≥LПОР=2.97 мкм.

| название | год | авторы | номер документа |

|---|---|---|---|

| ЯЧЕЙКА ПАМЯТИ КОМПЛЕМЕНТАРНОЙ МЕТАЛЛ-ОКСИД-ПОЛУПРОВОДНИКОВОЙ СТРУКТУРЫ ОЗУ | 2013 |

|

RU2554849C2 |

| Логический элемент сравнения комплементарной металл-оксид-полупроводниковой структуры ассоциативного селектора запоминающего устройства | 2016 |

|

RU2621011C1 |

| Асинхронный логический элемент комплементарной металл-оксид-полупроводниковой структуры | 2018 |

|

RU2693685C1 |

| ЯЧЕЙКА ПАМЯТИ КОМПЛЕМЕНТАРНОЙ МЕТАЛЛ-ОКСИД-ПОЛУПРОВОДНИКОВОЙ СТРУКТУРЫ ОЗУ | 2015 |

|

RU2580071C1 |

| БЛОК ПАМЯТИ КОМПЛЕМЕНТАРНОЙ МЕТАЛЛ-ОКСИД-ПОЛУПРОВОДНИКОВОЙ СТРУКТУРЫ ОЗУ | 2015 |

|

RU2580072C1 |

| Многовходовой логический элемент комплементарной металл-оксид-полупроводниковой структуры декодера | 2015 |

|

RU2616170C1 |

| ЭНЕРГОЭФФЕКТИВНЫЙ НИЗКОВОЛЬТНЫЙ КМОП-ТРИГГЕР | 2015 |

|

RU2611236C1 |

| ВЫХОДНОЙ ФОРМИРОВАТЕЛЬ ИМПУЛЬСНЫХ СИГНАЛОВ С УСТРОЙСТВОМ ЗАЩИТЫ ОТ ЭЛЕКТРОСТАТИЧЕСКИХ РАЗРЯДОВ ДЛЯ КМОП МИКРОСХЕМ | 2013 |

|

RU2540813C1 |

| Сбоеустойчивый самосинхронный однотактный RS-триггер с нулевым спейсером | 2019 |

|

RU2725780C1 |

| Сбоеустойчивый самосинхронный однотактный RS-триггер с единичным спейсером | 2019 |

|

RU2725781C1 |

Изобретение относится к области вычислительной техники и может быть использовано в элементах управления микропроцессорных КМОП микросхемах и элементах считывания запоминающих устройств. Техническим результатом является повышение устойчивости к воздействию одиночных ядерных частиц без избыточного увеличения площади, занимаемой триггером на кристалле в составе интегральной КМОП микросхемы. Триггер состоит из пар NМОП и РМОП транзисторов, соединенных между собой, с шиной источника питания, линиями управления и выходными линиями, транзисторы объединены в два блока, каждый из которых содержит две группы из двух NМОП транзисторов и двух РМОП транзисторов, причем два блока транзисторов размещены на кристалле интегральной микросхемы один от другого на расстоянии, равном или больше порогового расстояния, для исключения одновременного воздействия одиночной ядерной частицы на оба блока транзисторов с уровнем больше порогового. 1 табл., 2 ил.

Триггер комплементарной металл-оксид-полупроводниковой структуры микросхемы, состоящий из пар NМОП и РМОП транзисторов, соединенных между собой, с шиной источника питания, линиями управления и выходными линиями и размещенных на кристалле интегральной микросхемы, отличающийся тем, что транзисторы объединены в два блока, каждый из которых содержит две группы из двух NМОП транзисторов и двух РМОП транзисторов, стоки РМОП транзисторов в каждой группе соединены с затвором первого NМОП транзистора в группе, сток которого соединен с затвором первого из двух РМОП транзисторов, а исток со стоком второго NМОП транзистора в этой группе, сток первого РМОП транзистора первой группы блока соединен со стоком первого NМОП транзистора второй группы этого блока, причем два блока транзисторов размещены на кристалле интегральной микросхемы один от другого на расстоянии, равном или больше порогового расстояния, для исключения одновременного воздействия одиночной ядерной частицы на оба блока транзисторов с уровнем больше порогового.

| Триггер на КМОП транзисторах | 1980 |

|

SU921052A1 |

| РАДИАЦИОННО СТОЙКОЕ ТРИГГЕРНОЕ УСТРОЙСТВО | 1989 |

|

SU1600598A1 |

| Триггер | 1991 |

|

SU1804666A3 |

| US 7719304 B1, 18.05.2010 | |||

| US 2008211558 A1, 04.09.2008 | |||

| JP 8213884 A, 20.08.1996 | |||

| МЕХАНИЗМ ЛОКТЕВОГО ШАРНИРА ПРОТЕЗА | 0 |

|

SU281741A1 |

Авторы

Даты

2015-02-20—Публикация

2013-09-26—Подача