Изобретение относится к области вычислительной техники и может быть использовано в устойчивых к сбоям блоках асинхронной логики микропроцессорных систем.

Основой устойчивой к сбоям асинхронной логики микропроцессорных систем являются двухвходовые и более логические элементы с памятью текущего состояния, в которой в моменты нарушения их логического функционирования запоминаются и хранятся последние достоверные данные, и с этими данными должно осуществляться дальнейшее продолжение процесса обработки в потоке данных, поступающих на входы таких логических элементов. Такие асинхронные логические элементы содержат как комбинационные логические элементы, так и элементы хранения на триггерах. Воздействие отдельных ядерных частиц на триггеры таких логических элементов в интервал хранения данных приводит к возникновению импульсов помех и сбою логического состояния триггеров (single event upsets - SEU) таких элементов. Таким образом нарушается обработка данных в цепи, включающей асинхронный логический элемент. Снижение проектно-технологических норм КМОП СБИС до уровня менее 100 нм сопровождается ростом частоты одиночных сбоев (soft error rate - SER) таких комбинированных логических элементов, совмещающих элементы комбинационной и последовательностной логик, под действием одиночных ядерных частиц. Необходимо исключить возможность внесения погрешностей в процессе хранения данных в асинхронные логические элементы такого типа при воздействии одиночных ядерных частиц на триггер в их составе.

Вариантами КМОП асинхронного комбинационного логического элемента в настоящее время являются КМОП логический С-элемент на основе комбинационных элементов типа КМОП инвертор с третьим (высокоомным) состоянием по выходу и четырех-транзисторный D-триггер (Патент US №7 554 374 В2, кл. H03K 3/017, опублик. Jun. 30, 2009, фиг. 1А), а также асинхронный логический элемент (Патент US №2016/0 071 587 А1, кл. G11C 13/00, опублик. March 10, 2016, фиг. 1 и фиг. 2).

Наиболее близким по технической сущности и достигаемому результату является асинхронный логический элемент комплементарной металл-оксид-полупроводниковой структуры, включающий два инвертора с третьим состоянием, размещенных на кристалле интегральной микросхемы, первые и вторые входы инверторов с третьим состоянием соединены, соответственно, с первой и второй входными шинами (Патент US №6 281 707 В1, кл. H03K 19/02; H03K 19/094, опублик. Aug. 28,2001, фиг. 2)

Недостатком описанного элемента является плохая сбоеустойчивость (помехоустойчивость, надежность выполнения логической функции с временным хранением данных) к воздействию одиночных ядерных частиц. Сбой возникает даже при воздействии одиночной ядерной частицы на один внутренний узел триггера элемента. Это проблема всех элементов с использованием триггера на основе пары КМОП-инверторов.

Задачей настоящего изобретения является повышение надежности логического элемента при воздействии одиночной ядерной частицы.

Техническим результатом, ожидаемым от использования изобретения, является повышение помехоустойчивости (надежности выполнения логической функции) логического элемента при воздействии одиночных ядерных частиц.

Указанный технический результат достигается тем, что асинхронный логический элемент комплементарной металл-оксид-полупроводниковой структуры, включающий два инвертора с третьим состоянием, размещенные на кристалле интегральной микросхемы, первые и вторые входы инверторов с третьим состоянием соединены, соответственно, с первой и второй входными шинами, согласно изобретению, логический элемент снабжен триггером, состоящим из двух групп транзисторов, которые включают четыре комплементарные пары РМОП и NМОП транзисторов, два дополнительных РМОП транзистора в первой группе транзисторов триггера, два дополнительных NМОП транзистора в второй группе транзисторов триггера, затвор РМОП транзистора в первой паре РМОП и NМОП транзисторов в первой группе транзисторов триггера соединен с первым выводом первой группы транзисторов триггера и с стоком NМОП транзистора первой пары транзисторов, затвор которого соединен с стоком РМОП транзистора первой пары, с вторым выводом первой группы, с стоком NМОП транзистора в второй паре РМОП и NМОП транзисторов в первой группе, с затвором РМОП транзистора второй пары, сток которого соединен с истоком первого дополнительного РМОП транзистора, сток которого соединен с истоком второго дополнительного РМОП транзистора, сток которого соединен с затвором NМОП транзистора второй пары РМОП и NМОП транзисторов первой группы и с третьим выводом первой группы транзисторов, затворы первого и второго дополнительных РМОП транзисторов соединены, соответственно, с четвертым и пятым выводами первой группы транзисторов триггера, затвор РМОП транзистора в третьей паре РМОП и NМОП транзисторов соединен с первым выводом второй группы и с стоком первого дополнительного NМОП транзистора, исток которого соединен с стоком второго дополнительного NМОП транзистора, исток которого соединен с стоком NМОП транзистора третьей пары РМОП и NМОП транзисторов в второй группе, затвор которого соединен с стоком РМОП транзистора третьей пары РМОП и NМОП транзисторов, с вторым выводом второй группы транзисторов триггера, с затвором РМОП транзистора четвертой пары РМОП и NМОП транзисторов, с стоком NМОП транзистора четвертой пары транзисторов, затвор которого соединен с стоком РМОП транзистора четвертой пары транзисторов, с третьим выводом второй группы и с первым выводом первой группы транзисторов триггера, затворы первого и второго дополнительных NМОП транзисторов соединены, соответственно, с четвертым и пятым выводами второй группы транзисторов триггера, истоки РМОП и истоки NМОП транзисторов пар соединены, соответственно, с шиной питания и общей шиной элемента, выход первого инвертора с третьим состоянием соединен с первым выводом первой группы транзисторов триггера, выход второго инвертора с третьим состоянием соединен с третьим выводом первой группы транзисторов триггера и с первым выводом второй группы транзисторов триггера, четвертые выводы первой и второй групп транзисторов триггера соединены с первой входной шиной элемента, пятые выводы первой и второй групп транзисторов триггера соединены с второй входной шиной элемента, вторые выводы первой и второй групп транзисторов триггера, соответственно, соединены с первой и второй выходными шинами элемента, причем две группы транзисторов триггера размещены на кристалле интегральной микросхемы одна от другой на расстоянии, исключающем одновременное воздействие одиночной ядерной частицы на обе группы транзисторов триггера.

А также тем, что каждый инвертор с третьим состоянием включает пару РМОП транзисторов и пару NМОП транзисторов, стоки первых в паре РМОП и в паре NМОП транзисторов соединены, соответственно, с истоками вторых в паре РМОП и паре NМОП транзисторов, стоки которых объединены и соединены с выходом инвертора с третьим состоянием, затворы первых РМОП и NМОП транзисторов в парах соединены с первым входом, а затворы вторых NМОП и РМОП транзисторов соединены с вторым входом инвертора с третьим состоянием, истоки первых РМОП и первых NМОП транзисторов соединены, соответственно, с шиной питания и общей шиной элемента.

А также тем, что первый инвертор с третьим состоянием и первая группа транзисторов триггера составляют первый блок логического элемента, второй инвертор с третьим состоянием и вторая группа транзисторов триггера составляют второй блок логического элемента, которые размещены на кристалле интегральной микросхемы один за другим, при этом в цепочке логических элементов с чередованием групп транзисторов триггеров i-й и (i+1+K)-й блоки образуют i-й логический элемент, где i=1; 2;…; m. K - интервал чередования, разделяющий два блока одного элемента, где возможное количество разделяющих блоков K=0; 1; 2; …; m-1.

А также тем, что указанное расстояние, исключающее одновременное воздействие одиночной ядерной частицы на обе группы транзисторов триггера, составляет не менее двух диффузионных длин неосновных носителей заряда.

Указанная совокупность признаков позволяет снизить вероятность сбоя состояния триггера и повысить надежность (помехоустойчивость) асинхронного логического элемента при воздействии одиночной ядерной частицы.

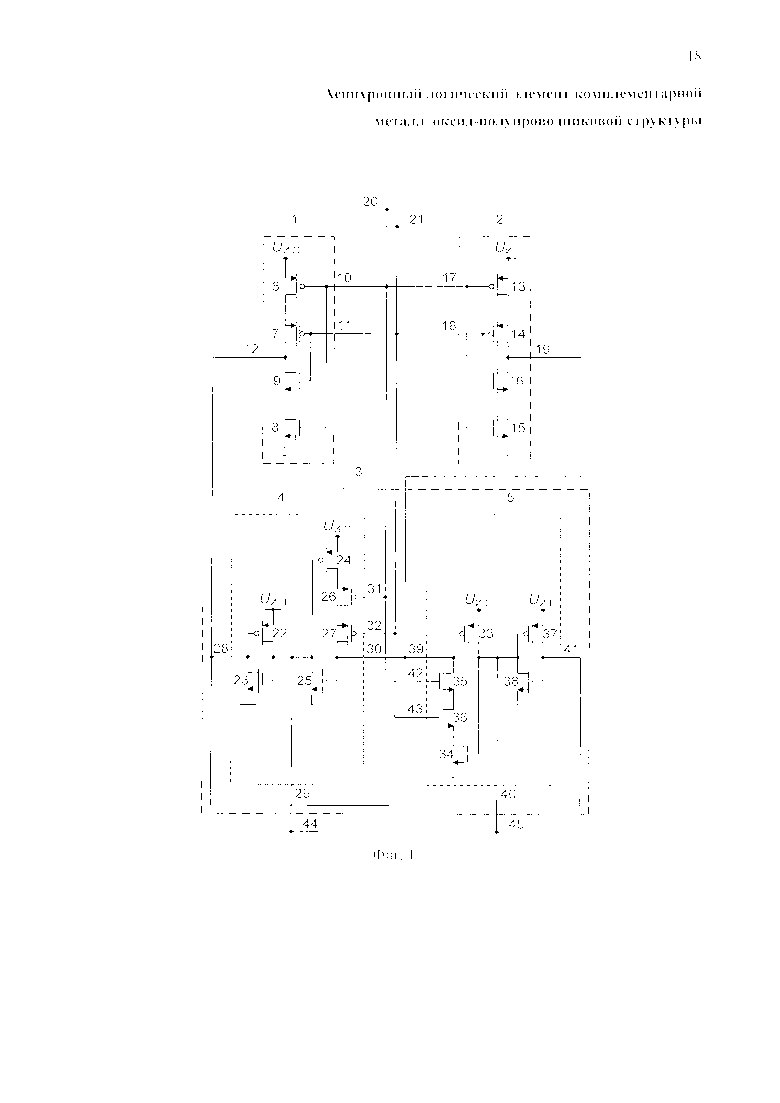

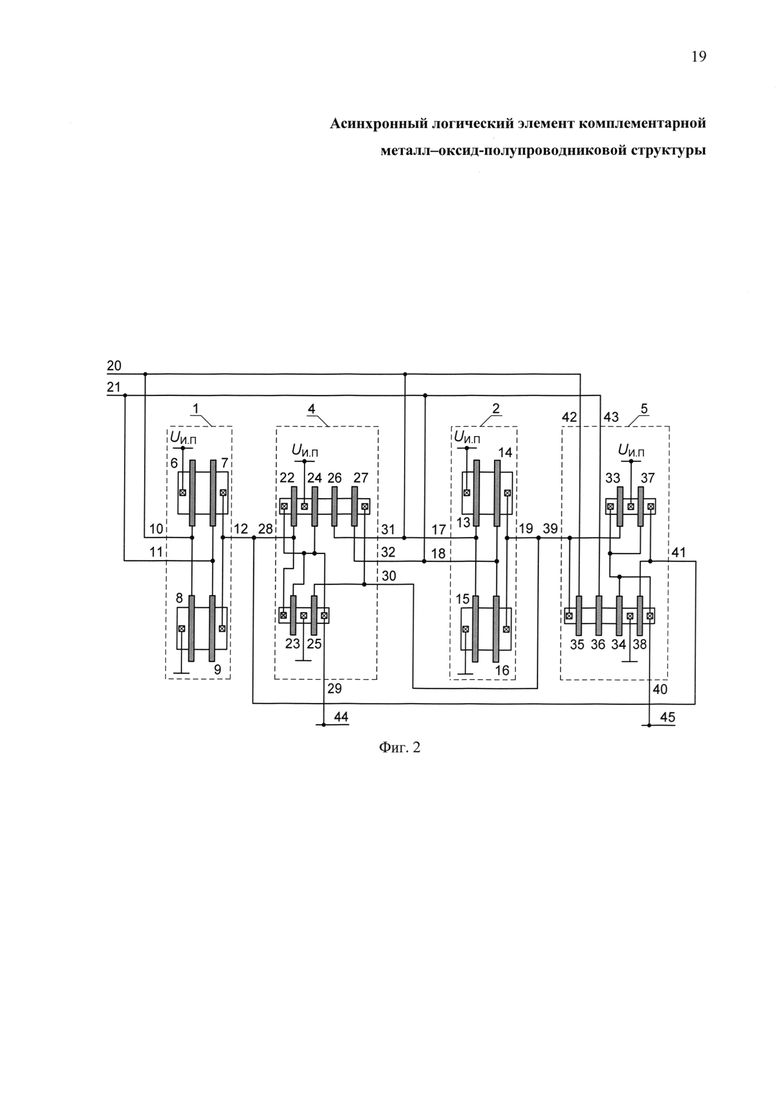

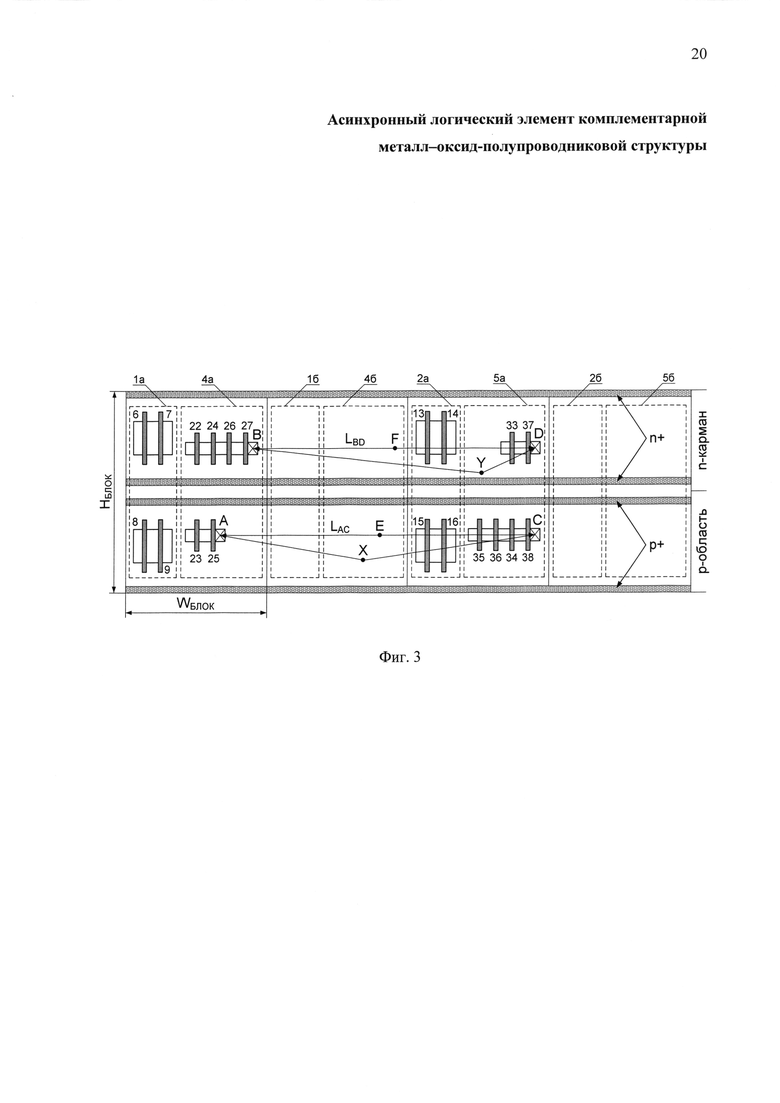

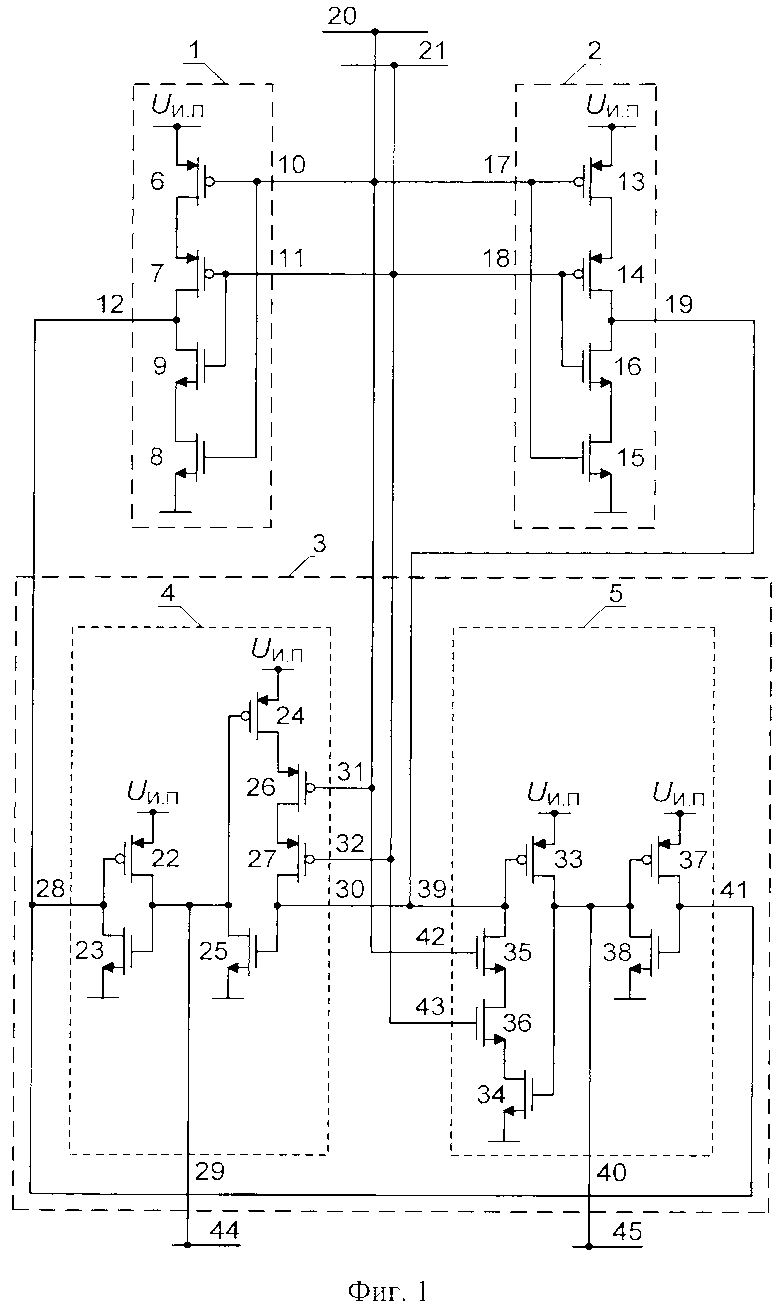

Изобретение поясняется чертежами, где на фиг. 1 изображена электрическая принципиальная схема асинхронного логического элемента, на фиг. 2 изображена схема взаимного расположения транзисторов одного логического элемента, на фиг. 3 изображена схема взаимного расположения транзисторов в базовом элементе регистра, содержащем два асинхронных логических элемента.

Использованы обозначения: РМОП транзистор - это транзистор со структурой металл-оксид-полупроводник и каналом дырочной проводимости, то есть Р-типа; NМОП транзистор - транзистор со структурой металл-оксид-полупроводник и каналом электронной проводимости, то есть N-типа.

Логический элемент содержит два инвертора 1, 2 с третьим состоянием, триггер 3, состоящий из первой и второй групп 4, 5 транзисторов. Первый инвертор 1 с третьим состоянием на РМОП транзисторах 6, 7 и NМОП транзисторах 8, 9 имеет два входа 10, 11 и выход 12, второй инвертор 2 с третьим состоянием на РМОП транзисторах 13, 14 и NМОП транзисторах 15, 16 имеет два входа 17, 18 и выход 19. Первые входы 10, 17 первого и второго инверторов 1, 2 с третьим состоянием соединены с первой входной шиной 20 элемента, вторые входы 11, 18 первого и второго инверторов 1, 2 с третьим состоянием соединены со второй входной шиной 21 элемента. Первая группа 4 транзисторов триггера 3 на первой паре РМОП и NМОП транзисторов 22, 23 и второй паре РМОП и NМОП транзисторов 24, 25 с двумя дополнительными РМОП транзисторами 26, 27 имеет пять выводов 28, 29, 30, 31, 32, вторая группа 5 триггера 3 на третьей паре РМОП и ТУМОП транзисторов 33, 34 с двумя дополнительными NМОП транзисторами 35, 36 и четвертой паре РМОП и NМОП транзисторов 37, 38 имеет пять выводов 39, 40, 41, 42, 43, затвор РМОП транзистора 22 в первой паре РМОП и NМОП транзисторов в первой группе 4 транзисторов триггера 3 соединен с первым выводом 28 первой группы и с стоком NМОП транзистора 23 первой пары транзисторов, затвор которого соединен с стоком РМОП транзистора 22 первой пары, с вторым выводом 29 первой группы 4, с стоком NМОП транзистора 25 в второй паре РМОП и NМОП транзисторов в первой группе 4, с затвором РМОП транзистора 24 второй пары, сток которого соединен с истоком первого дополнительного РМОП транзистора 26, сток которого соединен с истоком второго дополнительного РМОП транзистора 27, сток которого соединен с затвором NМОП транзистора 25 второй пары РМОП и NМОП транзисторов первой группы 4 и с третьим выводом 30 первой группы 4 транзисторов, затворы первого и второго дополнительных РМОП транзисторов 26, 27 соединены, соответственно, с четвертым и пятым выводами 31, 32 первой группы 4 транзисторов триггера 3, затвор РМОП транзистора 33 в третьей паре РМОП и NМОП транзисторов 33, 34 в второй группе 5 транзисторов триггера 3 соединен с первым выводом 39 второй группы 5 и с стоком первого дополнительного NМОП транзистора 35, исток которого соединен с стоком второго дополнительного NМОП транзистора 36, исток которого соединен с стоком NМОП транзистора 34 третьей пары РМОП и NМОП транзисторов 33, 34 в второй группе 5, затвор NМОП транзистора 34 соединен с стоком РМОП транзистора 33 третьей пары, с вторым выводом 40 второй группы 5 транзисторов триггера 3, с затвором РМОП транзистора 37 четвертой пары РМОП и NМОП транзисторов 37, 38, с стоком NМОП транзистора 38 четвертой пары, затвор которого соединен с стоком РМОП транзистора 37 четвертой пары и с третьим выводом 41 второй группы 5 транзисторов триггера 3, затворы первого и второго дополнительных NМОП транзисторов 35, 36 соединены, соответственно, с четвертым и пятым выводами 42, 43 второй группы 5 транзисторов триггера 3, истоки РМОП и истоки NМОП транзисторов пар соединены, соответственно, с шиной питания и общей шиной элемента, выход 12 первого инвертора 1 с третьим состоянием соединен с первым выводом 28 первой группы 4 транзисторов триггера 3 и третьим выводом 41 второй группы 4 транзисторов триггера 3, выход 19 второго инвертора 2 с третьим состоянием соединен с третьим выводом 30 первой группы 4 транзисторов триггера 3 и первым выводом 39 второй группы 5 транзисторов триггера 3. Четвертые выводы 31, 42 первой и второй групп 4, 5 транзисторов триггера 3 соединены с первой входной шиной 20 элемента, пятые выводы 32, 43 первой и второй групп 4, 5 транзисторов триггера 3 соединены с второй входной шиной 21 элемента, второй вывод 29 первой группы 4 транзисторов триггера 3 соединен с первой выходной шиной 44 элемента, второй вывод 40 второй группы 5 транзисторов триггера 3 соединен с второй выходной шиной 45 элемента.

При этом в первом инверторе 1 с третьим состоянием на РМОП транзисторах 6, 7 и NМОП транзисторах 8, 9 стоки первых РМОП и NМОП транзисторов 6, 8 соединены, соответственно, с истоками вторых РМОП и NМОП транзисторов 7, 9, стоки которых объединены и соединены с выходом 12 инвертора 1, затворы первых РМОП и NМОП транзисторов 6, 8 соединены с первым входом 10, а затворы вторых NМОП и РМОП транзисторов 7, 9 соединены, соответственно, с вторым входом 11 инвертора 1, истоки первого РМОП и первого NМОП транзисторов 6, 8 соединены, соответственно, с шиной питания и общей шиной элемента.

Описанное устройство работает следующим образом.

Асинхронный логический элемент, представленный на фиг. 1, может работать в одном из двух режимов: передача потока данных с входных шин 20, 21 на выходные шины 44, 45 при совпадении логических уровней на входных шинах 20, 21 с записью выходной переменной в триггер 3 и хранение выходной переменной в триггере 3 с момента несовпадения данных на входных шинах 20, 21 до момента последующего совпадения одинаковых логических уровней на входных шинах 20, 21 с данными, хранимыми в триггере 3 и находящимися на выходных шинах 44, 45.

Передача логических сигналов с входных шин 20, 21 на выходные шины 44, 45 осуществляется посредством инверторов 1, 2 с третьим состоянием, записывающих данные в два узла триггера 3 через выводы 28, 41 и 30, 39 двух групп 4 и 5 транзисторов триггера 3 при одинаковых логических уровнях на обеих входных шинах 20, 21.

Несовпадение логических уровней сигналов на входных шинах 20, 21 инициирует переход инверторов 1 и 2 с третьим состоянием в третье (высокоомное) состояние по выходам 12, 19 и, соответственно, отключение выводов 28, 30, 39, 41 групп 4, 5 триггера 3 от входных шин 20, 21, что переводит триггер 3 в режим памяти записанного в него логического состояния в виде фиксации логических уровней на выводах 28, 29, 30, 39, 40, 41 групп 4, 5 транзисторов триггера 3.

Логическим уровням Х20=Х21=''0'' на входных шинах 20, 21 соответствует следующий набора логических уровней Х29Х30Х40Х41=0101 на выводах 29, 30, 40, 41 групп 4, 5 транзисторов триггера 3 и логические уровни на выходных шинах Х44=Х45=''0'', причем логические уровни на выводах 30 и 39 групп 4, 5 одинаковы Х39=Х30, так же как логические уровни на выводах 28 и 41 групп 4, 5 одинаковы X28=Х41.

Логическим уровням Х20=Х21=''1'' на входных шинах 20, 21 соответствует следующий набор логических уровней Х29Х30Х40Х41=1010 на выводах 29, 30, 40, 41 групп 4, 5 транзисторов триггера 3 и логические уровни на выходных шинах Х44=Х45=''1'', причем логические уровни на выводах 30 и 39 групп 4, 5 одинаковы Х39=Х30, так же как логические уровни на выводах 28 и 41 групп 4, 5 одинаковы Х28=Х41.

Изменение связи сигналов на входных шинах 20, 21, выходах 12, 19 инверторов с третьим состоянием 1, 2 и выходных шинах 44, 45 асинхронного логического элемента можно описать, используя следующие длительности интервалов времени (включая длительности задержек):

1) длительность импульса на входных шинах 20, 21, осуществляющего переключение асинхронного логического элемента из логического состояния ''0'' в состояние ''1'' с последующим возвратом асинхронного логического элемента в логическое состояние ''0'': ΔtВХ.1=tПЕР1+ΔtТР1+tПЕР0;

2) длительность импульса на входных шинах 20, 21, осуществляющего переключение асинхронного логического элемента из логического состояния ''1'' в состояние ''0'' с последующим возвратом асинхронного логического элемента в логическое состояние ''1'':

ΔtВХ.1=tПЕР0+ΔtТР0+tПЕР1

где tПЕР1 - задержка переключения асинхронного логического элемента из логического состояния ''0'' в состояние ''1'' логическим сигналом ''1'' на входных шинах 20, 21;

где tПЕР0 - задержка переключения асинхронного логического элемента из логического состояния ''1'' в состояние ''0'' логическим сигналом ''0'' на входных шинах 20, 21;

ΔtТР1 - длительность нахождения триггера 3 асинхронного логического элемента в состоянии ''1'' (сохранения логических сигналов ''1'' на выходных шинах 44, 45);

ΔtТР0 _ длительность нахождения триггера 3 асинхронного логического элемента в состоянии ''0'' (сохранения логических сигналов ''0'' на выходных шинах 44, 45).

Для повышения надежности выполнения передаточной логической функции асинхронным логическим элементом при воздействии одиночной ядерной частицы необходимо уменьшать длительности задержки переключения логического сигнала ''1'' с входных шин 20, 21 на выходные шины 44, 45 асинхронного логического элемента /пер1 и задержки переключения логического сигнала ''0'' с входных шин 20, 21 на выходные шины 44, 45 асинхронного логического элемента tПЕР0 для того, чтобы минимизировать возможность (вероятность) перекрытия интервалов времен нахождения триггера 3 в этих переходных состояниях и интервала времени воздействия одиночной ядерной частицы на транзисторы триггера 3 асинхронного логического элемента.

Кроме того, для повышения надежности выполнения передаточной логической функции асинхронным логическим элементом при воздействии одиночной ядерной частицы необходимо исключить сбой логического состояния триггера 3 в интервалы времени нахождения триггера 3 в устойчивом состоянии ''0'' ΔtТР0 и нахождения триггера 3 в устойчивом состоянии ''1'' ΔtТР1

Дополнительные транзисторы 26,27, 35, 36, которыми снабжены группы 4, 5 триггера 3 асинхронного логического элемента, обеспечивают снижение задержек при переходе триггера 3 из одного логического состояния в другое и снижение задержек переключения логических сигналов ''0'' и "1" с входных шин 20, 21 на выходные шины 44, 45 асинхронного логического элемента. При смене сигналов с ''0'' на ''1'' на входных шинах 20, 21 дополнительные РМОП транзисторы 26 и 27, управляемые с входных шин 20 и 21, переходят из открытого состояния в запертое, что размыкает положительную обратную связь в цепочке транзисторов 24, 25, 26, 27, обеспечивая снижение времен задержки установления логического уровня ''0'' на выводах 30 и 39 групп 4, 5 триггера 3 и задержки установления логического уровня ''1'' на выводе 29 группы 4 триггера 3 и выходной шине 44. Одновременно дополнительные NМОП транзисторы 35 и 36, управляемые с входных шин 20 и 21, переходят из запертого состояния в открытое, что замыкает положительную обратную связь в цепочке транзисторов 33, 34, 35, 36, обеспечивая снижение времени задержки установления логического уровня ''1'' на выводе 40 группы 5 триггера 3 и выходной шине 45.

При смене сигналов с ''1'' на ''0'' на входных шинах 20, 21 дополнительные РМОП транзисторы 26 и 27, управляемые с входных шин 20 и 21, переходят из запертого состояния в открытое, что замыкает положительную обратную связь в цепочке транзисторов 24, 25, 26, 27, обеспечивая снижение времени задержки установления логического уровня ''1'' на выводах 30 и 39 групп 4, 5 триггера 3 и времени задержки установления логического уровня ''0'' на выводе 29 группы 4 триггера 3 и выходной шине 44. Одновременно дополнительные NМОП транзисторы 35 и 36, управляемые с входных шин 20 и 21, переходят из открытого состояния в запертое, что размыкает положительную обратную связь в цепочке транзисторов 33, 34, 35, 36, обеспечивая снижению времени задержки установления логического уровня ''0'' на выводе 40 группы 5 триггера 3 и выходной шине 45.

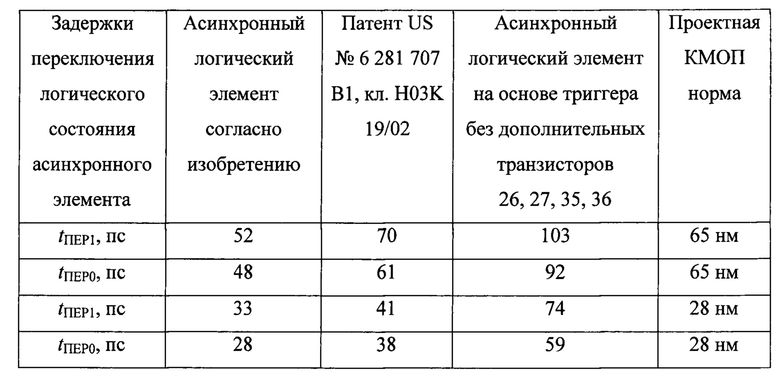

В таблице 1 приведены результаты моделирования времен задержек переключения из состояния ''0'' в ''1'' tПЕР1 и из ''1'' в ''0'' tПЕР0 для вариантов асинхронных логических элементов, спроектированных в соответствии с проектно-технологической нормой и ''объемный КМОП 65 нм'' и ''объемный КМОП 28 нм''. Приведены задержки переключения для предложенного асинхронного логического элемента, для наиболее близкого по электрическим параметрам аналога (Патент US №6 281 707 В1, кл. Н03K 19/02; Н03K 19/094, опублик. Aug. 28, 2001, фиг. 2) и для варианта асинхронного логического элемента на основе триггера 3 без дополнительных транзисторов 26, 27, 35, 36.

Моделирование асинхронных логических элементов проведено в симуляторе Cadence Spectre на основе моделей, предоставленных фабрикой-изготовителем микросхем при напряжении питания 1.0 В для 65-нм технологии и 0.9 В для 28-нм технологии при температуре +25°С с учетом паразитных RC-параметров соединений.

Значения задержек переключения у предложенного асинхронного логического элемента на 48-55% меньше по сравнению с вариантом асинхронного логического элемента на основе триггера без дополнительных транзисторов 26, 27, 35, 36.

Таблица 1. Задержки переключения из ''0'' в ''1'' tПЕР1 и из ''1'' в ''0'' tПЕР0 для вариантов асинхронных логических элементов по объемной КМОП технологии с проектными нормами 65 нм и 28 нм

Снижение задержек переключении логического состояния триггера 3 обеспечивает как повышение быстродействия асинхронного логического элемента, то есть предельной частоты переключения сигналов на входных шинах 20 и 21, так и необходимо для снижения интервала времени возможного негативного воздействия одиночной ядерной частицы в этом интервале времени задержек переключении при переходном процессе изменения логического состояния триггера 3.

Критичными при оценке надежности асинхронного логического элемента при передаче данных с входных шин 20, 21 на выходные шины 44, 45 является интервал времени с момента, когда произошло несовпадение сигналов на входных шинах 20 и 21 до момента, когда восстанавливается совпадение сигналов на входных шинах 20 и 21 и сигналы на выходных шинах 44, 45 должны соответствовать сигналам на входных шинах 20 и 21, бывшим до момента их несовпадения. В этот интервал времени триггер 3 сохраняет последнее логическое состояние асинхронного логического элемента, бывшее перед несовпадением сигналов на входных шинах 20 и 21. Недопустимо, чтобы в этот интервал времени произошел сбой данных, записанных в триггер 3, вызванный эффектами воздействия одиночной ядерной частицы на асинхронный логический элемент на кристалле микросхемы.

Сбой триггера 3, который сохраняет последнее логическое состояние асинхронного логического элемента, бывшее перед несовпадением сигналов на входных шинах 20, 21, возможен только в случае одновременного сбора заряда с трека одиночной ядерной частицы обратно смещенными стоковыми pn-переходами двух запертых взаимно чувствительных NМОП транзисторах 25, 38 в одном из логических состояний триггера 3 или в случае одновременного сбора заряда с трека частицы стоковыми pn-переходами двух запертых взаимно чувствительных РМОП транзисторов 27, 37 в другом логическом состоянии триггера 3. При этом собранные заряды на обоих взаимно чувствительных запертых NМОП или РМОП транзисторах должны превышать пороговые значения. Взаимно чувствительные узлы разнесены на эскизе топологии на фиг. 3 для минимизации вероятности сбоев триггера 3.

На практике возможны все направления треков одиночных частиц внутри шарообразной сферы всех направлений воздействия частицы на кристалл микросхемы, на котором выполнен асинхронный логический элемент.В исследовательских целях для оценки устойчивости к сбоям КМОП элементов чаще всего используется вариант воздействий, когда трек частицы направлен по нормали к поверхности кристалла микросхемы. КМОП транзисторы в микросхемах по объемной технологии с проектными нормами 65 нм и менее изготавливаются в «островках» кремния, окруженных толстым слоем диоксида кремния, под которым находится слой кремния практически такой же толщины и того же типа проводимости, что и «островки». Для таких микросхем критичными воздействиями являются те, когда трек частицы проходит, например, в непосредственной близости от (или прямо через область) обратно смещенного рп-перехода сток-подложка запертого транзистора 25 первой группы 4 транзисторов триггера 3, а на парный взаимно чувствительный запертый транзистор 38 второй группы 5 транзисторов действует заряд неосновных носителей, диффундирующих к нему от трека частицы в слое кремния под слоем толстого изолирующего диоксид кремния и «островков». В этих случаях наклон трека частицы в пределах 45-60° относительно нормали к поверхности существенно не изменяет результаты оценки устойчивости к сбоям. Таким образом, основным оценочным фактором является диффузионная длина неосновных носителей заряда LДИФФ и величина заряда, образованного на части трека, проходящего через активный (приборный) слой кремния. Расстояния от точки входа трека ядерной частицы в кристалл до каждого из пары взаимно чувствительных запертых транзисторов должно быть больше диффузионной длины неосновных носителей заряда LДИФФ.

Пример реализации изобретения

Устройство по изобретению реализовано в виде блока регистра асинхронных логических элементов в составе КМОП СБИС микропроцессорной системы по проектной норме 65 нм. Блок содержит 64 предложенных логических элементов. Эскизное изображение конструкции (топологии) одного логического элемента приведено на фиг. 2. Эскизное изображение конструкции базового элемента регистра, состоящего из двух асинхронных логических элементов, взаимное расположение блоков которых обеспечивает необходимое расстояние между взаимно чувствительными узлами запертых транзисторов с обратно смещенными стоковыми pn-переходами, приведено на фиг. 3. Для достижения технического результата - повышения надежности (помехоустойчивости) выполнения логической функции селекции при воздействии одиночной ядерной частицы, когда триггер 3 на основе двух групп 4 и 5 транзисторов находится в стационарном состоянии - транзисторы 6, 7, 8, 9 первого инвертора 1 с третьим состоянием размещены на кристалле интегральной микросхемы рядом с транзисторами 22, 23, 24, 25, 26, 27 первой группы 4 транзисторов триггера 3 и образуют первый блок асинхронного логического элемента, транзисторы 13, 14, 15, 16 второго инвертора 2 с третьим состоянием размещены на кристалле интегральной микросхемы рядом с транзисторами 33, 34, 35, 36, 37, 38 второй группы 5 транзисторов триггера 3 и образуют второй блок логического элемента, при этом первый и второй блоки элемента, включающие группы 4 и 5 транзисторов триггера 3 логического элемента (см. фиг.3) размещены на расстоянии между взаимно чувствительными узлами запертых транзисторов двух групп 4 и 5 транзисторов триггера 3 больше порогового расстояния LПОР=2LДИФ=2.0 мкм для исключения одновременного воздействия заряда с трека одиночной ядерной частицы на обе группы 4 и 5 транзисторов триггера 3 для всех тяжелых ядерных частиц (ионов) с линейными потерями энергии (ЛПЭ) в диапазоне до ЛПЭ=60 МэВ×см2/мг.

Основой топологической конструкции статического регистра асинхронных логических элементов является базовый элемент на фиг. 3, состоящий из двух предложенных логических элементов на основе четырех блоков, образующих эти два логических элемента. Каждый из двух асинхронных логических элементов состоит из двух блоков, отмеченных индексами «а» и «б», соответственно, для первого и второго асинхронных логических элементов на основе соответствующих групп 4 и 5 транзисторов и инверторов 1 и 2 с третьим состоянием двух асинхронных логических элементов (всего четыре блока, которые чередуются). Первый логический элемент содержит группы 1а, 2а, 4а, 5а транзисторов, второй логический элемент - группы 1б, 2б, 4б, 5б транзисторов. Расположение транзисторов в каждой из групп логических элементов на фиг. 3 соответствует расположению транзисторов в группах элемента на фиг. 2.

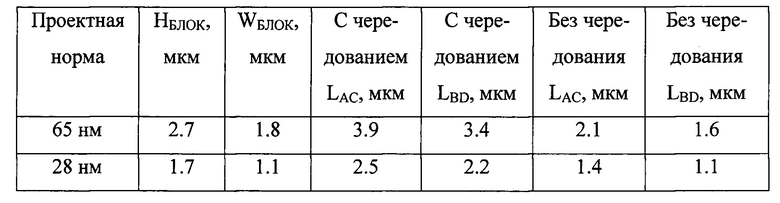

Области стоков NМОП транзисторов 25, 38 триггера 3 обозначены, соответственно, буквами А и С, а области стоков РМОП транзисторов 27, 37 триггера 3 обозначены, соответственно, буквами В и D. В таблице 2 приведены размеры блоков транзисторов и расстояния между обратно смещенными стоковыми pn переходами взаимно чувствительных транзисторов для асинхронных логических элементов, спроектированных по объемной технологии КМОП с проектной нормой 65 нм и 28 нм с чередованием блоков и без чередования для логического состояния ''1'' триггера 3.

Таблица 2. Размеры блоков и расстояния между обратно смещенными стоковыми рп переходами взаимно чувствительных транзисторов из двух блоков по объемной КМОП технологии для логического состояния "1" триггера 3

Для объемной кремниевой технологии КМОП 65 нм высота блоков составляет НБЛОК=2.7 мкм, а ширина WБЛОК=1.8 мкм. Расстояние между двумя взаимно чувствительными стоками NМОП транзисторов 25, 38 для КМОП 65 нм в каждом логическом элементе с чередованием составляет LAC=3.9 мкм, а расстояние между двумя взаимно чувствительными стоками РМОП транзисторов 27, 37 составляет LBD=3.4 мкм.

Для объемной кремниевой технологии КМОП 28 нм высота блоков составляет НБЛОК=1.7 мкм, а ширина WБЛОК =1.1 мкм. Расстояние между двумя взаимно чувствительными стоками NМОП транзисторов 25, 38 в каждом логическом элементе составляет LAC=2.5 мкм, а расстояние между двумя взаимно чувствительными стоками РМОП транзисторов 27, 37 составляет LBD=2.2 мкм.

На фиг. 3 и в таблице 2 расстояния LAC и LBD между обратно смещенными стоковыми pn переходами взаимно чувствительных к сбору заряда с трека одиночной частицы пары NМОП транзисторов 25, 38 и пары РМОП транзисторов 27, 37 приведены для нахождения триггера 3 в состоянии логической единицы ''1'' при логических уровнях Х29Х30Х40Х41=1010 на выводах 29, 30, 40, 41 групп 4, 5 транзисторов триггера 3. В состоянии логического нуля ''0'' триггера 3 при логических уровнях Х29Х30Х40Х41=0101 на выводах 29, 30, 40, 41 групп 4, 5 транзисторов триггера 3 расстояния между обратно смещенными стоковыми pn переходами взаимно чувствительных транзисторов 23, 35 равны расстоянию LBD при состоянии ''1'' триггера 3, то есть L23-35(''0'')=LBD(''1''), а расстояние между стоками пары РМОП транзисторов 22, 33 равны расстоянию LAC при состоянии ''1'' триггера 3, то есть L22-З3(''0'')=LAC(''1'').

В КМОП микросхемах с повышенной устойчивостью к воздействиям одиночных ядерных частиц, изготавливаемых по объемной технологии, области NМОП транзисторов (на фиг. 3 позиции 8, 9, 15, 16, 23, 25, 34, 35, 36, 38) и РМОП транзисторов (на фиг. 3 позиции 6, 7, 13, 14, 22, 24, 26, 27, 33, 37) разделены изолирующими диффузионными областями n+ и p+ типа проводимости с контактами к шине питания и общей шине (земли). Изолирующие диффузионные области служат для вывода зарядов неравновесных носителей из активной области полупроводникового кристалла, которые генерируются на треке одиночной ядерной частицы.

Потеря энергии частицей в полупроводниковом кристалле вдоль трека вызывает генерацию носителей заряда (пар электрон-дырка). Неосновные носители заряда для данной области полупроводника диффундируют от области трека в прилегающие области, где собираются обратно смещенными pn-переходами КМОП транзисторов. Такой сбор заряда приводит к образованию импульсов помех, которые могут вызвать сбой логического состояния триггера и вызвать временное изменение логического состояния комбинационной логики.

Величина диффундируемого заряда зависит от потерь энергии одиночной ядерной частицей (при больших потерях энергии возникает больше носителей заряда), а размеры области такого диффузионного «растекания» заряда зависят от диффузионной длины генерируемых носителей заряда, на которую влияет как температура, так и конкретный уровень легирования этих областей кристалла.

КМОП транзисторы в микросхемах по объемной технологии 65 нм изготавливаются в «островках» кремния, окруженных диоксидом кремния толщиной 400 нм, под которым находится слой кремния такой же толщины и того же типа проводимости, что и «островки».

Экспериментальные результаты исследования воздействий одиночных ядерных частиц разной энергии и линейных потерь энергии в кремнии таковы (M.S. Gorbunov, P.S. Dolotov, A.A. Antonov, G.I. Zebrev, V.V. Emeliyanov, A.B. Boruzdina, A.G. Petrov, A.V. Ulanova. Design of 65 nm CMOS SRAM for Space Applications: a Comparative Study // IEEE Transactions on Nuclear Science, 2014. V. 61, №4, P. 1575-1582), что диффузионная длина неравновесных носителей заряда не превышает 1 мкм в активных (приборных) слоях кремния микросхем по объемной технологии КМОП 65 нм.

На фиг. 3 даны примеры возможных точек входа трека одиночной частицы в полупроводниковый кристалл в области стоков транзисторов 25, 38, и 27, 37, являющихся взаимно чувствительными к сбору заряда парами узлов, условно обозначенные, соответственно, как пара узлов А, С и пара узлов В, D. Кроме того, приведены варианты точек входа трека, обозначенные как Е, F, X, Y. Точка Е входа трека на фиг. 3 соответствует середине расстояния между точками А и С, точка F входа трека соответствует середине расстояния между точками В и D, точки X, Y являются примерами других возможных точек входа трека частицы, точка X расположена в p-области кристалла, в которой выполнены NМОП транзисторы, а точка Y расположена в «-кармане, в котором выполнены РМОП транзисторы.

Сбой триггера 3, который сохраняет последнее логическое состояние асинхронного логического элемента, бывшее перед несовпадением сигналов на входных шинах 20, 21, возможен только в случае одновременных импульсов помех на стоках двух взаимно чувствительных NМОП транзисторов 25, 38 (узлы А и С) в одном из логических состояний триггера 3 или в случае одновременных импульсов помех на стоках двух взаимно чувствительных РМОП транзисторов 27, 37 (узлы В и D) в другом логическом состоянии триггера 3. При этом параметры импульсов помех на обоих узлах должны превышать пороговые значения.

Критичными для возникновения сбоя триггера 3 являются треки одиночных ядерных частиц с точками входа Е и F, соответственно, посередине между узлами А и С в области NМОП транзисторов и посередине между узлами В и D в области РМОП транзисторов. Расстояние между стоками NМОП транзисторов 25, 38 (узлы А и С) и расстояние между стоками РМОП транзисторов 27, 37 (узлы В и D) должны быть выбраны как минимум в два раза больше значения диффузионной длины носителей заряда, генерируемых на треке частицы, то есть должны выполняться ограничения LAC>2LДИФФ и LBD>2LДИФФ, где LДИФФ - диффузионная длина носителей заряда. Чередование блоков из групп транзисторов двух логических элементов на фиг. 3 обеспечивает достаточные расстояния между взаимно чувствительными узлами в двух группах 2 и 5 транзисторов триггера 3 при проектных нормах 65 нм и 28 нм, поскольку LAC(65 нм)=3.9 мкм> LAC(28 нм)=2.5 мкм>2LДИФФ=2 мкм и LBD(65 нм)=3.4 мкм>LBD(28 нм)=2.2 мкм>2LДИФФ=2 мкм, где LДИФФ=1 мкм. В этом случае расстояния от точки Е входа трека до узлов А и С и от точки F до узлов В и D, соответственно, превышают диффузионную длину носителей заряда, и воздействия с этими точками входа трека не приведут к сбоям состояния триггера 3.

При других случайных точках входа трека частицы (два варианта как примеры приведены на фиг. 3 с обозначениями X и Y) помеха от воздействия частицы может превысить пороговое значение только на одном из узлов А, В, С, D, который ближе к этой точке входа трека, что исключает сбой триггера 3. Увеличить расстояния между взаимно чувствительными узлами в двух группах 2 и 5 транзисторов каждого из логических элементов можно, если использовать чередование блоков трех смежных в регистре асинхронных логических элементов.

| название | год | авторы | номер документа |

|---|---|---|---|

| Логический элемент сравнения комплементарной металл-оксид-полупроводниковой структуры ассоциативного селектора запоминающего устройства | 2016 |

|

RU2621011C1 |

| ТРИГГЕР КОМПЛЕМЕНТАРНОЙ МЕТАЛЛ-ОКСИД-ПОЛУПРОВОДНИКОВОЙ СТРУКТУРЫ МИКРОСХЕМЫ | 2013 |

|

RU2541894C1 |

| БЛОК ПАМЯТИ КОМПЛЕМЕНТАРНОЙ МЕТАЛЛ-ОКСИД-ПОЛУПРОВОДНИКОВОЙ СТРУКТУРЫ ОЗУ | 2015 |

|

RU2580072C1 |

| ЯЧЕЙКА ПАМЯТИ КОМПЛЕМЕНТАРНОЙ МЕТАЛЛ-ОКСИД-ПОЛУПРОВОДНИКОВОЙ СТРУКТУРЫ ОЗУ | 2015 |

|

RU2580071C1 |

| ЯЧЕЙКА ПАМЯТИ КОМПЛЕМЕНТАРНОЙ МЕТАЛЛ-ОКСИД-ПОЛУПРОВОДНИКОВОЙ СТРУКТУРЫ ОЗУ | 2013 |

|

RU2554849C2 |

| ЭНЕРГОЭФФЕКТИВНЫЙ НИЗКОВОЛЬТНЫЙ КМОП-ТРИГГЕР | 2015 |

|

RU2611236C1 |

| ВЫХОДНОЙ ФОРМИРОВАТЕЛЬ ИМПУЛЬСНЫХ СИГНАЛОВ С УСТРОЙСТВОМ ЗАЩИТЫ ОТ ЭЛЕКТРОСТАТИЧЕСКИХ РАЗРЯДОВ ДЛЯ КМОП МИКРОСХЕМ | 2013 |

|

RU2540813C1 |

| ПОЛУПРОВОДНИКОВОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1995 |

|

RU2128371C1 |

| Сбоеустойчивый самосинхронный однотактный RS-триггер с нулевым спейсером | 2019 |

|

RU2725780C1 |

| Счетчик | 1988 |

|

SU1529448A1 |

Изобретение относится к области вычислительной техники. Технический результат заключается в повышении помехоустойчивости логического элемента при воздействии одиночных ядерных частиц. Технический результат достигается за счет асинхронного логического элемента комплементарной металл-оксид-полупроводниковой структуры, состоящего из двух инверторов с третьим состоянием, кристалла интегральной микросхемы, первого и второго входа инверторов, первой и второй входных шин, триггера, состоящего из двух групп транзисторов, которые включают четыре комплементарные пары РМОП и NМОП транзисторов, двух дополнительных РМОП транзисторов в первой группе транзисторов триггера, двух дополнительных NМОП транзисторов во второй группе транзисторов триггера, затвора РМОП транзистора в первой паре РМОП и NМОП транзисторов в первой группе транзисторов триггера, стока NМОП транзистора первой пары транзисторов, затвора NМОП транзистора второй пары РМОП и NМОП транзисторов первой группы, стока РМОП транзистора четвертой пары транзисторов. 3 з.п. ф-лы, 3 ил., 2 табл.

1. Асинхронный логический элемент комплементарной металл-оксид-полупроводниковой структуры, включающий два инвертора с третьим состоянием, размещенных на кристалле интегральной микросхемы, первые и вторые входы инверторов с третьим состоянием соединены соответственно с первой и второй входными шинами, отличающийся тем, что логический элемент снабжен триггером, состоящим из двух групп транзисторов, которые включают четыре комплементарные пары РМОП и NМОП транзисторов, два дополнительных РМОП транзистора в первой группе транзисторов триггера, два дополнительных NМОП транзистора во второй группе транзисторов триггера, затвор РМОП транзистора в первой паре РМОП и NМОП транзисторов в первой группе транзисторов триггера соединен с первым выводом первой группы транзисторов триггера и со стоком NМОП транзистора первой пары транзисторов, затвор которого соединен со стоком РМОП транзистора первой пары, со вторым выводом первой группы, со стоком NМОП транзистора во второй паре РМОП и NМОП транзисторов в первой группе, с затвором РМОП транзистора второй пары, сток которого соединен с истоком первого дополнительного РМОП транзистора, сток которого соединен с истоком второго дополнительного РМОП транзистора, сток которого соединен с затвором NМОП транзистора второй пары РМОП и NМОП транзисторов первой группы и с третьим выводом первой группы транзисторов, затворы первого и второго дополнительных РМОП транзисторов соединены соответственно с четвертым и пятым выводами первой группы транзисторов триггера, затвор РМОП транзистора в третьей паре РМОП и NМОП транзисторов соединен с первым выводом второй группы и со стоком первого дополнительного NМОП транзистора, исток которого соединен со стоком второго дополнительного NМОП транзистора, исток которого соединен со стоком NМОП транзистора третьей пары РМОП и NМОП транзисторов во второй группе, затвор которого соединен с стоком РМОП транзистора третьей пары РМОП и NМОП транзисторов, со вторым выводом второй группы транзисторов триггера, с затвором РМОП транзистора четвертой пары РМОП и NМОП транзисторов, со стоком NМОП транзистора четвертой пары транзисторов, затвор которого соединен со стоком РМОП транзистора четвертой пары транзисторов, с третьим выводом второй группы и с первым выводом первой группы транзисторов триггера, затворы первого и второго дополнительных NМОП транзисторов соединены соответственно с четвертым и пятым выводами второй группы транзисторов триггера, истоки РМОП и истоки NМОП транзисторов пар соединены соответственно с шиной питания и общей шиной элемента, выход первого инвертора с третьим состоянием соединен с первым выводом первой группы транзисторов, выход второго инвертора с третьим состоянием соединен с третьим выводом первой группы транзисторов триггера и с первым выводом второй группы транзисторов триггера, четвертые выводы первой и второй групп транзисторов триггера соединены с первой входной шиной элемента, пятые выводы первой и второй групп транзисторов триггера соединены со второй входной шиной элемента, вторые выводы первой и второй групп транзисторов триггера соответственно соединены с первой и второй выходными шинами элемента, причем две группы транзисторов триггера размещены на кристалле интегральной микросхемы одна от другой на расстоянии, исключающем одновременное воздействие одиночной ядерной частицы на обе группы транзисторов триггера.

2. Логический элемент по п. 1, отличающийся тем, что каждый инвертор с третьим состоянием включает пару РМОП транзисторов и пару NМОП транзисторов, стоки первых в паре РМОП и в паре NМОП транзисторов соединены соответственно с истоками вторых в паре РМОП и паре NМОП транзисторов, стоки которых объединены и соединены с выходом инвертора с третьим состоянием, затворы первых РМОП и NМОП транзисторов в парах соединены с первым входом, а затворы вторых NМОП и РМОП транзисторов соединены со вторым входом инвертора с третьим состоянием, истоки первых РМОП и первых NМОП транзисторов соединены соответственно с шиной питания и общей шиной элемента.

3. Логический элемент по п. 1, отличающийся тем, что первый инвертор с третьим состоянием и первая группа транзисторов триггера составляют первый блок логического элемента, второй инвертор с третьим состоянием и вторая группа транзисторов триггера составляют второй блок логического элемента, которые размещены на кристалле интегральной микросхемы один за другим, при этом в цепочке логических элементов с чередованием групп транзисторов триггеров i-й и (i+1+K)-й блоки образуют i-й логический элемент, где i=1; 2;…; m, K - интервал чередования, разделяющий два блока одного элемента, где возможное количество разделяющих блоков K=0; 1; 2;…; m-1.

4. Логический элемент по п. 1, отличающийся тем, что указанное расстояние, исключающее одновременное воздействие одиночной ядерной частицы на обе группы транзисторов триггера, составляет не менее двух диффузионных длин неосновных носителей заряда.

| Токарный резец | 1924 |

|

SU2016A1 |

| US 6281707 B1, 28.08.2001 | |||

| US 6859071 B2, 22.02.2005 | |||

| Автомобиль-сани, движущиеся на полозьях посредством устанавливающихся по высоте колес с шинами | 1924 |

|

SU2017A1 |

| ПОЛУПРОВОДНИКОВЫЙ ПЕРЕКЛЮЧАТЕЛЬ С НАДЕЖНЫМ ПОВЕДЕНИЕМ ПРИ ОТКЛЮЧЕНИИ ПИТАНИЯ И НИЗКОЙ МОЩНОСТЬЮ УПРАВЛЕНИЯ | 2012 |

|

RU2586447C2 |

| Автомобиль-сани, движущиеся на полозьях посредством устанавливающихся по высоте колес с шинами | 1924 |

|

SU2017A1 |

Авторы

Даты

2019-07-03—Публикация

2018-11-06—Подача