Изобретение относится к области электронной техники и может быть использовано в системах управления, где требуется высокая надежность выполнения заданного режима (например, в системах управления космическими аппаратами, в авиационной технике и в других системах).

Известно устройство формирования сигналов управления [1], содержащее в каждом канале формирователь управляющих сигналов, элементы, исключающие ИЛИ, многовходовые элементы ИЛИ.

Недостаток этого устройства состоит в его сложности и низкой надежности.

Наиболее близким техническим решением к предлагаемому устройству является устройство формирования сигналов управления [2], содержащее три канала, каждый из которых включает в себя формирователь управляющих сигналов, вход которого соединен с входной шиной.

Недостатком этого устройства является низкая надежность, так как каждый канал содержит фактически два самых сложных блока - два формирователя управляющих сигналов (основной формирователь и модель-подобие формирователя), что значительно снижает надежность канала.

Задача изобретения - повышение надежности.

Решение этой задачи в первом варианте достигается тем, что в устройство формирования сигналов управления, содержащее три канала, каждый из которых включает в себя формирователь управляющих сигналов, вход которого соединен с входной шиной, дополнительно введены дешифратор, формирователь заданного числа и формирователь заданного рассогласования, а в каждый канал дополнительно введены сумматор, элемент выделения модуля, первый и второй цифровые компараторы, при этом выходная шина сумматора соединена с входной шиной элемента выделения модуля, выходная шина которого соединена с шиной А второго цифрового компаратора, выход которого А>В соединен с первым выходом канала, выходная шина контроля формирователя управляющих сигналов соединена с шиной А первого цифрового компаратора, инверсный выход которого А=В соединен со вторым выходом канала, выходная шина управления формирователя управляющих сигналов соединена с входной шиной «слагаемого» сумматора и выходной шиной канала, выход формирователя заданного рассогласования соединен с шиной В второго цифрового компаратора всех каналов, выход формирователя заданного числа соединен с шиной В первого цифрового компаратора всех каналов, первый и второй выходы каждого канала соединены с соответствующими входами дешифратора, первый, второй и третий выходы неисправности которого соединены соответственно с первым, вторым и третьим выходами устройства, выходные шины первого, второго и третьего каналов соединены соответственно с входной шиной «вычитаемого» сумматора третьего, первого и второго каналов.

Дешифратор содержит входной регистр, программируемое запоминающее устройство и выходной регистр, при этом вход каждого разряда входного регистра соединен с соответствующим входом дешифратора, выход входного регистра соединен с шиной адреса программируемого запоминающего устройства, шина данных которого соединена с входной шиной выходного регистра, выход каждого из разрядов которого соединен с соответствующими выходами дешифратора.

Решение этой задачи во втором варианте достигается тем, что в устройство формирования сигналов управления, содержащее три канала, каждый из которых включает в себя формирователь управляющих сигналов, вход которого соединен с входной шиной, дополнительно введены m (m=1, 2, …) резервных формирователей управляющих сигналов, дешифратор, формирователь заданного числа, формирователь заданного рассогласования, счетчик импульсов, элемент ИЛИ, а в каждый канал дополнительно введены первый и второй мультиплексоры, регистр, коммутатор, элемент задержки, сумматор, элемент выделения модуля, первый и второй цифровые компараторы, при этом выходная шина сумматора соединена с входной шиной элемента выделения модуля, выходная шина которого соединена с шиной А второго цифрового компаратора, выход которого А>В соединен с первым выходом канала, выходная шина контроля формирователя управляющих сигналов соединена с основной входной шиной второго мультиплексора, выход которого соединен с шиной А первого цифрового компаратора, инверсный выход которого А=В соединен со вторым выходом канала, выходная шина управления формирователя управляющих сигналов соединена с основной входной шиной первого мультиплексора, выход которого соединен с входной шиной «слагаемого» сумматора и выходной шиной канала, выход элемента задержки соединен с входом управления коммутатора, выход которого соединен с входом регистра, выходная шина которого соединена с шиной управления первого и второго мультиплексоров, первый и второй выходы каждого канала соединены с соответствующими входами дешифратора, первый выход неисправности которого соединен с входом элемента задержки первого канала, первым входом элемента ИЛИ и первым выходом устройства, второй выход неисправности дешифратора соединен с входом элемента задержки второго канала, вторым входом элемента ИЛИ и вторым выходом устройства, третий выход неисправности дешифратора соединен с входом элемента задержки третьего канала, третьим выходом устройства и третьим входом элемента ИЛИ, выход которого соединен с входом С счетчика импульсов, выходная шина кодового состояния которого соединена с входной шиной коммутатора всех каналов и шиной неисправности устройства, выход формирователя заданного числа соединен с шиной В первого цифрового компаратора всех каналов, выход формирователя заданного рассогласования соединен с шиной В второго цифрового компаратора всех каналов, входы всех резервных формирователей управляющих сигналов соединены с входной шиной, выходные шины управления и выходные шины контроля всех резервных формирователей управляющих сигналов соединены с соответствующими резервными входами соответственно первого и второго мультиплексоров всех каналов, выходные шины первого, второго и третьего каналов соединены соответственно с входной шиной «вычитаемого» сумматора третьего, первого и второго каналов.

Дешифратор содержит входной регистр, программируемое запоминающее устройство и выходной регистр, при этом вход каждого разряда входного регистра соединен с соответствующим входом дешифратора, выход входного регистра соединен с шиной адреса программируемого запоминающего устройства, шина данных которого соединена с входной шиной выходного регистра, выход каждого из разрядов которого соединен с соответствующими выходами дешифратора.

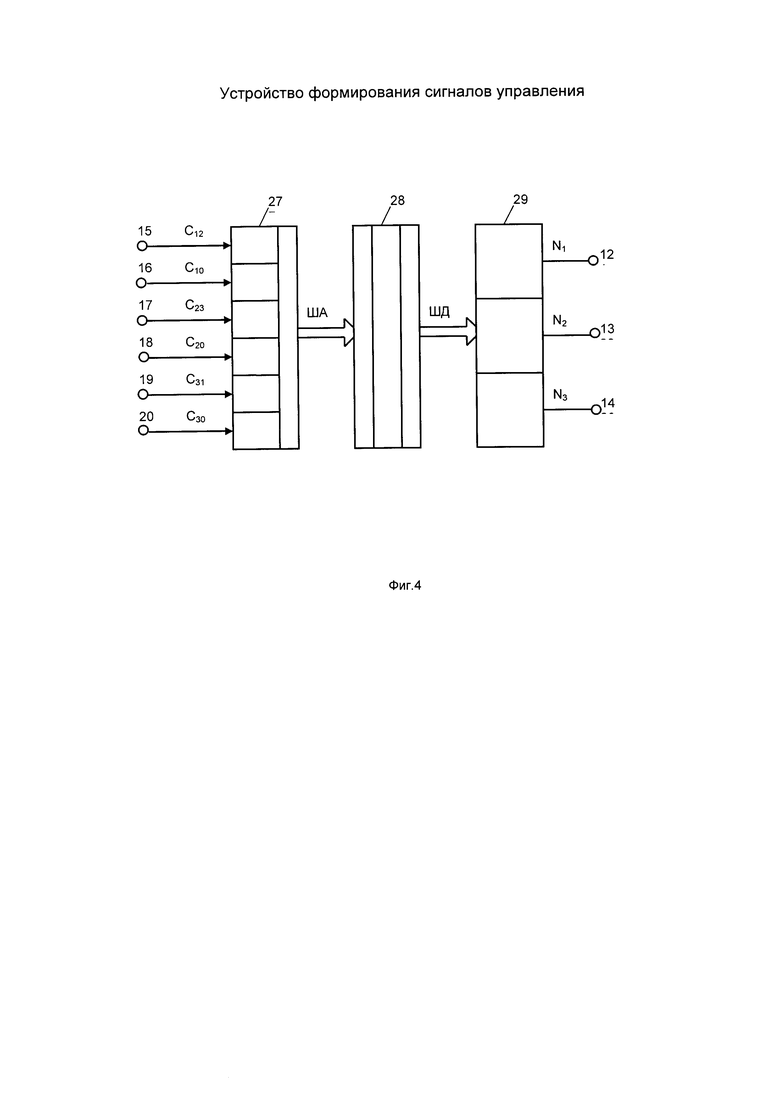

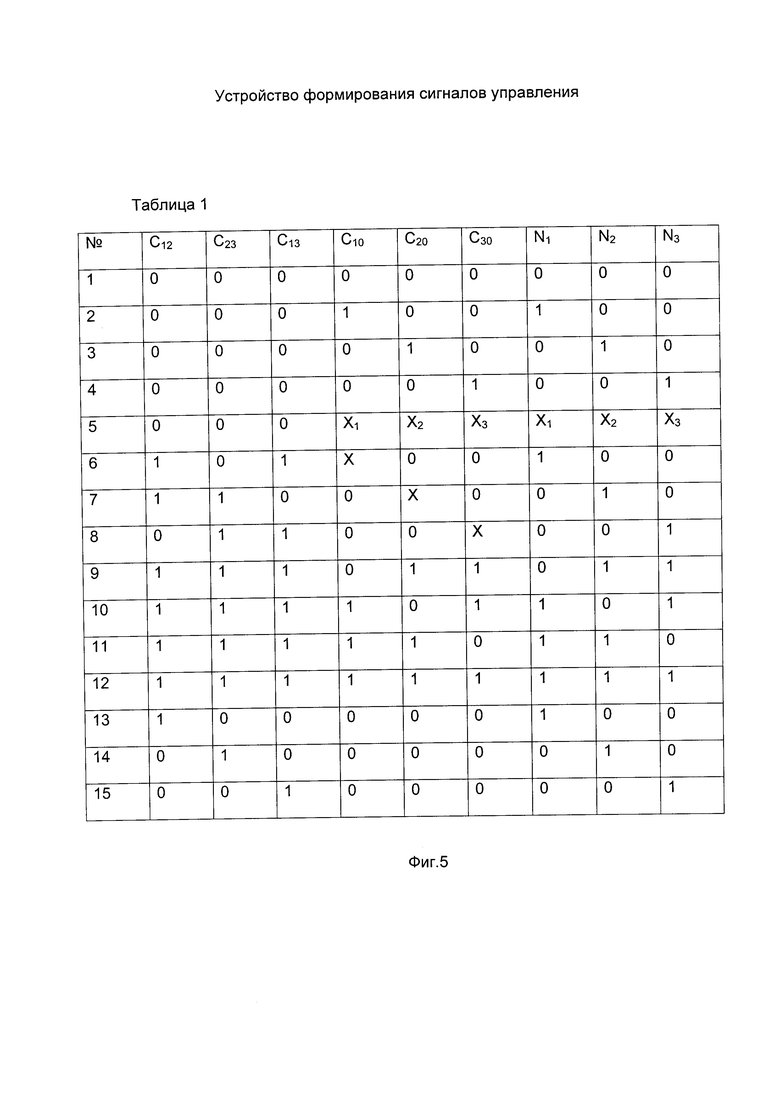

На фиг. 1 приведена блок-схема устройства формирования сигналов управления первого варианта, на фиг. 2 приведена блок-схема дешифратора первого варианта, на фиг. 3 приведена блок-схема устройства формирования сигналов управления второго варианта, на фиг. 2 приведена блок-схема дешифратора второго варианта.

На фиг. 1: 1 - входная шина, 2 - формирователь управляющих сигналов, 3 - первый цифровой компаратор, 4 - сумматор, 5 - элемент выделения модуля, 6 - второй цифровой компаратор, 7 и 8 - соответственно первый и второй выходы канала, 9 - формирователь заданного рассогласования, 10 - формирователь заданного числа, 11 - дешифратор, 12, 13 и 14 - соответственно первый, второй и третий выходы устройства, 15, 16, 17, 18, 19 и 20 - соответственно первый, второй, третий, четвертый, пятый и шестой входы дешифратора, 21, 22 и 23 - соответственно выходная шина первого, второго и третьего каналов, 24, 25 и 26 - соответственно первый, второй и третий каналы.

На фиг. 2: 12, 13 и 14 - упомянутые выходы устройства, 15, 16, 17, 18, 19 и 20 - упомянутые входы дешифратора, 27 - входной регистр, 28 - программируемое запоминающее устройство, 29 - выходной регистр.

На фиг. 1: входная шина 1 соединена с входами формирователя управляющих сигналов 2 всех каналов. В каждом канале выходная шина управления формирователя управляющих сигналов 2 соединена с входной шиной «слагаемого» сумматора 4 и выходной шиной канала, выходная шина контроля формирователя управляющих сигналов 2 соединена с шиной А первого цифрового компаратора 3, инверсный выход которого А=В соединен со вторым выходом канала 8. Выходная шина сумматора 4 соединена с входной шиной элемента выделения модуля 5, выходная шина которого соединена с шиной А второго цифрового компаратора 6, выход которого А>В соединен с первым выходом канала 7. Выход формирователя заданного числа 10 соединен с шиной В первого цифрового компаратора 3 всех каналов. Первый 7 и второй 8 выходы каждого канала соединены с соответствующими входами 15, 16, 17, 18, 19 и 20 дешифратора 11, первый, второй и третий выходы неисправности которого соединены соответственно с первым 12, вторым 13 и третьим 14 выходами устройства. Выходные шины 21, 22 и 23 первого 24, второго 25 и третьего 26 каналов соединены соответственно с входной шиной «вычитаемого» сумматора 4 третьего 26, первого 24 и второго 25 каналов.

На фиг. 2: входы каждого разряда входного регистра 27 соединены с соответствующими входами 15, 16, 17, 18, 19 и 20 дешифратора, выход входного регистра 27 соединен с шиной адреса программируемого запоминающего устройства 28, шина данных которого соединена с входной шиной выходного регистра 29, выход каждого из разрядов которого соединен с соответствующими выходами 12, и 13, 14 дешифратора.

На фиг. 3: 1 - входная шина, 2 - формирователь управляющих сигналов, 3 - первый цифровой компаратор, 4 - сумматор, 5 - элемент выделения модуля, 6 - второй цифровой компаратор, 7 и 8 - соответственно первый и второй выходы канала, 9 - формирователь заданного рассогласования, 10 - формирователь заданного числа, 11 - дешифратор, 12, 13 и 14 - соответственно первый, второй и третий выходы устройства, 15, 16, 17, 18, 19 и 20 - соответственно первый, второй, третий, четвертый, пятый и шестой входы дешифратора, 21, 22 и 23 - соответственно выходная шина первого, второго и третьего каналов, 24, 25 и 26 - соответственно первый, второй и третий каналы 30 - элемент задержки, 31 - первый мультиплексор, 32 - второй мультиплексор, 33 - регистр, 34 - коммутатор, 35 - первый резервный формирователь управляющих сигналов, 36 - m-й резервный формирователь управляющих сигналов, 37 - счетчик импульсов, 38 - элемент ИЛИ, 39 - шина неисправности устройства.

На фиг. 4: 15, 16, 17, 18, 19 и 20 - упомянутые входы дешифратора, 12, 13 и 14 - упомянутые выходы устройства, 27 - входной регистр, 28 - программируемое запоминающее устройство, 29 - выходной регистр.

На фиг. 3: входная шина 1 соединена с входами формирователя управляющих сигналов 2 всех каналов и входами всех резервных формирователей управляющих сигналов 35 и 36. В каждом канале выходная шина управления формирователя управляющих сигналов 2 соединена с основной входной шиной первого мультиплексора 31, выходная шина контроля формирователя управляющих сигналов 2 соединена с основной входной шиной второго мультиплексора 32. Выход первого мультиплексора 31 соединен с входной шиной «слагаемого» сумматора 4 и выходной шиной канала, выходная шина контроля формирователя управляющих сигналов 2 соединена с шиной А первого цифрового компаратора 3, инверсный выход которого А=В соединен со вторым выходом канала 8. Выходная шина сумматора 4 соединена с входной шиной элемента выделения модуля 5, выходная шина которого соединена с шиной А второго цифрового компаратора 6, выход которого А>В соединен с первым выходом канала 7. Выход элемента задержки 30 соединен с входом управления коммутатора 34, выход которого соединен с входом регистра 33, выходная шина которого соединена с шиной управления первого 31 и второго 32 мультиплексоров. Выходные шины управления и выходные шины контроля всех резервных формирователей управляющих сигналов 35 и 36 соединены с соответствующими резервными входами соответственно первого 31 и второго 32 мультиплексоров всех каналов. Выход формирователя заданного числа 10 соединен с шиной В первого цифрового компаратора 3 всех каналов. Первый 7 и второй 8 выходы каждого канала соединены с соответствующими входами 15, 16, 17, 18, 19 и 20 дешифратора 11, первый выход неисправности дешифратора 11 соединен с входом элемента задержки 30 первого канала 24, первым выходом устройства 12 и первым входом элемента ИЛИ 38, второй выход неисправности дешифратора 11 соединен с входом элемента задержки 30 второго канала 25, вторым выходом устройства 13 и вторым входом элемента ИЛИ 38, третий выход неисправности дешифратора 11 соединен с входом элемента задержки 30 третьего канала 26, третьим выходом устройства 14 и третьим входом элемента ИЛИ 38, выход которого соединен с входом С счетчика импульсов 37, шина кодового состояния которого соединена с входной шиной коммутатора 34 всех каналов и шиной неисправности устройства 39. Выходные шины 21, 22 и 23 первого 24, второго 25 и третьего 26 каналов соединены соответственно с входной шиной «вычитаемого» сумматора 4 третьего 26, первого 24 и второго 25 каналов.

На фиг. 4: входы каждого разряда входного регистра 27 соединены с соответствующими входами 15, 16, 17, 18, 19 и 20 дешифратора, выход входного регистра 27 соединен с шиной адреса программируемого запоминающего устройства 28, шина данных которого соединена с входной шиной выходного регистра 29, выход каждого из разрядов которого соединен с соответствующими выходами 12, 13 и 14 дешифратора.

Устройство формирования сигналов управления первого варианта (фиг. 1) работает следующим образом. Основным элементом устройства является формирователь управляющих сигналов 2, который выполняет многочисленные функции в системе управления. Так в системе управления движением космического аппарата этот блок производит обработку сигналов датчиков ориентации и перемещения, осуществляет вычисление параметров ориентации и параметров движения, формирует сигналы управления исполнительными двигателями. Этот блок в устройстве формирования управляющих сигналов является самым сложным, вследствие чего и «самым ненадежным». Безусловное выполнение задачи требует резервирования устройства формирования сигналов управления, а регистрация отказа одного из каналов позволяет значительно повысить надежность устройства.

Все каналы управления функционируют по одному и тому же алгоритму и поэтому их выходная информация не должна существенно различаться. Будем считать, что формирователь управляющих сигналов 2 имеет на своем выходе управления некоторый код, соответствующий вычисленному текущему значению сигнала управления U (некоторое число). Одновременно формирователь управляющих сигналов 2 на шине контроля формирует некоторый контрольный сигнал K в виде заданного числа путем постоянного периодического вычисления заданной функции с заранее известным результатом.

Будем предполагать, что сигнал управления U и контрольный сигнал K появляются на выходных шинах формирователя управляющих сигналов 2 периодически с некоторым периодом Т0. Сигнал U1 (для первого канала 24) поступает на входную шину «слагаемого» сумматора 4 и входную шину «вычитаемого» сумматора 4 третьего канала 26. На входную шину «вычитаемого» сумматора 4 первого канала 24 поступает сигнал U2 с выходной шины управления формирователя управляющих сигналов 2 второго канала 25. Сумматор 4 производит операцию сложения

и его выходной сигнал S1 поступает вход элемента выделения модуля 5, выходной сигнал которого |S1| определяется в виде

Выходной сигнал |S1| элемента выделения модуля 5 поступает на шину А второго цифрового компаратора 6, на шину В которого подается сигнал Δ с выхода формирователя заданного рассогласования 9. Сигнал Δ определяет допустимое рассогласование сигналов управления U1 (первый канал) и U2 (второй канал). Выходной сигнал А>В второго цифрового компаратора 6 подается на соответствующий вход 15 дешифратора 11. Если

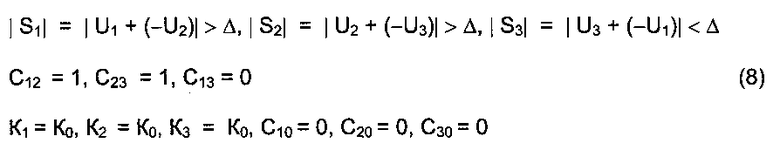

где C12 выходной сигнал второго цифрового компаратора 6.

Если

Равенство «единице» сигнала С12 свидетельствует об отказе в первом или (и) во втором каналах. Индекс «12» сигнала С12 характеризует сравнение сигналов управления первого и второго каналов.

Контрольный сигнал Κ1 (первый канал) с выходной шины контроля формирователя управляющих сигналов 2 поступает на шину А первого цифрового компаратора 3. Сигнал Κ1 представляет собой результат проведения известных вычислительных операций, характеризующих исправность основных блоков формирователя управляющих сигналов 2. На шину В первого цифрового компаратора 3 поступает сигнал K0 с выхода формирователя заданного числа 10. Сигнал K0 представляет собой известный результат проведения вычислительных операций формирователем управляющих сигналов 2. Равенство сигналов Κ1 и K0 характеризует исправную работу вычислительной части формирователем управляющих сигналов 2. Если

на инверсном выходе А=В первого цифрового компаратора 3 формируется сигнал C10=0. Этот сигнал поступает на второй вход 16 дешифратора 11. Если

то на инверсном выходе А=В первого цифрового компаратора 3 формируется сигнал C10=1. Все сказанное в равной степени относится и к остальным каналам.

Сформулируем основные соображения по возможным отказам формирователя управляющих сигналов 2. При отказе в вычислительном блоке формирователя управляющих сигналов 2, который производит вычисление всех параметров сигнала управления U, например, в первом канале 24, вычисленное им значение сигнала U1, будет существенно отличаться от вычисленных значений U2 и U3 исправно работающих второго 25 и третьего 26 каналов. В этом случае

При отказе, например, в канале приема информации второго канала 25 вычисленное блоком формирователя управляющих сигналов 2 значение сигнала U2, будет существенно отличаться от вычисленных значений U1 и U3 исправно работающих первого 24 и третьего 26 каналов. Вместе с тем, вычисленные значения контрольных сигналов Κ1, K2 и K3 будут соответствовать сигналу K0. В этом случае будут выполняться следующие соотношения

При отказе формирователей управляющих сигналов 2 в двух каналах, например, в первом 24 и во втором 25 сигналы С12, С23, С13 будут равны «единице» (сигналы управления U1, U2, U3 будут существенно отличаться друг от друга). Лишь сигнал С30=0 на выходе третьего исправно работающего канала. Иначе, в рассматриваемом случае

При отказе формирователей управляющих сигналов 2 в трех каналах сигналы C12, С23, С13 будут равны «единице» (сигналы управления U1, U2, U3 будут существенно отличаться друг от друга). Сигналы С10, С20, C30 также будут равны «единице». Иначе, в рассматриваемом случае

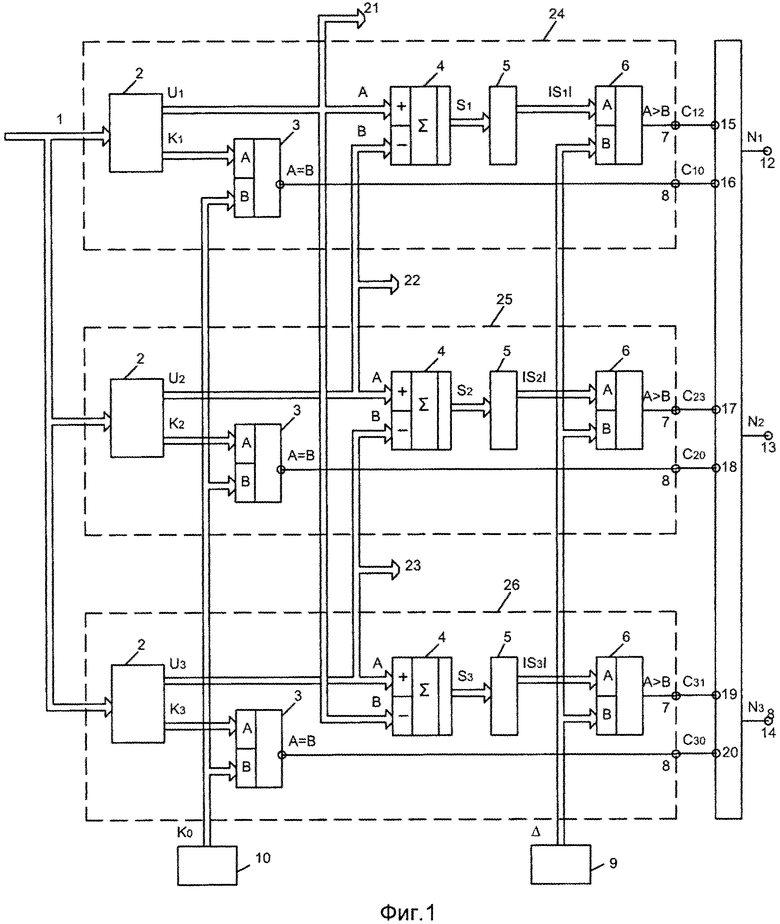

Сигналы C12, С23, C13, С10, С20, С30 поступают на вход дешифратора 11, функциональная схема которого приведена на фиг. 2. Дешифратор 11 представляет собой схему, содержащую входной регистр 27, программируемое запоминающее устройство 28 и выходной регистр 29. Упомянутые входные сигналы управляют соответствующими разрядами входного регистра 27, выходная шина которого является шиной адреса программируемого запоминающего устройства 28. Сигналы с шины данных программируемого запоминающего устройства 28 поступают на вход выходного регистра 29 и устанавливают его разряды в соответствующее состояние. Шина данных программируемого запоминающего устройства 28 содержит три разряда, состояние каждого из которых определяет неисправность соответствующего канала. Сигнал N1 на выходе устройства 12 определяет неисправность первого канала сигнал N2 на выходе устройства 13 определяет неисправность второго канала сигнал N3 на выходе устройства 14 определяет неисправность третьего канала Сигнал Ni (i=1, 2, 3) равен «нулю» при исправной работе канала, сигнал Ni равен «единице» при неисправной работе канала. Преобразование входных сигналов C12, С23, C13, С10, С20, С30 программируемым запоминающим устройством 28 в сигналы неисправности Ν1, Ν2, N3 определяется таблицей 1 (Фиг. 5).

В этой таблице сигналы X1, X2, X3 могут принимать значения «0» или «1». Равенство «нулю» сигналов С12, С23, С13 свидетельствует об исправности вычисления сигналов управления U1, U2, U3, а равенство «единице» сигналов X1, Х2, X3 свидетельствует о неисправности в определении контрольных сигналов K0, Κ1, K2 и K3. В таблице сигнал X может принимать значение «0» или «1». Значение сигналов неисправности N1, N2, N3 не зависит от значения сигнала X, так как при неисправной работе канала формирование контрольного сигнала K может быть правильным.

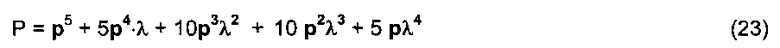

Оценим надежность известного [2] и предлагаемого устройства. В известном устройстве оценка исправности канала производится благодаря введению в каждый канал модели-подобия устройства формирования управляющего сигнала. Основным элементом устройства, определяющим его надежность, является формирователь управляющих сигналов 2. Если надежность формирователя управляющих сигналов равна p, то надежность одного канала известного устройства [2] будет равна р2. Надежность одного канала предлагаемого устройства в тех же условиях будет равна р. Оценим надежность Ρ предлагаемого и надежность P1 известного устройства при трехканальном исполнении. Каждое из устройств сохраняет свою работоспособность при любых двух отказах. Надежность Ρ и P1 определятся в виде

где λ=1-p, p1=p2, λ1=1-p1.

Пусть надежность p=0,9. Тогда Ρ=0,999, P1=0,9931. Вероятность отказа предлагаемого устройства λп=1-Ρ=0,001, вероятность отказа известного устройства λи=1-P1=0,0069. Вероятность отказа предлагаемого устройства в 6.9 раза ниже вероятности отказа известного устройства (λи/λп=6,9).

Устройство формирования сигналов управления второго варианта (фиг. 3) работает следующим образом. Основным элементом устройства является формирователь управляющих сигналов 2, который выполняет многочисленные функции в системе управления. Так в системе управления движением космического аппарата этот блок производит обработку сигналов датчиков ориентации и перемещения, осуществляет вычисление параметров ориентации и параметров движения, формирует сигналы управления исполнительными двигателями. Этот блок в устройстве формирования управляющих сигналов является самым сложным, вследствие чего и «самым ненадежным». Безусловное выполнение задачи требует резервирования устройства формирования сигналов управления, а регистрация отказа одного из каналов позволяет значительно повысить надежность устройства.

Все каналы управления функционируют по одному и тому же алгоритму и поэтому их выходная информация не должна существенно различаться. Будем считать, что формирователь управляющих сигналов 2 имеет на своем выходе управления некоторый код, соответствующий вычисленному текущему значению сигнала управления U (некоторое число). Одновременно формирователь управляющих сигналов 2 на шине контроля формирует некоторый контрольный сигнал K в виде заданного числа путем постоянного периодического вычисления заданной функции с заранее известным результатом.

Будем предполагать, что сигнал управления U и контрольный сигнал K появляются на выходных шинах формирователя управляющих сигналов 2 периодически с некоторым периодом Т0. Сигнал U1 (для первого канала 24) поступает на основную входную шину первого мультиплексора 31 и с его выхода на шину «слагаемого» сумматора 4 и входную шину «вычитаемого» сумматора 4 третьего канала 26. На входную шину «вычитаемого» сумматора 4 первого канала 24 поступает сигнал U2 с выходной шины управления формирователя управляющих сигналов 2 второго канала 25 после прохождения через первый мультиплексор 31 второго канала. Считаем, что в исходном состоянии регистры 33 всех каналов «обнулены» и выходная шина первого 31 и второго 32 мультиплексоров подключена к основной входной шине упомянутых мультиплексоров.

Сумматор 4 первого канала 24 производит операцию сложения

и его выходной сигнал S1 поступает вход элемента выделения модуля 5, выходной сигнал которого |S1| определяется в виде

Выходной сигнал |S1| элемента выделения модуля 5 поступает на шину А второго цифрового компаратора 6, на шину В которого подается сигнал Δ с выхода формирователя заданного рассогласования 9. Сигнал Δ определяет допустимое рассогласование сигналов управления U1 (первый канал) и U2 (второй канал). Выходной сигнал А>В второго цифрового компаратора 6 подается на соответствующий вход 15 дешифратора 11. Если

где C12 выходной сигнал второго цифрового компаратора 6.

Если

Равенство единице сигнала С12 свидетельствует об отказе в первом или (и) во втором каналах. Индекс «12» сигнала С12 характеризует сравнение сигналов управления первого и второго каналов.

Контрольный сигнал Κ1 (первый канал) с выходной шины контроля формирователя управляющих сигналов 2 поступает на шину А первого цифрового компаратора 3. Сигнал Κ1 представляет собой результат проведения известных вычислительных операций, характеризующих исправность основных блоков формирователя управляющих сигналов 2. На шину В первого цифрового компаратора 3 поступает сигнал K0 с выхода формирователя заданного числа 10. Сигнал K0 представляет собой известный результат проведения вычислительных операций формирователем управляющих сигналов 2. Равенство сигналов Κ1 и K0 характеризует исправную работу вычислительной части формирователем управляющих сигналов 2. Если

то на инверсном выходе А=В первого цифрового компаратора 3 формируется сигнал С10=0. Этот сигнал поступает на второй вход дешифратора 11. Если

то на инверсном выходе А=В первого цифрового компаратора 3 формируется сигнал C10=1. Все сказанное в равной степени относится и к остальным каналам.

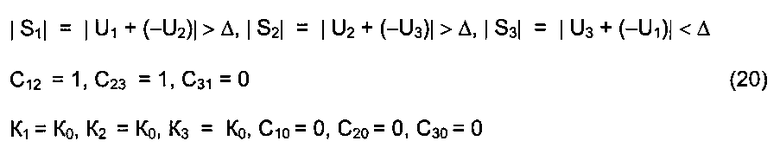

Сформулируем основные соображения по возможным отказам формирователя управляющих сигналов 2. При отказе в вычислительном блоке формирователя управляющих сигналов 2, который производит вычисление всех параметров сигнала управления U, например, в первом канале 24, вычисленное им значение сигнала U1, будет существенно отличаться от вычисленных значений U2 и U3 исправно работающих второго 25 и третьего 26 каналов. В этом случае

При отказе, например, в канале приема информации второго канала 25 вычисленное блоком формирователя управляющих сигналов 2 значение сигнала U2, будет существенно отличаться от вычисленных значений U1 и U3 исправно работающих первого 24 и третьего 26 каналов. Вместе с тем, вычисленные значения контрольных сигналов Κ1, K2 и K3 будут соответствовать сигналу K0. В этом случае будут выполняться следующие соотношения

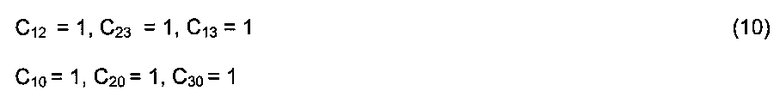

При отказе формирователей управляющих сигналов 2 в двух каналах, например, в первом 24 и во втором 25 сигналы C12, C23, С31 будут равны единице (сигналы управления U1, U2, U3 будут существенно отличаться друг от друга). Лишь сигнал С30=0 на выходе третьего исправно работающего канала. Иначе, в рассматриваемом случае

При отказе формирователей управляющих сигналов 2 в трех каналах сигналы C12, С23, С31 будут равны единице (сигналы управления U1, U2, U3 будут существенно отличаться друг от друга). Сигналы С10, С20, C30 также будут равны единице. Иначе, в рассматриваемом случае

Сигналы С12, С23, С31, C10, C20, C30 поступают на вход дешифратора 11, функциональная схема которого приведена на фиг. 4. Дешифратор 11 представляет собой схему, содержащую входной регистр 27, программируемое запоминающее устройство 28 и выходной регистр 29. Упомянутые входные сигналы управляют соответствующими разрядами входного регистра 27, выходная шина которого является шиной адреса программируемого запоминающего устройства 28. Сигналы с шины данных программируемого запоминающего устройства 28 поступают на вход выходного регистра 29 и устанавливают его разряды в соответствующее состояние. Шина данных программируемого запоминающего устройства 28 содержит три разряда, состояние каждого из которых определяет неисправность соответствующего канала. Сигнал N1 на выходе устройства 12 определяет неисправность первого канала 24, сигнал N2 на выходе устройства 13 определяет неисправность второго канала 25, сигнал N3 на выходе устройства 14 определяет неисправность третьего канала 26. Сигнал Ni (i=1, 2, 3) равен «нулю» при исправной работе канала, сигнал Ni равен «единице» при неисправной работе канала. Преобразование входных сигналов С12, С23, С31, C10, С20, C30 программируемым запоминающим устройством 28 в сигналы неисправности N1, N2, N3 определяется таблицей 2 (фиг. 6).

В этой таблице сигналы X1, Х2, Х3 могут принимать значения «0» или «1». Равенство «нулю» сигналов С12, С23, С31 свидетельствует об исправности вычисления сигналов управления U1, U2, U3, а равенство «единице» сигналов X1, Х2, Х3 свидетельствует о неисправности в определении контрольных сигналов K0, Κ1, K2 и K3. В таблице сигнал X может принимать значение «0» или «1». Значение сигналов неисправности Ν1, N2, N3 не зависит от значения сигнала X, так как при неисправной работе канала формирование контрольного сигнала K может быть правильным.

При отказе в вычислительном блоке формирователя управляющих сигналов 2 первого канала 24 в соответствии с (19) формируется на первом выходе 12 сигнал неисправности N1=1 (позиция 6 таблицы 2). В этом случае этот сигнал поступает на первый вход элемента ИЛИ 38 и далее на вход счетчика импульсов 37, изменяя его состояние на «+1». Кодовое состояние «+1» счетчика импульсов 37 поступает на шину неисправности 13 и входную шину коммутаторов 34 всех каналов. По истечении времени задержки τ3 элемента задержки 30 сигнал N1=1 с первого выхода дешифратора 11 поступает на вход управления коммутатора 34, открывает его и регистр 33 первого канала 24 устанавливается в состояние «+1». В этом случае первый 31 и второй 32 мультиплексоры первого канала 24 переключают свой выход на первый резервный вход упомянутых мультиплексоров, отключая тем самым неисправно работающий формирователь управляющих сигналов 2 первого канала 24 и подключая вместо него исправно работающий формирователь управляющих сигналов 35. В результате выходные сигналы этого формирователя UP1 и ΚP1 поступают соответственно на шину «слагаемого» сумматора 4 и шину А первого цифрового компаратора 3. После этой процедуры исправными становятся все три канала, что приводит к снятию сигнала неисправности N1 (N1=0).

При отказе, например, в канале приема информации второго канала 25 вычисленное блоком формирователя управляющих сигналов 2 значение сигнала U2, будет существенно отличаться от вычисленных значений U1 и U3 исправно работающих первого 24 и третьего 26 каналов. Вместе с тем, вычисленные значения контрольных сигналов Κ1, K2 и K3 будут соответствовать сигналу K0. Согласно (20) и таблице 2 (позиция 7) будет сформирован на втором выходе устройства 13 сигнал N2=1, что свидетельствует об отказе второго канала 25. Этот сигнал поступает на второй вход элемента ИЛИ 38 и далее на вход счетчика импульсов 37, изменяя его состояние на «+1». Кодовое состояние «+2» счетчика импульсов 37 поступает на шину неисправности 13 и входную шину коммутаторов 34 всех каналов. По истечении времени задержки τ3 элемента задержки 30 сигнал N2=1 со второго выхода дешифратора 11 поступает на вход управления коммутатора 34, открывает его и регистр 33 второго канала 25 устанавливается в состояние «+2». В этом случае первый 31 и второй 32 мультиплексоры второго канала 25 переключают свой выход на второй резервный вход упомянутых мультиплексоров, отключая тем самым неисправно работающий формирователь управляющих сигналов 2 второго канала 25 и подключая вместо него исправно работающий формирователь управляющих сигналов 35. В результате выходные сигналы этого формирователя UP1m и KP1m (m=2) поступают соответственно на шину «слагаемого» сумматора 4 и шину А первого цифрового компаратора 3. После этой процедуры исправными становятся все три канала, что приводит к снятию сигнала неисправности N2 (N2=0).

Если число резервных формирователей управляющих сигналов m=2, то дальнейшее функционирование устройства будет следующим. При очередном отказе, например, в третьем канале 26 на третьем выходе устройства 14 будет сформирован сигнал N3=1. Этот сигнал поступает на третий вход элемента ИЛИ 38 и далее на вход счетчика импульсов 37, изменяя его состояние на «+1». Новое кодовое состояние счетчика импульсов 37 «+3». По истечении времени задержки τ3 элемента задержки 30 сигнал N3=1 с третьего выхода дешифратора 11 поступает на вход управления коммутатора 34, открывает его и регистр 33 третьего канала 26 устанавливается в состояние «+3». В результате первый 31 и второй 32 мультиплексоры третьего канала 26 отключают неисправно работающий блок формирователя управляющих сигналов 2 и сигнал неисправности третьего канала остается неизменным N3=1.

При дальнейшем функционировании в случае возникновения очередного отказа будут сформированы сигналы неисправности N1=1 либо N2=1. Эти сигналы позволяют не использовать при управлении сигналы неисправного канала. Таким образом, рассматриваемое устройство обеспечивает работоспособность системы при (m+2) отказах формирователей управляющих сигналов.

Оценим надежность известного [2] и предлагаемого устройства. В известном устройстве оценка исправности канала производится благодаря введению в каждый канал модели-подобия устройства формирования управляющего сигнала. Основным элементом устройства, определяющим его надежность, является формирователь управляющих сигналов 2. Если надежность формирователя управляющих сигналов равна p, то надежность одного канала известного устройства [2] будет равна р2. Надежность одного канала предлагаемого устройства в тех же условиях будет равна р. Надежность резервного формирователя управляющих сигналов ввиду его сложности можно считать равной надежности одного канала. Оценим надежность Ρ предлагаемого и надежность P1 известного устройства при трех-канальном исполнении и при использовании двух резервных формирователей управляющих сигналов. В этом случае известное устройство содержит фактически шесть, а предлагаемое устройство пять формирователей управляющих сигналов. Известное устройство сохраняет свою работоспособность при любых двух отказах, а предлагаемое устройство при отказах четырех формирователей управляющих сигналов. Надежность Ρ и P1 определятся в виде

где λ=1-p, p1=p2, λ1=1-p1.

Пусть надежность p=0,9. Тогда Ρ=0,99999, P1=0,9931. Вероятность отказа предлагаемого устройства λп=1-Ρ=0,00001, вероятность отказа известного устройства λи=1-P1=0,0069. Вероятность отказа предлагаемого устройства в 690 раз ниже вероятности отказа известного устройства (λи/λп=690).

Предлагаемая совокупность признаков в рассмотренных авторами решениях не встречалась для решения поставленной задачи и не следует явным образом из уровня техники, что позволяет сделать вывод о соответствии технического решения критериям "новизна" и "изобретательский уровень". В качестве элементов для реализации устройства могут быть использованы стандартные цифровые компараторы, сумматоры, элементы выделения модуля, регистры, программируемые запоминающие устройства.

Литература

1. Патент Российской Федерации №2342773, Кл. H03K 17/00, 2008 г.

2. Патент Российской Федерации №2382463, Кл. Η02H 9/00, 2003 г.

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифроаналоговый преобразователь с автокалибровкой | 1989 |

|

SU1683176A1 |

| УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ ПАРАМЕТРОВ ПРОСТРАНСТВЕННОГО ПОЛОЖЕНИЯ ОБЪЕКТОВ | 2015 |

|

RU2597463C2 |

| СИСТЕМА УПРАВЛЕНИЯ КОСМИЧЕСКОГО АППАРАТА | 2013 |

|

RU2560204C2 |

| УСТРОЙСТВО ДЛЯ МАЖОРИТАРНОГО ВЫБОРА СИГНАЛОВ (3 ВАРИАНТА) | 2014 |

|

RU2580791C2 |

| Резервированная система | 1988 |

|

SU1584137A1 |

| Многоканальное устройство для регистрации | 1985 |

|

SU1322156A1 |

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ И ВОССТАНОВЛЕНИЯ ТЕХНИЧЕСКИХ СРЕДСТВ МЕДИЦИНСКОГО НАЗНАЧЕНИЯ | 1992 |

|

RU2072788C1 |

| СИСТЕМА АВТОМАТИЧЕСКОГО УПРАВЛЕНИЯ | 2013 |

|

RU2534955C1 |

| Многоканальная система измерения и регистрации | 1988 |

|

SU1707546A1 |

| РЕЛЕЙНЫЙ РЕГУЛЯТОР | 2009 |

|

RU2408046C2 |

Предлагаемая группа изобретений относится к области электронной техники и может быть использована в системах управления, где требуется высокая надежность выполнения заданного режима, например, в системах управления космическими аппаратами, в авиационной технике и в других системах. Технический результат - повышение надежности устройства формирования сигналов управления. Для этого предложено устройство формирования сигналов управления, которое содержит три канала, каждый из которых включает в себя формирователь управляющих сигналов, первый и второй цифровые компараторы, сумматор, формирователь заданного числа, формирователь заданного рассогласования и дешифратор, выполненный в виде входного и выходного регистров и программируемого запоминающего устройства. 2 н. и 2 з.п. ф-лы, 6 ил.

1. Устройство формирования сигналов управления, содержащее три канала, каждый из которых включает в себя формирователь управляющих сигналов, вход которого соединен с входной шиной, отличающееся тем, что в устройство дополнительно введены дешифратор, формирователь заданного числа и формирователь заданного рассогласования, а в каждый канал дополнительно введены сумматор, элемент выделения модуля, первый и второй цифровые компараторы, при этом выходная шина сумматора соединена с входной шиной элемента выделения модуля, выходная шина которого соединена с шиной A второго цифрового компаратора, выход которого A>B соединен с первым выходом канала, выходная шина контроля формирователя управляющих сигналов соединена с шиной A первого цифрового компаратора, инверсный выход которого A=B соединен со вторым выходом канала, выходная шина управления формирователя управляющих сигналов соединена с входной шиной «слагаемого» сумматора и выходной шиной канала, выход формирователя заданного рассогласования соединен с шиной В второго цифрового компаратора всех каналов, выход формирователя заданного числа соединен с шиной В первого цифрового компаратора всех каналов, первый и второй выходы каждого канала соединены с соответствующими входами дешифратора, первый, второй и третий выходы неисправности которого соединены соответственно с первым, вторым и третьим выходами устройства, выходные шины первого, второго и третьего каналов соединены соответственно с входной шиной «вычитаемого» сумматора третьего, первого и второго каналов.

2. Устройство формирования сигналов управления по п. 1, отличающееся тем, что дешифратор содержит входной регистр, программируемое запоминающее устройство и выходной регистр, при этом вход каждого разряда входного регистра соединен с соответствующим входом дешифратора, выход входного регистра соединен с шиной адреса программируемого запоминающего устройства, шина данных которого соединена с входной шиной выходного регистра, выход каждого из разрядов которого соединен с соответствующими выходами дешифратора.

3. Устройство формирования сигналов управления, содержащее три канала, каждый из которых включает в себя формирователь управляющих сигналов, вход которого соединен с входной шиной, отличающееся тем, что в устройство дополнительно введены m (m=1, 2, …) резервных формирователей управляющих сигналов, дешифратор, формирователь заданного числа, формирователь заданного рассогласования, счетчик импульсов, элемент ИЛИ, а в каждый канал дополнительно введены первый и второй мультиплексоры, регистр, коммутатор, элемент задержки, сумматор, элемент выделения модуля, первый и второй цифровые компараторы, при этом выходная шина сумматора соединена с входной шиной элемента выделения модуля, выходная шина которого соединена с шиной A второго цифрового компаратора, выход которого A>B соединен с первым выходом канала, выходная шина контроля формирователя управляющих сигналов соединена с основной входной шиной второго мультиплексора, выход которого соединен с шиной A первого цифрового компаратора, инверсный выход которого A=B соединен со вторым выходом канала, выходная шина управления формирователя управляющих сигналов соединена с основной входной шиной первого мультиплексора, выход которого соединен с входной шиной «слагаемого» сумматора и выходной шиной канала, выход элемента задержки соединен с входом управления коммутатора, выход которого соединен с входом регистра, выходная шина которого соединена с шиной управления первого и второго мультиплексоров, первый и второй выходы каждого канала соединены с соответствующими входами дешифратора, первый выход неисправности которого соединен с входом элемента задержки первого канала, первым входом элемента ИЛИ и первым выходом устройства, второй выход неисправности дешифратора соединен с входом элемента задержки второго канала, вторым входом элемента ИЛИ и вторым выходом устройства, третий выход неисправности дешифратора соединен с входом элемента задержки третьего канала, третьим выходом устройства и третьим входом элемента ИЛИ, выход которого соединен с входом C счетчика импульсов, выходная шина кодового состояния которого соединена с входной шиной коммутатора всех каналов и шиной неисправности устройства, выход формирователя заданного числа соединен с шиной B первого цифрового компаратора всех каналов, выход формирователя заданного рассогласования соединен с шиной B второго цифрового компаратора всех каналов, входы всех резервных формирователей управляющих сигналов соединены с входной шиной, выходные шины управления и выходные шины контроля всех резервных формирователей управляющих сигналов соединены с соответствующими резервными входами соответственно первого и второго мультиплексоров всех каналов, выходные шины первого, второго и третьего каналов соединены соответственно с входной шиной «вычитаемого» сумматора третьего, первого и второго каналов.

4. Устройство формирования сигналов управления по п. 3, отличающееся тем, что дешифратор содержит входной регистр, программируемое запоминающее устройство и выходной регистр, при этом вход каждого разряда входного регистра соединен с соответствующим входом дешифратора, выход входного регистра соединен с шиной адреса программируемого запоминающего устройства, шина данных которого соединена с входной шиной выходного регистра, выход каждого из разрядов которого соединен с соответствующими выходами дешифратора.

| КОММУТАТОР НАПРЯЖЕНИЯ | 2007 |

|

RU2382463C2 |

| СПОСОБ ФОРМИРОВАНИЯ МЕТОК ВРЕМЕНИ И УСТРОЙСТВО ДЛЯ ЕГО РЕАЛИЗАЦИИ | 2007 |

|

RU2391773C2 |

| МНОГОКАНАЛЬНЫЙ КОММУТАТОР НАПРЯЖЕНИЯ | 2007 |

|

RU2342773C1 |

| US 4156278 A1, 22.05.1979. | |||

Авторы

Даты

2016-04-10—Публикация

2014-06-27—Подача