Область техники

Изобретение относится к области прецизионного преобразования времени события в код (сокращенно - «время - код»). Такое преобразование используется для регистрации временных характеристик регулярных и нерегулярных потоков импульсов в различных физических экспериментах.

Уровень техники

Одним из известных методов преобразования «время - код» является метод считывания, предполагающий генерацию шкалы времени с квантом, равным периоду тактового генератора, и считывание состояния этой шкалы в момент входного события [1]. Мертвое время этого метода преобразования не превышает величины кванта, однако и точность этого метода преобразования ограничена этой же величиной.

Для повышения точности преобразования «время - код» используют сочетание метода считывания и метода интерполяции [2]. При этом метод считывания дает основной (грубый) результат преобразования, а интерполяция позволяет уточнить этот результат в пределах кванта и сводится к оценке фазового соотношения между входным сигналом и тактовыми импульсами. По принципу действия интерполяторы можно разделить на два класса: аналоговые и дискретные.

В основе дискретных интерполяторов [3] лежит использование цепочки линий задержек, по которой распространяется тактовый сигнал. Фиксация состояния этой цепочки в момент поступления входного сигнала позволяет определить фазовое соотношение между входным сигналом и тактовыми импульсами с точностью до шага задержки. Основным достоинством дискретных интерполяторов является минимальное мертвое время (до нескольких наносекунд), но их точность ограничена (от десятков до сотен пикосекунд).

Аналоговые интерполяторы [4, 5, 6] обеспечивают высокую точность измерений (единицы пикосекунд), но имеют существенно большее мертвое время. Принцип действия аналоговых интерполяторов основан на том, что определение фазового соотношения между входным сигналом и тактовыми импульсами производится путем выделения так называемого интервала несинхронности (длительностью от момента появления входного сигнала до ближайшего тактового импульса). Затем этот интервал несинхронности преобразуется в уровень напряжения. Возможности высокоточной оценки уровня этого напряжения определяют высокую точность аналоговой интерполяции. После преобразования уровня напряжения в код интерполятор возвращается в исходное состояние. Временные затраты от момента прихода входного сигнала и до момента возвращения интерполятора в исходное состояние составляют мертвое время интерполяции.

Наиболее близким к предлагаемому является аналоговый интерполятор, представленный на фигуре 5 [4] и содержащий генератор тока, управляемый ключ, накопительный конденсатор, транзистор сброса и аналого-цифровой преобразователь (ADC). В основе принципа действия интерполятора лежит заряд накопительного конденсатора в течение длительности интервала несинхронности, оцифровка аналогового эквивалента интервала несинхронности с помощью ADC и приведение схемы в исходное состояние импульсом по входу транзистора сброса. Подразумевается, что исходное состояние на накопительном конденсаторе поддерживается с помощью диода и дополнительного генератора тока, как это имеет место в интерполяторе на фигуре 4 [4].

Наиболее существенным недостатком известного интерполятора является большое мертвое время, уменьшить которое мешают два принципиальных обстоятельства. Во-первых, входной сигнал интерполятора и тактовые импульсы принципиально асинхронны. Известно, что одновременное или квазиодновременное воздействие сигналов по входам логического элемента (например, по С и D входам триггера) может вызвать метастабильность его выходного состояния. Для того чтобы исключить влияние метастабильности, выделение интервала несинхронности приходится производить путем двухтактной синхронизации, т.е. от момента появления входного сигнала до второго ближайшего тактового импульса [6]. Это увеличивает мертвое время на длительность такта. Во-вторых, в известных аналоговых интерполяторах принципиально необходимы временные затраты на фазы аналого-цифрового (АЦ) преобразования и возврат интерполятора в начальное состояние, что вызывает соответствующее увеличение мертвого времени интерполяции. В то же время для регистрации временных характеристик высокоинтенсивных потоков импульсов (например, при килогерцевой лазерной локации космических объектов) актуальной является задача уменьшения величины мертвого времени при сохранении высокой точности интерполяции, присущей методу аналоговой интерполяции.

Раскрытие изобретения

Задачей предлагаемого изобретения является минимизация мертвого времени интерполяции.

Технический результат достигается тем, что в интерполятор для преобразования «время - код» с малым мертвым временем, содержащий управляемый ключ, генератор положительного тока, генератор отрицательного тока, накопительный конденсатор, первый диод, тактовый генератор и аналого-цифровой преобразователь (ADC), имеющий информационные выходы, выход индикации превышения рабочего диапазона OR и тактовый вход, причем вход ключа соединен с выходом генератора положительного тока, выход ключа соединен с накопительным конденсатором, анодом первого диода, выходом генератора отрицательного тока и входом ADC, а выход тактового генератора соединен с тактовым входом ADC, с целью минимизации мертвого времени интерполяции дополнительно введены D-триггер, включенный в счетном режиме, второй диод, источники напряжения смещения первого и второго диодов и регистр с входом управления записью и информационными входами и выходами, причем входом интерполятора является счетный вход D-триггера, выход которого соединен с управляющим входом ключа, анод первого диода соединен с катодом второго диода, источники напряжения смещения первого и второго диодов соединены соответственно с катодом и анодом этих диодов, информационные выходы ADC соединены с информационными входами регистра, выход OR ADC соединен со входом управления записью регистра, выход D-триггера соединен с одним из информационных входов регистра, а информационные выходы регистра являются выходом интерполятора.

Предпочтительно, ток генератора положительного тока устанавливается равным величине 2I, ток генератора отрицательного тока устанавливается равным величине I. Так как особенностью предлагаемого интерполятора является наличие двух начальных состояний и, соответственно, двух передаточных характеристик, то таким выбором величин токов обеспечивается идентичность этих характеристик. Принцип работы интерполятора предусматривает, что уровни источников напряжения смещения первого и второго диодов устанавливаются такими, чтобы при отсутствии входных сигналов обеспечивались два начальных уровня напряжения на накопительном конденсаторе, лежащих вне верхней и нижней границы рабочего диапазона ADC.

Краткое описание чертежей

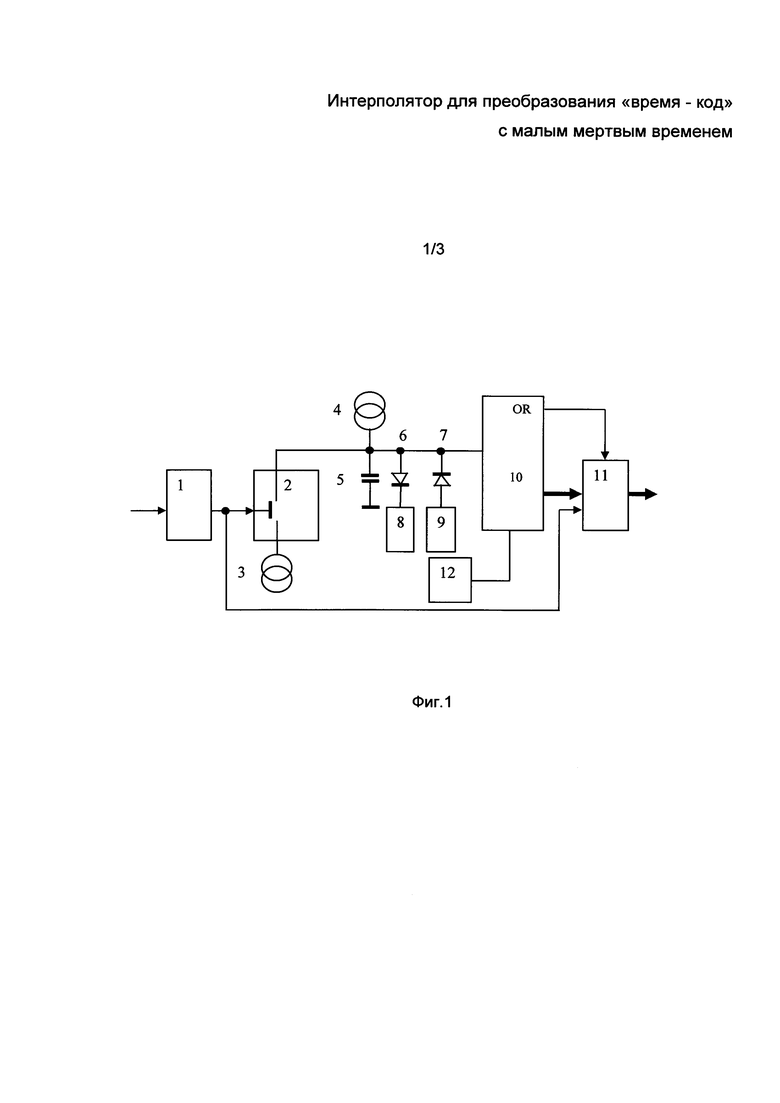

На Фиг. 1 изображена структурная схема предлагаемого устройства.

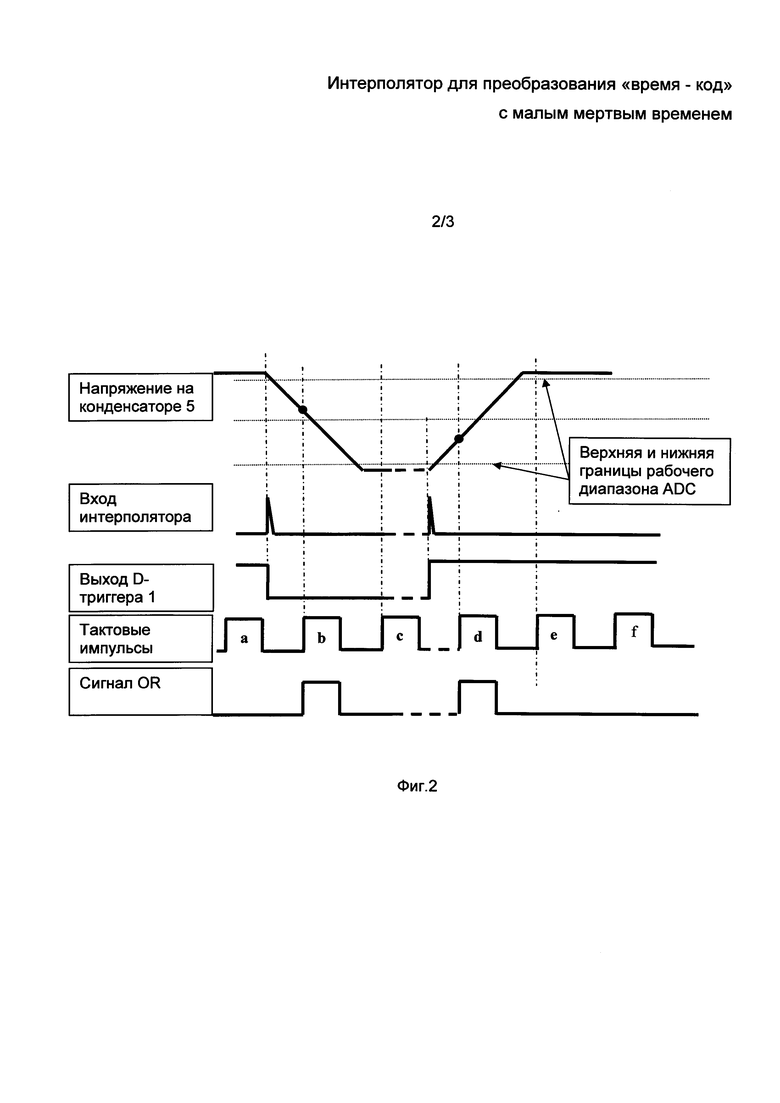

На Фиг. 2 приведена временная диаграмма, иллюстрирующая работу устройства.

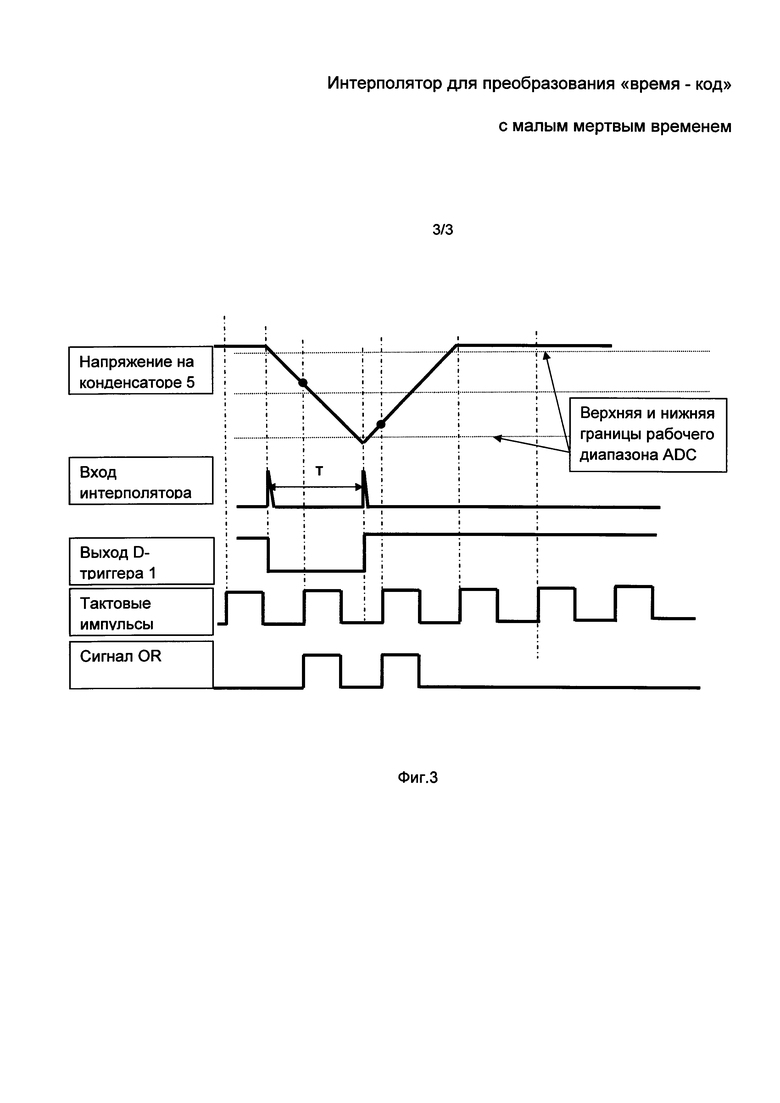

На Фиг. 3 показана временная диаграмма, соответствующая минимальному временному интервалу Т между входными импульсами.

Осуществление изобретения

На Фиг. 1 приведена структурная схема предлагаемого устройства. Интерполятор содержит D-триггер 1, включенный в счетном режиме, управляемый ключ 2, генератор 3 положительного тока величиной 2I, генератор 4 отрицательного тока величиной I, накопительный конденсатор 5, первый диод 6, второй диод 7, источник 8 напряжения смещения первого диода и источник 9 напряжения смещения второго диода, аналого-цифровой преобразователь (ADC) 10, имеющий информационные выходы, выход индикации превышения рабочего диапазона OR и вход тактирования, регистр 11 с входом управления записью и информационными входами и выходами, тактовый генератор 12. Вход интерполятора, которым является счетный вход D-триггера 1, соединен с управляющим входом ключа 2, вход которого соединен с выходом генератора 3 положительного тока величиной +2I, а выход соединен с накопительным конденсатором 5, анодом первого диода 6, катодом второго диода 7, выходом генератора 4 отрицательного тока величиной I и входом ADC 10. Источники напряжения смещения 8 и 9 первого и второго диодов 6 и 7 соединены соответственно с катодом и анодом этих диодов. Информационные выходы и выход OR ADC 10 соединены соответственно с информационными входами и входом управления записью регистра 11, а выход тактового генератора 12 соединен с входом тактирования ADC 10. Выход D-триггера 1 соединен с дополнительным информационным входом регистра 11, счетный вход D-триггера 1 является входом интерполятора, а его выходом является выход кодов регистра 11.

Реализован принцип интерполяции следующим образом. Схема имеет два начальных состояния, в зависимости от состояния выхода D-триггера 1. Рассмотрим первое начальное состояние, когда управляющий сигнал с выхода D-триггера 1 обеспечивает замыкание ключа 2 и положительный ток 2I от генератора тока 3 суммируется с отрицательным током I от генератора тока 4. Результирующий положительный ток величиной I протекает через открытый диод 6, который обеспечивает на накопительном конденсаторе начальное напряжение, равное падению напряжения на открытом диоде 6 с учетом напряжения его смещения 8. Второй диод 7 при этом закрыт. Аналого-цифровой преобразователь ADC 10 в моменты генерации сигналов тактирования от генератора 12 производит АЦ преобразование напряжения на накопительном конденсаторе 5, причем с помощью источника напряжения смещения 8 напряжение на конденсаторе 5 предварительно устанавливается за нижней границей рабочего диапазона ADC 10. Благодаря этому, при отсутствии входных событий, сигнала OR от ADC 10 нет и запись результатов АЦ преобразования в регистр 11 не производится.

В момент прихода входного события переключается D-триггер 1 и ключ 2 размыкается, отключая тем самым положительный ток 2I. Отрицательный ток I закрывает диод 6 и начинается заряд накопительного конденсатора 5, что приводит к появлению на нем линейно меняющегося напряжения. При этом напряжение на входе ADC 10 достигает его рабочего диапазона, что приводит к появлению сигнала OR в моменты тактирования ADC 10. Наличие сигнала OR разрешает запись результата АЦ преобразования в регистр 11. Значение тока I выбирается таким, чтобы сигнал на накопительном конденсаторе 5 проходил рабочий диапазон ADC 10 за время, равное длительности такта. Заряд конденсатора 5 происходит до тех пор, пока на нем не установится напряжение, равное падению напряжения на открытом диоде 7 с учетом напряжения его смещения 9 (второе начальное состояние). Первый диод 6 при этом закрыт. С помощью источника напряжения смещения 9 напряжение на конденсаторе 5 предварительно устанавливается за верхней границей рабочего диапазона ADC 10. Благодаря этому, при отсутствии входных событий, сигнала OR от ADC 10 нет и запись результатов АЦ преобразования в регистр 11 не производится.

В момент прихода последующего входного события переключается D-триггер 1 и ключ 2 замыкается, подключая тем самым положительный ток 2I. Положительный ток I закрывает диод 7 и начинается перезаряд накопительного конденсатора 5, что приводит к появлению на нем линейно меняющегося напряжения. При этом напряжение на входе ADC 10 достигает его рабочего диапазона, что приводит к появлению сигнала OR в моменты тактирования ADC 10. Наличие сигнала OR разрешает запись результата АЦ преобразования в регистр 11. Заряд конденсатора 5 происходит до тех пор, пока на нем не установится напряжение, равное падению напряжения на открытом диоде 6 с учетом напряжения его смещения 8, что соответствует переходу интерполятора в первое начальное состояние.

Особенностью предлагаемого интерполятора является наличие двух начальных состояний и, соответственно, двух передаточных характеристик. Для их различения одновременно с записью результата АЦ преобразования в регистр 11 по дополнительному информационному входу записывается текущее состояние выхода D-триггера 1.

Как видно из принципа действия интерполятора, величина выходного тока (2I) генератора положительного тока 3 и величина выходного тока (I) генератора отрицательного тока 4 выбираются так, чтобы перезаряд накопительного конденсатора 5 осуществлялся одинаковыми токами величиной I, но разного знака. Этим обеспечивается идентичность характеристик интерполятора для обоих начальных состояний.

Работа интерполятора проиллюстрирована временной диаграммой на Фиг. 2, которая начинается с первого начального состояния интерполятора, когда ключ 2 замкнут. Аналого-цифровой преобразователь ADC 10 в момент прихода тактового импульса а производит АЦ преобразование напряжения на накопительном конденсаторе 5, однако уровень этого напряжения находится за нижней границей рабочего диапазона ADC 10, сигнал OR не генерируется и запись результата АЦ преобразования в регистр 11 не производится. В момент прихода входного события переключается D-триггер 1 и ключ 2 размыкается, что приводит к появлению на накопительном конденсаторе 5 линейно меняющегося напряжения. Так как в момент прихода тактового импульса b напряжение на входе ADC 10 будет в границах его рабочего диапазона, то ADC 10 генерирует сигнал OR и производится запись результата АЦ преобразования в регистр 11. Как видно из временной диаграммы, результат этого АЦ преобразования является результатом интерполяции, так как позволяет определить фазовое соотношение между входным сигналом и тактом. К моменту прихода следующего тактового импульса с интерполятор находится во втором начальном состоянии и запись этого результата АЦ преобразования в регистр 10 не производится.

В таком состоянии интерполятор может находиться сколь угодно долго, до момента прихода очередного входного события, когда переключится D-триггер 1, и на накопительном конденсаторе 5 появится линейно меняющееся напряжение. К моменту прихода тактового импульса d напряжение на входе ADC 10 будет в границах его рабочего диапазона, что обеспечивает генерацию сигнал OR и запись результата АЦ преобразования в регистр 11. Как видно из временной диаграммы, результат этого АЦ преобразования также является результатом интерполяции, так как позволяет определить фазовое соотношение между входным сигналом и тактом. Затем интерполятор переходит в первое начальное состояние. При этом, хотя ADC 10 в моменты прихода тактовых импульсов е и f производит АЦ преобразование, но запись этих результатов в регистр 11 не производится.

На Фиг. 3 показана ситуация, соответствующая минимальному временному интервалу Т между входными импульсами. Этот интервал определяет мертвое время интерполятора. Как видно из временной диаграммы, длительность этого интервала равна времени перехода интерполятора из одного начального состояния в другое. Так как значение тока I выбирается таким, чтобы сигнал на накопительном конденсаторе 5 проходил рабочий диапазон ADC 10 за время длительности такта, то и мертвое время интерполятора получается близким к этой величине.

Преимуществом предлагаемого изобретения является то, что в процессе интерполяции практически исключаются непроизводительные затраты времени. К непроизводительным затратам в известных аналоговых интерполяторах можно отнести временные затраты на двухтактную синхронизацию при выделении интервала несинхронности и на фазу возврата интерполятора в начальное состояние.

В предложенном устройстве интерполяции нет явного выделения интервала несинхронности, поэтому отпадает необходимость в двухтактной синхронизации и связанных с этим временных затрат. Характерная для прототипа фаза возврата интерполятора в начальное состояние совмещена с фазами измерения и исключена из алгоритма работы интерполятора. В результате получается, что минимальный временной интервал между входными импульсами (мертвое время интерполятора) близок по величине к периоду тактового генератора. Представляется, что это минимальное время, которое может быть достигнуто при аналоговом принципе интерполяции.

Источники информации

1. Th. L. Bunn, W.S. Woodward, Т. Baer Design and operation of a 12.5-ns multichannel scaler. Rev. Sci. Instrum., 55 (1984), No. 11, 1849-1853.

2. Määttä K., Kostamovaara J. A High-Precision Time-to-Digital Converter for Puised Time-of-Flight Laser Radar Applications. IEEE Transactions on Instrumentation and Measurement, vol. 47 (1998), No. 2, 521-536.

3. US Patent 4439046. David R. Hoppe. Time Interpolator. 27.03.1984.

4. Kalisz J. Reviev of metods for time interval measurements with picosecond resolution. Metrologia, vol. 41 (2004), 17-32.

5. US Patent 8324952. Lewis W Masters. Time Interpolator Circuits. 04.12.2012.

6. US Patent 8064293. Sassan Tabatabaei. High Rasolution Time Interpolator. 22.11.2011.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для измерения временных интервалов | 1985 |

|

SU1293692A1 |

| ПРЕОБРАЗОВАТЕЛЬ ВРЕМЯ-КОД | 2005 |

|

RU2303803C2 |

| Измеритель временных интервалов | 1985 |

|

SU1307444A1 |

| Преобразователь кода во временной интервал | 1985 |

|

SU1300637A1 |

| Линейный интерполятор | 1982 |

|

SU1075276A1 |

| Времяимпульсный амплитудный преобразователь | 1986 |

|

SU1435131A1 |

| ПРЕОБРАЗОВАТЕЛЬ НАПРЯЖЕНИЯ В ИНТЕРВАЛ ВРЕМЕНИ | 1991 |

|

RU2032269C1 |

| Измеритель длительности импульсов | 1990 |

|

SU1714535A1 |

| Преобразователь напряжения в интервал времени | 1985 |

|

SU1285599A1 |

| Цифровой линейный интерполятор | 1988 |

|

SU1624406A1 |

Изобретение относится к области прецизионного преобразования времени события в код (сокращенно - «время - код»). Интерполятор содержит управляемый ключ, генератор положительного тока, генератор отрицательного тока, накопительный конденсатор, первый диод, тактовый генератор и аналого-цифровой преобразователь (ADC), имеющий информационные входы, выход индикации превышения рабочего диапазона OR и тактовый вход. Причем вход ключа соединен с выходом генератора положительного тока, выход ключа соединен с накопительным конденсатором, анодом первого диода, выходом генератора отрицательного тока и входом ADC, а выход тактового генератора соединен с тактовым входом ADC. Кроме того, введены D-триггер, включенный в счетном режиме, второй диод, источники напряжения смещения первого и второго диодов и регистр с входом управления записью и информационными входами и выходами. При этом входом интерполятора является счетный вход D-триггера, выход которого соединен с управляющим входом ключа, анод первого диода соединен с катодом второго диода, источники напряжения смещения первого и второго диодов соединены соответственно с катодом и анодом этих диодов, информационные выходы ADC соединены с информационными входами регистра, выход OR ADC соединен со входом управления записью регистра, выход D-триггера соединен с одним из информационных входов регистра, а информационные выходы регистра являются выходом интерполятора. Технический результат заключается в минимизации мертвого времени интерполяции. 1 з.п. ф-лы, 3 ил.

1. Интерполятор для преобразования «время - код» с малым мертвым временем, содержащий управляемый ключ, генератор положительного тока, генератор отрицательного тока, накопительный конденсатор, первый диод, тактовый генератор и аналого-цифровой преобразователь (ADC), имеющий информационные выходы, выход индикации превышения рабочего диапазона OR и тактовый вход, причем вход ключа соединен с выходом генератора положительного тока, выход ключа соединен с накопительным конденсатором, анодом первого диода, выходом генератора отрицательного тока и входом ADC, а выход тактового генератора соединен с тактовым входом ADC, отличающийся тем, что с целью минимизации мертвого времени интерполяции он дополнительно содержит D-триггер, включенный в счетном режиме, второй диод, источники напряжения смещения первого и второго диодов и регистр с входом управления записью и информационными входами и выходами, причем входом интерполятора является счетный вход D-триггера, выход которого соединен с управляющим входом ключа, анод первого диода соединен с катодом второго диода, источники напряжения смещения первого и второго диодов соединены соответственно с катодом и анодом этих диодов, информационные выходы ADC соединены с информационными входами регистра, выход OR ADC соединен со входом управления записью регистра, выход D-триггера соединен с одним из информационных входов регистра, а информационные выходы регистра являются выходом интерполятора.

2. Интерполятор по п. 1, отличающийся тем, что ток генератора положительного тока установлен величиной 2I, ток генератора отрицательного тока установлен величиной I, а уровни источников напряжения смещения первого и второго диодов устанавливаются такими, чтобы при отсутствии входных сигналов обеспечивались два начальных уровня напряжения на накопительном конденсаторе, лежащих вне верхней и нижней границы рабочего диапазона ADC.

| US 8064293 B2, 22.11.2011 | |||

| US 8324952 B2, 04.12.2012 | |||

| US 4439046 A, 27.03.1984 | |||

| US 7737875 B2, 15.06.2010 | |||

| Функциональный интерполятор | 1981 |

|

SU991374A1 |

Авторы

Даты

2016-05-20—Публикация

2015-04-17—Подача