стей интерполятора за счет отработки горизонтальных и вертикальных отрезков прямых. Интерполятор содержит регистры 1 и 2 координатных приращений, блок 3 сравнения, входной коммутатор 4, блок 5 выделения нулевого состояния, блок 6 управления, делитель 7 координатных приращений, двоичный 8 и накопительный 9 сумматоры, коммутаторы 10-12. Отличительной особенностью предлагаемого интерполятора является возможность отработки координатных и вертикальных отрезков прямых, что стало возможным за счет введения блока 5 выделения нулевого состояния и третьего 11 коммутатора. При нулевом меньшем приращении, что соответствует отработке горизонтальных и вертикальных отрезков прямых, нулевой управляющий сигнал с выхода блока 5 выделения нулевого состояния открывает третий коммутатор 11 для прохождения значения большего приращения с его г о- рсго входа на выходи последующе/ записи во внешнее устройство. 3 ил.

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой линейный интерполятор | 1986 |

|

SU1310779A1 |

| Цифровой линейный интерполятор | 1989 |

|

SU1693592A1 |

| Линейный интерполятор | 1985 |

|

SU1298714A1 |

| Цифровой линейный интерполятор | 1991 |

|

SU1807450A1 |

| Интерполятор | 1987 |

|

SU1596346A1 |

| Линейный интерполятор | 1987 |

|

SU1439532A1 |

| Цифровой линейный интерполятор | 1989 |

|

SU1675849A1 |

| Цифровой линейный интерполятор | 1990 |

|

SU1805449A1 |

| Цифровой линейный интерполятор | 1987 |

|

SU1434406A1 |

| Графический интерполятор | 1985 |

|

SU1401509A1 |

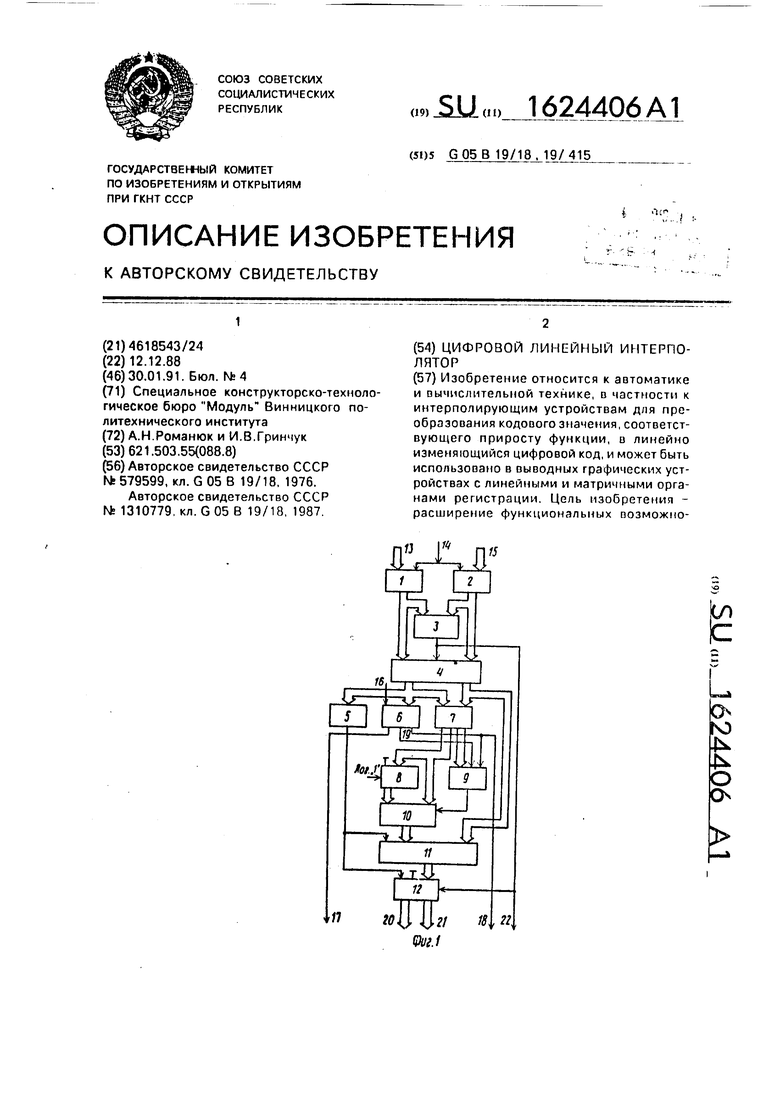

Изобретение относится к автоматике и вычислительной технике, в частности к интерполирующим устройствам для преобразования кодового значения, соответствующего приросту функции, в линейно изменяющийся цифровой код, и может быть использовано в выводных графических устройствах с линейными и матричными органами регистрации. Цель изобретения - расширение функциональных возможно

Изобретение относится к автоматике и вычислительной технике и может быть использовано в выводных графических устройствах с линейными и матричными органами регистрации, а также в станках с числовым программным управлением, в которых используются линейные и матричные исполнительные органы.

Целью изобретения является расширение функциональных возможностей интер- полятора за счет обработки горизонтальных и вертикальных отрезков прямых.

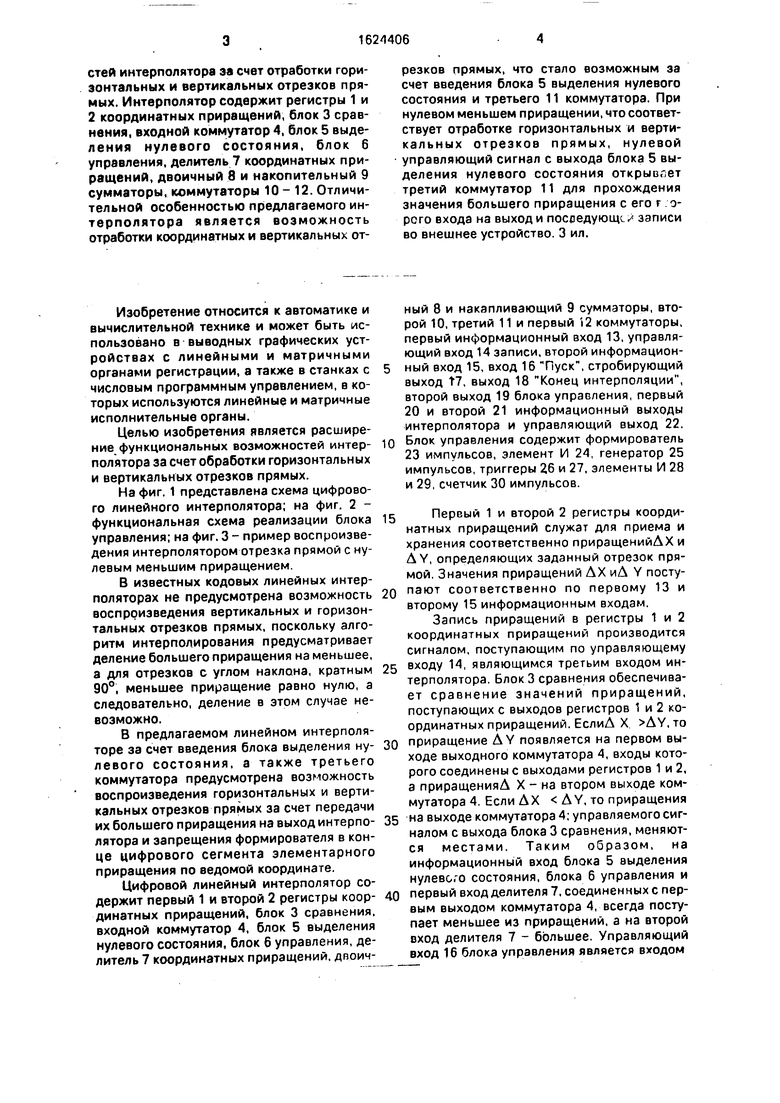

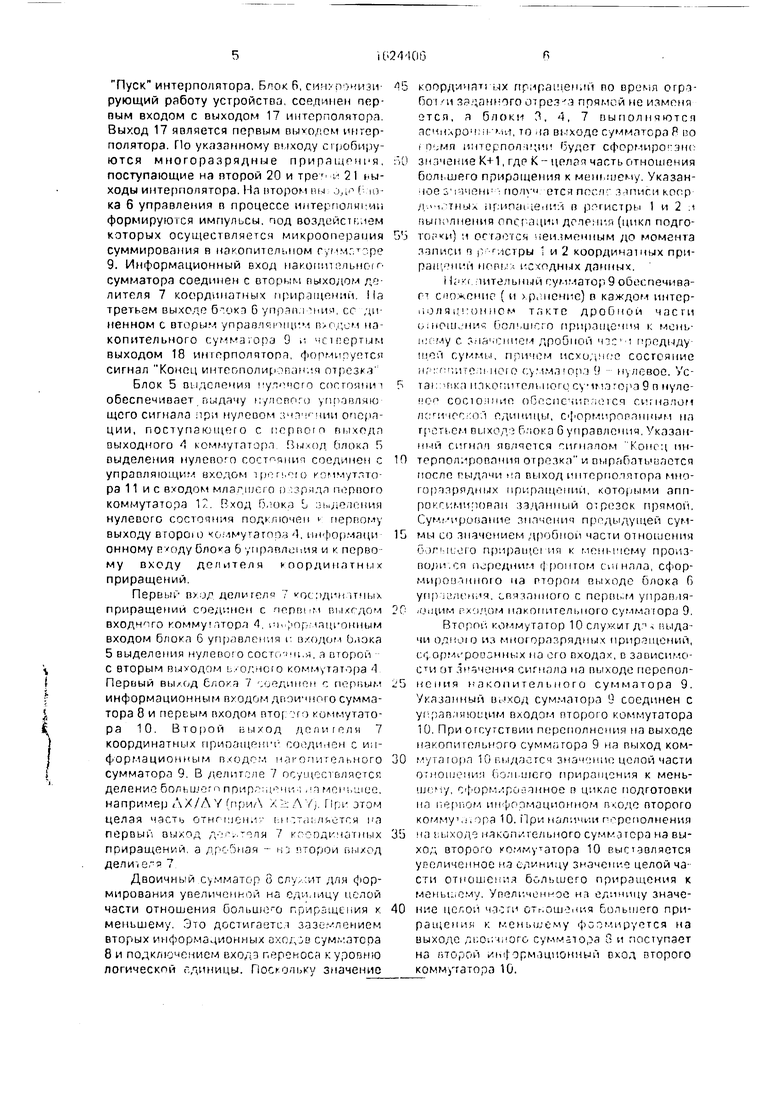

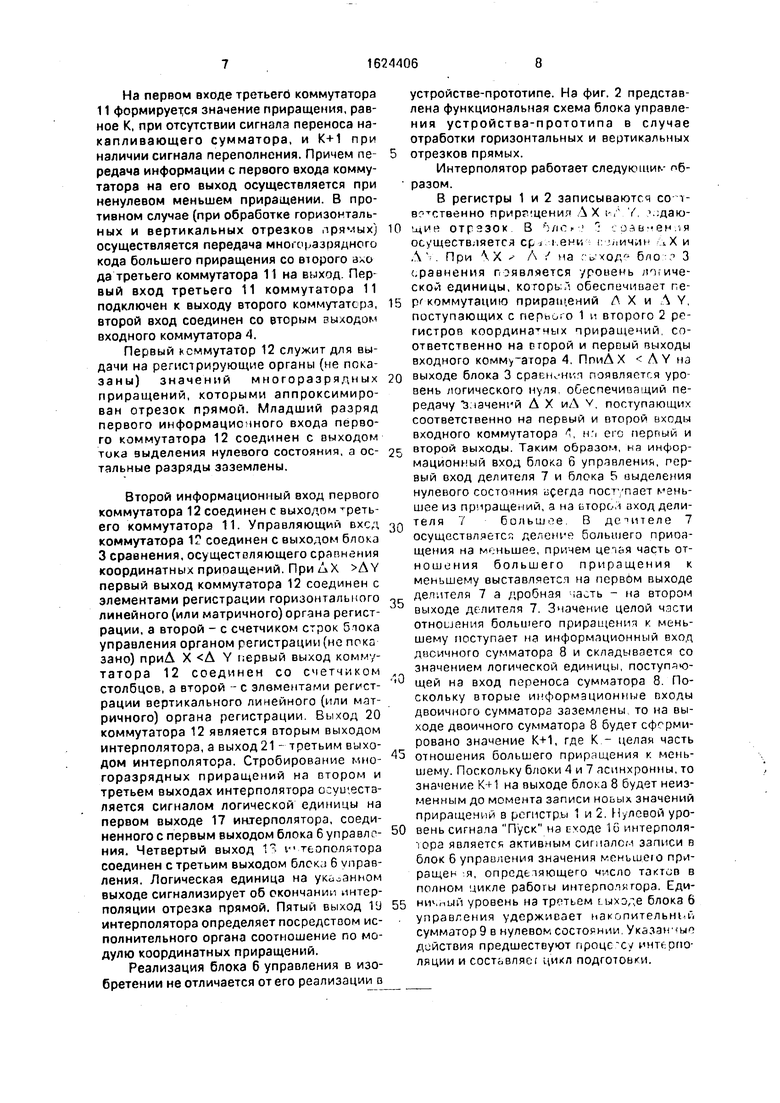

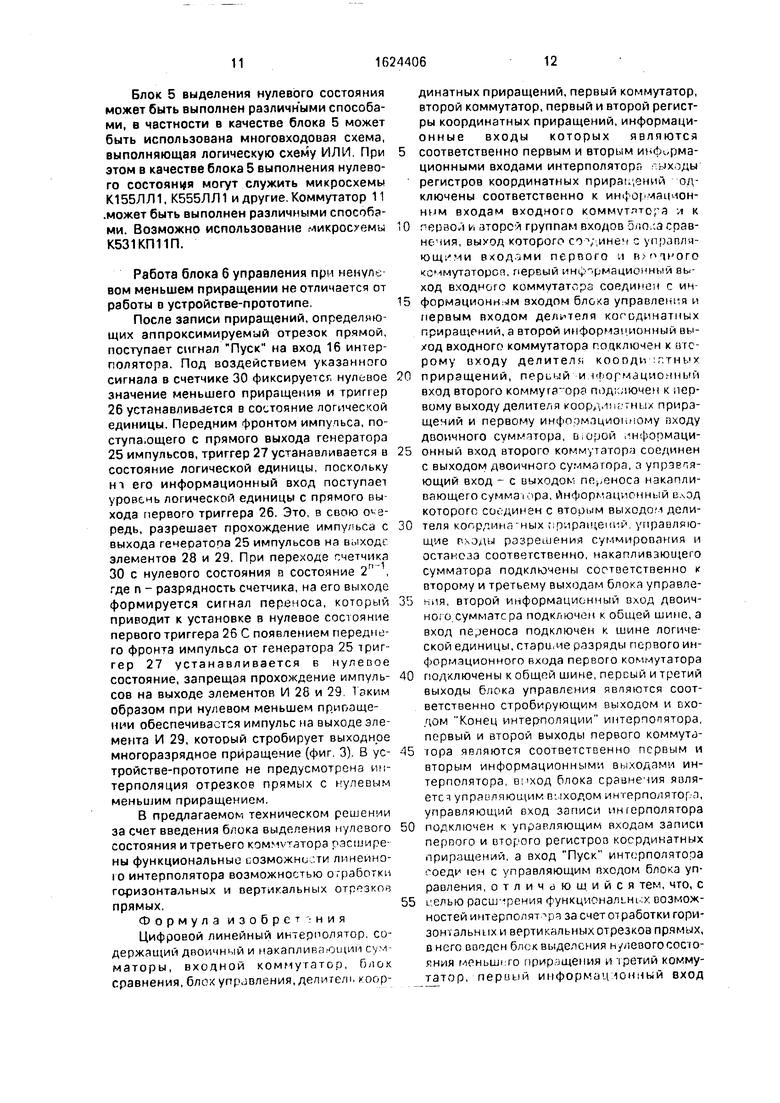

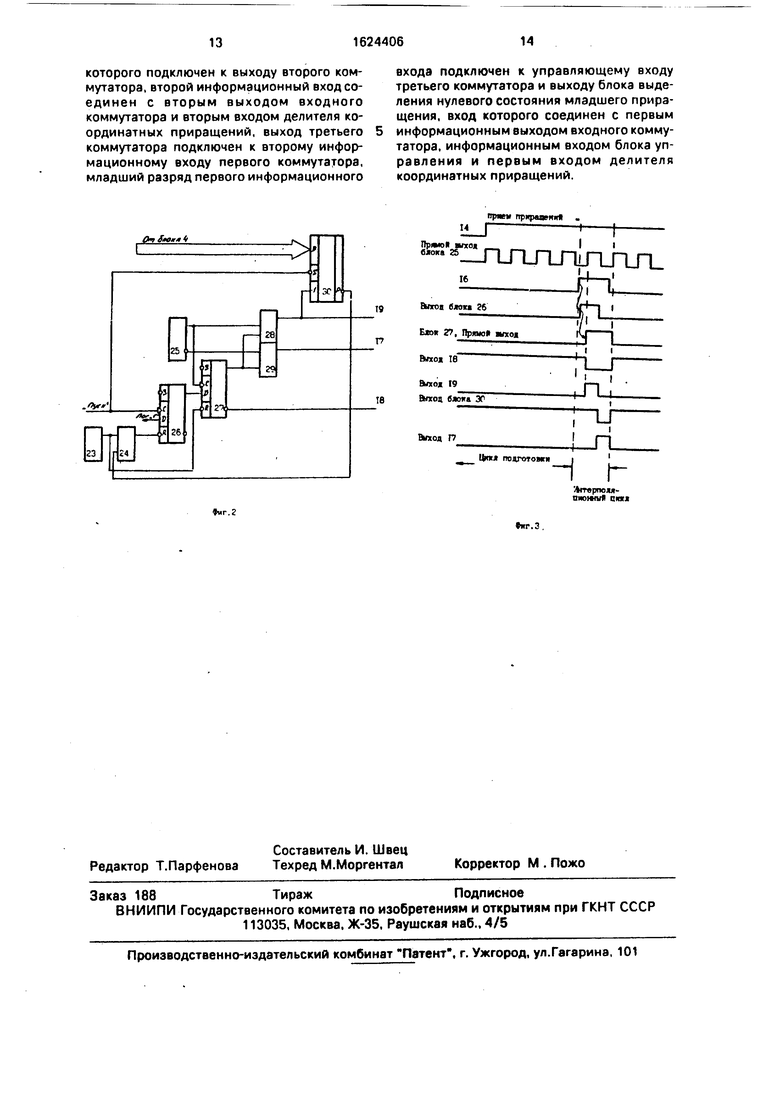

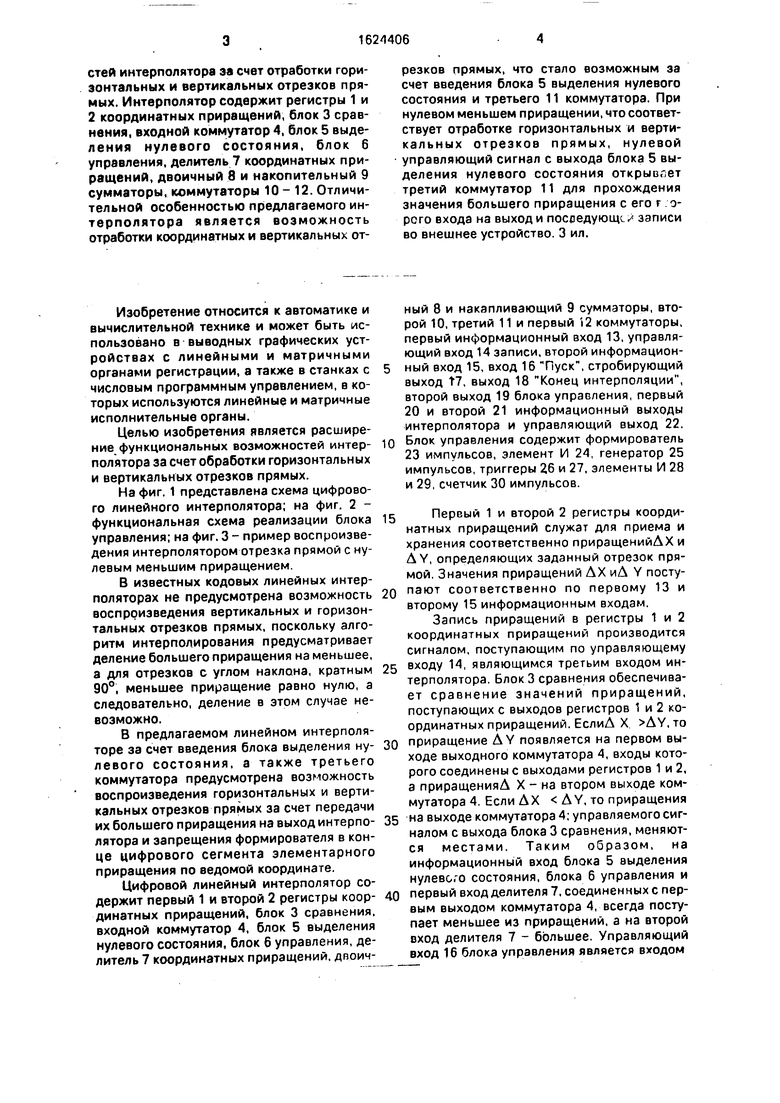

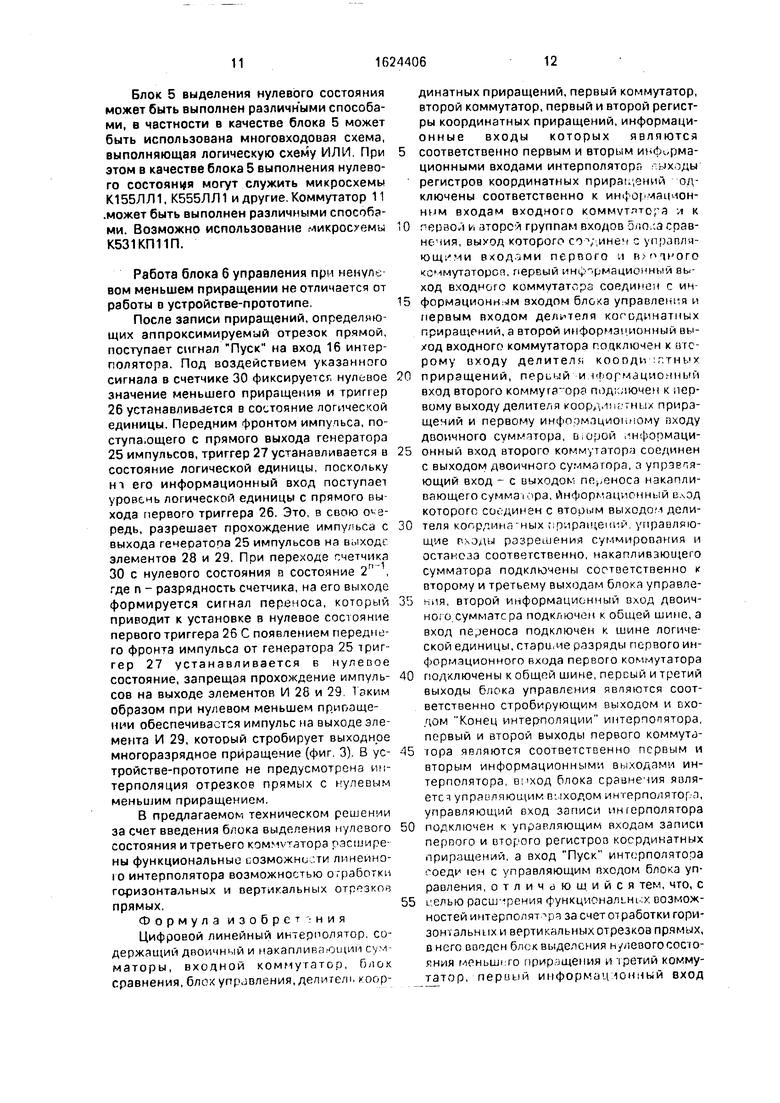

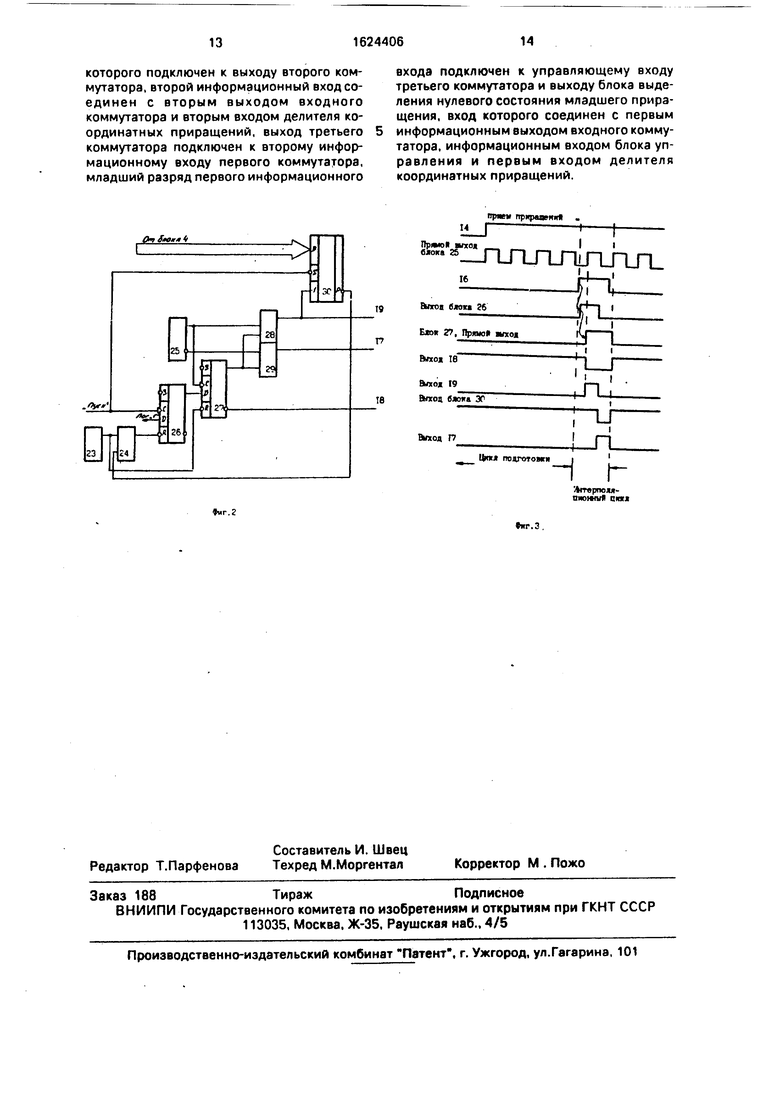

На фиг. 1 представлена схема цифрового линейного интерполятора; на фиг. 2 - функциональная схема реализации блока управления; на фиг. 3 - пример воспроизведения интерполятором отрезка прямой с нулевым меньшим приращением.

В известных кодовых линейных интерполяторах не предусмотрена возможность воспроизведения вертикальных и горизонтальных отрезков прямых, поскольку алгоритм интерполирования предусматривает деление большего приращения на меньшее, а для отрезков с углом наклона, кратным 90°, меньшее приращение равно нулю, а следовательно, деление в этом случае невозможно.

В предлагаемом линейном интерполяторе за счет введения блока выделения ну- левого состояния, а также третьего коммутатора предусмотрена возможность воспроизведения горизонтальных и вертикальных отрезков прямых за счет передачи их большего приращения на выход интерпо- лятора и запрещения формирователя в конце цифрового сегмента элементарного приращения по ведомой координате.

Цифровой линейный интерполятор содержит первый 1 и второй 2 регистры коор- динатных приращений, блок 3 сравнения, входной коммутатор 4, блок 5 выделения нулевого состояния, блок 6 управления, делитель 7 координатных приращений, двоичный 8 и накапливающий 9 сумматоры, второй 10, третий 11 и первый 2 коммутаторы, первый информационный вход 13, управляющий вход 14 записи, второй информационный вход 15, вход 16 Пуск, стробирующий выход 17, выход 18 Конец интерполяции, второй выход 19 блока управления, первый 20 и второй 21 информационный выходы интерполятора и управляющий выход 22. Блок управления содержит формирователь 23 импульсов, элемент И 24, генератор 25 импульсов, триггеры 2.6 и 27, элементы И 28 и 29, счетчик 30 импульсов.

Первый 1 и второй 2 регистры координатных приращений служат для приема и хранения соответственно приращенийАХ и Д Y, определяющих заданный отрезок прямой, Значения приращений ДХ иД Y поступают соответственно по первому 13 и второму 15 информационным входам.

Запись приращений в регистры 1 и 2 координатных приращений производится сигналом, поступающим по управляющему входу 14, являющимся третьим входом интерполятора. Блок 3 сравнения обеспечивает сравнение значений приращений, поступающих с выходов регистров 1 и 2 координатных приращений. ЕслиД X ДУ, то приращение Д Y появляется на первом выходе выходного коммутатора 4, входы которого соединены с выходами регистров 1 и 2, а приращенияД X - на втором выходе коммутатора 4. Если ДХ Д Y, то приращения на выходе коммутатора 4; управляемого сигналом с выхода блока 3 сравнения, меняются местами. Таким образом, на информационный вход блока 5 выделения нулевого состояния, блока 6 управления и первый вход делителя 7, соединенных с первым выходом коммутатора 4, всегда поступает меньшее из приращений, а на второй вход делителя 7 - большее. Управляющий вход 16 блока управления является входом

Пуск интерполятора. Блок б,сич г /низи рующий работу устройства соединен первым входом с выходом 17 интерполятора Выход 17 является первым выводом интерполятора. По указанному вчходу сгробиру- ются многоразрядные приращения, поступающие на второй 20 и трег „ 21 иы- ходы интерполятора. На втором вы ,f п ка 6 управления в процессе т формируются импульсы, под возденет г.ием которых осуществляется микроопераиия суммирования в накопительном г, 9. Информационный вход накопительною сумматора соединен с вторым выходом де лителя 7 координатных приращении На третьем выходе 6 упрчп i чиы ее ди пенном С вторым упоаотпощим в/г на копительного с.дMjiopj 9 .1 чстертым выходом 18 интерполятора формипу тся сигнал Конец интеополиртпан..я отрезк.э

Блок 5 выделения согтояьи обеспечивает выдачу пгпвляю щсго сигнала .три нулевом : чип операции, поступающего с первого выхода выходного Л коммутатор блока F выделения нулевого состояния соединен с управляющим входом п pt г,го к°ммут то рэ 11 и с вводом млаг1исго и зрядл первого коммутэтора 1 Рход П, ока L .Ь.Р.КНИЯ нулевого состояния подключен первому выходу Bropoi о ко 1мутэгпоа . пнформаци онному Р оду 6 управления и к перво му входу делителя координатных приращений

Первый в JP делигело 7 TJCIWH .тчых приращении соединен с перрл-м выхгдом входного комму -.тора 4 гь пр чацнонным входом блока 6 управления i входом Ьлока 5 выделения нулевого сосгч и я, л второй с вторым выводом L-одного коммутатора 1 Первый вы/од блока 7 .и динон с информационныг входом двоичною сумматора 8 и первым входом птог; ч-) киммутэто- ра 10 Второй выход до пи г ел я 7 координатных припащенп- соединен с информационным nai-огнпельного сумматора 9 В делителе 7 ос/щсствляется деление большего прирг .ни , ,n MeHi.aiue. например Л//ЛУ при/ Л (} Пги этом целая часть отнгпснл i н-.-л; па

ПерВЫЬ ВЫ/ОД Д -.ЛЯ 7 У( ОДГЧОГНЫХ

приращений а лр.нач - ь ьыход деликт 7

Двоичный сумматор 8 слу ит для формирования увеличенной на едп ыцу целой части отношения большего г,рирсще.иия к меньшему Это достигаезтс заземлением вторых информационных ,:в сум.-.-атсоа 8 и подключением входт переноса к уровню логической гдиницы. Поскольку значение

5 координат НУ прирапен.ш во opesin огрт- Гют и зя ;ан ого прямой не изменп отел, а блоки 3, 4, 7 выполняются .рои ii ми, то ia Bi ходе сумматора Р во t гт.мп интерпол ip;i i будет сформирован

1 значение К+1, ГДР К- целая часть отношения

бол- шего приращения к мет тему Указан),1чен1 етслпгсп читигикогр

j 1 ТНЫА iifnnai idtii 1 о регистры 1 и 2 i

nHib neiinB rnet ации дпенип (цикл подго 5 тсн ки) и остается 1еи менным до момента л-зписи п | г,-;сгры и 2 координатных при- paii /Mii H новь1, исходных данных.

тительныи гумматорЭ обеспечива- f сношение ( и р пение) в каждом интер- ноля чжнем такте дробной части ь,noiLK нис () прпращечия к мень .ч му с j-ifi iein CM дробной i средыду шей сумгш, причем нсхи,(чг С состояние нг ,.ITO ц ною с мма on j Ч нулевое. Уст ТЭ1 fKd ткопптелиюгс с и эгО|1з 9 п нуле- с сосютир пбесмс 1иг iCicn птнатои лсги(е1- о i единицы, сформнрпрлнпым на ем выход э б юка 6 управления Указан- ннй сигнач является гигнапом Конец пн0 терполировлиия отрезка и вырабатывается после гыдлчи са BLIXO/I 1 нтерпоплтора мнп- гор прядных приращении, которыми апп- рои им1гн)ран пцанный отр(%зок прямой, Cyffnpofjanne зшчения прпдыдущей сумС мы со значением дробной части отношения )г ц его прираще ия к пенимему производи ел передним с|)оптом сигнала, сформированного на гторог/1 выходе блока Г упр лмен. я сггплнного с перв1 м управ 1ЯГ ищим АГ)ОГИ накопительного сумма гора 9 Второй, коммутатор Юслухитд1, иыда чи одною из мносоратрядных приращений, t ; орг 1 роозннь:х но его входа/, в зависимости от зидчения сигнала на выходе перепол5 нения накопительного сумматора 9. Указанный гк код сумматора 9 соединен с yt pan шкнчим входом пторого коммутатора 10 При отсутствии переполнения на выходе накопительного сумматора 9 на выход ком0 мутагора Юг.ыдастся целой части oriioiueHU i do/iruiero приращения к мень- iu( у, ofорг .-ролнное п цикле подготовки на пчрьом ин ропмациокном второго комму , эра 10. При наличии г реполнения

i3 HJI и холэ накопительного су мг зтора на выход второго коммутатора 10 выставляется улеличснное на единицу значение целой ча сти отношения большего приращения к мены..ем/ Увеличенное н i единицу значе0 ние целой чт:ги отг.ош нич большего приращения к меньшему фот ми руст с я на выходе Д1.о.много сумматора 3 и поступает на ьторой ,зционный вход второго коммутатора 10.

На первом входе третьего коммутатора 11 формируется значение приращения, равное К, при отсутствии сигнала переноса накапливающего сумматора, и К+1 при наличии сигнала переполнения. Причем передача информации с первого входа коммутатора на его выход осуществляется при ненулевом меньшем приращении. В противном случае (при обработке горизонтальных и вертикальных отрезков прямых) осуществляется передача многоразрядного кода большего приращения со вюрого ахо да третьего коммутатора 11 на выход. Первый вход третьего 11 коммутатора 11 подключен к выходу второго коммутатора, второй вход соединен со вторым выходом входного коммутатора 4.

Первый коммутатор 12 служит для выдачи на регистрирующие органы (не показаны) значений многоразрядных приращений, которыми аппроксимирован отрезок прямой. Младший разряд первого информационного входа первого коммутатора 12 соединен с выходом тока выделения нулевого состояния, а остальные разряды заземлены.

Второй информационный вход первого коммутатора 12 соединен с выходом треть- его коммутатора 11. Управляющий вхсд коммутатора 12 соединен с выходом блока 3 сравнения, осуществляющего сравнения координатных приоащений. При АХ Д Y первый выход коммутатора 12 соединен с элементами регистрации горизонтального линейного (или матричного) органа регистрации, а второй - с счетчиком строк бтока управления органом регистрации (не пока зано) приЛ X Д Y первый выход коммутатора 12 соединен со счетчиком столбцов, а второй - с элементами регистрации вертикального линейного (или матричного) органа регистрации. Выход 20 коммутатора 12 является вторым выходом интерполятора, а выход 21 - третьим выходом интерполятора. Стробирование многоразрядных приращений на втором и третьем выходах интерполятора осуществляется сигналом логической единицы на первом выходе 17 интерполятора, соединенного с первым выходом блока 6 управления. Четвертый выход 1 v теополятора соединен с третьим выходом блекл 6 управления. Логическая единица на уко-анном выходе сигнализирует об скончании интерполяции отрезка прямой. Пятый выход 1U интерполятора определяет посредством исполнительного органа соотношение по модулю координатных приращений.

Реализация блока 6 управления в изобретении не отличается от его реализации в

устройстве-прототипе. На фиг. 2 представлена функциональная схема блока управления устройства-прототипа в случае отработки горизонтальных и вертикальных

отрезков прямых.

Интерполятор работает следующие пб- разом.

В регистры 1 и 2 записываются со i- вг-тственно прирг цения X iV У .,даю цин отрезок В )лг. : о В -ен я осуществляется ср i i ени i -личин ..Хи А1 При X - А / на и ход - бло 3 (.равнения появляется уровень логической единицы, когорьЛ обеспечивает перс коммутацию приращений Л X и Y, поступающих с перои;о 1 и второго 2 регистров координатчых приращений соответственно на второй и первый выходы входного комм агора 4. ПоиДХ AY на

выходе блока 3 срасн шп появляется уровень логического нуля обеспечиоащий передачу 5 1эчений Д X иА v, поступающих соответственно на первый и второй входы входного коммутатора , HPI его мерный и

второй выходы. Таким образом, на информационный вход блока 6 управления, первый вход делителя 7 и блока 5 выделения нулевого состояния пос -пает меньшее из приращений, а на ьторои вход делителя Убольшее В де-чиеле 7

осуществляется деление большего приоа- щения на меньшее, причем цетья часть отношения большего приращения к меньшему выставлаетсп на первбм выходе депителя 7 а дробная .асть - на втором выходе делителя 7. Значение целой части отношения большего приращетп к меньшему поступает на информационный вход двоичного сумматора 8 и складывается со значением логической единицы, поступяющей на вход переноса сумматора 8. Поскольку вторые информационные входы двоичного сумматора заземлены то на выходе двоичного сумматора 8 будет ровано значение К+1, где К - целая часть

отношения большего приращения к меньшему. Поскольку блоки 4 и 7 асинхронны, то значение КМ на выходе блока 8 будет неизменным до момента записи ноьых значений приращений в регистры 1 и 2. Н/левой уровень сигнала Пуск на 16 интерполятора является активным сигналом записи в блок 6 управления значения меньшею приращен я, определяющего число тактов в полном цикле работы интерпотигора. Единичпый уровень на третьем .ыхэде блока 6 управления удерживает накопительны,, сумматор 9 в нулевом состоянии Указэнчыо действия предшествуют процессу инт опоЛЯЦИИ И СОСТаВЛЯС ЦИКЛ ПОДГОТОВКИ.

Интерполирование заданного отрезка прямой начинается с появлением логике ской единицы на входе 16 Пуск интерполятора. При этом на третьем выходу блока В управления появляется сигнал логического нуля, не являющийся активным по отиоше нию к сигналу установки в нулевоэ состояние накопительного суммаюра 9. i la с open выходе блока 6 управления формируете- серия импульсов, число которых равно меньшему приращению. С появлением переднего фронта каждого из у ч Чи. их импульсов в накопительном сумматоре выполняется микроопера ;ия суммировании лро iju част i отношения бо - кмо приращения к меньщг ; с з ченисг. дробной части предыдущл C /MN-L, При стг, толъии переполнении из дробныv ртзр М1 -1 ,ч- горэ 9 на выход комму гат-фо Ч) пепедтпсч значение многоразрядного приращения с его персэго пхэдч V лдзапнг т на 1оние равно целой ч тети отн,, .РНИЯ большего г,рира- щения к меньшему При позни о очеиии переполнения из дробны, разряде ч сумматора 9 коммутатор 10 об-спР1 иг Рт тереда- чу значенип К-Ч, сформированного на втором входе коммутатора 10, на pro пичгд. В зависимости от сипала н- упплтияющем оходе третьего коммутлгогп 1 г-or/ -a:,.; щего с выхода блока 5 PI |дег,ен.-п упевот состояние, осущсс сляетс пере; п гигна ла на выход третьего к ог- - ута гор.) 11 с по;- вого или второго его РХОЧЭВ Причг ч при

еДИНИЧНОМ ЗНПЧ-МШИ НЛ управляющем ЯХ

де третьего коммутатот 1 1 ооущес i впагчхя передача сигнала нл третьего 1т,мчу татора 11 с пер ого ипи вгг го ir, р-г.до Причем, при е/ иниччом TII-T OHI i н, /ппап ляющем входе третье: о комм/ г л гот 11 осуществляется переда с ипп м с «л о п ппого входа на . В зйи:-с,1мости от зил ,ош«я сигнала на выходе блоха 3 г,г тьнен я осу ществляется передача К ипи К,1 с выхода коммутатора 10 на 20 .пи третий 21 выход интерполятора При АХ -AY первый выход комг.,та7ог,п 1 -о динен с элементами регистрации г.тр ir блока ynp. ления органом региггр : .1п Гнч носазань, при А-Х AV псрпы/i ni.i/ij i т.чмутм ра 12 соединен со ,ь . ыорчй - с элементами p- .rt c.Tf, inn.i рт.- - j 1ыюго линейного (или м .r.- i.o;oj регистрации. Сrpof . м ю сратрядных

ПрИрЭ1 СН.1Й. ПОСТ Л .1Х НО tit, ХОДЫ АО И

21 интерполятора, ocyiv-cit- -о ся сигналом, сфсрмироалнним б .-л ом :. /правления на его первом БЫЛО;,о /vr сэеспече (ия принципа единой прпеннси опганизгц/и сигналы на первом и orcpofi iij одах блока б управления формируются в л рот ьофазе, При этгм Гм) время действия .толожительного импульса на ртором выходе блока G у i- г мления злкак иваются все переходные процессы, свчзаш.ыр с суммированном в б юке 9 и коммутацией полученных значений п блоках 10 - 12. При нулевом уровне сигнала (отсутствие импульса) на втором выходе бгока 6 управления на его первом вы- одг1 форми /ется иг.-лульс, стробирующий г гзчения многоразрядных приращений

При этом на опном из выходов коммутатора 12, соответствующем ведущей координате, выставляется значение К или К+1, а на дру- том, сответствующем ведомой координате, З .ачг не 1. Значенип многоразрядных приплщяпий К или К i поступают на регистри- ( элементы (но показаны), а значим,че единицы - в счетчик строк или счетчик столбцов, причем последнее отрабатывается после отработки приращений К или К-41 по

чедущей координате. Число тактов в полном цикле работы интерполятора не зависит от опогг.ел с; вич приращений и равно величине меньшего из приоащоний

Г

Тциклэ АХ, приАХ АУ ЛУ. приАХ АУ

Сигнал Конец гнтгрполировлчипотрез- к-1 пмр бчтываетгя в блоке G управления по: ic определения равенства между числом g;i Ч1ных уполвляюидих тактов и величиной из приращений.

Рассмотрим рлботу интерполятора в случае отработки вертикальных (горизонтать iiix) отрезков прямых. В данном случае меньшое приращение равно нулю. На выходе блока 5 выделения нулевого состояния выставляется нулевой управляющий сигнал, под иоэдойст-шсм которого осуществляется

передача значения большого приращения со второго п.-.ода грстьсю коммутатора 11 на его . Нулевой сигнал с выхода блока 5 выделения нулевого состояния поступает также на младший разряд первого входа

первого коммутатора 12, что приводит к запрещению элементарного приращения на ведомой координате в пределах формиру- мого цифрового сегмента.

При нулевом, меньшем приращении

блок 6 управления обеспечивает выдачу единичного импульса, стробирующего многоразрядное приращение. В случае отработки вертикальных (горизонтальных отрезков прямых последние состоят только из одного

цифрового сегмента (мноюраэрядного при- ).

инторполя гора не отличается ог реализации уст.-зэйстоа-прототипа. Следует толо -о отметить особенность реализации вь /тенных блоксв.

Блок 5 выделения нулевого состояния может быть выполнен различными способами, в частности в качестве блока 5 может быть использована многовходовая схема, выполняющая логическую схему ИЛИ. При этом в качестве блока 5 выполнения нулевого состояния могут служить микросхемы К155ЛЛ1, К555ЛЛ1 и другие. Коммутатор 11 .может быть выполнен различными способами. Возможно использование микросхемы К531КП11П.

Работа блока 6 управления при ненулевом меньшем приращении не отличается от работы в устройстве-прототипе.

После записи приращений, определяющих аппроксимируемый отрезок прямой, поступает сигнал Пуск на вход 16 интерполятора. Под воздействием указанного сигнала в счетчике 30 фиксируется нулевое значение меньшего приращения и триггер 26 устанавливается в состояние логической единицы. Передним фронтом импупьса, поступающего с прямого выхода генератора 25 импульсов, триггер 27 устанавливается в состояние логической единицы, поскольку нт его информационный вход поступает уровень логической единицы с прямого выхода первого триггера 26. Это, в свою редь, разрешает прохождение импульса с выхода гечеоатооа 25 импульсов на выходе элементов 28 и 29. При переходе счетчика 30 с нулевого состояния в состояние 2П , где п - разрядность счетчика, на его выходе формируется сигнал переноса, который приводит к установке в нулевое состояние первого триггера 26 С появлением переднего фронта импульса от генератора 25 триггер 27 устанавливается в нулевое состояние, запрещая прохождение импульсов на выходе элементов И 28 и 29 1зким образом при нулевом меньшем пр.иоаще- нии обеспечивается импульс на выходе элемента И 29, который стробирует выходное многоразрядное приращение (фиг. 3). В устройстве-прототипе не предусмотрена интерполяция отрезков прямых с нулевым меньшим приращением.

В предлагаемом техническом решении за счет введения блока выделения нулевого состояния и третьего коммутатора расширены функциональные юзможнь:ти линеино- ю интерполятора возможностью отработки горизонтальных и вертикальных отрезков прямых,

Формула и з о б р с т н и я

Цифровой линейный интерполятор, содержащий двоичный и накапливающий cv-i маторы, входной коммутатор, блок сравнения, блох управления, делителе координатных приращений, первый коммутатор, второй коммутатор, первый и второй регистры координатных приращений, информационные входы которых являются

соответственно первым и вторым информационными входами интерполятор -ыходы регистров координатных приращений ол- ключены соответственно к информационным входам входного коммутатора и к

0 первой ь аторсй группам входов эг.о са срав- не-чия, выход которого .инеч с управляющими входами первого и плотного ксммутаторсп, первый информационный выход входного коммутатора соединен с ич5 формационн -лм входом блока управления и первым входом делителя когсдинатных приращений, а второй информационный выход входного коммутатора подключен к второму входу делителе коооди т.тных

П приращений, перьий и информационный вход второго коммуга орэ подключен к iieP вому выходу делителя координатных приращений и первому инфоомациоьмому входу двоичного сумматора, в.орой информаци5 онный вход второго коммутатора соединен с выходом двоичного сумматора, а управляющий вход - с выходок переноса накапливающего сумма i -Фа, информационный в,эд которого соединен с вторым выходом дели0 теля ког,рл, г.риращепий управляющие пчоды разрешения суммирования и останозэ соответственно, накапливающего сумматора подключены соответственно к второму и третьему выходам блока управле5 ьия, второй информацисжный вход двоичного сумматора подключен к общей шине, а вход переноса подключен к шине логической единицы, стари.ие разряды первого информационного входа первого коммутатора

0 подключены к общей шине, персый и третий выходы блока управления являются соответственно стробирующим выходом и входом Конец интерполяции интерпопятора, первый и второй выходы первого коммутсЗ5 гора являются соответственно первым и вторым информационными выходами интерполятора, блока сравнения является управляющим выходом ин 1ерполятог э, управляющий вход записи интерполятора

0 подключен к управляющим входам записи первого и второго регистров координатных приращений, а вход Пуск интерполятора соеди 1ен с управляющим входом блока управления, отличающийся тем, что, с

5 ь елью расшмрения функциональных, оозмож- ностей интерполят за счет от работки гори- зонгэльних и вертикальныхотрезков прямых, в него введен блек выделения и/левого состояния MpHbiut го приращения третий коммутатор, первый имформлц юнный вход

которого подключен к выходу второго коммутатора, второй информационный вход соединен с вторым выходом входного коммутатора и вторым входом делителя координатных приращений, выход третьего 5 информационным выходом входного комму- коммутатора подключен к второму инфор- татора, информационным входом блока уп- мационному входу первого коммутатора, младший разряд первого информационного

равления и первым входом делителя координатных приращений.

О t

30 -,

28

29

-fr

9

.

24

23

входа подключен к управляющему входу третьего коммутатора и выходу блока выделения нулевого состояния младшего приращения, вход которого соединен с первым

информационным выходом входного комму- татора, информационным входом блока уп-

равления и первым входом делителя координатных приращений.

м

прием пркрааекяЯ .

Лржю жид блока 25

-njTJTJ-iLrLTLTL

к

19

Выход влоп 26

Р

Блок 27. Пряно впсо«

Выход 16

18

Ьгхож 19 ЕЬход блока 30

Внход П

подготожи

-

Д|терполя- пношия цикл

| Цифровой линейный интерполятор | 1976 |

|

SU579599A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

| Цифровой линейный интерполятор | 1986 |

|

SU1310779A1 |

Авторы

Даты

1991-01-30—Публикация

1988-12-12—Подача