Изобретение относится к вычислительной технике и может быть использовано для построения средств автоматики, функциональных узлов систем управления и др.

Известны логические вычислители (см., например, патент РФ 2276399, кл. G06F 7/00, 2006 г.), которые реализуют параллельный набор n простых симметричных булевых функций, зависящих от последовательного набора n аргументов - входных двоичных сигналов.

К причине, препятствующей достижению указанного ниже технического результата при использовании известных логических вычислителей, относится неоднородность состава, обусловленная тем, что, в частности, упомянутый аналог состоит из элементов И, элементов ИЛИ и D-триггеров.

Наиболее близким устройством того же назначения к заявленному изобретению по совокупности признаков является принятый за прототип логический вычислитель (патент РФ 2294558, кл. G06F 7/57, 2007 г.), который содержит n-разрядный регистр и реализует параллельный набор n простых симметричных булевых функций, зависящих от последовательного набора n аргументов - входных двоичных сигналов.

К причине, препятствующей достижению указанного ниже технического результата при использовании прототипа, относится неоднородность состава, обусловленная тем, что прототип состоит из элементов И, элементов ИЛИ и регистра.

Техническим результатом изобретения является упрощение устройства за счет повышения однородности состава при сохранении функциональных возможностей прототипа.

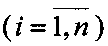

Указанный технический результат при осуществлении изобретения достигается тем, что в логическом вычислителе, содержащем n-разрядный регистр, i-й  вход и вход сброса, вход записи которого соединены соответственно с i-м выходом и первым, вторым управляющими входами логического вычислителя, особенность заключается в том, что в него введены n мажоритарных элементов, причем второй, третий входы и выход i-го мажоритарного элемента соединены соответственно с i-м выходом n-разрядного регистра, информационным входом и i-м выходом логического вычислителя, второй вход предыдущего мажоритарного элемента подключен к первому входу последующего мажоритарного элемента, а первый вход первого мажоритарного элемента соединен с шиной единичного потенциала.

вход и вход сброса, вход записи которого соединены соответственно с i-м выходом и первым, вторым управляющими входами логического вычислителя, особенность заключается в том, что в него введены n мажоритарных элементов, причем второй, третий входы и выход i-го мажоритарного элемента соединены соответственно с i-м выходом n-разрядного регистра, информационным входом и i-м выходом логического вычислителя, второй вход предыдущего мажоритарного элемента подключен к первому входу последующего мажоритарного элемента, а первый вход первого мажоритарного элемента соединен с шиной единичного потенциала.

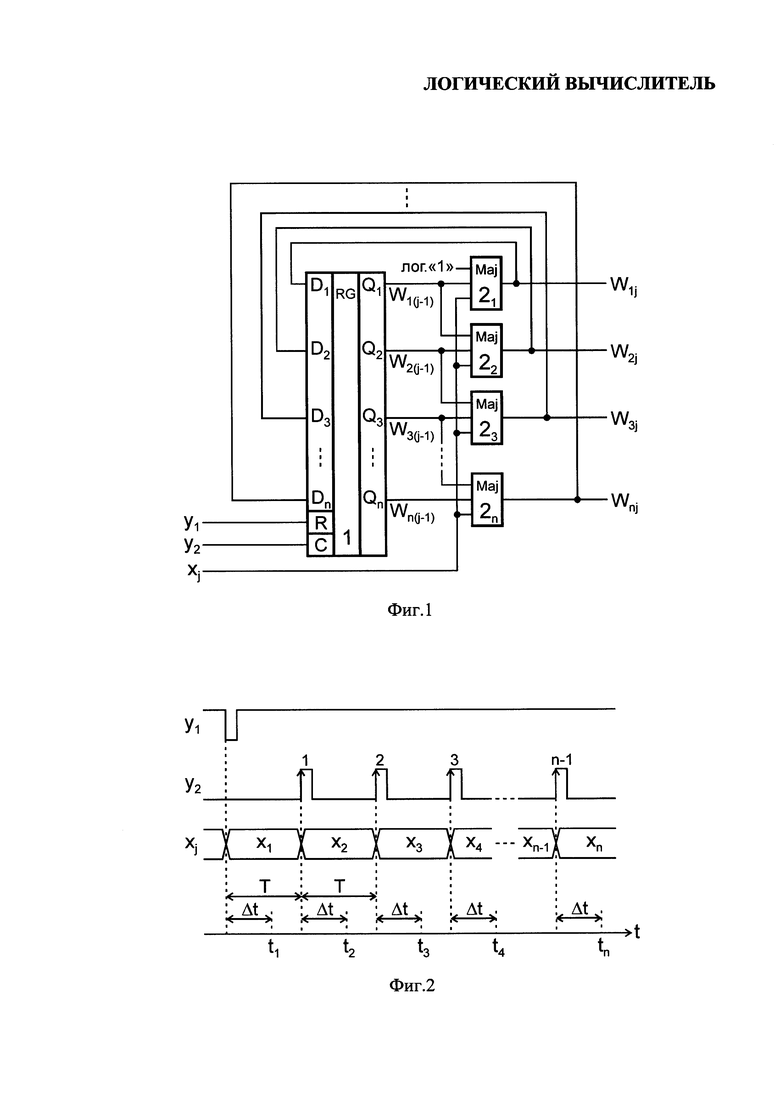

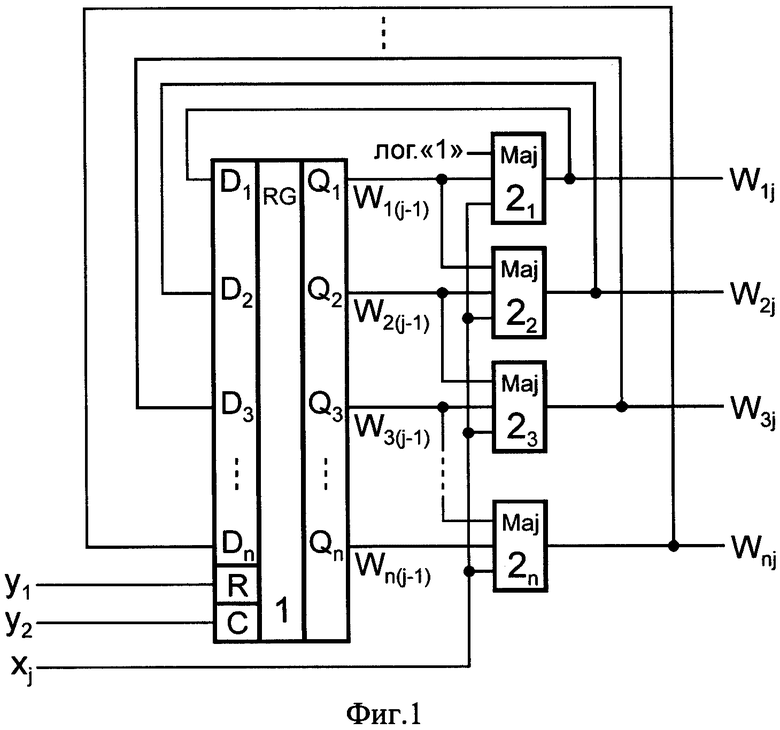

На фиг. 1 и фиг. 2 представлены соответственно схема предлагаемого логического вычислителя и временные диаграммы, поясняющие принцип его работы.

Логический вычислитель содержит n-разрядный регистр 1 и мажоритарные элементы 21, …, 2n, причем i-й  вход и вход сброса, вход записи регистра 1 соединены соответственно с i-м выходом и первым, вторым управляющими входами логического вычислителя, второй, третий входы и выход элемента 2i соединены соответственно с i-м выходом регистра 1, информационным входом и i-м выходом логического вычислителя, второй вход элемента 2k

вход и вход сброса, вход записи регистра 1 соединены соответственно с i-м выходом и первым, вторым управляющими входами логического вычислителя, второй, третий входы и выход элемента 2i соединены соответственно с i-м выходом регистра 1, информационным входом и i-м выходом логического вычислителя, второй вход элемента 2k

подключен к первому входу элемента 2k+1, а первый вход элемента 21 соединен с шиной единичного потенциала.

подключен к первому входу элемента 2k+1, а первый вход элемента 21 соединен с шиной единичного потенциала.

Работа предлагаемого логического вычислителя осуществляется следующим образом. На его первый, второй управляющие входы подаются соответственно импульсные сигналы  (фиг. 2), причем период Т сигнала y2 должен удовлетворять условию Т>Δt, где Δt=ΔtР+ΔtЭ, а ΔtР и ΔtЭ есть длительности задержек, вносимых регистром 1 и мажоритарным элементом. Синхронно с передним фронтом импульса сигнала y1 и передними фронтами первого, …, (n-1)-го импульсов сигнала y2 на информационный вход логического вычислителя последовательно подаются двоичные сигналы х1 и х2, …, xn соответственно (фиг. 2). Тогда сигнал на выходе элемента 2i

(фиг. 2), причем период Т сигнала y2 должен удовлетворять условию Т>Δt, где Δt=ΔtР+ΔtЭ, а ΔtР и ΔtЭ есть длительности задержек, вносимых регистром 1 и мажоритарным элементом. Синхронно с передним фронтом импульса сигнала y1 и передними фронтами первого, …, (n-1)-го импульсов сигнала y2 на информационный вход логического вычислителя последовательно подаются двоичные сигналы х1 и х2, …, xn соответственно (фиг. 2). Тогда сигнал на выходе элемента 2i

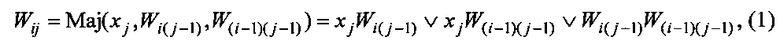

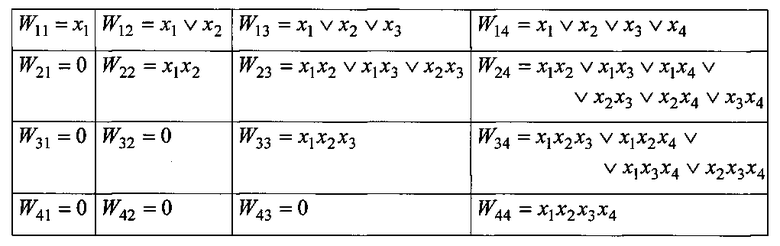

будет определяться рекуррентным выражением

будет определяться рекуррентным выражением

где  есть номер момента времени tj (фиг. 2); Wi0=0; W0(j-1)=1. В представленной ниже таблице приведены значения выражения (1) при n=4.

есть номер момента времени tj (фиг. 2); Wi0=0; W0(j-1)=1. В представленной ниже таблице приведены значения выражения (1) при n=4.

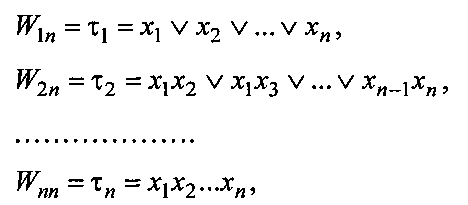

Таким образом, на первом, втором, …, n-м выходах предлагаемого логического вычислителя при j=n соответственно имеем

где τ1, …, τn есть простые симметричные булевы функции (см. стр. 126 в книге Поспелов Д.А. Логические методы анализа и синтеза схем. - М.: Энергия, 1974). Отметим, что обнуление выходных сигналов регистра 1 и загрузка в него данных происходят соответственно по низкому уровню сигнала на входе сброса и по положительному перепаду (из «0» в «1») сигнала на входе записи, поэтому указанный регистр может быть аппаратно выполнен с помощью, например, микросхемы КР1533ИР38.

Вышеизложенные сведения позволяют сделать вывод, что предлагаемый логический вычислитель реализует параллельный набор n простых симметричных булевых функций, зависящих от последовательного набора n аргументов - входных двоичных сигналов, и имеет более однородный по сравнению с прототипом состав.

| название | год | авторы | номер документа |

|---|---|---|---|

| ЛОГИЧЕСКИЙ ВЫЧИСЛИТЕЛЬ | 2004 |

|

RU2260837C1 |

| ЛОГИЧЕСКИЙ ВЫЧИСЛИТЕЛЬ | 2005 |

|

RU2294558C1 |

| ЛОГИЧЕСКИЙ ВЫЧИСЛИТЕЛЬ | 2016 |

|

RU2641446C2 |

| ЛОГИЧЕСКИЙ ВЫЧИСЛИТЕЛЬ | 2016 |

|

RU2630391C1 |

| ЛОГИЧЕСКИЙ ВЫЧИСЛИТЕЛЬ | 2005 |

|

RU2294009C1 |

| ЛОГИЧЕСКИЙ ПРОЦЕССОР | 2003 |

|

RU2251142C2 |

| ЛОГИЧЕСКИЙ ПРОЦЕССОР | 2005 |

|

RU2294008C1 |

| ЛОГИЧЕСКИЙ ПРЕОБРАЗОВАТЕЛЬ | 2021 |

|

RU2768627C1 |

| ЛОГИЧЕСКИЙ МОДУЛЬ | 2021 |

|

RU2776920C1 |

| ЛОГИЧЕСКИЙ ВЫЧИСЛИТЕЛЬ | 2007 |

|

RU2353967C1 |

Изобретение относится к вычислительной технике и может быть использовано для построения средств автоматики, функциональных узлов систем управления и др. Техническим результатом является упрощение устройства. Логический вычислитель предназначен для реализации простых симметричных булевых функций и может быть использован в системах цифровой вычислительной техники как средство преобразования кодов. Логический вычислитель содержит n-разрядный регистр (1) и n мажоритарных элементов (21, …, 2n). За счет мажоритарных элементов повышена однородность состава. В результате достигнуто упрощение устройства. 2 ил., 1 табл.

Логический вычислитель, предназначенный для реализации параллельного набора n простых симметричных булевых функций, зависящих от последовательного набора n аргументов - входных двоичных сигналов, содержащий n-разрядный регистр, i-й

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Способ восстановления хромовой кислоты, в частности для получения хромовых квасцов | 1921 |

|

SU7A1 |

| Способ приготовления мыла | 1923 |

|

SU2004A1 |

Авторы

Даты

2016-08-27—Публикация

2015-03-13—Подача