Изобретение относится к вычислительной технике, а именно к многопроцессорным электронно-вычислительным машинам, являющихся частью программно-аппаратных комплексов и может быть использовано в таких областях техники, как квантовая информатика, метеорология, геологическая разведка, а также при выполнении задач, связанных с интенсивным нерегулярным обращением к памяти вычислительного устройства (DIS-задачи), высокоскоростной обработкой сигналов и изображений и работой с хранилищами разнородной информации большого размера (RDF - базы данных).

Известны мультитредовые устройства процессоров электронно-вычислительных машин, выполняющие различные вычислительные задачи, в том числе с 32-х и 64-х разрядными числами с плавающей точкой и так называемыми «длинными» 160-ти разрядными числами (см., TW, 201543357 А, кл. G06F 9/28, опубл. 16.11.2015; CN, 104937541 А, кл. G06F 9/28, опубл. 23.09.2015; US, 2016019063 А1, кл. G06F 9/30, опубл. 21.01.2016; US, 2016011869 А1, кл. G06F 9/30, опубл. 14.01.2016; JP, 2015505998 А, кл. G06F 9/305, 26.02.2015; US, 2016011869 А1, кл. G06F 9/30, опубл. 14.01.2016; US, 2014351565 А1, кл. G06F 9/308, опубл. 27.11.2014; US, 2007266224 А1, кл. G06F 9/30, опубл. 15.11.2007; SU, 980097 А, кл. G06F 13/06, опубл. 07.12.1982; SU, 822168 А, кл. G06F 3/04, опубл. 15.04.1981; RU, 2291477 С2, кл. G06F 9/302, опубл. 10.01.2007).

Недостатками известных технических решений являются недостаточная степень быстродействия вычислительных устройств, объективные сложности, возникающие при обработке процессорами больших объемов информации (графовых баз данных), в частности, при работе в режиме интенсивного нерегулярного обращения к памяти и недостаточное распараллеливание команд.

Известен способ организации глобально-адресуемой общей памяти в многопроцессорной ЭВМ на основе многоядерно-мультитредового микропроцессора, использующего двухуровневую сегментную виртуальную память и содержащего множество вычислительных узлов, соединенных между собой посредством коммуникационной сети, по способу функционирования и совокупности существенных признаков, принятый за ближайший аналог (прототип) изобретения (см. RU, 2396592 С2, кл. G06F 12/02, опубл. 10.08.2010).

Недостатками известного технического решения являются недостаточная степень быстродействия и организации обработки данных вычислительного устройства многопроцессорной ЭВМ, отсутствие достаточного количества средств оптимизации, учитывающих неоднородность доступа к глобально адресуемой памяти, невысокая отказоустойчивость элементов, входящих в состав многопроцессорной ЭВМ.

Задачей, на решение которой направлено заявляемое изобретение, является повышение эффективности организации обработки в реальном времени множества интенсивных потоков данных, включая работу через единое адресное пространство с объемом памяти не менее нескольких десятков петабайт.

Достигаемый при этом технический результат, заключающийся в повышении быстродействия устройства, обеспечивается за счет того, что вычислительное устройство программно-аппаратного комплекса имеет многослойную структуру и содержит секционный микропроцессор на кристаллической основе с мультитредовыми ядрами, подключенный через высокоскоростные каналы обмена данными к основной памяти типа DRAM вычислительного устройства, энергонезависимой памяти типа NVRAM и функционально-логическому устройству, состоящему из конвейера обработки запросов TCU и сетевого сопроцессора, при этом каждое мультитредовое ядро имеет в своем составе домены защиты и тредовые устройства с регистрами памяти, выполненными с двойным уровнем индексации, при этом первый уровень представляет собой многовходовую регистровую память, а второй - статическую память, на которую отображается вся регистровая память ядра, обмен между двумя уровнями ведется посредством регистровых страниц, процессорные модули с аппаратными ядрами и каналами обработки процессов-тредов, кодирующее устройство, подключенное к аппаратным ядрам сетевого сопроцессора, конвейера обработки запросов и процессорных модулей и взаимодействующее с функциональными устройствами соседнего кристалла секционной сборки, кристаллы микропроцессора выполнены без корпуса на керамических подложках, магистральные линии обмена информацией которых между собой выполнены в виде соединения бесштырькового типа с использованием углеродистых нанотрубок карбоново-оксидной структуры с металлическими лигандами, дополнительно устройство содержит модуль выполнения логических и арифметических операций SIMD с адресуемыми однобитовыми регистрами для запоминания признаков выполнения логических и арифметических операций, связанный через контроллеры DMA с WDM-трансиверами, служащими для реализаций передачи сообщений одновременно на разных длинах волн, контроллеры кэш-памяти, устройство сериализации/десериализации пакетов сообщений, сетевой маршрутизатор, блок выполнения операций над битовыми матрицами, устройство для работы со 160-разрядными данными, линии диагностики и контроля, линии подключения к системе обеспечения надежности, готовности и сервиса, адаптеры межузловой сети, блоки доменов защиты задач, блоки интерфейса с внекристаллической памятью, блок гипертранспорта и операционную систему, управляющую доменами защиты с помощью набора привилегированных команд.

Кроме того, количество доменов защиты устройства составляет 16, количество тредовых устройств в каждом ядре составляет 256 единиц, количество ядер от 2-512.

Кроме того, тактовая частота секционного микропроцессора составляет 10 ГГц, размер адресов команд составляет 48 разрядов, объем адресуемых данных составляет до 32 Пбайт.

Кроме того, на этапе подготовки задачи, конвейер обработки запросов TCU работает с семантической частью кодирования цепочки клиентских запросов и опкодом инструкций.

Кроме того, кодирующее устройство выполнено в виде дешифратора.

Кроме того, кодирующее устройство выполнено в виде шифратора.

Кроме того, аппаратные ядра процессорных модулей эмулируют сверхлегкие и легкие процессы-треды через модуль SIMD, соединенный с контроллерами DMA и WDM-трансиверами.

Кроме того, аппаратные ядра процессорных модулей эмулируют средние процессы-треды через устройство сериализации/десериализации пакетов сообщений, после чего через сетевой маршрутизатор данные передаются во внешнюю высокоскоростную магистраль.

Кроме того, аппаратные ядра процессорных модулей эмулируют тяжелые процессы-треды с обращением к кэш-памяти.

Кроме того, вычислительное устройство изготавливается посредством модульной 3D сборки электронных блоков с чередованием процессорных кристаллов и кристаллов памяти посредством «плотной склейки» без контактных проводов и дополнительных линий шунтирования.

Кроме того, вычислительное устройство изготавливается посредством объединения в блоки трехмерных сверхбольших интегральных схем типа «система на кристалле».

Кроме того, число узлов на одном кристалле составляет 63648 единиц.

Кроме того, количество адресуемых однобитовых регистров составляет 80 единиц.

Использование предложенной конструкции вычислительного устройства в программно-аппаратных комплексах имеет следующий ряд преимуществ:

- во-первых, заявляемое вычислительное устройство имеет несколько уровней иерархии, обладает высоким параллелизмом организации команд и глобально адресуемой памятью, а также достаточным количеством средств оптимизации, учитывающим неоднородность доступа к глобально адресуемой памяти;

- во-вторых, заявляемое вычислительное устройство изготовлено с использованием отечественной элементной базы (микросхемы и платы), что значительно удешевляет стоимость как данного изделия в целом, так и построенных на этой элементной базе специализированных суперкомпьютеров, без потерь в качестве работы и быстродействии;

- в-третьих, быстродействие заявляемого вычислительного устройства, на основе результатов проведенных экспериментов заявителем-автором, по сравнению с классическими процессорными вычислительными системами при решении задач с интенсивной нерегулярной работой с памятью (DIS-задачи) увеличивается приблизительно в 100 раз;

- в-четвертых, для повышения эффективности осуществления логических операций, использует функционально-логическое устройство с конвейером обработки запросов TCU, который на этапе постановки задачи, работает не только с сигнатурами операций, как классическое устройство обработки запросов, но и с семантической составляющей кодирования цепочки клиентских запросов посредством формирования генеративных таблиц, хранящихся в соответствующих тредовых регистрах t_reg., после чего осуществляется передача стандартной процедурной составляющей (опкод инструкций: набор кода данных и кода команд, модификаторов и флагов условных переходов);

- в-пятых, для значительного повышения скорости быстродействия вычислительного устройства, устройство, осуществляющее кодирование/декодирование команд (шифратор/дещифратор), имеет прямое канальное подключение к аппаратным ядрам процессора, сетевому сопроцессору и конвейеру обработки запросов с возможностью быстрого обмена с функциональными устройствами соседнего кристалла секционной сборки;

- в-шестых, для значительной экономии внутренних ресурсов ядер и повышенной толерантности к задержкам выполнения операций с памятью и сетью, сетевой сопроцессор позволяет выполнять математические операции с пакетами сообщений и передавать результаты на межмодульную сеть напрямую, не затрагивая при этом микропроцессор;

- в-седьмых, заявляемое вычислительное устройство позволяет осуществлять трехуровневую обработку векторов (короткие, средние, длинные), для оптимизации работы с памятью и повышения быстродействия имеет множество встроенных команд-функций и макрокоманд, а также аппарат почтовых ящиков на уровне архитектурных регистров, что обеспечивает большую эффективность использования площади при сборке кристалла и оптимальное потребление энергии;

- в-восьмых, по сравнению с классическими процессорными вычислительными устройствами, заявляемое устройство обладает улучшенными характеристиками, а именно: 3D-сборкой электронных блоков, использованием доменной защиты данных, команд и тредовых устройств, наличием подсистемы обеспечения отказоустойчивости;

- в-девятых, в заявляемом вычислительном устройстве снижено ограничение на объем выполняемых программ, что способствует повышению надежности.

Таким образом, отличия заявляемого вычислительного устройства от классических процессорных вычислительных систем следующие:

- имеет блок формирования пакетов-запросов в другие модули системы, содержащие физическую память, адресуемую через единое глобально адресуемое виртуальное адресное пространство;

- имеет прямую связь кристаллов микропроцессора на трех уровнях, что может быть применено для увеличения количества ядер микропроцессора, а также для повышения отказоустойчивости (дублирование ресурсов, задействованных при выполнении программы и контроль сверкой выдаваемых ими результатов);

- реализует атомарное выполнение целочисленных арифметических и логических операций непосредственно над ячейкой памяти, осуществляет работу с теговыми битами доступа и состояния;

- имеет канал непосредственной передачи запросов из сети, если они содержат обращение по физическому адресу, причем к области, которая не кэшируется микропроцессором в кэш-памяти уровня L2. В данном случае, во-первых, не требуется дополнительная трансляция виртуального адреса в блоке MMU микропроцессора с использованием второго уровня виртуальной адресации (аппарат R-сегментов и R-страниц), а во-вторых, не требуется поиск в кэш-памятях. Таким образом, внутрь микропроцессора через блок NI сообщение передавать не требуется, что приводит к значительной экономии ресурсов и повышению быстродействия;

- имеет сопряжение с сетью с терабитной пропускной способностью, на подложке линии связей реализованы с использованием нанотехнологий и технологии «горячей сверхпроводимости»;

- имеет интерфейс для передачи пакетов в межмодульную сеть, сверхбыструю передачу пакетов с уплотнением, что может осуществлять сериализацию/десериализацию пакетов.

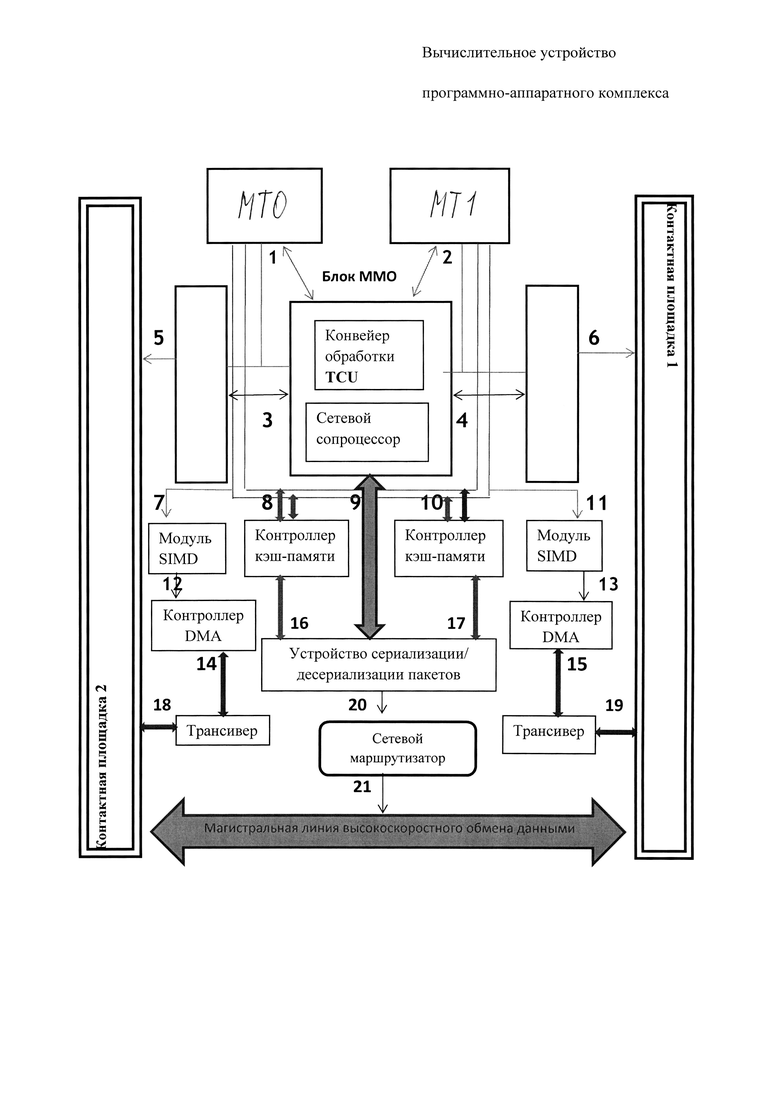

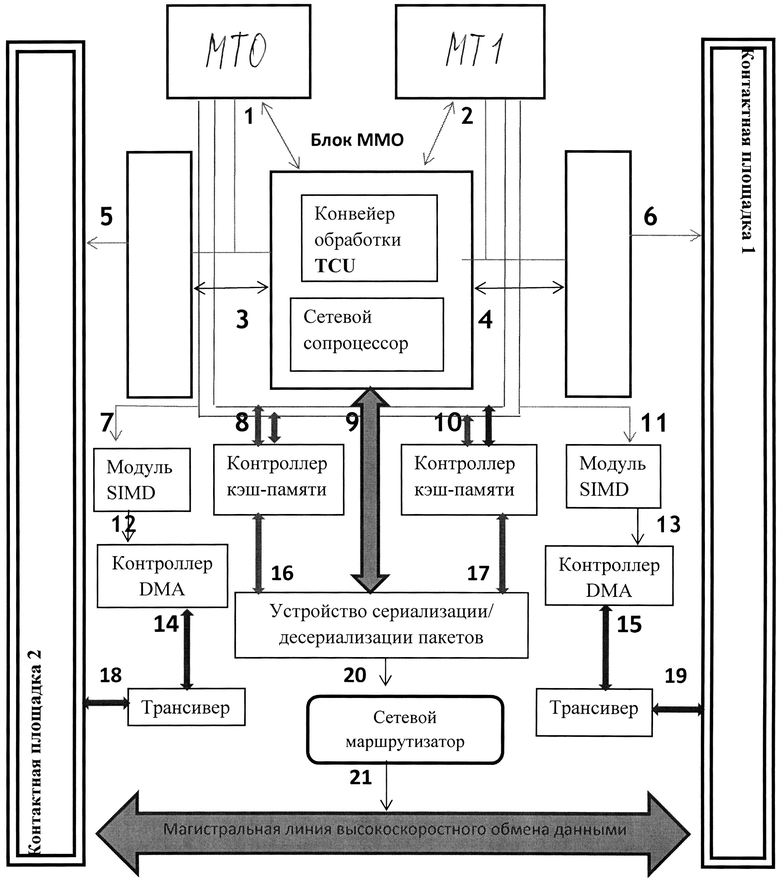

Заявляемое изобретение иллюстрируется схемой, наиболее полно поясняющей сущность предлагаемого технического решения.

Вычислительное устройство программно-аппаратного комплекса - секционного типа. Один кристалл имеет два ядра (МТ0 и МТ1). Количество ядер может быть увеличено до 512. Тактовая частота секционного микропроцессора составляет 10 ГГц. К микропроцессору подключена основная память типа DRAM вычислительного узла, а также память типа NVRAM (энергонезависимая память, ее можно рассматривать как сверхбыстрый диск).

Стрелками 1, 2 условно показаны каналы обмена между процессорными ядрами МТ0, МТ1 и блоком функционально-логического устройства (ММО), состоящего из конвейера обработки запросов TCU и сетевого сопроцессора.

Дешифратор/шифратор - устройство, осуществляющее кодирование/декодирование команд процессора, имеет прямое канальное подключение к аппаратным ядрам процессора, сетевому сопроцессору и конвейеру обработки запросов (стрелки 3, 4) с возможностью быстрого обмена с функциональными устройствами соседнего кристалла секционной сборки (стрелки 5, 6).

Сетевой сопроцессор позволяет выполнять математические операции с пакетами сообщений и передавать результаты на межмодульную сеть напрямую, не задействуя микропроцессор, благодаря чему получается значительная экономия ресурсов ядер МТ0 и МТ1 с повышенной толерантностью к задержкам выполнения операций с памятью и сетью.

Кроме сетевых операций сетевой процессор выполняет следующие функции: трансляцию виртуальных адресов, после трансляции адреса разделяет обращения в локальную память узла от обращений в удаленные узлы, производит агрегирование обращений к удаленным узлам, а также распаковку поступающих сообщений от удаленных узлов, выполняет локализованные в непосредственной близости от памяти функции, которыми могут быть атомарные операции, транзакционные преобразования структур данных, сложные функции синхронизации типа действий специальных узлов синхронизации или преобразования данных (акторы).

Кристаллы микропроцессора размещаются без корпусов на керамической подложке. На подложках имеются сверхскоростные соединения и контактные переходы между подложками. Это позволяет одновременно с масштабированием количества ядер масштабировать и интерфейсы с памятью, сетью, а также внутрикристальную сеть. Это возможно благодаря тому, что можно соединять секции сверхбыстрыми связями на трех уровнях (конвейеры команд, функциональные устройства, порты внутрикристальных коммутаторов со стороны конвейеров и функциональных устройств).

Контактная зона (площадка) 1 и Контактная зона (площадка) 2 - высокоскоростные линки подложки, выполненные с использованием нанотехнологий, для обеспечения прямой связи кристаллов микропроцессора и для реализации N-мерной сети модулей для организации сверхбыстрого обмена данными между разными секциями сборочных модулей вычислительного устройства (магистральные линии обмена информации). Представляют собой соединения бесштырького типа с использованием карбоновых нанотрубок с металлическими лигандами, собирающимися по новейшей технологии с реализацией функциональности «горячей сверхпроводимости».

Процессорные модули вычислительного устройства могут быть разными по типу поддерживаемых в ядре процессов и эмулировать выполнения команд одного или множества процессов-тредов - сверхлегкие, легкие, средней тяжести, тяжелые, а именно: сверхлегкие ядра графических процессоров (GPU), средние ядра RISC-микропроцессоров типа MIPS, тяжелые ядра суперскалярных микропроцессоров с архитектурой х86, легкие ядра векторных процессоров с поддержкой SIMD-режима.

Стрелки 7, 11, 12, 13 - каналы обработки легких и сверхлегких процессов-тредов: в схему добавлен модуль SIMD, который напрямую по линиям 14 и 15 получает доступ через DMA-интерфейс (контроллеры DMA) к WDM - трансиверам, которые служит для реализации передачи сообщений через оптоволокно одновременно на разных длинах волн (магистрали 18 и 19).

Стрелка 9 - канал обработки средних процессов-тредов: для работы реализована связь с устройством сериализации/десериализации пакетов сообщений с целью уплотнения (сжатия) передачи данных, обеспечивает распознавание большого количества форматов сообщений, реализацию методов агрегирования коротких сообщений в длинные и обратное преобразование, затем они передаются через сетевой маршрутизатор во внешнюю высокоскоростную магистраль (стрелки 20, 21). При этом не используется «накачка» данных из кэш-памяти.

Стрелки 8, 10, 16, 17 - каналы обработки тяжелых процессов-тредов: требуется для выполнения инженерно-расчетных задач с «накачкой» данных из кэш-памяти.

В вычислительном устройстве используются средства работы с очень большими данными (большими объемами данных из многоуровневой памяти системы), а также выделенные магистрали для работы с сетями передачи данных (датчиками, через которые поступают потоки данных). Производительность устройства - 10 ПФлопс (1015 вычислений операций с плавающей точкой).

При разработке вычислительного устройства использовался аппарат теории графов, теории алгоритмов, декомпозиции иерархических структур для формализации процессов информационного взаимодействия с учетом архитектуры гипервизоров и особенностей современных технологий виртуализации аппаратных ресурсов.

В качестве средств разработки использовались: программный пакет схемотехнической разработки VHDL, GNU ассемблер, отладчик Total View. Исследования проводились на тестировочном стенде VIPNet - Coordinator, который объединяет 50 сервисных узлов хранения данных, 30 серверов, 60 рабочих станций операторов и представляет собой виртуальную защищенную сеть.

Заявителем-автором проводилось экспериментальное исследование, в ходе которого сравнивались быстродействие выполнения разного класса задач на физическом кластере с разными типами процессоров.

В качестве метода тестирования использовалась математическая оценка с помощью критериев пространственно-временной локализации. В качестве средства - набор тестов Арех-Мар, который синтезирует разные пространственно-временные режимы локализации обращений к памяти, используются обращения на считывание, и при этом измеряет среднее количество тактов процессора, приходящихся на выполнение одного обращение. Выделяется большой массив М объемом около половины физически доступной оперативной памяти. В этом массиве периодически производится прохождение с единичным шагом ячеек памяти из областей с заданным параметром теста объемом L (меняется в границах, гораздо меньше М).

Размещение этих областей в М меняется случайным образом, что управляется параметром А (или α), который больше нуля, но меньше или равен единице. Параметр L задает пространственную локализацию, а параметр А определяет временную. Работа теста Арех-Мар состоит в том, что он проходит весь диапазон значений L и А и для каждой пары выбранных значений, определяет среднее время выполнения обращения к памяти на считывание. Эта точка рассматривается как одна из точек АРЕХ-поверхности, которую строит этот тест в конечном итоге.

В результате проведенного патентно-информационного поиска не было найдено ни одного источника информации, содержащего всю совокупность существенных признаков заявленного изобретения, что позволяет сделать вывод о его соответствии критериям патентоспособности «новизна», «изобретательский уровень» и «промышленная применимость».

| название | год | авторы | номер документа |

|---|---|---|---|

| СПОСОБ ФУНКЦИОНИРОВАНИЯ ОПЕРАЦИОННОЙ СИСТЕМЫ ВЫЧИСЛИТЕЛЬНОГО УСТРОЙСТВА ПРОГРАММНО-АППАРАТНОГО КОМПЛЕКСА | 2016 |

|

RU2626350C1 |

| ИНСТРУКЦИЯ И ЛОГИКА ДЛЯ ДОСТУПА К ПАМЯТИ В КЛАСТЕРНОЙ МАШИНЕ ШИРОКОГО ИСПОЛНЕНИЯ | 2013 |

|

RU2662394C2 |

| МОДУЛЬ СОПРОЦЕССОРА КЭША | 2011 |

|

RU2586589C2 |

| ИНСТРУКЦИЯ И ЛОГИКА ДЛЯ ИДЕНТИФИКАЦИИ ИНСТРУКЦИЙ ДЛЯ УДАЛЕНИЯ В МНОГОПОТОЧНОМ ПРОЦЕССОРЕ С ИЗМЕНЕНИЕМ ПОСЛЕДОВАТЕЛЬНОСТИ | 2013 |

|

RU2644528C2 |

| СПОСОБ ОРГАНИЗАЦИИ ГЛОБАЛЬНО АДРЕСУЕМОЙ ОБЩЕЙ ПАМЯТИ В МНОГОПРОЦЕССОРНОЙ ЭВМ | 2008 |

|

RU2396592C2 |

| КОМАНДА И ЛОГИКА ДЛЯ ОБЕСПЕЧЕНИЯ ФУНКЦИОНАЛЬНЫХ ВОЗМОЖНОСТЕЙ ЦИКЛА ЗАЩИЩЕННОГО ХЕШИРОВАНИЯ С ШИФРОМ | 2014 |

|

RU2637463C2 |

| НЕЧУВСТВИТЕЛЬНЫЙ К ЗАДЕРЖКЕ БУФЕР ТРАНЗАКЦИИ ДЛЯ СВЯЗИ С КВИТИРОВАНИЕМ | 2014 |

|

RU2598594C2 |

| УСТРОЙСТВО И СПОСОБ РЕВЕРСИРОВАНИЯ И ПЕРЕСТАНОВКИ БИТОВ В РЕГИСТРЕ МАСКИ | 2014 |

|

RU2636669C2 |

| КОМАНДА И ЛОГИЧЕСКАЯ СХЕМА ДЛЯ СОРТИРОВКИ И ВЫГРУЗКИ КОМАНД СОХРАНЕНИЯ | 2014 |

|

RU2663362C1 |

| ВЫЧИСЛИТЕЛЬНЫЙ МОДУЛЬ ДЛЯ МНОГОПОТОКОВОЙ ОБРАБОТКИ ЦИФРОВЫХ ДАННЫХ И СПОСОБ ОБРАБОТКИ С ИСПОЛЬЗОВАНИЕМ ДАННОГО МОДУЛЯ | 2018 |

|

RU2708794C2 |

Изобретение относится к вычислительной технике и может быть использовано при выполнении задач, связанных с интенсивным нерегулярным обращением к памяти вычислительного устройства и высокоскоростной обработкой сигналов и изображений с хранилищами разнородной информации большого размера. Технический результат заключается в повышении быстродействия устройства. Вычислительное устройство имеет многослойную структуру и секционный микропроцессор с мультитредовыми ядрами, процессорные модули с аппаратными ядрами и каналами обработки процессов-тредов, кодирующее устройство, подключенное к аппаратным ядрам сетевого сопроцессора, конвейера обработки запросов и процессорных модулей и взаимодействующее с функциональными устройствами соседнего кристалла секционной сборки. Устройство также содержит модуль выполнения операций SIMD с однобитовыми регистрами для запоминания признаков выполнения логических и арифметических операций, связанный через контроллеры DMA с WDM-трансиверами, для реализаций передачи сообщений одновременно на разных длинах волн, контроллеры кэш-памяти, устройство сериализации/десериализации пакетов сообщений, маршрутизатор, блок выполнения операций над битовыми матрицами, устройство для работы со 160-разрядными данными. 12 з.п. ф-лы, 1 ил.

1. Вычислительное устройство программно-аппаратного комплекса, отличающееся тем, что имеет многослойную структуру и содержит секционный микропроцессор на кристаллической основе с мультитредовыми ядрами, подключенный через высокоскоростные каналы обмена данными к основной памяти типа DRAM вычислительного устройства, энергонезависимой памяти типа NVRAM и функционально-логическому устройству, состоящему из конвейера обработки запросов TCU и сетевого сопроцессора, при этом каждое мультитредовое ядро имеет в своем составе домены защиты и тредовые устройства с регистрами памяти, выполненными с двойным уровнем индексации, при этом первый уровень представляет собой многовходовую регистровую память, а второй - статическую память, на которую отображается вся регистровая память ядра, обмен между двумя уровнями ведется посредством регистровых страниц, процессорные модули с аппаратными ядрами и каналами обработки процессов-тредов, кодирующее устройство, подключенное к аппаратным ядрам сетевого сопроцессора, конвейера обработки запросов и процессорных модулей и взаимодействующее с функциональными устройствами соседнего кристалла секционной сборки, кристаллы микропроцессора выполнены без корпуса на керамических подложках, магистральные линии обмена информацией которых между собой выполнены в виде соединения бесштырькового типа с использованием углеродистых нанотрубок карбоново-оксидной структуры с металлическими лигандами, дополнительно устройство содержит модуль выполнения логических и арифметических операций SIMD с адресуемыми однобитовыми регистрами для запоминания признаков выполнения логических и арифметических операций, связанный через контроллеры DMA с WDM-трансиверами, служащими для реализаций передачи сообщений одновременно на разных длинах волн, контроллеры кэш-памяти, устройство сериализации/десериализации пакетов сообщений, сетевой маршрутизатор, блок выполнения операций над битовыми матрицами, устройство для работы со 160-разрядными данными, линии диагностики и контроля, линии подключения к системе обеспечения надежности, готовности и сервиса, адаптеры межузловой сети, блоки доменов защиты задач, блоки интерфейса с внекристаллической памятью, блок гипертранспорта и операционную систему, управляющую доменами защиты с помощью набора привилегированных команд.

2. Вычислительное устройство по п. 1, отличающееся тем, что количество доменов защиты устройства составляет 16, количество тредовых устройств в каждом ядре составляет 256 единиц, количество ядер от 2-512.

3. Вычислительное устройство по п. 1, отличающееся тем, что тактовая частота секционного микропроцессора составляет 10 ГГц, размер адресов команд составляет 48 разрядов, объем адресуемых данных составляет до 32 Пбайт.

4. Вычислительное устройство по п. 1, отличающееся тем, что на этапе подготовки задачи конвейер обработки запросов TCU работает с семантической частью кодирования цепочки клиентских запросов и опкодом инструкций.

5. Вычислительное устройство по п. 1, отличающееся тем, что кодирующее устройство выполнено в виде дешифратора.

6. Вычислительное устройство по п. 1, отличающееся тем, что кодирующее устройство выполнено в виде шифратора.

7. Вычислительное устройство по п. 1, отличающееся тем, что аппаратные ядра процессорных модулей эмулируют сверхлегкие и легкие процессы-треды через модуль SIMD, соединенный с контроллерами DMA и WDM-трансиверами.

8. Вычислительное устройство по п. 1, отличающееся тем, что аппаратные ядра процессорных модулей эмулируют средние процессы-треды через устройство сериализации/десериализации пакетов сообщений, после чего через сетевой маршрутизатор данные передаются во внешнюю высокоскоростную магистраль.

9. Вычислительное устройство по п. 1, отличающееся тем, что аппаратные ядра процессорных модулей эмулируют тяжелые процессы-треды с обращением к кэш-памяти.

10. Вычислительное устройство по п. 1, отличающееся тем, что вычислительное устройство изготавливается посредством модульной 3D-сборки электронных блоков с чередованием процессорных кристаллов и кристаллов памяти посредством «плотной склейки» без контактных проводов и дополнительных линий шунтирования.

11. Вычислительное устройство по п. 1, отличающееся тем, что вычислительное устройство изготавливается посредством объединения в блоки трехмерных сверхбольших интегральных схем типа «система на кристалле».

12. Вычислительное устройство по п. 1, отличающееся тем, что число узлов на одном кристалле составляет 63648 единиц.

13. Вычислительное устройство по п. 1, отличающееся тем, что количество адресуемых однобитовых регистров составляет 80 единиц.

| СПОСОБ ОРГАНИЗАЦИИ ГЛОБАЛЬНО АДРЕСУЕМОЙ ОБЩЕЙ ПАМЯТИ В МНОГОПРОЦЕССОРНОЙ ЭВМ | 2008 |

|

RU2396592C2 |

| МОДУЛЬ МНОГОПРОЦЕССОРНОЙ СИСТЕМЫ | 2004 |

|

RU2282236C1 |

| Токарный резец | 1924 |

|

SU2016A1 |

| US 20160019063 A1, 21.01.32016. | |||

Авторы

Даты

2017-05-03—Публикация

2016-03-23—Подача