Изобретение относится к вычислительной технике и может быть использовано для построения средств автоматики, функциональных узлов систем управления и др.

Известны двоичные вычитатели (см., например, рис. 9.9б на стр. 219 в книге Токхейм Р. Основы цифровой электроники. М: Мир, 1988 г.), которые выполняют операцию А-В, где А, В ∈ {0,1} есть входные двоичные сигналы.

К причине, препятствующей достижению указанного ниже технического результата при использовании известных двоичных вычитателей, относятся ограниченные функциональные возможности, обусловленные тем, что не допускается обработка трех входных сигналов.

Наиболее близким устройством того же назначения к заявленному изобретению по совокупности признаков является принятый за прототип двоичный вычитатель (рис. 9.11 в на стр. 220 в книге Токхейм Р. Основы цифровой электроники. М.: Мир, 1988 г.), который содержит элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, элемент НЕ и выполняет операцию А-В-Bin, где A, B, Bin ∈ {0,1} есть входные двоичные сигналы.

К причине, препятствующей достижению указанного ниже технического результата при использовании прототипа, относится сложность последнего, обусловленная тем, что цена по Квайну прототипа равна 12 и в нем имеется два места пересечения соединений.

Техническим результатом изобретения является упрощение двоичного вычитателя за счет уменьшения его цены по Квайну и устранения мест пересечения соединений при сохранении функциональных возможностей прототипа.

Указанный технический результат при осуществлении изобретения достигается тем, что в двоичном вычитателе, содержащем элемент НЕ и элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, j-й  вход которого соединен с j-ым входом двоичного вычитателя, особенность заключается в том, что в него дополнительно введены два замыкающих и два размыкающих ключа, причем вход второго и вход первого замыкающих ключей соединены соответственно с выходом элемента НЕ и вторым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, подсоединенного выходом к управляющему входу всех ключей, а выход j-го замыкающего ключа соединен с выходом j-го размыкающего ключа и j-ым выходом двоичного вычитателя, подсоединенного третьим входом к входу элемента НЕ и входу j-го размыкающего ключа.

вход которого соединен с j-ым входом двоичного вычитателя, особенность заключается в том, что в него дополнительно введены два замыкающих и два размыкающих ключа, причем вход второго и вход первого замыкающих ключей соединены соответственно с выходом элемента НЕ и вторым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, подсоединенного выходом к управляющему входу всех ключей, а выход j-го замыкающего ключа соединен с выходом j-го размыкающего ключа и j-ым выходом двоичного вычитателя, подсоединенного третьим входом к входу элемента НЕ и входу j-го размыкающего ключа.

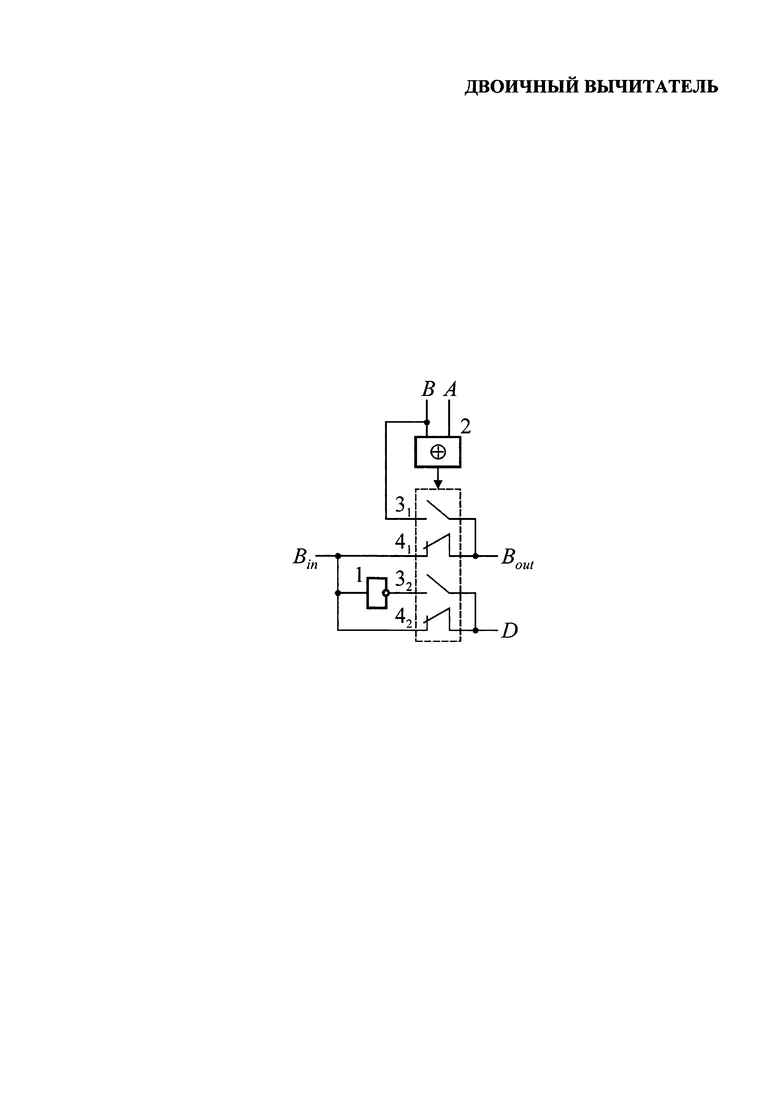

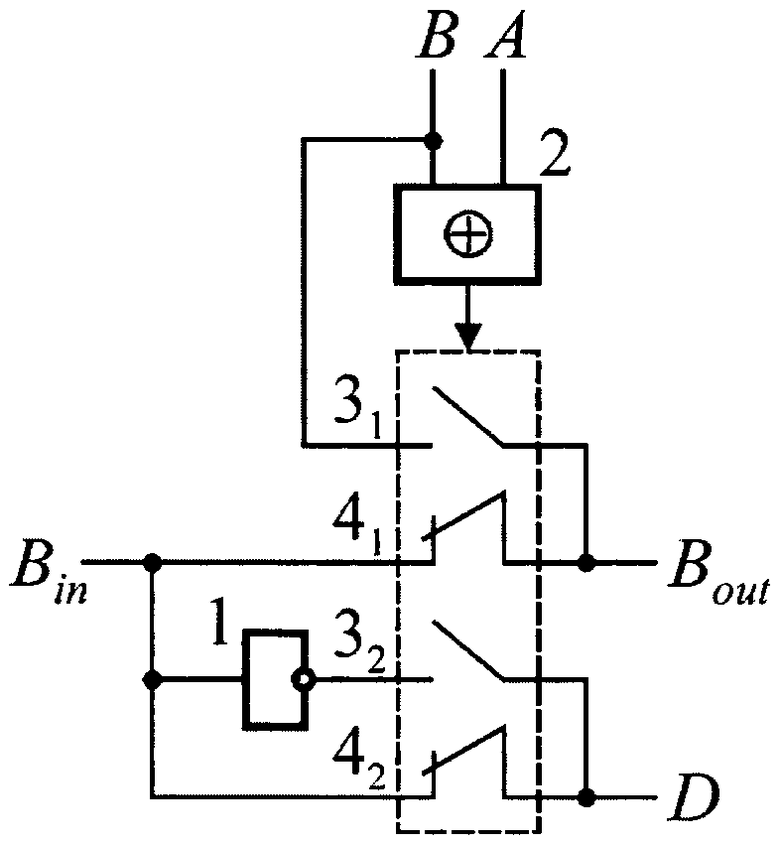

На чертеже представлена схема предлагаемого двоичного вычитателя.

Двоичный вычитатель содержит элемент НЕ 1, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 2, замыкающие ключи 31, 32 и размыкающие ключи 41, 42, причем входы ключей 32 и 31 соединены соответственно с выходом элемента 1 и вторым входом элемента 2, подсоединенного выходом к управляющему входу всех ключей, а выход ключа 3j  соединен с выходом ключа 4j и j-ым выходом двоичного вычитателя, подсоединенного j-ым и третьим входами соответственно к j-му входу элемента 2 и входу элемента 1, входу ключа 4j.

соединен с выходом ключа 4j и j-ым выходом двоичного вычитателя, подсоединенного j-ым и третьим входами соответственно к j-му входу элемента 2 и входу элемента 1, входу ключа 4j.

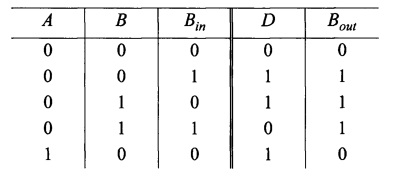

Работа предлагаемого двоичного вычитателя осуществляется следующим образом. На его первый, второй, третий входы подаются соответственно двоичные сигналы A, B, Bin ∈ {0,1}. Если на управляющем входе ключей 31, 32, 41, 42 присутствует логическая «1» (логический «0»), то ключи 31, 32 замкнуты (разомкнуты), а ключи 41, 42 разомкнуты (замкнуты). В представленной ниже таблице приведены полученные с учетом работы ключей значения действующих на первом, втором выходах предлагаемого вычитателя сигналов Bout, D для всех возможных наборов значений сигналов А, В, Bin.

Представленная таблица совпадает с таблицей (рис. 9.10б на стр. 219 в книге Токхейм Р. Основы цифровой электроники. М.: Мир, 1988 г.), согласно которой реализуется операция A-B-Bin.

Вышеизложенные сведения позволяют сделать вывод, что предлагаемый двоичный вычитатель выполняет операцию A-B-Bin, где A, B, Bin ∈ {0,1} есть входные двоичные сигналы, и является по сравнению с прототипом более простым, так как цена по Квайну предлагаемого вычитателя равна 8 и в нем отсутствуют места пересечения соединений.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО СРАВНЕНИЯ ДВОИЧНЫХ ЧИСЕЛ | 2012 |

|

RU2504825C1 |

| ДВОИЧНЫЙ ВЫЧИТАТЕЛЬ | 2019 |

|

RU2709653C1 |

| ВЫЧИТАТЕЛЬ ПО МОДУЛЮ q | 2021 |

|

RU2770798C1 |

| УМНОЖИТЕЛЬ ПО МОДУЛЮ q | 2019 |

|

RU2713862C1 |

| ДВОИЧНЫЙ ВЫЧИТАТЕЛЬ | 2016 |

|

RU2629453C1 |

| СУММАТОР ПО МОДУЛЮ ТРИ | 2019 |

|

RU2708793C1 |

| СУММАТОР-УМНОЖИТЕЛЬ ПО МОДУЛЮ ТРИ | 2020 |

|

RU2762548C1 |

| СУММАТОР ПО МОДУЛЮ ТРИ | 2019 |

|

RU2703676C1 |

| УСТРОЙСТВО СОРТИРОВКИ ДВОИЧНЫХ ЧИСЕЛ | 2004 |

|

RU2264645C1 |

| ДВОИЧНЫЙ ВЫЧИТАТЕЛЬ | 2022 |

|

RU2789722C1 |

Изобретение относится к вычислительной технике. Технический результат заключается в упрощении двоичного вычитателя. Двоичный вычитатель предназначен для выполнения операции А-В-Bin, где А, В, Bin ∈ {0,1} есть входные двоичные сигналы, и может быть использован в системах цифровой вычислительной техники как средство арифметической обработки дискретной информации. Двоичный вычитатель содержит элемент НЕ (1), элемент ИСКЛЮЧАЮЩЕЕ ИЛИ (2), два замыкающих и два размыкающих ключа (31, 32 и 41, 42). За счет указанного аппаратурного состава достигнуто уменьшение цены по Квайну и устранение мест пересечения соединений. 1 ил., 1 табл.

Двоичный вычитатель, содержащий элемент НЕ и элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, j-й  вход которого соединен с j-ым входом двоичного вычитателя, отличающийся тем, что в него дополнительно введены два замыкающих и два размыкающих ключа, причем вход второго и вход первого замыкающих ключей соединены соответственно с выходом элемента НЕ и вторым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, подсоединенного выходом к управляющему входу всех ключей, а выход j-го замыкающего ключа соединен с выходом j-го размыкающего ключа и j-ым выходом двоичного вычитателя, подсоединенного третьим входом к входу элемента НЕ и входу j-го размыкающего ключа.

вход которого соединен с j-ым входом двоичного вычитателя, отличающийся тем, что в него дополнительно введены два замыкающих и два размыкающих ключа, причем вход второго и вход первого замыкающих ключей соединены соответственно с выходом элемента НЕ и вторым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, подсоединенного выходом к управляющему входу всех ключей, а выход j-го замыкающего ключа соединен с выходом j-го размыкающего ключа и j-ым выходом двоичного вычитателя, подсоединенного третьим входом к входу элемента НЕ и входу j-го размыкающего ключа.

| Одноразрядный двоичный вычитатель | 1983 |

|

SU1124289A1 |

| Одноразрядный двоичный вычитатель | 1982 |

|

SU1043639A1 |

| Последовательный двоичный вычитатель | 1984 |

|

SU1171781A1 |

| ШКАЛЬНОЕ УСТРОЙСТВО | 0 |

|

SU185504A1 |

| US 3424898 A1, 28.01.1969 | |||

| US 3482085 A1, 02.12.1969. | |||

Авторы

Даты

2017-06-02—Публикация

2015-12-08—Подача