Изобретение относится к вычислительной технике и может быть использовано для построения средств автоматики, функциональных узлов систем управления и др.

Известны двоичные вычитатели (см., например, рис. 9.11в на стр. 220 в книге Токхейм Р. Основы цифровой электроники. М.: Мир, 1988 г.), которые могут быть использованы для формирования двоичного кода разности двух одноразрядных двоичных чисел, задаваемых двоичными сигналами, и формирования бита, определяющего ее знак.

К причине, препятствующей достижению указанного ниже технического результата при использовании известных двоичных вычитателей, относятся элементный базис, образованный логическими элементами четырех типов, и ограниченные функциональные возможности, обусловленные тем, что не допускается обработка трехразрядных двоичных чисел.

Наиболее близким устройством того же назначения к заявленному изобретению по совокупности признаков является принятый за прототип двоичный вычитатель (рис. 9.9б на стр. 219 в книге Токхейм Р. Основы цифровой электроники. М.: Мир, 1988 г.), который содержит элемент И, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, элемент НЕ и формирует двоичный код разности двух одноразрядных двоичных чисел, задаваемых двоичными сигналами, и бит, определяющий ее знак.

К причине, препятствующей достижению указанного ниже технического результата при использовании прототипа, относятся ограниченные функциональные возможности, обусловленные тем, что не допускается обработка трехразрядных двоичных чисел.

Техническим результатом изобретения является расширение функциональных возможностей за счет обеспечения формирования двоичного кода разности двух трехразрядных двоичных чисел, задаваемых двоичными сигналами, и формирования бита, определяющего ее знак, при сохранении элементного базиса прототипа.

Указанный технический результат при осуществлении изобретения достигается тем, что в двоичном вычитателе, содержащем элемент И, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, элемент НЕ, особенность заключается в том, что в него дополнительно введены семь элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, пять элементов НЕ и пять элементов И, причем первый, второй входы i-го  элемента ИСКЛЮЧАЮЩЕЕ ИЛИ и второй вход i-го элемента И соединены соответственно с первым входом i-го элемента И, входом и выходом i-го элемента НЕ, первый, второй входы j-го (j∈{4,5}) и первый, второй входы k-го (k∈{6,8}) элементов ИСКЛЮЧАЮЩЕЕ ИЛИ соединены соответственно с выходами (j-3)-го элемента И, (j-2)-го элемента ИСКЛЮЧАЮЩЕЕ ИЛИ и выходами (k-2)-го элемента И, (k-1)-го элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, а первый, второй входы седьмого и первый, второй входы r-го

элемента ИСКЛЮЧАЮЩЕЕ ИЛИ и второй вход i-го элемента И соединены соответственно с первым входом i-го элемента И, входом и выходом i-го элемента НЕ, первый, второй входы j-го (j∈{4,5}) и первый, второй входы k-го (k∈{6,8}) элементов ИСКЛЮЧАЮЩЕЕ ИЛИ соединены соответственно с выходами (j-3)-го элемента И, (j-2)-го элемента ИСКЛЮЧАЮЩЕЕ ИЛИ и выходами (k-2)-го элемента И, (k-1)-го элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, а первый, второй входы седьмого и первый, второй входы r-го  элементов ИСКЛЮЧАЮЩЕЕ ИЛИ соединены соответственно с выходами пятого, третьего элементов И и r-м, (3+r)-м входами двоичного вычитателя, первый, второй, третий и четвертый выходы которого образованы соответственно выходами первого, четвертого, шестого и восьмого элементов ИСКЛЮЧАЮЩЕЕ ИЛИ.

элементов ИСКЛЮЧАЮЩЕЕ ИЛИ соединены соответственно с выходами пятого, третьего элементов И и r-м, (3+r)-м входами двоичного вычитателя, первый, второй, третий и четвертый выходы которого образованы соответственно выходами первого, четвертого, шестого и восьмого элементов ИСКЛЮЧАЮЩЕЕ ИЛИ.

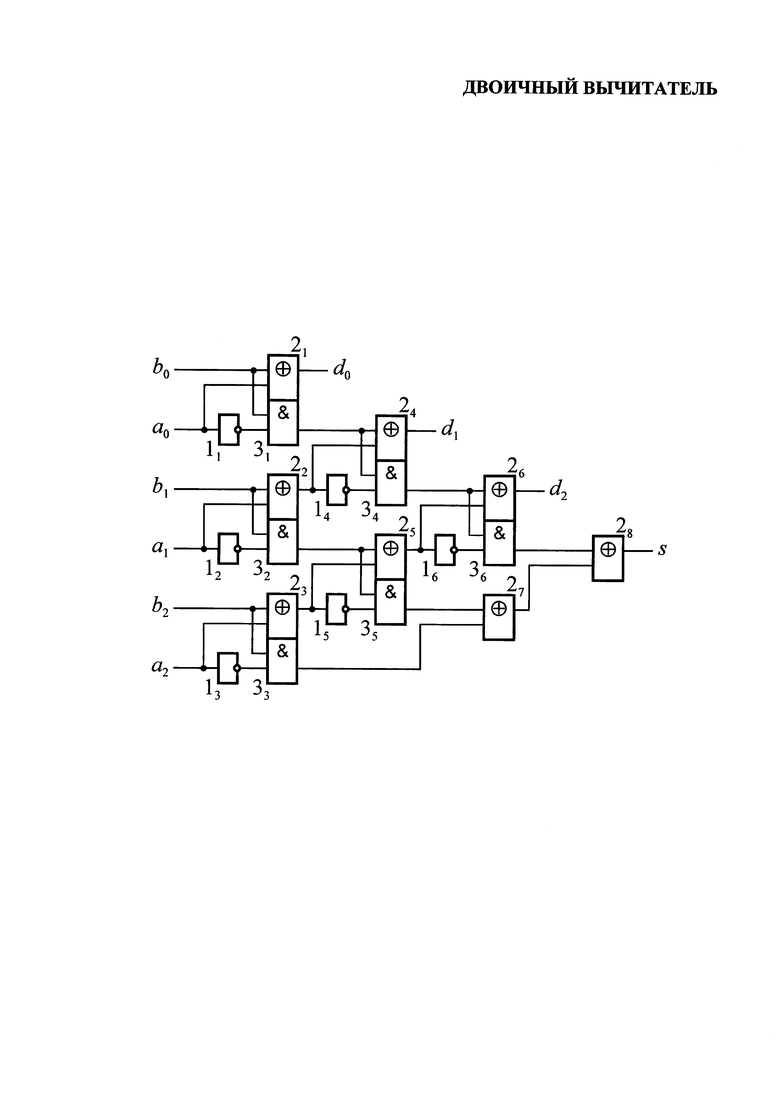

На чертеже представлена схема предлагаемого двоичного вычитателя.

Двоичный вычитатель содержит элементы НЕ 11, …, 16, элементы ИСКЛЮЧАЮЩЕЕ ИЛИ 21, …, 28, элементы И 31, …, 36, причем первый, второй входы элемента 2i  и второй вход элемента 3i соединены соответственно с первым входом элемента 3i, входом и выходом элемента 1i, первый, второй входы элемента 2j (j∈{4,5}) и первый, второй входы элемента 2k (k∈{6,8}) соединены соответственно с выходами элементов 3j-3, 2j-2 и 3k-2, 2k-1, а первый, второй входы элемента 27 и первый, второй входы элемента 2r

и второй вход элемента 3i соединены соответственно с первым входом элемента 3i, входом и выходом элемента 1i, первый, второй входы элемента 2j (j∈{4,5}) и первый, второй входы элемента 2k (k∈{6,8}) соединены соответственно с выходами элементов 3j-3, 2j-2 и 3k-2, 2k-1, а первый, второй входы элемента 27 и первый, второй входы элемента 2r  соединены соответственно с выходами элементов 35, 33 и r-м, (3+r)-м входами двоичного вычитателя, первый, второй, третий и четвертый выходы которого образованы соответственно выходами элементов 21, 24, 26 и 28.

соединены соответственно с выходами элементов 35, 33 и r-м, (3+r)-м входами двоичного вычитателя, первый, второй, третий и четвертый выходы которого образованы соответственно выходами элементов 21, 24, 26 и 28.

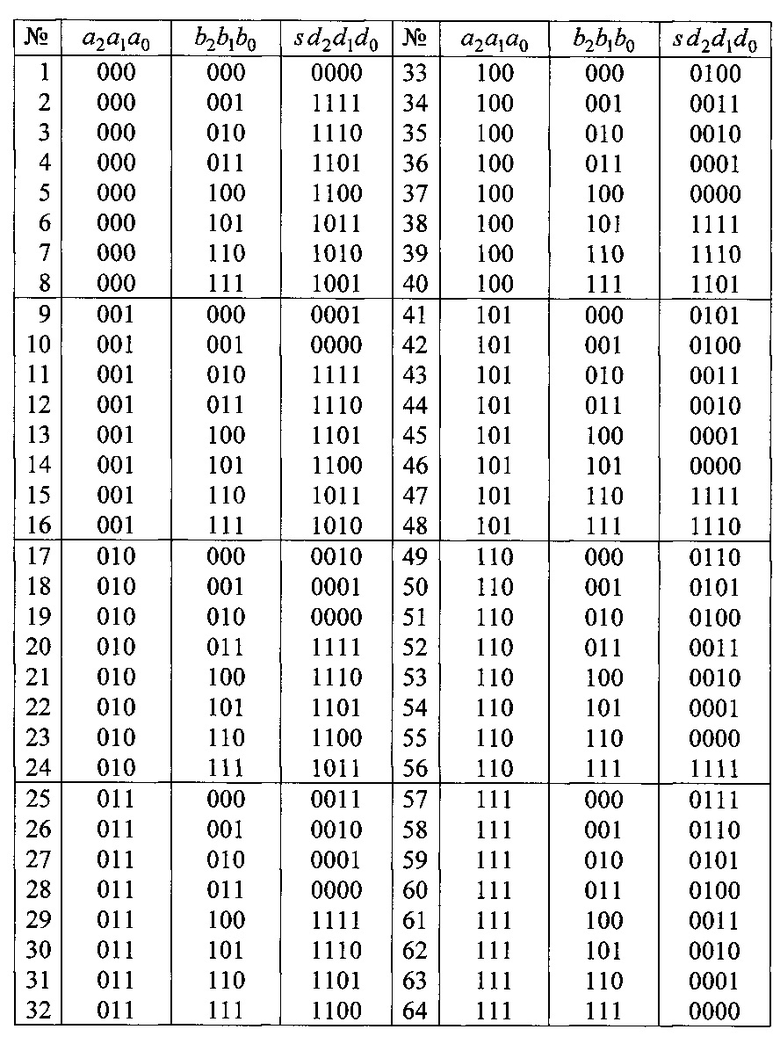

Работа предлагаемого двоичного вычитателя осуществляется следующим образом. На его первый, второй, третий и четвертый, пятый, шестой входы подаются соответственно двоичные сигналы b0, b1, b2 ∈ {0,1} и а0, а1, а2 ∈ {0,1}, которые задают трехразрядные двоичные числа B=b2b1b0, А=а2а1а0 так, что а2, b2 и а0, b0 есть старшие и младшие разряды соответственно. В приведенной ниже таблице указаны значения действующих на выходах предлагаемого вычитателя сигналов d0, d1, d2, s для всех возможных наборов значений сигналов a0, a1, a2, b0, b1, b2.

Таким образом, на выходах предлагаемого вычитателя получим трехразрядное двоичное число D=d2d1d0=А-В и бит s, определяющий его знак, причем если А≥В, то s=0, если А<В, то s=1 и разность D представлена в дополнительном коде.

Вышеизложенные сведения позволяют сделать вывод, что предлагаемый двоичный вычитатель построен в элементном базисе прототипа и обладает более широкими по сравнению с прототипом функциональными возможностями, поскольку обеспечивает обработку трехразрядных двоичных чисел.

| название | год | авторы | номер документа |

|---|---|---|---|

| ДВОИЧНЫЙ ВЫЧИТАТЕЛЬ | 2019 |

|

RU2709653C1 |

| ДВОИЧНЫЙ ВЫЧИТАТЕЛЬ | 2022 |

|

RU2789722C1 |

| ДВОИЧНЫЙ ВЫЧИТАТЕЛЬ | 2022 |

|

RU2789731C1 |

| КОМБИНАЦИОННЫЙ СУММАТОР | 2013 |

|

RU2514785C1 |

| ДВОИЧНЫЙ ВЫЧИТАТЕЛЬ | 2024 |

|

RU2840388C1 |

| ДВОИЧНЫЙ СУММАТОР | 2020 |

|

RU2758184C1 |

| ДВОИЧНЫЙ ВЫЧИТАТЕЛЬ | 2024 |

|

RU2829014C1 |

| ВЫЧИТАТЕЛЬ ПО МОДУЛЮ q | 2021 |

|

RU2770798C1 |

| УСТРОЙСТВО ДЛЯ КОРРЕКЦИИ ПОРЯДКА ПРИ НОРМАЛИЗАЦИИ ЧИСЕЛ | 2017 |

|

RU2638724C1 |

| КОМПАРАТОР ДВОИЧНЫХ ЧИСЕЛ | 2008 |

|

RU2361266C1 |

Изобретение относится к двоичныму вычитателю, который формирует двоичный код разности двух двоичных чисел, задаваемых двоичными сигналами, а также формирования бита, определяющего ее знак. Технический результат заключается в обеспечении обработки трехразрядных двоичных чисел. Двоичный вычитатель содержит шесть элементов НЕ (11, …, 16), восемь элементов ИСКЛЮЧАЮЩЕЕ ИЛИ (21, …, 28) и шесть элементов И (31, …, 36). 1 ил., 1 табл.

Двоичный вычитатель, содержащий элемент И, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, элемент НЕ, отличающийся тем, что в него дополнительно введены семь элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, пять элементов НЕ и пять элементов И, причем первый, второй входы i-го  элемента ИСКЛЮЧАЮЩЕЕ ИЛИ и второй вход i-го элемента И соединены соответственно с первым входом i-го элемента И, входом и выходом i-го элемента НЕ, первый, второй входы j-го (j∈{4,5}) и первый, второй входы k-го (k∈{6,8}) элементов ИСКЛЮЧАЮЩЕЕ ИЛИ соединены соответственно с выходами (j-3)-го элемента И, (j-2)-го элемента ИСКЛЮЧАЮЩЕЕ ИЛИ и выходами (k-2)-го элемента И, (k-1)-го элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, а первый, второй входы седьмого и первый, второй входы r-го

элемента ИСКЛЮЧАЮЩЕЕ ИЛИ и второй вход i-го элемента И соединены соответственно с первым входом i-го элемента И, входом и выходом i-го элемента НЕ, первый, второй входы j-го (j∈{4,5}) и первый, второй входы k-го (k∈{6,8}) элементов ИСКЛЮЧАЮЩЕЕ ИЛИ соединены соответственно с выходами (j-3)-го элемента И, (j-2)-го элемента ИСКЛЮЧАЮЩЕЕ ИЛИ и выходами (k-2)-го элемента И, (k-1)-го элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, а первый, второй входы седьмого и первый, второй входы r-го  элементов ИСКЛЮЧАЮЩЕЕ ИЛИ соединены соответственно с выходами пятого, третьего элементов И и r-м, (3+r)-м входами двоичного вычитателя, первый, второй, третий и четвертый выходы которого образованы соответственно выходами первого, четвертого, шестого и восьмого элементов ИСКЛЮЧАЮЩЕЕ ИЛИ.

элементов ИСКЛЮЧАЮЩЕЕ ИЛИ соединены соответственно с выходами пятого, третьего элементов И и r-м, (3+r)-м входами двоичного вычитателя, первый, второй, третий и четвертый выходы которого образованы соответственно выходами первого, четвертого, шестого и восьмого элементов ИСКЛЮЧАЮЩЕЕ ИЛИ.

| Последовательный двоичный вычитатель | 1984 |

|

SU1171781A1 |

| Счетчик для вычитания | 1984 |

|

SU1228276A1 |

| Одноразрядный двоичный вычитатель | 1982 |

|

SU1043639A1 |

| CN 101201731 A, 18.06.2008. | |||

Авторы

Даты

2017-08-29—Публикация

2016-04-19—Подача