Перекрестные ссылки на родственные заявки

Данная заявка основана и испрашивает приоритет по предварительной заявке на патент США № 61/803,997, поданной 21 марта 2013 года, и заявке на патент США № 14/020,534, поданной 6 сентября 2013 года, содержимое всех из которых полностью содержится в данном документе по ссылке.

Область техники, к которой относится изобретение

Варианты осуществления, описанные в данном документе, в общем, относятся к энергонезависимому оперативному запоминающему устройству.

Уровень техники

Энергонезависимые оперативные запоминающие устройства, к примеру, магнитное оперативное запоминающее устройство, исследованы и разработаны в качестве запоминающих устройств для замены энергозависимых запоминающих устройств, к примеру, DRAM и SRAM.

Чтобы уменьшать затраты на разработку и выполнять плавную замену, желательно управлять энергонезависимыми оперативными запоминающими устройствами посредством использования спецификаций, идентичных спецификациям DRAM и SRAM. Также можно достигать низкой потребляемой мощности и вычислений в нормально разомкнутом режиме посредством использования энергонезависимых оперативных запоминающих устройств, например, посредством увеличения числа банков, формирующих матрицу ячеек запоминающего устройства, и минимизации числа банков, которые должны активироваться, из числа этих банков.

Тем не менее, если число банков, формирующих матрицу ячеек запоминающего устройства, увеличивается, число битов адреса для выбора каждого из этих банков также увеличивается. Чтобы достигать спецификаций, идентичных спецификациям универсального DRAM и SRAM, как описано выше, необходимо сконструировать систему, в которой число штырьковых выводов не увеличивается, и скорость работы не снижается, даже когда число битов адреса увеличивается.

Краткое описание чертежей

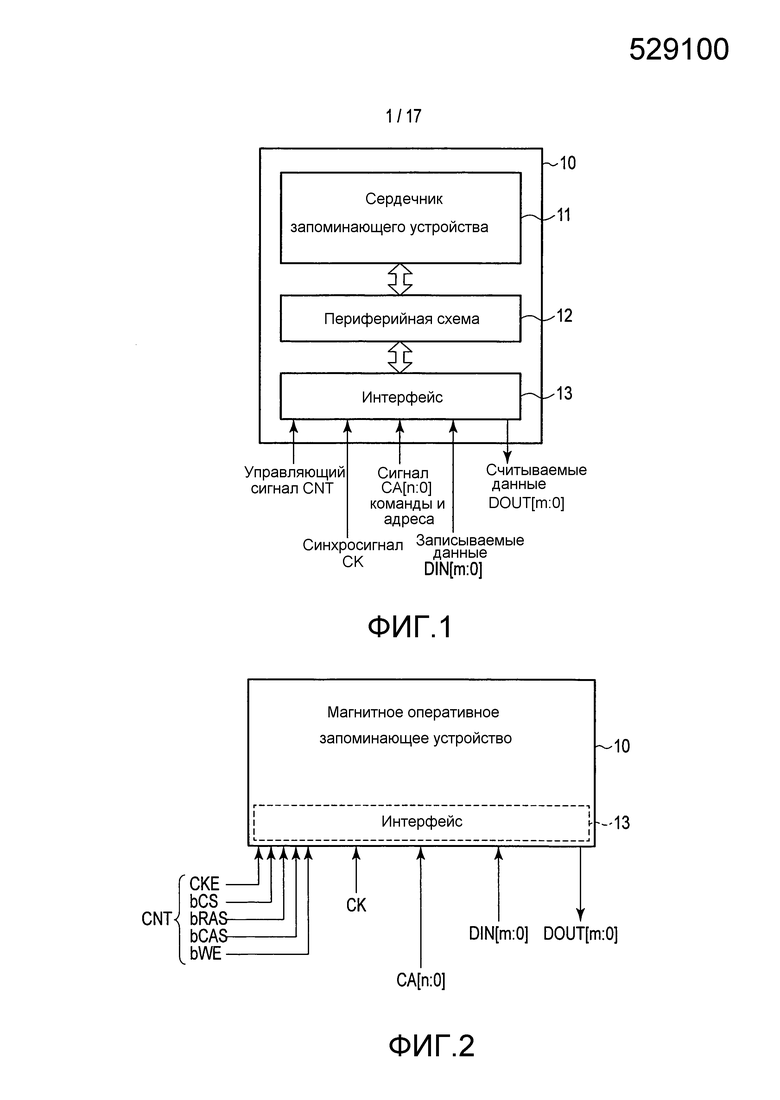

Фиг. 1 является видом, показывающим энергонезависимое оперативное запоминающее устройство;

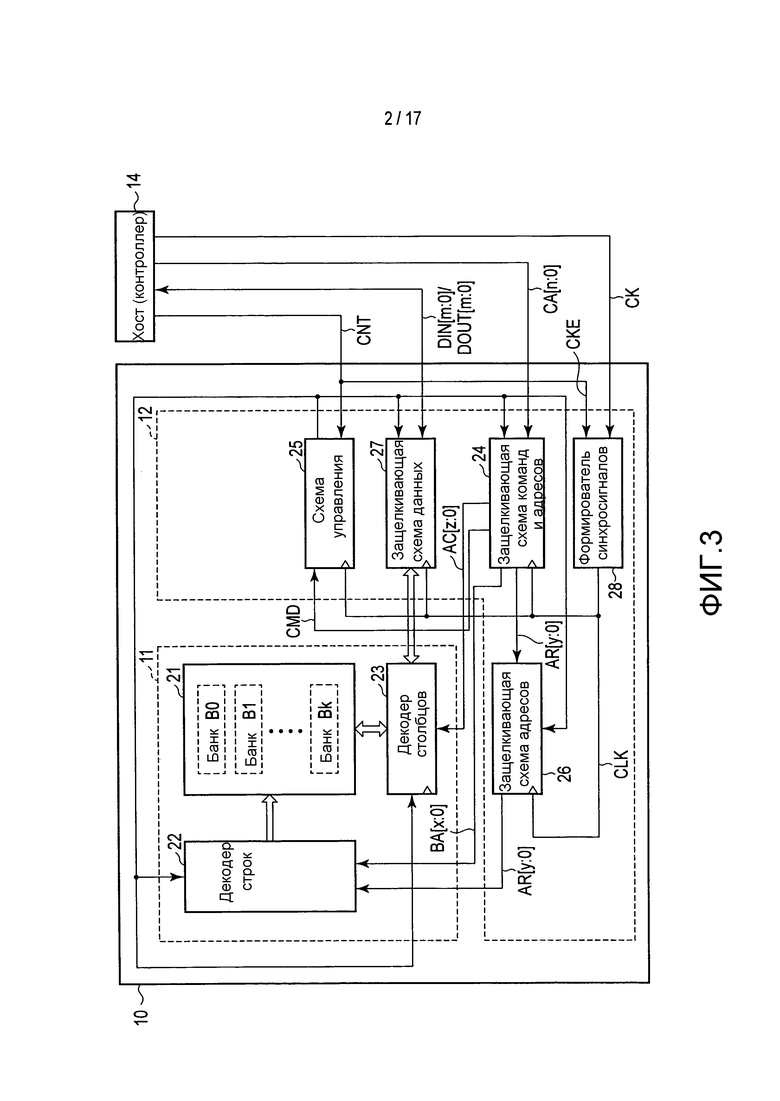

Фиг. 2 является видом, показывающим спецификации интерфейса;

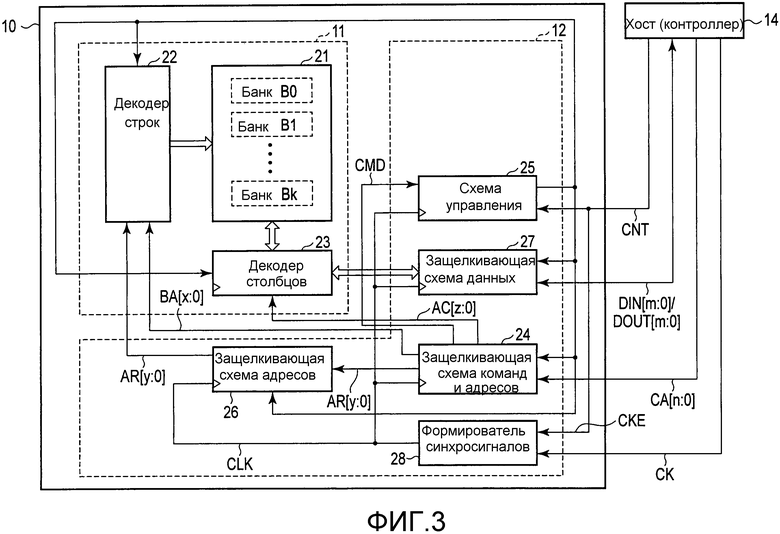

Фиг. 3 является видом, показывающим ядро запоминающего устройства и периферийную схему;

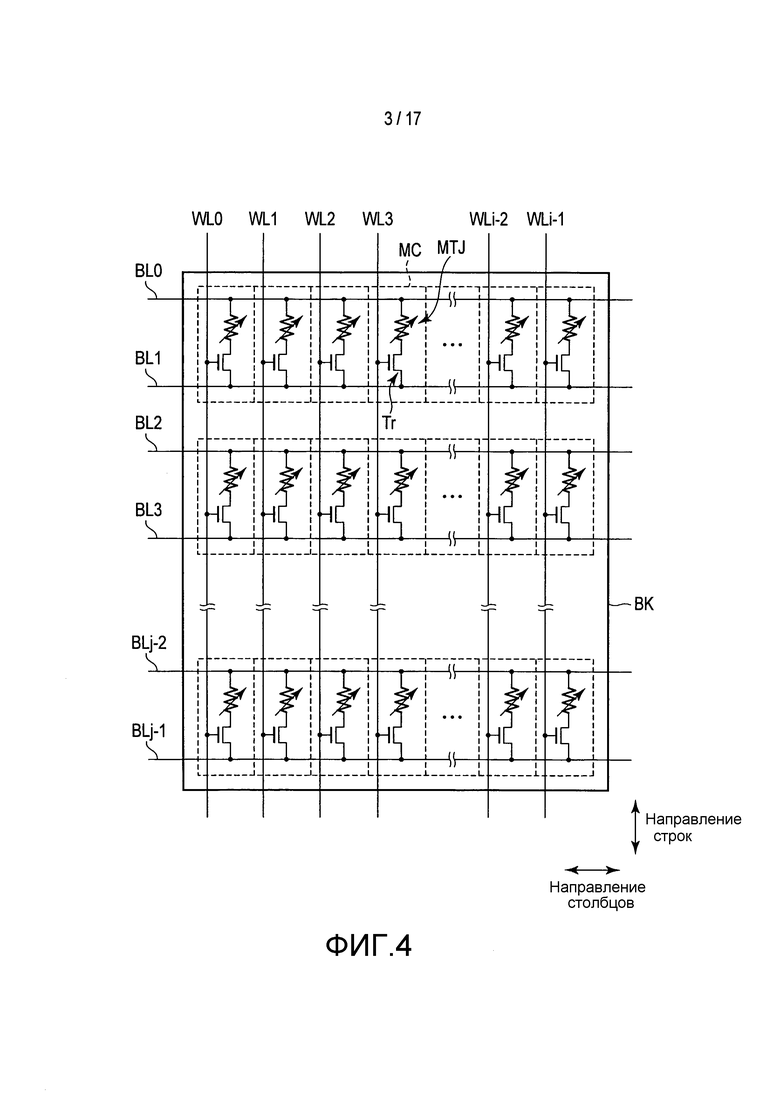

Фиг. 4 является видом, показывающим матрицу ячеек запоминающего устройства;

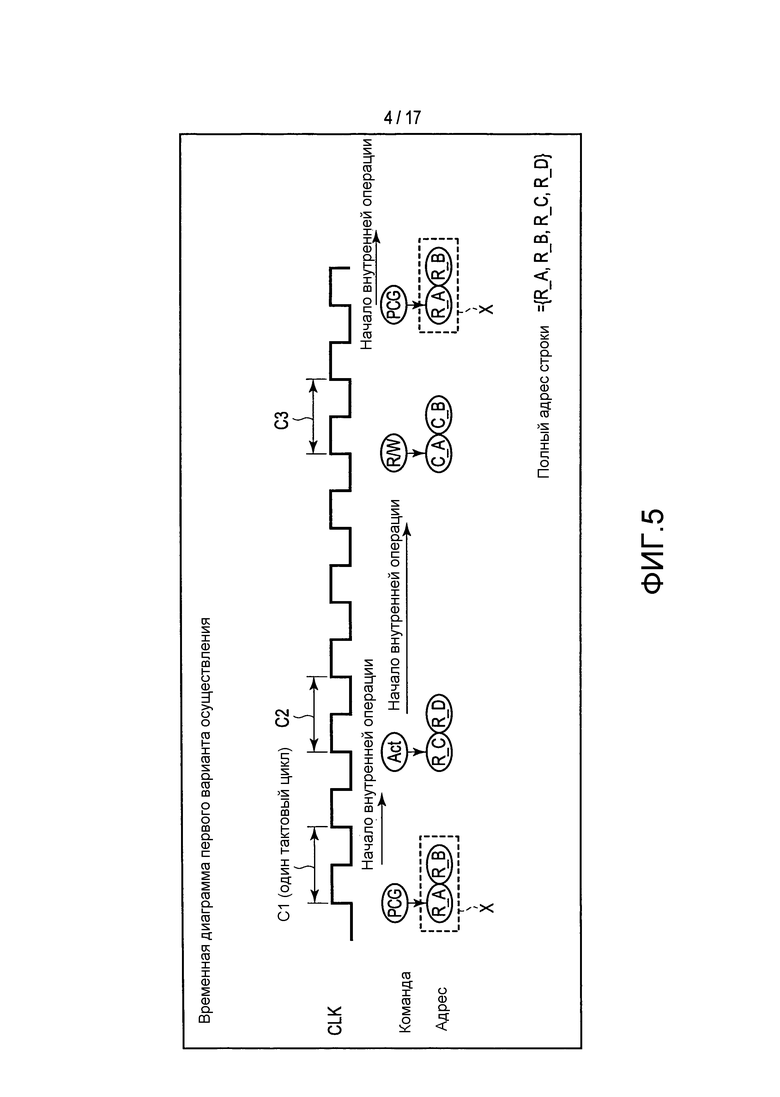

Фиг. 5 является временной диаграммой, показывающей первый вариант осуществления;

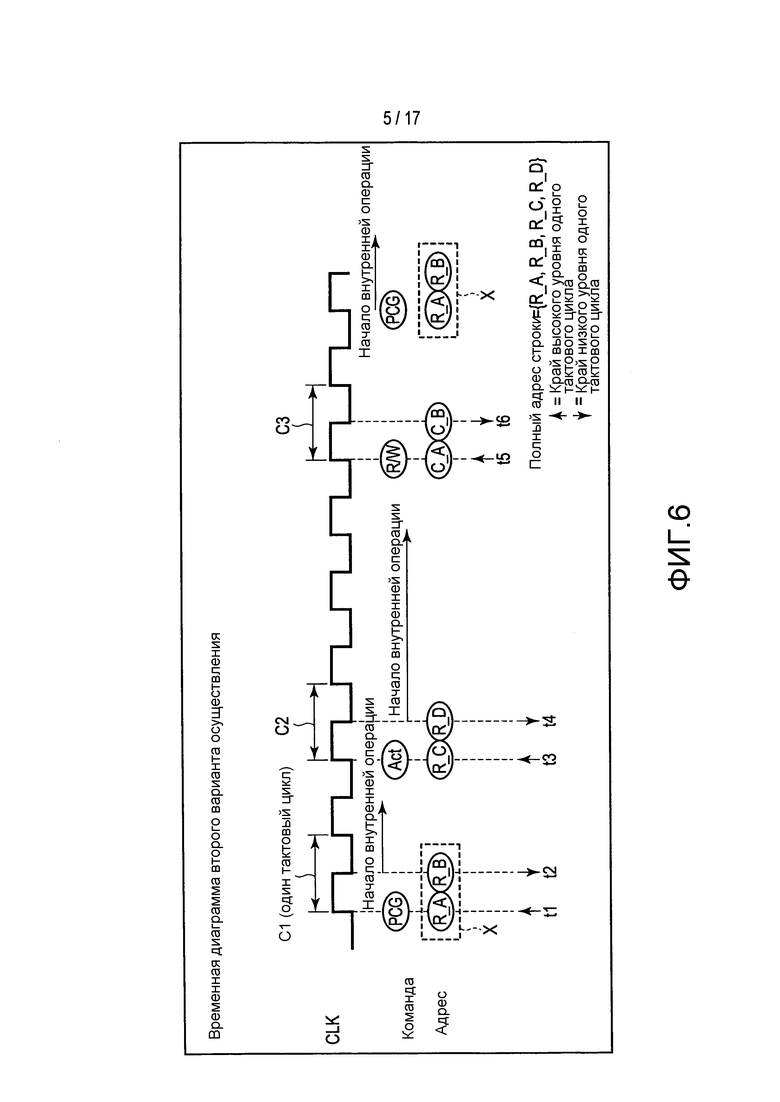

Фиг. 6 является временной диаграммой, показывающей второй вариант осуществления;

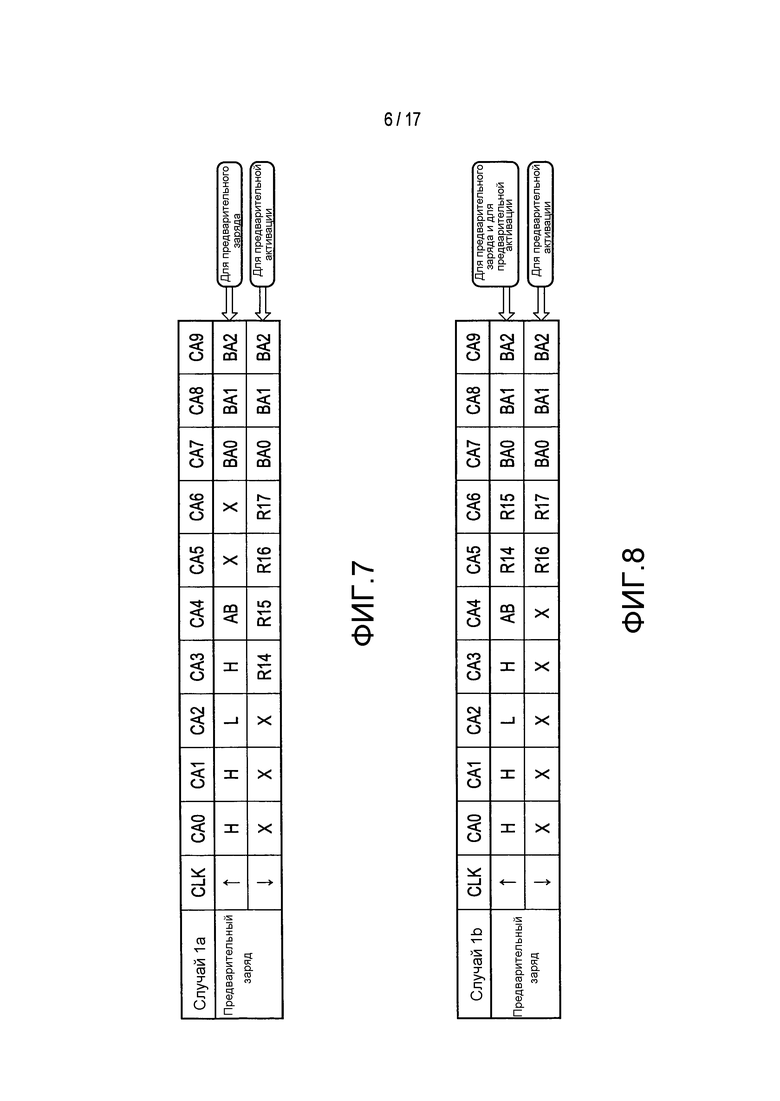

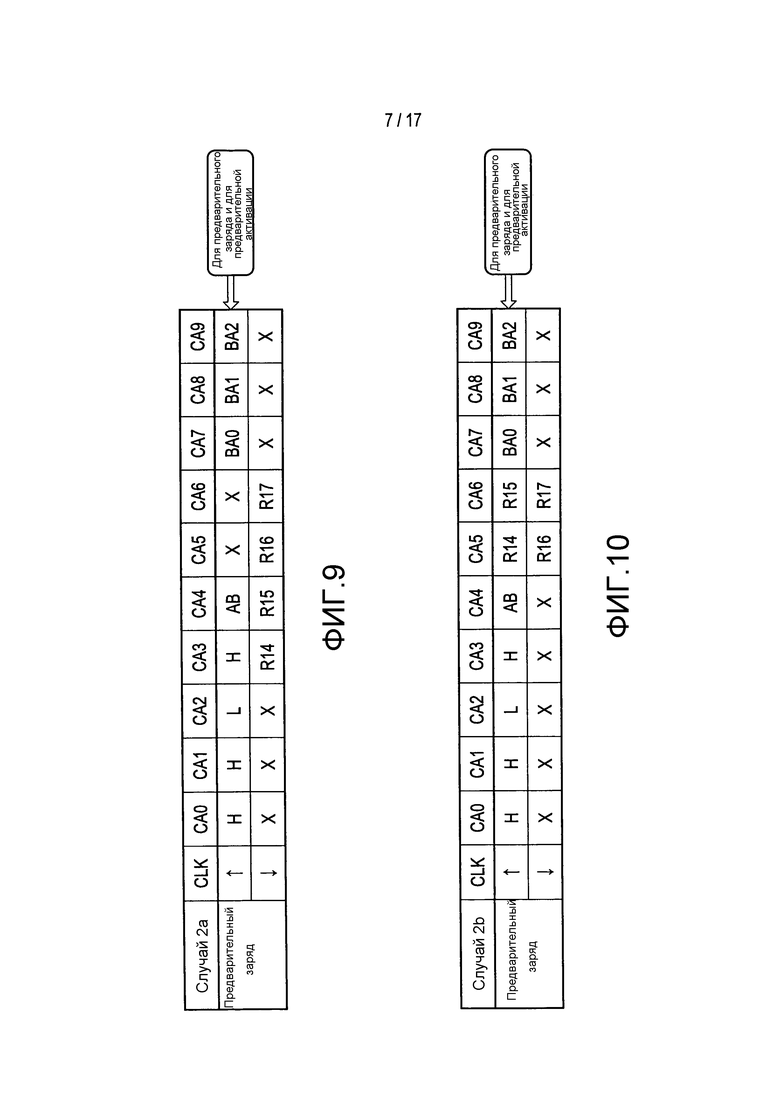

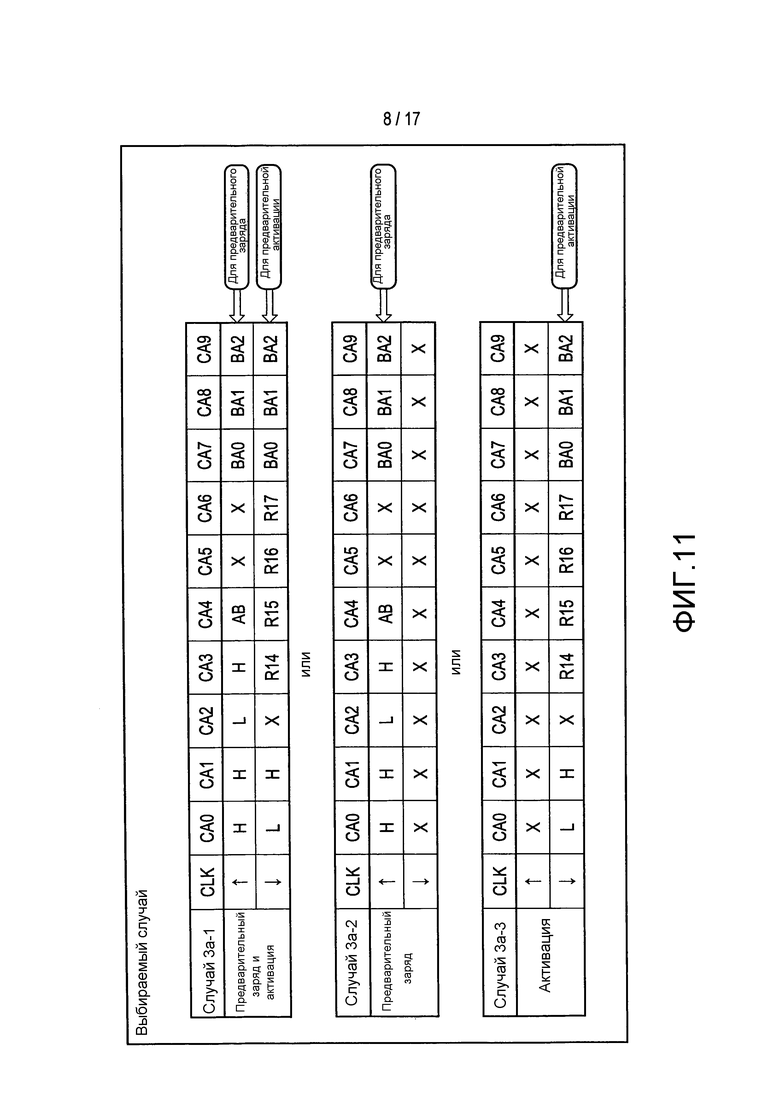

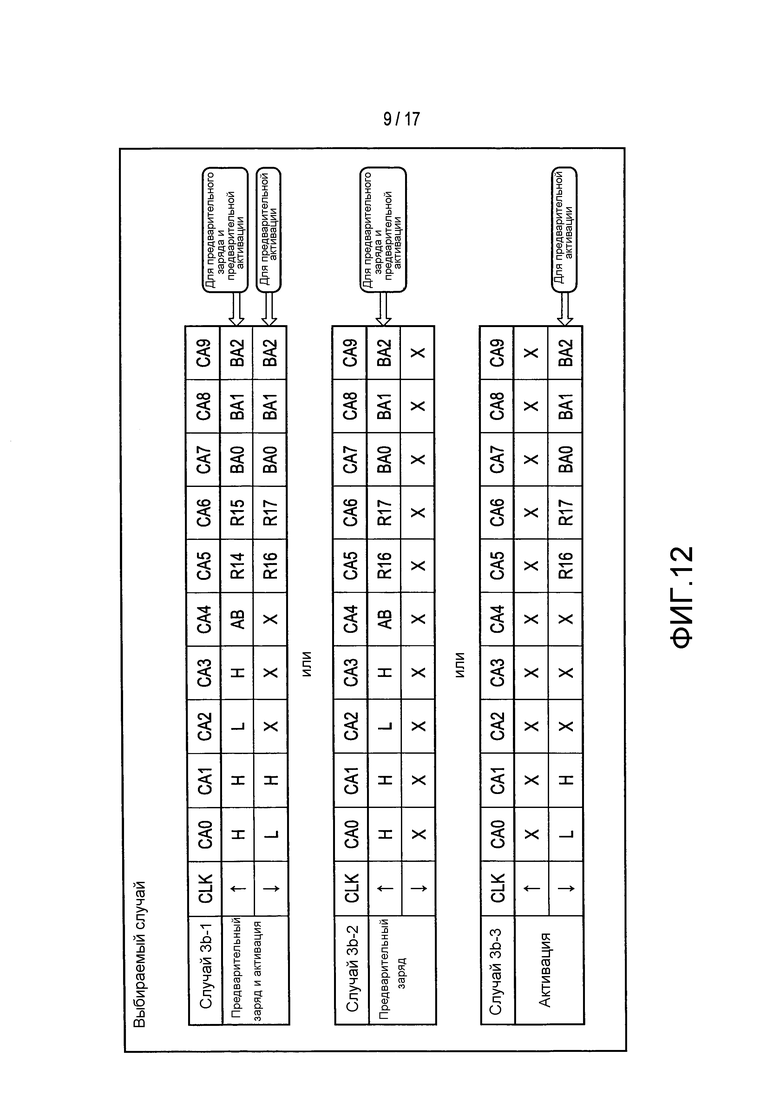

Фиг. 7, 8, 9, 10, 11 и 12 являются видами, показывающими примеры загрузки команд и адресов второго варианта осуществления;

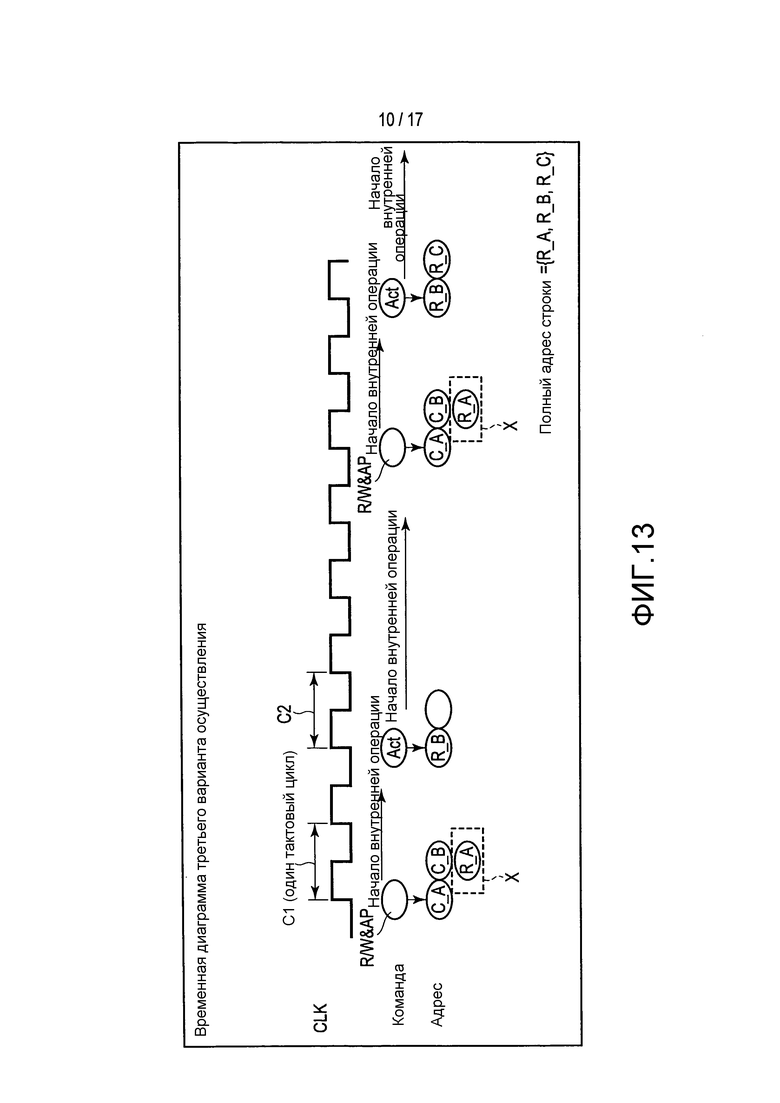

Фиг. 13 является временной диаграммой, показывающей третий вариант осуществления;

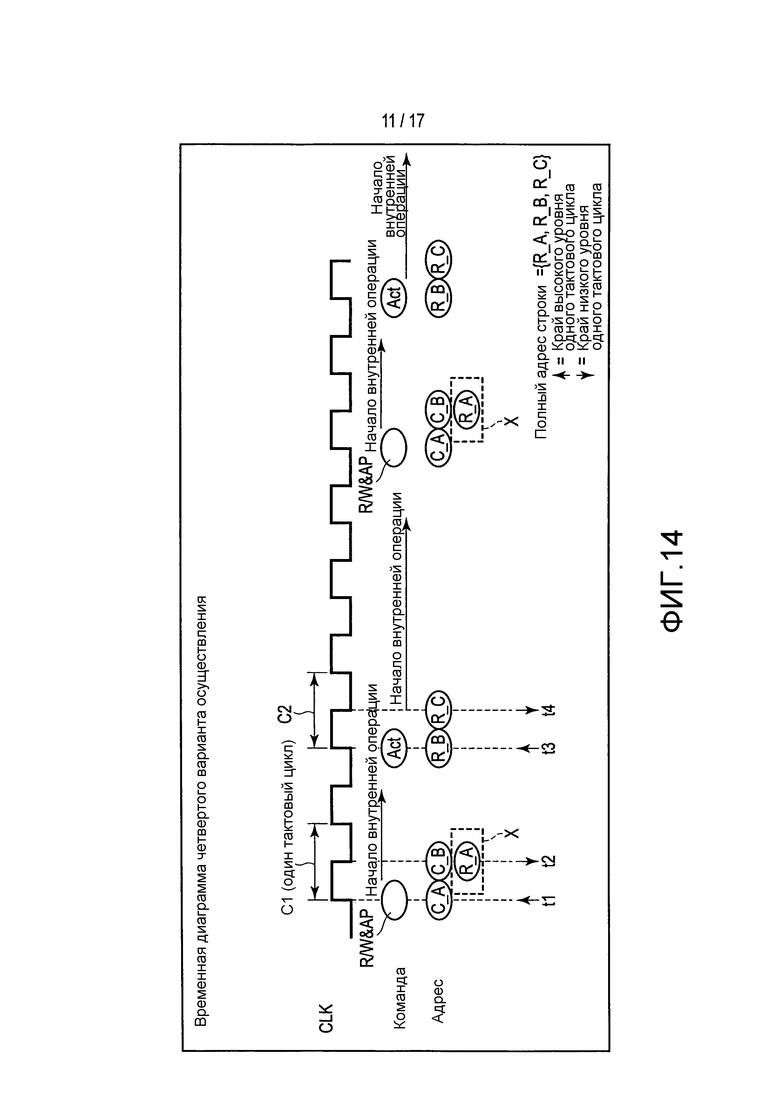

Фиг. 14 является временной диаграммой, показывающей четвертый вариант осуществления;

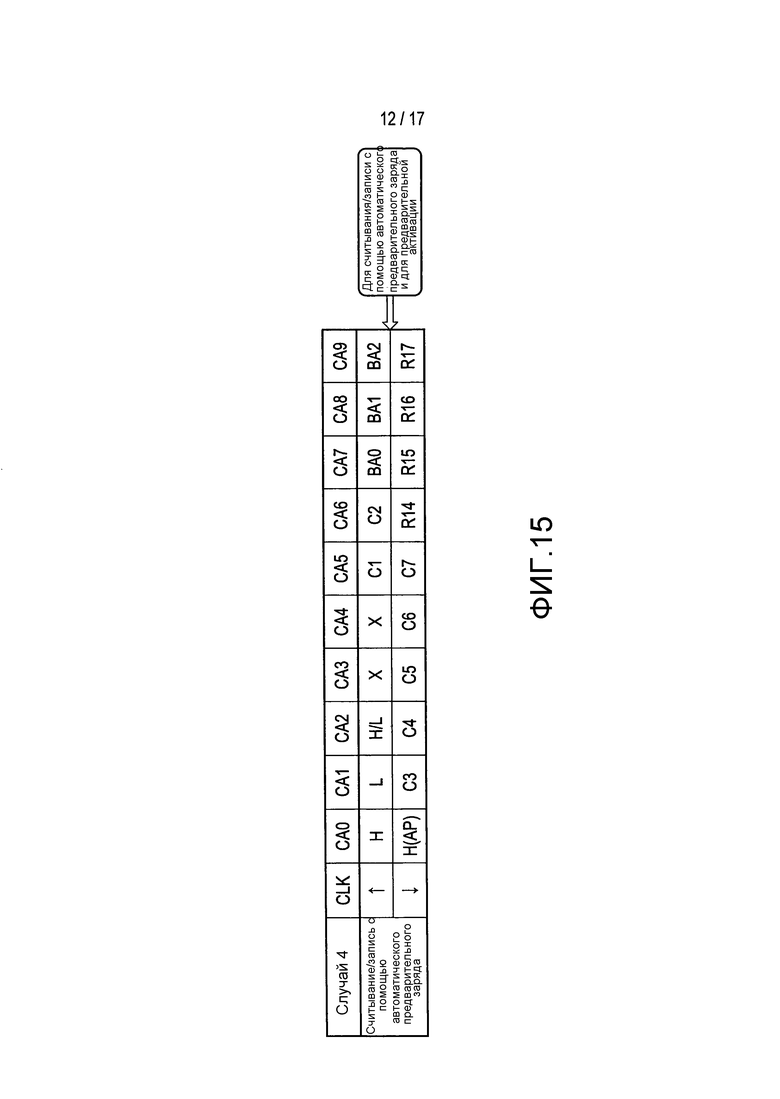

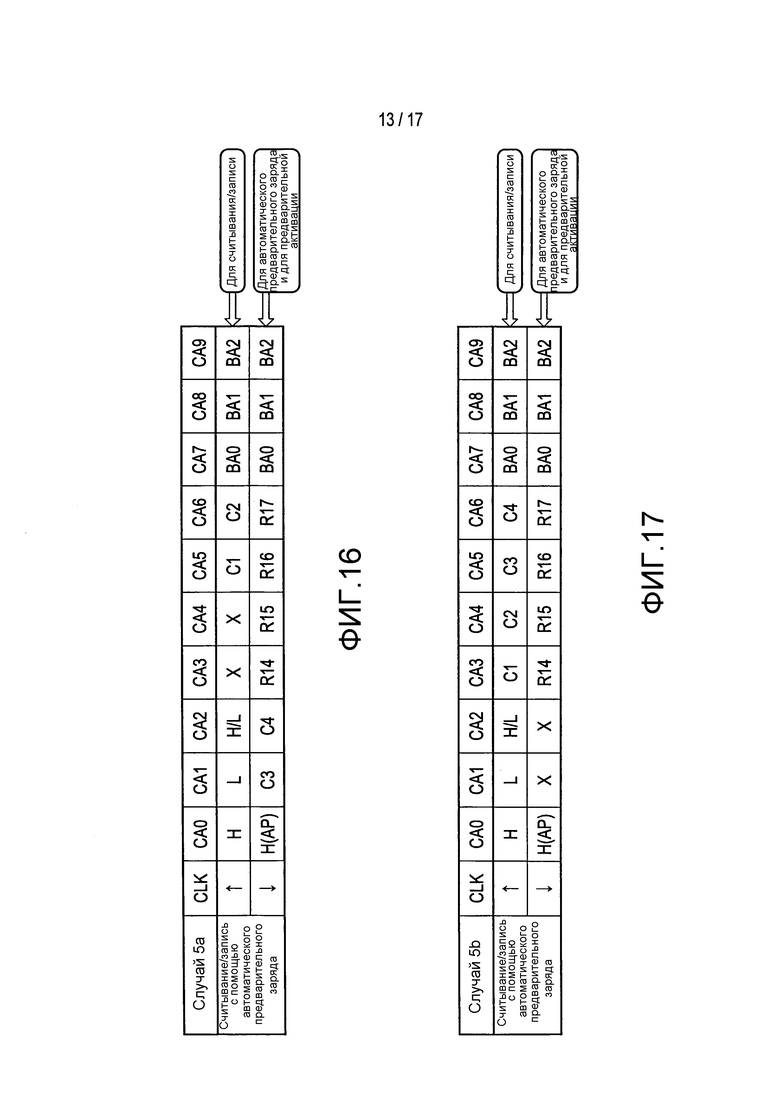

Фиг. 15, 16 и 17 являются видами, показывающими примеры загрузки команд и адресов четвертого варианта осуществления;

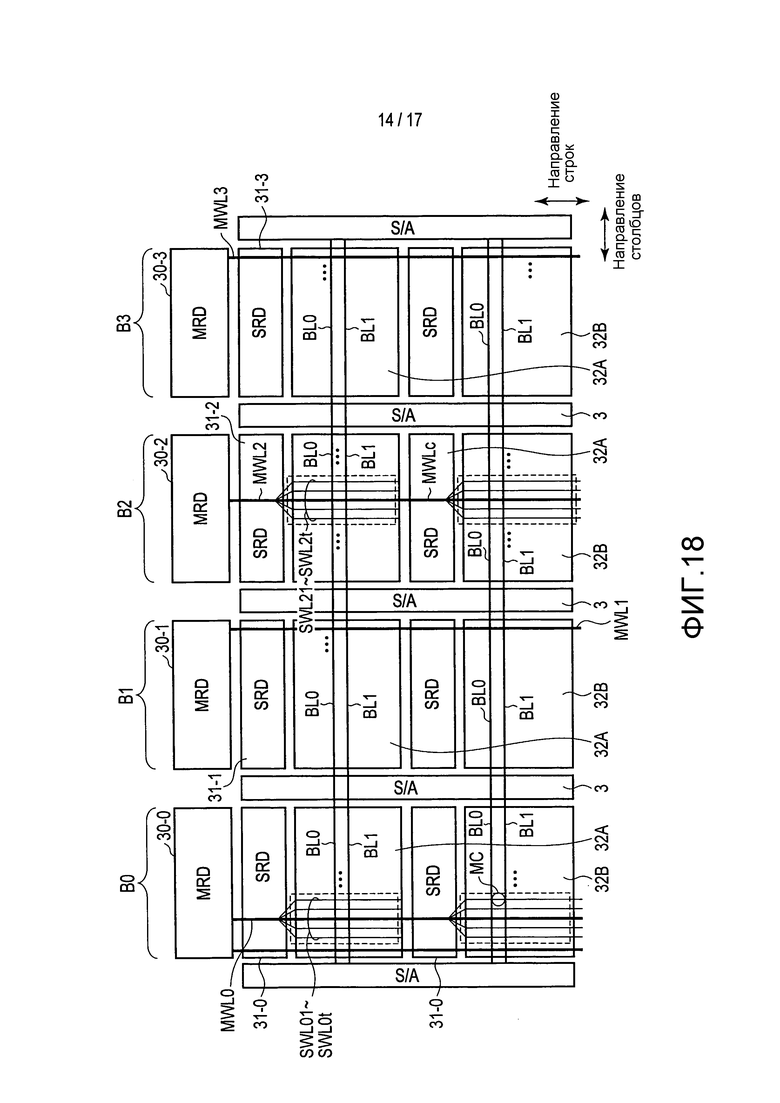

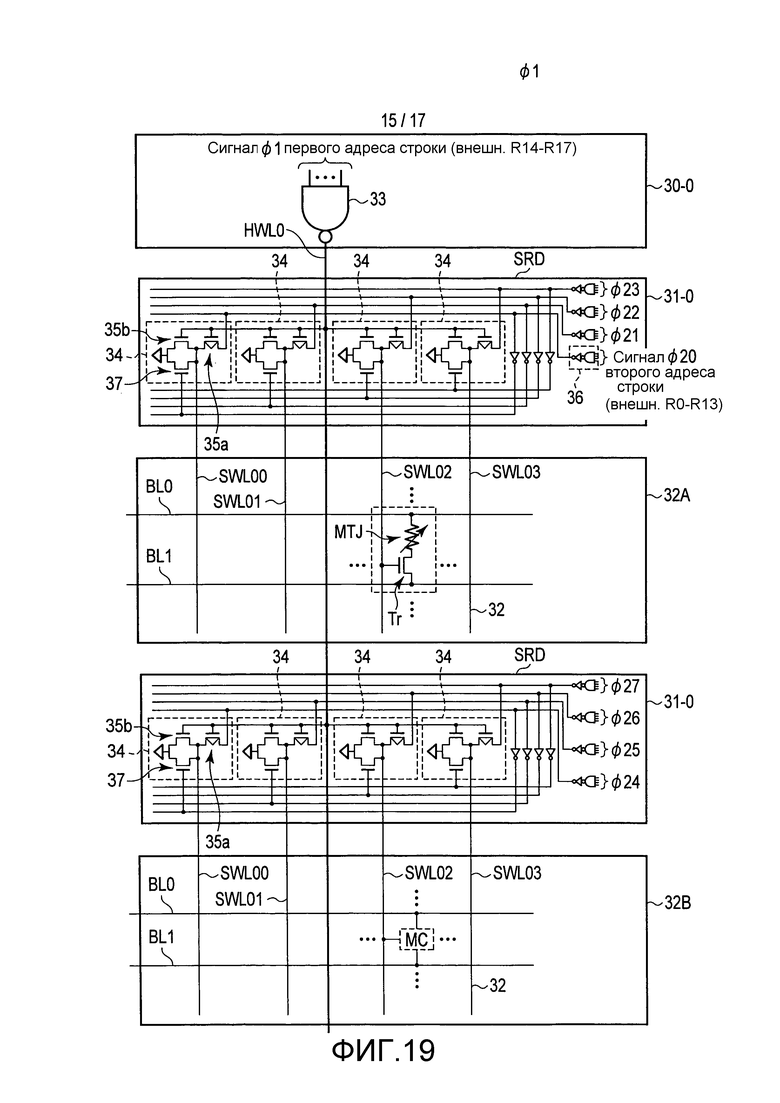

Фиг. 18 и 19 являются видами, показывающими иерархическую структуру линий слова;

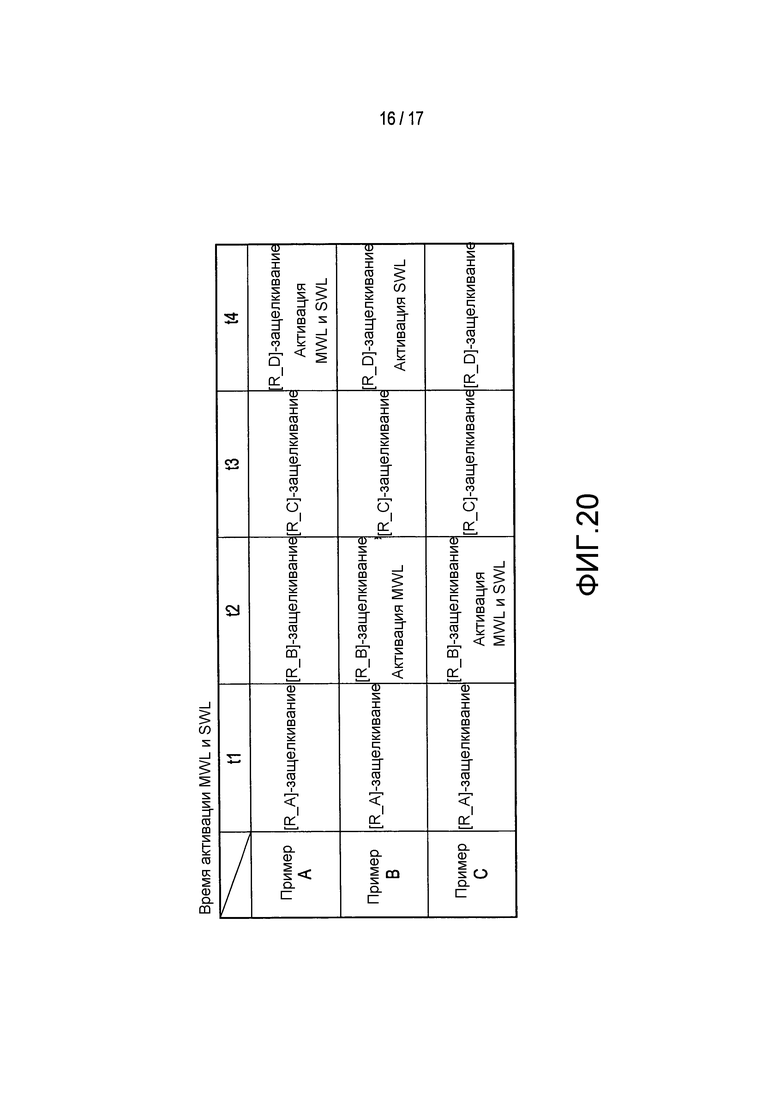

Фиг. 20 является видом, показывающим варьирование времен активации основных/дополнительных линий слова второго варианта осуществления; и

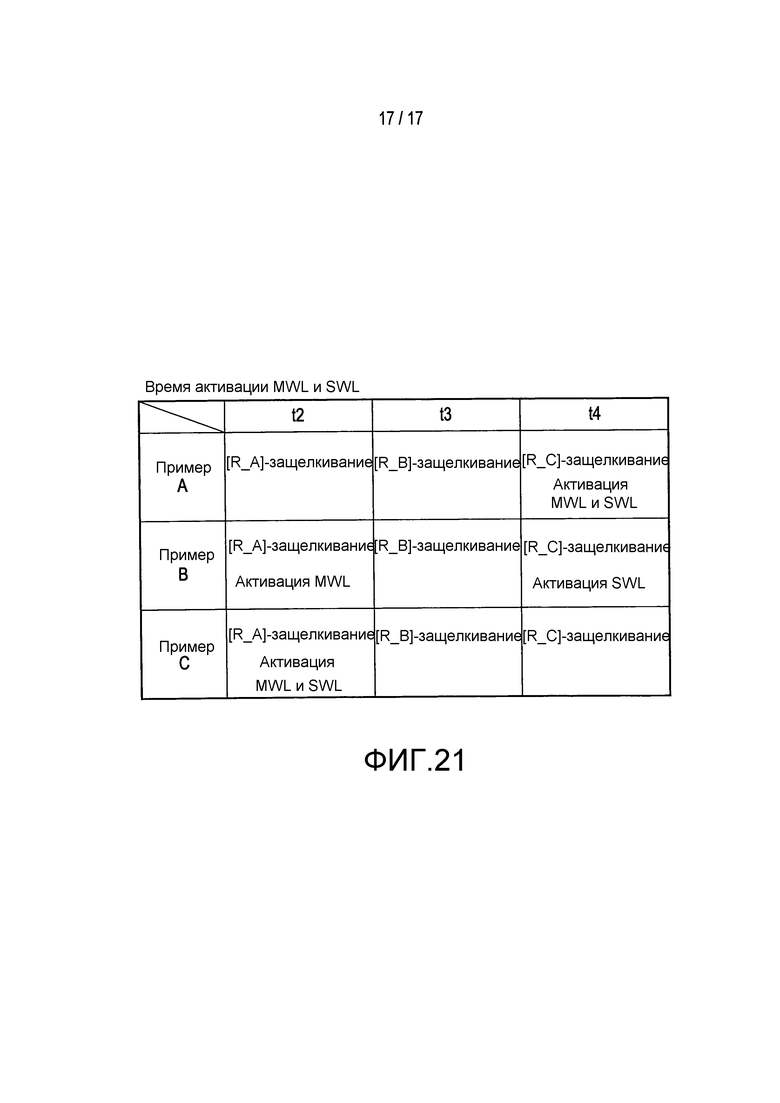

Фиг. 21 является видом, показывающим варьирование времен активации основных/дополнительных линий слова четвертого варианта осуществления.

Подробное описание изобретения

В общем, согласно одному варианту осуществления, энергонезависимое оперативное запоминающее устройство содержит: матрицу ячеек запоминающего устройства с банками, причем каждый банк включает в себя строки; первые линии слова, предоставленные в соответствии со строками; схему-защелку адресов, которая защелкивает сигнал первого адреса строки; декодер строк, который активирует одну из первых линий слова; и схему управления, которая выполнена с возможностью: выполнять первую операцию, которая активирует один из банков на основе сигнала адреса банка, когда загружается первая команда, и вторую операцию, которая защелкивает сигнал первого адреса строки в схеме-защелке адресов, и выполнять третью операцию, которая активирует одну из первых линий слова посредством декодера строк на основе сигнала второго адреса строки и сигнала первого адреса строки, защелкиваемых в схеме-защелке адресов, когда вторая команда загружается после первой команды.

Энергонезависимое оперативное запоминающее устройство

Фиг. 1 показывает энергонезависимое оперативное запоминающее устройство.

Энергонезависимое оперативное запоминающее устройство 10 включает в себя ядро 11 запоминающего устройства, периферийную схему 12 и интерфейс 13.

Ядро 11 запоминающего устройства включает в себя множество магниторезистивных элементов (ячеек запоминающего устройства) для сохранения данных. Периферийная схема 12 выполняет считывание/запись данных для ядра 11 запоминающего устройства.

Интерфейс 13 принимает управляющие сигналы CNT для считывания/записи, тактовый сигнал CK для управления таймингами (временами, временными распределениями) операций считывания/записи и сигнал CA[n:0] команды и адреса для определения внутренней операции для считывания/записи и обозначения адреса ячейки запоминающего устройства, к которой должен осуществляться доступ в ядре 11 запоминающего устройства.

Кроме того, интерфейс 13 выводит считываемые данные DOUT[m:0] и принимает записываемые данные DIN[m:0].

CA[n:0] означает (n+1)-битовые сигналы CA[n], CA[n-1], …, CA[0] команд и адресов. DOUT[m:0] означает (m+1)-битовые считываемые данные DOUT[m], DOUT[m-1], …, DOUT[0]. DIN[m:0] означает (m+1)-битовые записываемые данные DIN[m], DIN[m-1], …, DIN[0].

Следует отметить, что n и m являются натуральными числами.

Фиг. 2 показывает спецификации интерфейса.

Интерфейс 13 энергонезависимого оперативного запоминающего устройства 10 имеет две системы тракта передачи данных, чтобы, например, выводить считываемые данные DOUT[m:0] и принимать записываемые данные DIN[m:0] параллельно, за счет этого повышая пропускную способность.

Тем не менее, также можно использовать идентичную систему тракта передачи данных в качестве входного тракта и выходного тракта.

Согласно управляющему сигналу CNT и сигналу CA[n:0] команды и адреса, в настоящем варианте осуществления, управляющий сигнал CNT содержит только сигнал CKE разрешения подачи тактового сигнала и сигнал BC выбора кристалла, и декодирование команды считывания, записи и т.д., на основе кодированной команды с использованием CA[n:0].

Следует отметить, что CK представляет собой тактовый сигнал для синхронного выполнения ввода/вывода данных и ввода команд, описанных выше.

Фиг. 3 показывает ядро запоминающего устройства и периферийную схему.

Ядро 11 запоминающего устройства включает в себя матрицу 21 ячеек запоминающего устройства, декодер 22 строк и декодер 23 столбцов. Матрица 21 ячеек запоминающего устройства включает в себя k (k является натуральным числом в 2 или более) банков B0, B1, …, Bk. Поскольку банки B0, B1, …, Bk могут независимо активироваться, потребление мощности может уменьшаться, например, посредством активации только требуемых банков в ходе считывания/записи.

Декодер 22 строк декодирует, например, x-битовый сигнал BA[x:0] адреса банка для выбора одного из k банков B0, B1, …, Bk и y-битовый сигнал AR[y:0] адреса строки для выбора одной строки в выбранном банке. Сигнал AR[y:0] адреса строки также может включать в себя, например, старший бит, средний бит и младший бит.

Декодер 23 столбцов декодирует, например, z-битовый сигнал AC[z:0] адреса столбца для выбора одного столбца в матрице 21 ячеек запоминающего устройства.

Периферийная схема 12 включает в себя схему-защелку 24 команд и адресов, схему-защелку 25 данных, схему 26 управления, схему-защелку 27 адресов и формирователь 28 тактовых сигналов.

Схема-защелка 24 команд и адресов принимает сигнал CA[n:0] команды и адреса из хоста 14. Иными словами, схема-защелка 24 команд и адресов временно запоминает сигнал CMD команды для определения внутренней операции для считывания/записи и сигнал ADD адреса для обозначения адреса в ядре 11 запоминающего устройства.

Сигнал CMD команды передается в схему 25 управления. Схема 25 управления управляет внутренней операцией на основе управляющих сигналов CNT и сигнала CMD команды из хоста 14.

Из сигнала ADD адреса, сигнал BA[x:0] адреса банка передается в декодер 22 строк, сигнал AR[y:0] адреса строки передается в схему-защелку 26 адресов, а сигнал AC[z:0] адреса столбца передается в декодер 23 столбцов.

В этом варианте осуществления, как описано ниже, когда вводится команда активации для активации линии слова (строки) в выбранном банке, часть сигнала AR[y:0] адреса строки вводится в схему-защелку 26 адресов. Кроме того, когда вводится предварительно определенная команда, предшествующая команде активации, другая часть сигнала AR[y:0] адреса строки вводится в схему-защелку 26 адресов заранее.

Как описано выше, часть сигнала AR[y:0] адреса строки вводится заранее до того, как вводится команда активации. Следовательно, даже когда, например, число битов сигнала AR[y:0] адреса строки для выбора линии слова (строки) в матрице 21 ячеек запоминающего устройства увеличивается, энергонезависимое оперативное запоминающее устройство может быть включено в систему без увеличения числа штырьковых выводов и снижения скорости работы, т.е. без изменения спецификаций.

Следует отметить, что предварительно определенная команда представляет собой, например, команду предварительного заряда банка для предварительного заряда выбранного банка. Когда вводится команда предварительного заряда банка, декодер 22 строк принимает сигнал BA[x:0] адреса банка и начинает предварительный заряд выбранного банка.

Команда активации представляет собой команду для выполнения операции активации для активации одной (выбранной линии слова) из множества линий слова в выбранном банке. Команда предварительного заряда банка представляет собой команду для выполнения операции предварительного заряда банка для задания одного (выбранного банка) из множества банков в начальном состоянии (состоянии предварительного заряда) для считывания/записи.

Схема-защелка 27 данных временно запоминает считываемые данные DOUT[m:0] или записываемые данные DIN[m:0]. Считываемые данные DOUT[m:0] считываются из ячейки запоминающего устройства в выбранном банке через декодер 23 столбцов. Записываемые данные DIN[m:0] записываются в ячейку запоминающего устройства в выбранном банке через декодер 23 столбцов.

Формирователь 28 тактовых сигналов формирует внутренний тактовый сигнал CLK на основе тактового сигнала CK из хоста 14. Внутренний тактовый сигнал CLK вводится в схему-защелку 24 команд и адресов, схему 25 управления, схему-защелку 26 адресов и схему-защелку 27 данных и управляет таймингами работы этих схем.

Фиг. 4 показывает пример матрицы ячеек запоминающего устройства.

В этом примере, поясняется компоновка одного банка Bk в матрице ячеек запоминающего устройства. Кроме того, магнитное оперативное запоминающее устройство приспосабливается в качестве примера энергонезависимого оперативного запоминающего устройства.

Множество ячеек MC запоминающего устройства размещаются в форме матрицы вдоль направлений строк и столбцов. Множество линий слова WL0-WLi-1 формируются в соответствии "один-к-одному" с множеством строк и идут в направлении строк в банке Bk. Множество битовых линий BL0-BLj-1 идут в направлении столбцов в банке Bk. Следует отметить, что i является натуральным числом в 2 или более, и j является четным числом в 2 или более.

Одна ячейка MC запоминающего устройства включает в себя один магниторезистивный элемент MTJ и один транзистор Tr выбора (FET: полевой транзистор), подключенные последовательно. Одна ячейка MC запоминающего устройства включает в себя один узел управления и два узла тока.

Узел управления подключается к одной линии слова WLi-1. Один из двух узлов тока подключается к битовой линии BLj-2 с четным номером, а другой подключается к битовой линии BLj-1 с нечетным номером.

Магниторезистивный элемент MTJ включает в себя первый ферромагнитный слой (слой намагничивания со штырьковыми выводами), в котором направление намагничивания является неизменяемым, второй ферромагнитный слой (свободный слой намагничивания), в котором направление намагничивания является переменным, и изолирующий слой (туннельный барьерный слой), сформированный между первым и вторым ферромагнитными слоями.

Магниторезистивный элемент MTJ представляет собой, например, элемент с переносом спинового крутящего момента, допускающий изменение направления намагничивания во втором ферромагнитном слое посредством тока переноса спинового крутящего момента. Иными словами, ток переноса спинового крутящего момента (двунаправленный электрический ток), протекающий между битовой линией BLj-2 с четным номером и битовой линией BLj-1 с нечетным номером, определяет направление намагничивания во втором ферромагнитном слое магниторезистивного элемента MTJ.

Следует отметить, что магниторезистивный элемент MTJ может представлять собой либо элемент с перпендикулярным намагничиванием, в котором направление намагничивания остаточного намагничивания является перпендикулярным поверхности пленки (поверхности раздела между первым или вторым ферромагнитным слоем и изолирующим слоем), либо элемент с намагничиванием в плоскости, в котором это направление намагничивания является параллельным поверхности пленки.

Варианты осуществления

Ниже поясняются варианты осуществления с использованием энергонезависимого оперативного запоминающего устройства, показанного на фиг. 1, 2 и 3.

Иными словами, предварительные условия заключаются в том, что матрица ячеек запоминающего устройства включает в себя множество банков, каждый банк включает в себя множество строк, и множество линий слова формируются в соответствии "один-к-одному" с множеством строк.

Первый и второй варианты осуществления

Фиг. 5 показывает временную диаграмму согласно первому варианту осуществления.

Внутренний тактовый сигнал CLK формируется, например, посредством формирователя 28 тактовых сигналов, показанного на фиг. 3. В первом тактовом цикле C1 (одном тактовом цикле) внутреннего тактового сигнала CLK вводится (загружается) команда PCG предварительного заряда банка (первая команда).

Когда команда PCG предварительного заряда банка согласно активному банку вводится в состоянии активации активного банка из числа множества банков, операция предварительного заряда банка (первая операция) выполняется на основе сигнала адреса банка, а также выполняет операцию предварительной активации (вторую операцию) для защелкивания сигналов R_A и R_B первых адресов строк в схеме-защелке 26 адресов, показанной на фиг. 3.

Иными словами, первый вариант осуществления имеет такую особенность, что когда вводится команда PCG предварительного заряда банка, операция, в которой предварительно загружаются сигналы R_A и R_B первых адресов строк, добавляется (область X) в качестве новой операции предварительной активации, отделенной от операции предварительного заряда банка.

Операция предварительного заряда банка выполняется в качестве внутренней операции энергонезависимого оперативного запоминающего устройства посредством использования, например, двух тактовых циклов, и операция предварительной активации выполняется в качестве внутренней операции, отделенной от внутренней операции для операции предварительного заряда банка энергонезависимого оперативного запоминающего устройства посредством использования, например, одного тактового цикла.

Во втором тактовом цикле C2 (одном тактовом цикле) внутреннего тактового сигнала CLK вводится (загружается) команда Act активации (вторая команда).

Когда вводится команда Act активации, схема 25 управления, показанная на фиг. 3, загружает сигналы R_C и R_D вторых адресов строк, и на основе сигналов R_C и R_D вторых адресов строк и сигналов R_A и R_B первых адресов строк, защелкиваемых в схеме-защелке 26 адресов, показанной на фиг. 3, выполняет операцию активации (третью операцию) для активации одной из множества линий слова в матрице 21 ячеек запоминающего устройства посредством декодера 22 строк, показанного на фиг. 3.

Следует отметить, что схема-защелка 26 адресов, показанная на фиг. 3, поддерживает защелкивание сигналов R_A и R_B первых адресов строк до тех пор, пока не будет введена команда Act активации.

Операция активации выполняется в качестве внутренней операции энергонезависимого оперативного запоминающего устройства посредством использования, например, четырех тактовых циклов.

Кроме того, команда R/W считывания/записи вводится (загружается) в третьем тактовом цикле C3 (одном тактовом цикле) внутреннего тактового сигнала CLK.

Когда вводится команда R/W считывания/записи, схема 25 управления, показанная на фиг. 3, выполняет операцию приема сигналов C_A и C_B адресов столбцов.

В первом варианте осуществления, как описано выше, ввод сигналов R_A и R_B адресов строк доступен заранее во время ввода сигналов R_A и R_B адресов строк на основе команды PCG предварительного заряда банка, отделенного от времени ввода сигналов R_C и R_D адресов строк на основе команды Act активации.

Следовательно, даже когда, например, число битов сигналов полных адресов строк для выбора множества линий слова (множества строк) в матрице 21 ячеек запоминающего устройства, показанной на фиг. 3, увеличивается, энергонезависимое оперативное запоминающее устройство может быть включено в систему без увеличения числа штырьковых выводов и снижения скорости работы в зависимости от добавления ввода сигнала адреса на основе команды Act активации, т.е. без существенного изменения спецификаций.

Фиг. 6 показывает временную диаграмму согласно второму варианту осуществления.

По сравнению с первым вариантом осуществления, второй вариант осуществления имеет такую особенность, что команды и сигналы адресов загружаются на основе переднего фронта (↑) и заднего фронта (↓) одного тактового цикла внутреннего тактового сигнала CLK.

Внутренний тактовый сигнал CLK формируется, например, посредством формирователя 28 тактовых сигналов, показанного на фиг. 3. На переднем фронте (время t1) первого тактового цикла C1 (одного тактового цикла) внутреннего тактового сигнала CLK вводится (загружается) команда PCG предварительного заряда банка (первая команда).

Кроме того, часть R_A сигнала первого адреса строки вводится (загружается) на переднем фронте (время t1) первого тактового цикла C1 (одного тактового цикла), и другая часть R_B сигнала первого адреса строки вводится (загружается) на заднем фронте (время t2) первого тактового цикла C1 (одного тактового цикла).

Когда вводится команда PCG предварительного заряда банка в активном банке в состоянии активации активного банка из числа множества банков, операция предварительного заряда банка (первая операция) выполняется на основе сигнала адреса банка, а также выполняет операцию предварительной активации (вторую операцию) защелкивания сигналов R_A и R_B первых адресов строк в схеме-защелке 26 адресов, показанной на фиг. 3.

Иными словами, второй вариант осуществления также имеет такую особенность, что когда вводится команда PCG предварительного заряда банка, операция, в которой предварительно загружаются сигналы R_A и R_B первых адресов строк (область X), добавляется в качестве новой операции предварительной активации, отделенной от операции предварительного заряда банка.

Операция предварительного заряда банка выполняется в качестве внутренней операции энергонезависимого оперативного запоминающего устройства посредством использования, например, двух тактовых циклов, и операция предварительной активации выполняется в качестве внутренней операции, отделенной от внутренней операции для операции предварительного заряда банка энергонезависимого оперативного запоминающего устройства посредством использования, например, одного тактового цикла.

На переднем фронте (время t3) второго тактового цикла C2 (одного тактового цикла) внутреннего тактового сигнала CLK вводится (загружается) команда Act активации (вторая команда).

Кроме того, часть R_C сигнала второго адреса строки вводится (загружается) на переднем фронте (время t3) второго тактового цикла C2 (одного тактового цикла), и другая часть R_D сигнала второго адреса строки вводится (загружается) на заднем фронте (время t4) второго тактового цикла C2 (одного тактового цикла).

Когда вводится команда Act активации, схема 25 управления, показанная на фиг. 3, выполняет операцию активации (третью операцию) для активации одной из множества линий слова в матрице 21 ячеек запоминающего устройства посредством декодера 22 строк, показанного на фиг. 3, на основе сигналов R_C и R_D вторых адресов строк и сигналов R_A и R_B первых адресов строк, защелкиваемых в схеме-защелке 26 адресов, показанной на фиг. 3.

Следует отметить, что схема-защелка 26 адресов, показанная на фиг. 3, поддерживает защелкивание сигналов R_A и R_B первых адресов строк до тех пор, пока не будет введена команда Act активации.

Операция активации выполняется в качестве внутренней операции энергонезависимого оперативного запоминающего устройства посредством использования, например, четырех тактовых циклов.

Кроме того, команда R/W считывания/записи вводится (загружается) на переднем фронте (время t5) третьего тактового цикла C3 (одного тактового цикла) внутреннего тактового сигнала CLK.

Помимо этого, часть C_A сигнала адреса столбца вводится (загружается) на переднем фронте (время t5) третьего тактового цикла C3 (одного тактового цикла), и другая часть C_B сигнала адреса столбца вводится (загружается) на заднем фронте (время t6) третьего тактового цикла C3 (одного тактового цикла).

Когда вводится команда R/W считывания/записи, схема 25 управления, показанная на фиг. 3, выполняет операцию считывания/записи посредством выбора одной из множества пар битовых линий в матрице 21 ячеек запоминающего устройства посредством декодера 23 столбцов, показанного на фиг. 3, на основе сигналов C_A и C_B адресов столбцов.

Как описано выше, ввод адресов строк доступен заранее во время ввода сигналов R_A и R_B адресов строк на основе команды PCG предварительного заряда банка, отделенного от времени ввода сигнала R_C и R_D адреса строки на основе команды активации.

Следовательно, даже когда, например, число битов сигналов полных адресов строк для выбора множества линий слова (множества строк) в матрице 21 ячеек запоминающего устройства, показанной на фиг. 3, увеличивается, энергонезависимое оперативное запоминающее устройство может быть включено в систему без увеличения числа штырьковых выводов и снижения скорости работы в зависимости от добавления ввода сигнала адреса на основе команды активации, т.е. без существенного изменения спецификаций.

Фиг. 7, 8, 9, 10, 11 и 12 показывают примеры загрузки команд и адресов в первом и втором вариантах осуществления.

На этих чертежах, CLK обозначает внутренний тактовый сигнал, сформированный на основе тактового сигнала CK, вводимого из контактного вывода (штырькового вывода) тактового сигнала. Кроме того, CA0-CA9 обозначают сигналы команд и адресов, вводимые из контактных выводов (штырьковых выводов) команд и адресов.

В примерах, число контактных выводов CA0-CA9 команд и адресов равно 10. Тем не менее, число контактных выводов равно 10 для того, чтобы обеспечивать безусловную понятность пояснения, и, следовательно, не ограничено этим значением.

Кроме того, в нижеприведенном пояснении предполагается, что число банков в матрице ячеек запоминающего устройства равно восьми, а число битов сигналов BA0, BA1 и BA2 адресов банков для выбора этих банков равно трем. Тем не менее, эти числа также задаются таким образом, чтобы обеспечивать простоту и понятность пояснения, и, следовательно, не ограничены этими значениями.

Кроме того, в примерах, предполагается, что сигнал полного адреса строки имеет 18 битов от R0 до R17, и сигнал первого адреса строки (часть сигнала полного адреса строки), который вводится, когда вводится команда PCG предварительного заряда банка, имеет старшие биты R14-R17.

Тем не менее, эти числа также являются примерами, и для этого варианта осуществления важным является то, что часть сигнала полного адреса строки вводится заранее, когда вводится команда PCG предварительного заряда банка.

Фиг. 7 и 8 являются примерами, в которых назначение двух видов адреса банка доступно, и назначение банка в качестве цели операции предварительного заряда и банка в качестве цели операции предварительной активации доступно отдельно в команде предварительного заряда банка.

В "случае 1a" по фиг. 7, команда (H, H, L, H) предварительного заряда банка загружается в энергонезависимое оперативное запоминающее устройство из контактных выводов CA0-CA3 команд и адресов на основе переднего фронта (↑) внутреннего тактового сигнала CLK.

Кроме того, флаг AB для определения того, следует или нет выполнять операцию предварительного заряда всех банков, загружается в энергонезависимое оперативное запоминающее устройство из контактного вывода CA4 команд и адресов на основе переднего фронта (↑) внутреннего тактового сигнала CLK. Операция предварительного заряда всех банков представляет собой операцию возвращения всех активных банков в банки в состоянии ожидания.

Помимо этого, сигналы BA0, BA1 и BA2 адресов банков в качестве целей операции предварительного заряда загружаются в энергонезависимое оперативное запоминающее устройство из контактных выводов CA7-CA9 команд и адресов на основе переднего фронта (↑) внутреннего тактового сигнала CLK.

После этого, сигнал первого адреса строки (старшие биты R14-R17 сигнала полного адреса строки) загружается в энергонезависимое оперативное запоминающее устройство из контактных выводов CA3-CA6 команд и адресов на основе заднего фронта (↓) внутреннего тактового сигнала CLK (операция предварительной активации).

Кроме того, сигналы BA0, BA1 и BA2 адресов банков в качестве целей операции предварительной активации загружаются в энергонезависимое оперативное запоминающее устройство из контактных выводов CA7-CA9 команд и адресов на основе заднего фронта (↓) внутреннего тактового сигнала CLK.

Следует отметить, что на фиг. 7, X означает, что контактный вывод не используется для того, чтобы загружать сигнал команды или адреса на переднем фронте (↑) или на заднем фронте (↓) внутреннего тактового сигнала CLK.

"Случай 1b" на фиг. 8 является модификацией "случая 1a" на фиг. 7.

Этот пример, показанный на фиг. 8, отличается от примера, показанного на фиг. 7, тем, что сигнал первого адреса строки (старшие биты R14-R17 сигнала полного адреса строки) загружается в энергонезависимое оперативное запоминающее устройство на основе переднего фронта (↑) и заднего фронта (↓) внутреннего тактового сигнала CLK.

Иными словами, в этом примере, старшие биты R14 и R15 сигнала полного адреса строки загружаются в энергонезависимое оперативное запоминающее устройство из контактных выводов CA5 и CA6 команд и адресов на основе переднего фронта (↑) внутреннего тактового сигнала CLK, и старшие биты R16 и R17 сигнала полного адреса строки загружаются в энергонезависимое оперативное запоминающее устройство из контактных выводов CA5 и CA6 команд и адресов на основе заднего фронта (↓) внутреннего тактового сигнала CLK (операция предварительной активации).

Остальное является идентичным примеру, показанному на фиг. 7, так что повторяющееся пояснение пропускается.

Фиг. 9 и 10 являются примерами, в которых назначение адреса банка представляет собой только один вид, и банк, являющийся целью операции предварительного заряда, и банк, являющийся целью операции предварительной активации, являются идентичными.

"Случай 2a" на фиг. 9 отличается от "случая 1a" на фиг. 7 тем, что сигналы BA0, BA1 и BA2 адресов банков загружаются в энергонезависимое оперативное запоминающее устройство на основе только переднего фронта (↑) внутреннего тактового сигнала CLK, поскольку операция предварительного заряда и операция активации банка имеют банк, идентичный банку цели.

Иными словами, в этом примере, сигналы BA0, BA1 и BA2 адресов банков загружаются в энергонезависимое оперативное запоминающее устройство из контактных выводов CA7-CA9 команд и адресов на основе переднего фронта (↑) внутреннего тактового сигнала CLK, и сигнал адреса банка, который вводится на основе заднего фронта (↓) внутреннего тактового сигнала CLK, не существует.

Остальное является идентичным примеру, показанному на фиг. 7, так что повторяющееся пояснение пропускается.

"Случай 2b" на фиг. 10 отличается от "случая 1b" на фиг. 8 тем, что сигналы BA0, BA1 и BA2 адресов банков загружаются в энергонезависимое оперативное запоминающее устройство на основе только переднего фронта (↑) внутреннего тактового сигнала CLK, поскольку операция предварительного заряда и операция активации банка имеют банк, идентичный банку цели.

Иными словами, в этом примере, сигналы BA0, BA1 и BA2 адресов банков загружаются в энергонезависимое оперативное запоминающее устройство из контактных выводов CA7-CA9 команд и адресов на основе переднего фронта (↑) внутреннего тактового сигнала CLK и не вводятся на основе заднего фронта (↓) внутреннего тактового сигнала CLK.

Остальное является идентичным примеру, показанному на фиг. 8, так что повторяющееся пояснение пропускается.

В случае фиг. 7-10, операция предварительного заряда и операция предварительной активации банка выполняются только посредством команды предварительного заряда банка. Напротив, на фиг. 11 и 12, команда предварительной активации задается заново, операция предварительного заряда банка выполняется только на основе команды предварительного заряда банка, операция предварительной активации выполняется только на основе команды предварительной активации, и команда предварительного заряда банка и команда предварительной активации вводятся непрерывно посредством переднего фронта и заднего фронта в идентичном тактовом сигнале.

Ниже поясняются пример для реализации внутренней операции, идентичной внутренней операции для "случая 1a" на фиг. 7, и пример для реализации внутренней операции, идентичной внутренней операции для "случая 1b" на фиг. 8, посредством непрерывного ввода команды предварительного заряда банка и команды предварительной активации.

Фиг. 11 является примером для реализации внутренней операции, идентичной внутренней операции для "случая 1a" на фиг. 7.

В этом примере, может выбираться "случай 3a-1", "случай 3a-2" или "случай 3a-3".

Например, "случай 3a-1" основан на "случае 1a", и команда (L, H) предварительной активации загружается в энергонезависимое оперативное запоминающее устройство из контактных выводов CA0 и CA1 команд и адресов на основе заднего фронта (↓) внутреннего тактового сигнала CLK, в дополнение к команде (H, H, L, H) предварительного заряда банка.

В "случае 3a-2", выполняется только операция предварительного заряда банка в "случае 3a-1". В этом случае, сигнал команды и адреса загружается на основе только переднего фронта (↑) внутреннего тактового сигнала CLK и не загружается на заднем фронте (↓) внутреннего тактового сигнала CLK.

В "случае 3a-3", выполняется только операция предварительной активации в "случае 3a-1". В этом случае, сигнал команды и адреса загружается на основе только заднего фронта (↓) внутреннего тактового сигнала CLK и не загружается на переднем фронте (↑) внутреннего тактового сигнала CLK.

Фиг. 12 является примером для реализации внутренней операции, идентичной внутренней операции для "случая 1b" на фиг. 8.

В этом примере, может выбираться "случай 3b-1", "случай 3b-2" или "случай 3b-3".

Например, "случай 3b-1" основан на "случае 1b", и команда (L, H) предварительной активации загружается в энергонезависимое оперативное запоминающее устройство из контактных выводов CA0 и CA1 команд и адресов на основе заднего фронта (↓) внутреннего тактового сигнала CLK, в дополнение к команде (H, H, L, H) предварительного заряда банка.

В "случае 3b-2", выполняется только операция предварительного заряда банка в "случае 3b-1". В этом случае, сигнал команды и адреса загружается на основе только переднего фронта (↑) внутреннего тактового сигнала CLK и не загружается на заднем фронте (↓) внутреннего тактового сигнала CLK.

В "случае 3b-3", выполняется только операция предварительной активации в "случае 3b-1". В этом случае, сигнал команды и адреса загружается на основе только заднего фронта (↓) внутреннего тактового сигнала CLK и не загружается на переднем фронте (↑) внутреннего тактового сигнала CLK.

Третий и четвертый варианты осуществления

Фиг. 13 показывает временную диаграмму согласно третьему варианту осуществления.

Внутренний тактовый сигнал CLK формируется, например, посредством формирователя 28 тактовых сигналов, показанного на фиг. 3. Считывание/запись с помощью команды R/W&AP автоматического предварительного заряда (первой команды) вводится (загружается) в первом тактовом цикле C1 (одном тактовом цикле) внутреннего тактового сигнала CLK.

Когда вводится считывание/запись с помощью команды R/W&AP автоматического предварительного заряда в активный банк в состоянии активации активного банка из числа множества банков, операция предварительного заряда банка (первая операция) выполняется на основе сигнала адреса банка, а также выполняет операцию предварительной активации (вторую операцию) защелкивания сигнала R_A первого адреса строки в схеме-защелке 26 адресов, показанной на фиг. 3.

Иными словами, третий вариант осуществления имеет такую особенность, что когда вводится считывание/запись с помощью команды R/W&AP автоматического предварительного заряда, операция, в которой предварительно загружается сигнал R_A первого адреса строки (область X), в качестве новой операции предварительной активации, отделенной от операции предварительного заряда банка.

Кроме того, схема 25 управления, показанная на фиг. 3, выполняет операцию приема сигналов C_A и C_B адресов столбцов, когда вводится считывание/запись с помощью команды R/W&AP автоматического предварительного заряда.

Операция предварительного заряда банка выполняется в качестве внутренней операции энергонезависимого оперативного запоминающего устройства посредством использования, например, двух тактовых циклов, и операция предварительной активации выполняется в качестве внутренней операции, отделенной от внутренней операции для операции предварительного заряда банка энергонезависимого оперативного запоминающего устройства посредством использования, например, одного тактового цикла.

Помимо этого, команда Act активации (вторая команда) вводится (загружается) во втором тактовом цикле C2 (одном тактовом цикле) внутреннего тактового сигнала CLK.

Когда вводится команда Act активации, схема 25 управления, показанная на фиг. 3, загружает сигналы R_B и R_C вторых адресов строк, и на основе сигналов R_B и R_C вторых адресов строк и сигнала R_A первого адреса строки, защелкиваемых в схеме-защелке 26 адресов, показанной на фиг. 3, выполняет операцию активации (третью операцию) для активации одной из множества линий слова в матрице 21 ячеек запоминающего устройства посредством декодера 22 строк, показанного на фиг. 3.

Следует отметить, что схема-защелка 26 адресов, показанная на фиг. 3, поддерживает защелкивание сигнала R_A первого адреса строки до тех пор, пока не будет введена команда Act активации.

Операция активации выполняется в качестве внутренней операции энергонезависимого оперативного запоминающего устройства посредством использования, например, четырех тактовых циклов.

В третьем варианте осуществления, как описано выше, ввод сигнала R_A адреса строки доступен заранее во время ввода сигнала R_A адреса строки на основе команды предварительного заряда банка, отделенного от времени ввода сигнала R_B и R_C адреса строки на основе команды активации.

Следовательно, даже когда, например, число битов сигналов R_A, R_B и R_C полных адресов строк для выбора множества линий слова (множества строк) в матрице 21 ячеек запоминающего устройства, показанной на фиг. 3, увеличивается, энергонезависимое оперативное запоминающее устройство может быть включено в систему без увеличения числа штырьковых выводов и снижения скорости работы в зависимости от добавления ввода сигнала адреса, т.е. без существенного изменения спецификаций.

Фиг. 14 показывает временную диаграмму согласно четвертому варианту осуществления.

По сравнению с третьим вариантом осуществления, четвертый вариант осуществления имеет такую особенность, что команды и сигналы адресов загружаются на основе переднего фронта (↑) и заднего фронта (↓) одного тактового цикла внутреннего тактового сигнала CLK.

Внутренний тактовый сигнал CLK формируется, например, посредством формирователя 28 тактовых сигналов, показанного на фиг. 3. Считывание/запись с помощью команды R/W&AP автоматического предварительного заряда (первой команды) вводится (загружается) на переднем фронте (время t1) первого тактового цикла C1 (одного тактового цикла) внутреннего тактового сигнала CLK.

Кроме того, часть C_A сигнала адреса столбца вводится (загружается) на переднем фронте (время t1) первого тактового цикла C1 (одного тактового цикла), и другая часть C_B сигнала адреса столбца вводится (загружается) на заднем фронте (время t2) первого тактового цикла C1 (одного тактового цикла).

Помимо этого, сигнал R_A первого адреса строки вводится (загружается) на заднем фронте (время t2) первого тактового цикла C1 (одного тактового цикла).

Когда вводится считывание/запись с помощью команды R/W&AP автоматического предварительного заряда в активный банк в состоянии активации активного банка из числа множества банков, операция предварительного заряда банка (первая операция) выполняется на основе сигнала адреса банка, а также выполняет операцию предварительной активации (вторую операцию) защелкивания сигнала R_A первого адреса строки в схеме-защелке 26 адресов, показанной на фиг. 3.

Иными словами, четвертый вариант осуществления также имеет такую особенность, что когда вводится считывание/запись с помощью команды R/W&AP автоматического предварительного заряда, операция, в которой предварительно загружается сигнал R_A первого адреса строки (область X), в качестве новой операции предварительной активации добавляется отделенной от операции предварительного заряда банка.

Операция предварительного заряда банка выполняется в качестве внутренней операции энергонезависимого оперативного запоминающего устройства посредством использования, например, двух тактовых циклов, и операция предварительной активации выполняется в качестве внутренней операции, отделенной от внутренней операции для операции предварительного заряда банка энергонезависимого оперативного запоминающего устройства посредством использования, например, одного тактового цикла.

Команда Act активации (вторая команда) вводится (загружается) на переднем фронте (время t3) второго тактового цикла C2 (одного тактового цикла) внутреннего тактового сигнала CLK.

Кроме того, часть R_B сигнала второго адреса строки вводится (загружается) на переднем фронте (время t3) второго тактового цикла C2 (одного тактового цикла), и другая часть R_C сигнала второго адреса строки вводится (загружается) на заднем фронте (время t4) второго тактового цикла C2 (одного тактового цикла).

Когда вводится команда Act активации, схема 25 управления, показанная на фиг. 3, выполняет операцию активации (третью операцию) для активации одной из множества линий слова в матрице 21 ячеек запоминающего устройства посредством декодера 22 строк, показанного на фиг. 3, на основе сигналов R_B и R_C вторых адресов строк и сигнала R_A первого адреса строки, защелкиваемых в схеме-защелке 26 адресов, показанной на фиг. 3.

Следует отметить, что схема-защелка 26 адресов, показанная на фиг. 3, поддерживает защелкивание сигнала R_A первого адреса строки до тех пор, пока не будет введена команда Act активации.

Операция активации выполняется в качестве внутренней операции энергонезависимого оперативного запоминающего устройства посредством использования, например, четырех тактовых циклов.

Как описано выше, ввод сигнала адреса строки доступен заранее во время ввода сигнала R_A адреса строки на основе команды PCG предварительного заряда банка, отделенного от времени ввода сигнала R_B и R_C адреса строки на основе команды Act активации.

Следовательно, даже когда, например, число битов сигналов R_A, R_B и R_C полных адресов строк для выбора множества линий слова (множества строк) в матрице 21 ячеек запоминающего устройства, показанной на фиг. 3, увеличивается, энергонезависимое оперативное запоминающее устройство может быть включено в систему без увеличения числа штырьковых выводов и снижения скорости работы в зависимости от добавления ввода сигнала адреса на основе команды Act активации, т.е. без существенного изменения спецификаций.

Фиг. 15, 16 и 17 показывают примеры загрузки команд и адресов в третьем и четвертом вариантах осуществления.

На этих чертежах, CLK обозначает внутренний тактовый сигнал, сформированный на основе тактового сигнала CK, вводимого из контактного вывода (штырькового вывода) тактового сигнала. Кроме того, CA0-CA9 обозначают сигналы команд и адресов, вводимые из контактных выводов (штырьковых выводов) команд и адресов.

В примерах, число контактных выводов CA0-CA9 команд и адресов равно 10. Тем не менее, число контактных выводов равно 10 для того, чтобы обеспечивать безусловную понятность пояснения, и, следовательно, не ограничено этим значением.

Кроме того, в нижеприведенном пояснении предполагается, что число банков в матрице ячеек запоминающего устройства равно восьми, а число битов сигналов BA0, BA1 и BA2 адресов банков для выбора этих банков равно трем. Тем не менее, эти числа также задаются таким образом, чтобы обеспечивать простоту и понятность пояснения, и, следовательно, не ограничены этими значениями.

Кроме того, в примерах, предполагается, что сигнал полного адреса строки имеет 18 битов от R0 до R17, и сигнал первого адреса строки (часть сигнала полного адреса строки), который вводится, когда вводится считывание/запись с помощью команды R/W&AP автоматического предварительного заряда, имеет старшие биты R14-R17.

Тем не менее, эти числа также являются примерами, и для этого варианта осуществления важным является то, что часть сигнала полного адреса строки вводится заранее, когда вводится команда PCG предварительного заряда банка.

"Случай 4" на фиг. 15 является примером того, что выделение адреса банка представляет собой только один вид, и банк, являющийся целью предварительного заряда, и банк, являющийся целью операции предварительной активации, являются идентичными.

Как показано на фиг. 15, считывание/запись с помощью команды автоматического предварительного заряда загружается в энергонезависимое оперативное запоминающее устройство из контактных выводов CA0-CA2 (H, L, H/L) команд и адресов на основе переднего фронта (↑) внутреннего тактового сигнала CLK, а также загружается в энергонезависимое оперативное запоминающее устройство из контактного вывода CA0 (H(AP)) команд и адресов на основе заднего фронта (↓) внутреннего тактового сигнала CLK.

Кроме того, сигналы C1 и C2 адресов столбцов загружаются в энергонезависимое оперативное запоминающее устройство из контактных выводов CA5 и CA6 команд и адресов на основе переднего фронта (↑) внутреннего тактового сигнала CLK, и сигналы C3-C7 адресов столбцов загружаются в энергонезависимое оперативное запоминающее устройство из контактных выводов CA1-CA5 команд и адресов на основе заднего фронта (↓) внутреннего тактового сигнала CLK.

В этом примере, сигнал полного адреса столбца имеет семь битов от C1 до C7.

Помимо этого, сигналы BA0, BA1 и BA2 адресов банков в качестве целей считывания/записи с помощью операции автоматического предварительного заряда загружаются в энергонезависимое оперативное запоминающее устройство из контактных выводов CA7-CA9 команд и адресов на основе переднего фронта (↑) внутреннего тактового сигнала CLK.

Кроме того, сигнал первого адреса строки (старшие биты R14-R17 сигнала полного адреса строки) загружается в энергонезависимое оперативное запоминающее устройство из контактных выводов CA6-CA9 команд и адресов на основе заднего фронта (↓) внутреннего тактового сигнала CLK (операция предварительной активации).

Следует отметить, что на фиг. 15, X означает, что контактный вывод не используется для того, чтобы загружать сигнал команды или адреса на переднем фронте (↑) или на заднем фронте (↓) внутреннего тактового сигнала CLK.

Фиг. 16 и 17 являются примерами, в которых доступны два вида выделения адреса банка, банк, являющийся целью операции предварительного заряда, и банк, являющийся целью операции предварительной активации, выделяются отдельно при считывании/записи с помощью команды автоматического предварительного заряда.

В "случае 5a" по фиг. 16, считывание/запись с помощью команды автоматического предварительного заряда загружается в энергонезависимое оперативное запоминающее устройство из контактных выводов CA0-CA2 (H, L, H/L) команд и адресов на основе переднего фронта (↑) внутреннего тактового сигнала CLK, а также загружается в энергонезависимое оперативное запоминающее устройство из контактного вывода CA0 (H(AP)) команд и адресов на основе заднего фронта (↓) внутреннего тактового сигнала CLK.

Кроме того, сигналы C1 и C2 адресов столбцов загружаются в энергонезависимое оперативное запоминающее устройство из контактных выводов CA5 и CA6 команд и адресов на основе переднего фронта (↑) внутреннего тактового сигнала CLK, и сигналы C3 и C4 адресов столбцов загружаются в энергонезависимое оперативное запоминающее устройство из контактных выводов CA1 и CA2 команд и адресов на основе заднего фронта (↓) внутреннего тактового сигнала CLK.

В этом примере, сигнал полного адреса столбца имеет четыре бита от C1 до C4.

Помимо этого, сигналы BA0, BA1 и BA2 адресов банков в качестве целей считывания/записи загружаются в энергонезависимое оперативное запоминающее устройство из контактных выводов CA7-CA9 команд и адресов на основе переднего фронта (↑) внутреннего тактового сигнала CLK.

Кроме того, сигналы BA0, BA1 и BA2 адресов банков в качестве целей операции автоматического предварительного заряда и операции предварительной активации загружаются в энергонезависимое оперативное запоминающее устройство из контактных выводов CA7-CA9 команд и адресов на основе заднего фронта (↓) внутреннего тактового сигнала CLK.

Кроме того, сигнал первого адреса строки (старшие биты R14-R17 сигнала полного адреса строки) загружается в энергонезависимое оперативное запоминающее устройство из контактных выводов CA3-CA6 команд и адресов на основе заднего фронта (↓) внутреннего тактового сигнала CLK (операция предварительной активации).

Следует отметить, что на фиг. 16, X означает, что контактный вывод не используется для того, чтобы загружать сигнал команды или адреса на переднем фронте (↑) или на заднем фронте (↓) внутреннего тактового сигнала CLK.

В "случае 5b" по фиг. 17, считывание/запись с помощью команды автоматического предварительного заряда загружается в энергонезависимое оперативное запоминающее устройство из контактных выводов CA0-CA2 (H, L, H/L) команд и адресов на основе переднего фронта (↑) внутреннего тактового сигнала CLK, а также загружается в энергонезависимое оперативное запоминающее устройство из контактного вывода CA0 (H(AP)) команд и адресов на основе заднего фронта (↓) внутреннего тактового сигнала CLK.

Кроме того, сигналы C1-C4 адресов столбцов загружаются в энергонезависимое оперативное запоминающее устройство из контактных выводов CA3-CA6 команд и адресов на основе переднего фронта (↑) внутреннего тактового сигнала CLK.

В этом примере, сигнал полного адреса столбца имеет четыре бита от C1 до C4.

Помимо этого, сигналы BA0, BA1 и BA2 адресов банков в качестве целей считывания/записи загружаются в энергонезависимое оперативное запоминающее устройство из контактных выводов CA7-CA9 команд и адресов на основе переднего фронта (↑) внутреннего тактового сигнала CLK.

Кроме того, сигналы BA0, BA1 и BA2 адресов банков в качестве целей операции автоматического предварительного заряда и операции предварительной активации загружаются в энергонезависимое оперативное запоминающее устройство из контактных выводов CA7-CA9 команд и адресов на основе заднего фронта (↓) внутреннего тактового сигнала CLK.

Кроме того, сигнал первого адреса строки (старшие биты R14-R17 сигнала полного адреса строки) загружается в энергонезависимое оперативное запоминающее устройство из контактных выводов CA3-CA6 команд и адресов на основе заднего фронта (↓) внутреннего тактового сигнала CLK (операция предварительной активации).

Следует отметить, что на фиг. 17, X означает, что контактный вывод не используется для того, чтобы загружать сигнал команды или адреса на переднем фронте (↑) или на заднем фронте (↓) внутреннего тактового сигнала CLK.

Характеристики "случая 5b" заключаются в том, что весь сигнал адреса для считывания/записи вводится на основе переднего фронта (↑) внутреннего тактового сигнала CLK. Как результат, команда может выполняться независимо от заднего фронта (↓) внутреннего тактового сигнала CLK, в отличие от "случая 5a".

Примеры вариантов применения

Первый-четвертый варианты осуществления становятся очень эффективными при комбинировании с иерархической матрицей ячеек запоминающего устройства на основе линий слова.

Это обусловлено тем, что иерархическая система линий слова включает в себя, при выборе одной линии слова (одной строки) матрицы ячеек запоминающего устройства, этапы выбора сначала одной основной линии слова, общей для множества дополнительных линий слова, посредством использования старшего адреса и выбора затем одной из множества дополнительных линий слова, включенных в выбранную основную линию слова, посредством использования среднего или младшего адреса.

Иными словами, скорость работы энергонезависимого оперативного запоминающего устройства может повышаться посредством комбинирования первого и второго вариантов осуществления с иерархической матрицей ячеек запоминающего устройства на основе линий слова.

Фиг. 18 показывает иерархическую матрицу ячеек запоминающего устройства на основе линий слова.

В этом примере, матрица ячеек запоминающего устройства включает в себя множество банков B0-B3. Каждый из множества банков B0-B3 включает в себя основные декодеры 30-0 - 30-3 строк, дополнительные декодеры 31-0 - 31-3 строк, субматрицы 32A и 32B и сенсорные считывающие усилители S/A.

Следует отметить, что число банков B0-B3 не ограничено четырьмя и должно составлять только два или более. Также следует отметить, что число субматриц 32A и 32B в одном банке Br (r составляет одно из 0-3) не ограничено двумя и также может составлять три или более.

Основные линии слова MWL0 - MWL3 идут в направлении строк из основных декодеров 30-0 - 30-3 строк. Множество дополнительных линий слова SWLr0 - SWLrt (t является натуральным числом) идут в направлении строк из дополнительных декодеров 31-0 - 31-3 строк.

Одна основная линия слова MWLr является общей для множества дополнительных линий слова SWLr0 - SWLrt. Например, основная линия слова MWL0 является общей для множества дополнительных линий слова SWL01-SWL0t.

Сенсорные считывающие усилители S/A размещаются на двух концах субматриц 32A и 32B в направлении столбцов. Пара битовых линий BL0 и BL1 идет в направлении столбцов из субматриц 32A и 32B.

Фиг. 19 показывает основной декодер строк и дополнительный декодер строк, показанные на фиг. 18.

Поскольку основные декодеры строк и дополнительные декодеры строк во множестве банков имеют идентичную компоновку, ниже поясняются основной декодер 30-0 строк и дополнительный декодер 31-0 строк, показанные на фиг. 18. Помимо этого, для того чтобы обеспечивать безусловную понятность нижеприведенного пояснения, предполагается, что число дополнительных линий слова SWL01-SWL03, общих для основной линии слова MWL0, равно четырем.

Основной декодер 30-0 строк управляет активацией основной линии слова MWL0 на основе старшего бита сигнала адреса строки.

Например, когда матрица ячеек запоминающего устройства комбинирована с первым-четвертым вариантами осуществления, описанными выше, логическая схема 33 “И-НЕ” в качестве основного декодера 30-0 строк принимает сигнал ϕ1 первого адреса строки (к примеру, R14-R17), который предварительно загружается, когда вводится команда PCG предварительного заряда банка или считывание/запись с помощью команды R/W&AP автоматического предварительного заряда.

В этом примере, основная линия слова MWL0 активируется, когда все биты сигнала ϕ1 первого адреса строки имеют H-уровень. Иными словами, основная линия слова MWL0 изменяется на L-уровень.

Как описано ниже, время активации основной линии слова MWL0 может представлять собой время, когда загружается команда PCG предварительного заряда банка или считывание/запись с помощью команды R/W&AP автоматического предварительного заряда, или время, когда загружается команда Act активации после этого.

Когда основная линия слова MWL имеет L-уровень (активирована), FET 35a (полевой транзистор) с каналом p-типа включается, и FET 35b с каналом n-типа выключается в модуле 34 формирователя сигналов управления. Иными словами, дополнительный декодер 31-0 строк также активируется в этот момент времени.

Дополнительный декодер 31-0 строк управляет активацией дополнительных линий слова SWL00-SWL03 в субматрицах 32A и 32B на основе среднего или младшего бита сигнала адреса строки.

Например, когда матрица ячеек запоминающего устройства комбинирована с вышеописанными первым-четвертым вариантами осуществления, логическая схема 36 "И" в качестве дополнительного декодера 31-0 строк принимает набор ϕ20-ϕ27 сигналов вторых адресов строк (к примеру, R0-R13), которые загружаются, когда вводится команда Act активации.

В этом примере, дополнительная линия слова SWL00 в субматрице 32A активируется, когда все биты набора ϕ20 сигналов вторых адресов строк имеют H-уровень.

Иными словами, в этот момент времени вывод из логической схемы 36 "И", в которую вводится набор ϕ20 сигналов вторых адресов строк, имеет H-уровень, и FET 37 с каналом n-типа в модуле 34 формирователя сигналов управления, соответствующем набору ϕ20 сигналов вторых адресов строк, выключается.

Соответственно, вывод H-уровня из логической схемы 36 "И", в которую вводится набор ϕ20 сигналов вторых адресов строк, передается в дополнительную линию слова SWL00 в субматрице 32A.

В этот момент времени, по меньшей мере, один из сигнала адреса строки из набора ϕ21-ϕ27 сигналов вторых адресов строк имеет L-уровень. Иными словами, поскольку весь вывод из логической схемы 36 "И", в которую вводится этот набор ϕ21-ϕ27, имеет L-уровень, дополнительные линии слова SWL01-SWL03 в субматрице 32A и все дополнительные линии слова SWL00-SWL03 в субматрице 32B деактивируются.

Время активации дополнительной линии слова SWL00 представляет собой, например, время, когда загружается команда Act активации.

Следует отметить, что времена активации основной линии слова MWL0 и дополнительной линии слова SWL00 отличаются в этом примере, но они также могут быть идентичными.

Когда времена активации основной линии слова MWL0 и SWL00 являются идентичными, это время активации может представлять собой время, когда загружается команда PCG предварительного заряда банка или считывание/запись с помощью команды R/W&AP автоматического предварительного заряда, или время, когда загружается команда Act активации после этого.

Фиг. 20 и 21 показывают времена активации основных и дополнительных линий слова в иерархической системе линий слова, показанной на фиг. 18 и 19.

Фиг. 20 соответствует первому и второму вариантам осуществления, описанным выше.

Ссылаясь на фиг. 20, t1-t4 соответствуют t1-t4, показанным на фиг. 6, и сигналы R_A, R_B, R_C и R_D адресов строк соответствуют сигналам R_A, R_B, R_C и R_D адресов строк, показанным на фиг. 6.

В примере A, R_A защелкивается во время t1, R_B защелкивается во время t2, и R_C защелкивается во время t3. Во время t4, R_D защелкивается, и операция активации основной линии слова MWL0 и дополнительной линии слова SWL00, показанная на фиг. 18 и 19, выполняется на основе сигналов R_A, R_B, R_C и R_D адресов строк.

В примере B, R_A защелкивается во время t1. Во время t2 R_B защелкивается, и операция активации основной линии слова MWL0, показанная на фиг. 18 и 19, выполняется на основе сигналов R_A и R_B адресов строк. Во время t3 R_C защелкивается. Во время t4, R_D защелкивается, и операция активации дополнительной линии слова SWL00, показанная на фиг. 18 и 19, выполняется на основе сигналов R_C и R_D адресов строк.

Следует отметить, что также можно активировать основную линию слова MWL0 на основе R_A и части R_B и активировать дополнительную линию слова SWL00 на основе части R_B и R_C и R_D.

В примере C, R_A защелкивается во время t1. Во время t2, R_B защелкивается, и операция активации основной линии слова MWL0 и дополнительной линии слова SWL00, показанная на фиг. 18 и 19, выполняется на основе сигналов R_A и R_B адресов строк. Кроме того, R_C защелкивается во время t3, и R_D защелкивается во время t4. Сигналы R_C и R_D адресов строк используются не для цели выбора основной линии слова MWL0 и дополнительной линии слова SWL00, а для цели, например, определения ячейки запоминающего устройства, которая должна подключаться к сенсорному считывающему усилителю S/A.

Примеры A, B и C являются примерами. В них, основная линия слова MWL0 и дополнительная линия слова SWL00 могут активироваться во время, отличное от времени, описанного в примерах A, B и C.

Фиг. 21 соответствует третьему и четвертому вариантам осуществления, описанным выше.

Ссылаясь на фиг. 21, t2-t4 соответствуют t2-t4, показанным на фиг. 14, и сигналы R_A, R_B и R_C адресов строк соответствуют сигналам R_A, R_B и R_C адресов строк, показанным на фиг. 14.

В примере A, R_A защелкивается во время t2, R_B защелкивается во время t3, и R_C защелкивается во время t4. Кроме того, во время t4, операция активации основной линии слова MWL0 и дополнительной линии слова SWL00, показанная на фиг. 18 и 19, выполняется на основе сигналов R_A, R_B и R_C адресов строк.

В примере B, во время t2, защелкивается R_A, и операция активации основной линии слова MWL0, показанная на фиг. 18 и 19, выполняется на основе сигнала R_A адреса строки. Кроме того, R_B защелкивается во время t3, и R_C защелкивается во время t4. Помимо этого, во время t4, операция активации дополнительной линии слова SWL00, показанная на фиг. 18 и 19, выполняется на основе сигналов R_B и R_C адресов строк.

В примере C, во время t2, R_A защелкивается, и операция активации основной линии слова MWL0 и дополнительной линии слова SWL00, показанная на фиг. 18 и 19, выполняется на основе сигнала R_A адреса строки. Кроме того, R_B защелкивается во время t3, и R_C защелкивается во время t4. Сигналы R_B и R_C адресов строк используются не для цели выбора основной линии слова MWL0 и дополнительной линии слова SWL00, а для цели, например, определения ячейки запоминающего устройства, которая должна подключаться к сенсорному считывающему усилителю S/A.

Примеры A, B и C являются примерами. В них, основная линия слова MWL0 и дополнительная линия слова SWL00 могут активироваться во время, отличное от времени, описанного в примерах A, B и C.

Хотя описаны конкретные варианты осуществления, эти варианты осуществления представлены только в качестве примера и не предназначены ограничивать объем изобретения. Фактически, новые варианты осуществления, описанные в данном документе, могут быть осуществлены во множестве других форм; кроме того, различные пропуски, подстановки и изменения в форме вариантов осуществления, описанных в данном документе, могут осуществляться без отступления от сущности изобретения. Прилагаемая формула изобретения и ее эквиваленты предназначены охватывать такие формы и модификации как попадающие в пределы объема и сущности изобретения.

| название | год | авторы | номер документа |

|---|---|---|---|

| ПОЛУПРОВОДНИКОВОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 2014 |

|

RU2634217C2 |

| ПОЛУПРОВОДНИКОВОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 2014 |

|

RU2643629C2 |

| ПОЛУПРОВОДНИКОВОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 2014 |

|

RU2641478C2 |

| ПОЛУПРОВОДНИКОВОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 2014 |

|

RU2618368C2 |

| СПОСОБ И УСТРОЙСТВО ДЛЯ НЕЯВНОЙ ПРЕДВАРИТЕЛЬНОЙ ЗАРЯДКИ ДИНАМИЧЕСКОЙ ОПЕРАТИВНОЙ ПАМЯТИ (DRAM) | 2004 |

|

RU2331118C2 |

| ПОЛУПРОВОДНИКОВОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 2006 |

|

RU2391722C2 |

| МУЛЬТИПЛЕКСИРОВАНИЕ АДРЕСОВ В ПСЕВДО ДВУХПОРТОВОЙ ПАМЯТИ | 2009 |

|

RU2490731C2 |

| ПОЛУПРОВОДНИКОВАЯ ПАМЯТЬ | 1993 |

|

RU2156506C2 |

| Устройство для отображения информации | 1986 |

|

SU1441450A1 |

| ДЕКОДЕР ПОДВИЖНОГО ИЗОБРАЖЕНИЯ И СПОСОБ ЗАПИСИ ГРУППЫ ДАННЫХ ВИДЕОСИГНАЛА В СИНХРОННОМ ДИНАМИЧЕСКОМ УСТРОЙСТВЕ | 1996 |

|

RU2160969C2 |

Группа изобретений относится к энергонезависимым запоминающим устройствам. Техническим результатом является увеличение числа битов адреса без изменений спецификаций устройства. Устройство содержит матрицу ячеек запоминающего устройства с банками, причем каждый банк включает в себя строки, первые линии слова, предоставленные в соответствии со строками, схему-защелку адресов, которая защелкивает сигнал первого адреса строки, декодер строк, который активирует одну из первых линий слова, и схему управления, которая выполнена с возможностью исполнять первую операцию, которая активирует один из банков на основе сигнала адреса банка, когда загружается первая команда, и вторую операцию, которая защелкивает сигнал первого адреса строки в схеме-защелке адресов, и исполнять третью операцию, которая активирует одну из первых линий слова посредством декодера строк на основе сигнала второго адреса строки и сигнала первого адреса строки, защелкиваемых в схеме-защелке адресов, когда вторая команда загружается после первой команды. 2 н. и 33 з.п. ф-лы, 21 ил.

1. Энергонезависимое оперативное запоминающее устройство, содержащее:

- матрицу ячеек запоминающего устройства с банками, причем каждый банк включает в себя строки;

- первые линии слова, предоставленные в соответствии со строками;

- схему-защелку адресов, которая защелкивает сигнал первого адреса строки;

- декодер строк, который активирует одну из первых линий слова; и

- схему управления, которая выполнена с возможностью:

- исполнять первую операцию, которая активирует один из банков на основе сигнала адреса банка, когда загружается первая команда, и вторую операцию, которая защелкивает сигнал первого адреса строки в схеме-защелке адресов, и

- исполнять третью операцию, которая активирует одну из первых линий слова посредством декодера строк на основе сигнала второго адреса строки и сигнала первого адреса строки, защелкиваемых в схеме-защелке адресов, когда вторая команда загружается после первой команды.

2. Запоминающее устройство по п. 1, в котором:

- первая команда представляет собой команду предварительного заряда банка, и

- первая операция представляет собой операцию предварительного заряда банка, которая должна исполняться посредством команды предварительного заряда банка.

3. Запоминающее устройство по п. 2, в котором схема управления выполняет операцию приема сигнала адреса столбца, когда команда считывания/записи вводится после второй команды.

4. Запоминающее устройство по п. 1, в котором:

- первая команда представляет собой считывание/запись с помощью команды автоматического предварительного заряда, и

- первая операция представляет собой операцию предварительного заряда банка, которая должна исполняться посредством считывания/записи с помощью команды автоматического предварительного заряда.

5. Запоминающее устройство по п. 4, в котором схема управления выполняет операцию приема сигнала адреса столбца, когда вводится первая команда.

6. Запоминающее устройство по п. 1, дополнительно содержащее вторую линию слова, выполненную с возможностью выбирать строки вместе,

- при этом декодер строк активирует вторую линию слова на основе сигнала первого адреса строки, и

- активирует одну из первых линий слова на основе сигнала второго адреса строки.

7. Запоминающее устройство по п. 6, в котором одна из первых линий слова и вторая линия слова активируются, когда вводится вторая команда.

8. Запоминающее устройство по п. 6, в котором:

- вторая линия слова активируется, когда вводится первая команда, и

- одна из первых линий слова активируется, когда вводится вторая команда.

9. Запоминающее устройство по п. 1, дополнительно содержащее вторую линию слова, выполненную с возможностью выбирать строки вместе,

- при этом декодер строк активирует вторую линию слова на основе сигнала первого адреса строки и сигнала второго адреса строки.

10. Запоминающее устройство по п. 1, в котором схема-защелка адресов поддерживает защелкивание сигнала первого адреса строки до тех пор, пока не будет введена вторая команда.

11. Запоминающее устройство по п. 1, в котором:

- вторая команда представляет собой команду активации,

- третья операция представляет собой операцию активации, которая должна исполняться посредством команды активации, и

- вторая операция представляет собой операцию предварительной активации для подготовки к операции активации.

12. Запоминающее устройство по п. 1, в котором банк, являющийся целью второй операции, и банк, являющийся целью первой операции, выбираются одновременно.

13. Запоминающее устройство по п. 1, в котором банк, являющийся целью второй операции, выбирается независимо от банка, являющегося целью первой операции.

14. Запоминающее устройство по п. 1, дополнительно содержащее формирователь тактовых сигналов, выполненный с возможностью формировать внутренний тактовый сигнал,

- при этом первая команда и сигнал адреса банка вводятся на основе переднего фронта одного тактового цикла внутреннего тактового сигнала.

15. Запоминающее устройство по п. 1, дополнительно содержащее формирователь тактовых сигналов, выполненный с возможностью формировать внутренний тактовый сигнал,

- при этом первая команда вводится на основе переднего фронта одного тактового цикла внутреннего тактового сигнала,

- третья команда определяет то, что вторая операция представляет собой операцию подготовки к третьей операции, и

- третья команда вводится на основе заднего фронта упомянутого одного тактового цикла.

16. Запоминающее устройство по п. 1, дополнительно содержащее формирователь тактовых сигналов, выполненный с возможностью формировать внутренний тактовый сигнал,

- при этом сигнал адреса банка вводится на основе переднего фронта одного тактового цикла внутреннего тактового сигнала, и

- сигнал адреса банка, который обозначает банк в качестве цели сигнала первого адреса строки, вводится на основе заднего фронта упомянутого одного тактового цикла.

17. Запоминающее устройство по п. 1, дополнительно содержащее формирователь тактовых сигналов, выполненный с возможностью формировать внутренний тактовый сигнал,

- при этом сигнал первого адреса строки вводится на основе по меньшей мере одного из переднего фронта и заднего фронта одного тактового цикла внутреннего тактового сигнала.

18. Запоминающее устройство по п. 1, дополнительно содержащее формирователь тактовых сигналов, выполненный с возможностью формировать внутренний тактовый сигнал,

- при этом вторая команда и сигнал второго адреса строки вводятся на основе переднего фронта одного тактового цикла внутреннего тактового сигнала.

19. Запоминающее устройство по п. 1, дополнительно содержащее формирователь тактовых сигналов, выполненный с возможностью формировать внутренний тактовый сигнал,

- при этом сигнал второго адреса строки вводится на основе по меньшей мере одного из переднего фронта и заднего фронта одного тактового цикла внутреннего тактового сигнала.

20. Энергонезависимое оперативное запоминающее устройство, содержащее:

- матрицу ячеек запоминающего устройства, включающую в себя банки, причем каждый банк включает в себя строки;

- первые линии слова, сформированные в соответствии “один-к-одному” со строками;

- схему-защелку адресов, выполненную с возможностью защелкивать сигнал первого адреса строки;

- декодер строк, выполненный с возможностью активировать одну из первых линий слова;

- формирователь тактовых сигналов, выполненный с возможностью формировать внутренний тактовый сигнал; и

- схему управления, выполненную с возможностью принимать первую команду на основе переднего фронта одного тактового цикла внутреннего тактового сигнала, и

- принимать вторую команду на основе заднего фронта упомянутого одного тактового цикла.

21. Запоминающее устройство по п. 20, в котором схема управления выполняет первую операцию активации одного из банков на основе сигнала адреса банка, когда вводится первая команда,

- выполняет вторую операцию защелкивания сигнала первого адреса строки в схеме-защелке адресов, когда вводится вторая команда, и

- выполняет третью операцию активации одной из первых линий слова посредством декодера строк на основе сигнала второго адреса строки и сигнала первого адреса строки, защелкиваемых в схеме-защелке адресов, когда вводится третья команда после второй команды.

22. Запоминающее устройство по п. 21, дополнительно содержащее вторую линию слова, выполненную с возможностью выбирать строки вместе,

- при этом декодер строк активирует вторую линию слова на основе сигнала первого адреса строки, и

- активирует одну из первых линий слова на основе сигнала второго адреса строки.

23. Запоминающее устройство по п. 22, в котором одна из первых линий слова и вторая линия слова активируются, когда вводится третья команда.

24. Запоминающее устройство по п. 22, в котором:

- вторая линия слова активируется, когда вводится вторая команда, и

- одна из первых линий слова активируется, когда вводится третья команда.

25. Запоминающее устройство по п. 21, дополнительно содержащее вторую линию слова, выполненную с возможностью выбирать строки вместе,

- при этом декодер строк активирует вторую линию слова на основе сигнала первого адреса строки и сигнала второго адреса строки.

26. Запоминающее устройство по п. 21, в котором схема-защелка адресов поддерживает защелкивание сигнала первого адреса строки до тех пор, пока не будет введена третья команда.

27. Запоминающее устройство по п. 21, в котором:

- первая команда представляет собой команду предварительного заряда банка и первая операция представляет собой операцию предварительного заряда банка, которая должна исполняться посредством команды предварительного заряда банка,

- вторая команда представляет собой команду предварительной активации и вторая операция представляет собой операцию предварительной активации, которая должна исполняться посредством команды предварительной активации, и

- третья команда представляет собой команду активации и третья операция представляет собой операцию активации, которая должна исполняться посредством команды активации.

28. Запоминающее устройство по п. 27, в котором схема управления выполняет операцию приема сигнала адреса столбца, когда команда считывания/записи вводится после третьей команды.

29. Запоминающее устройство по п. 21, в котором:

- первая команда представляет собой считывание/запись с помощью команды автоматического предварительного заряда и первая операция представляет собой операцию предварительного заряда банка, которая должна исполняться посредством считывания/записи с помощью команды автоматического предварительного заряда,

- вторая команда представляет собой команду предварительной активации и вторая операция представляет собой операцию предварительной активации, которая должна исполняться посредством команды предварительной активации, и

- третья команда представляет собой команду активации и третья операция представляет собой операцию активации, которая должна исполняться посредством команды активации.

30. Запоминающее устройство по п. 29, в котором схема управления выполняет операцию приема сигнала адреса столбца, когда вводится первая команда.

31. Запоминающее устройство по п. 21, в котором банк, являющийся целью второй операции, и банк, являющийся целью первой операции, выбираются одновременно.

32. Запоминающее устройство по п. 21, в котором банк, являющийся целью второй операции, выбирается независимо от банка, являющегося целью первой операции.

33. Запоминающее устройство по п. 21, в котором сигнал адреса банка вводится на основе переднего фронта упомянутого одного тактового цикла.

34. Запоминающее устройство по п. 21, в котором:

- сигнал адреса банка вводится на основе переднего фронта упомянутого одного тактового цикла, и

- сигнал адреса банка для обозначения банка в качестве цели сигнала первого адреса строки вводится на основе заднего фронта упомянутого одного тактового цикла.

35. Запоминающее устройство по п. 21, в котором сигнал первого адреса строки вводится на основе по меньшей мере одного из переднего фронта и заднего фронта упомянутого одного тактового цикла.

| US 6510095 B1, 21.01.2003 | |||

| US 2002116657 A1, 22.08.2002 | |||

| US 2008151678 A1, 26.06.2008 | |||

| US 7818638 B2, 19.10.2010 | |||

| СПОСОБ И УСТРОЙСТВО ДЛЯ НЕЯВНОЙ ПРЕДВАРИТЕЛЬНОЙ ЗАРЯДКИ ДИНАМИЧЕСКОЙ ОПЕРАТИВНОЙ ПАМЯТИ (DRAM) | 2004 |

|

RU2331118C2 |

Авторы

Даты

2017-06-20—Публикация

2014-03-11—Подача