Перекрестная ссылка на родственные заявки

Данная заявка основана и притязает на приоритеты предварительной заявки США № 61/873,800, поданной 4 сентября 2013 года, и заявки на патент США № 14/201,686, поданной 7 марта 2014 года, содержимое которых полностью включено в данную заявку посредством ссылки.

Область техники, к которой относится изобретение

Варианты осуществления, описанные в данном документе, относятся в целом к полупроводниковому запоминающему устройству.

Уровень техники

MRAM (магниторезистивная оперативная память) представляет собой запоминающее устройство, которое использует магнитный элемент, обладающий магниторезистивным эффектом, в качестве ячейки памяти, выполненной с возможностью хранения информации, и привлекло к себе большое внимание как запоминающее устройство следующего поколения c высокоскоростной работой, большой емкостью и энергонезависимостью. Кроме того, ведутся научные исследования и разработки MRAM, которая заменит энергозависимую память, такую как DRAM или SRAM. В этом случае предпочтительно, чтобы MRAM управлялась в соответствии с теми же спецификациями, что и DRAM или SRAM, для уменьшения стоимости разработки и обеспечения легкой замены.

Краткое описание чертежей

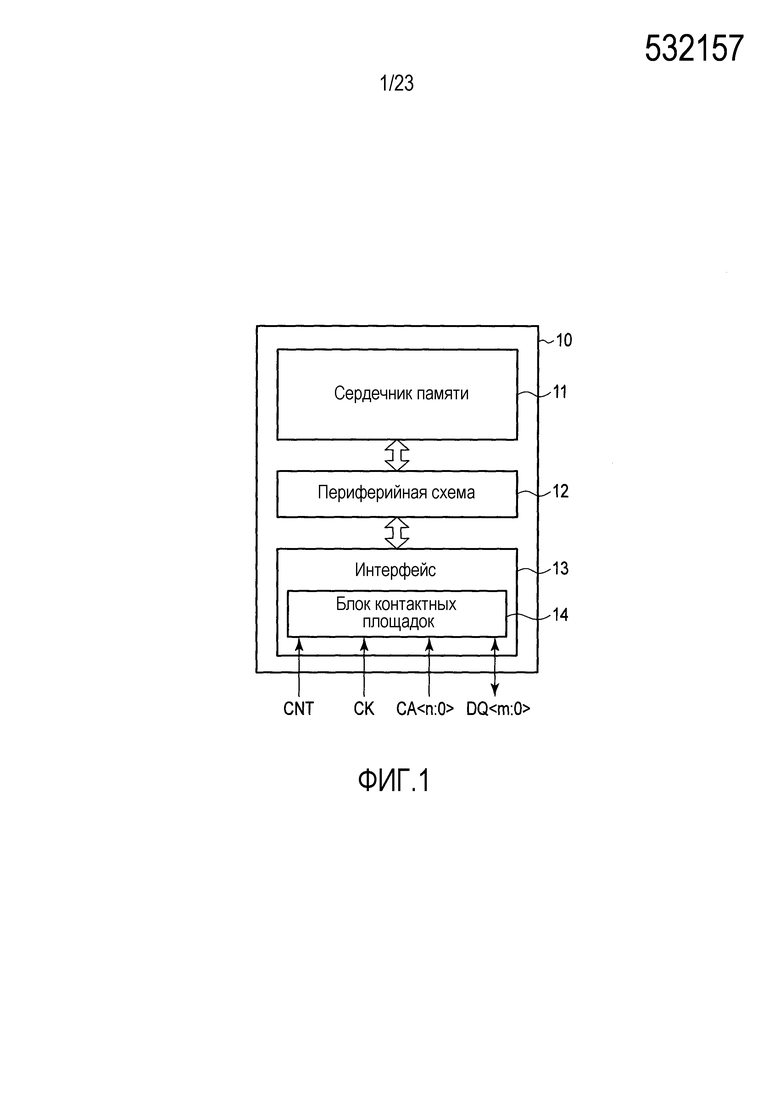

Фиг.1 представляет собой схематический вид полупроводникового запоминающего устройства согласно первому варианту осуществления;

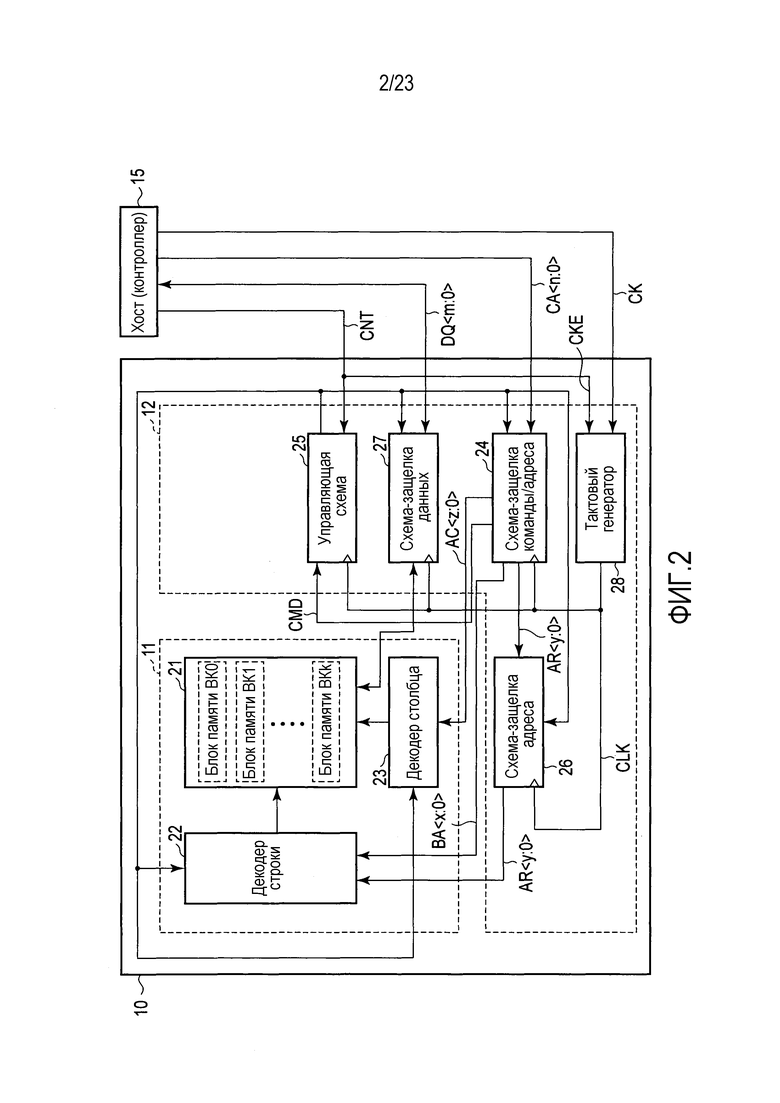

Фиг. 2 представляет собой блок-схему, показывающую пример сердечника памяти и периферийной схемы;

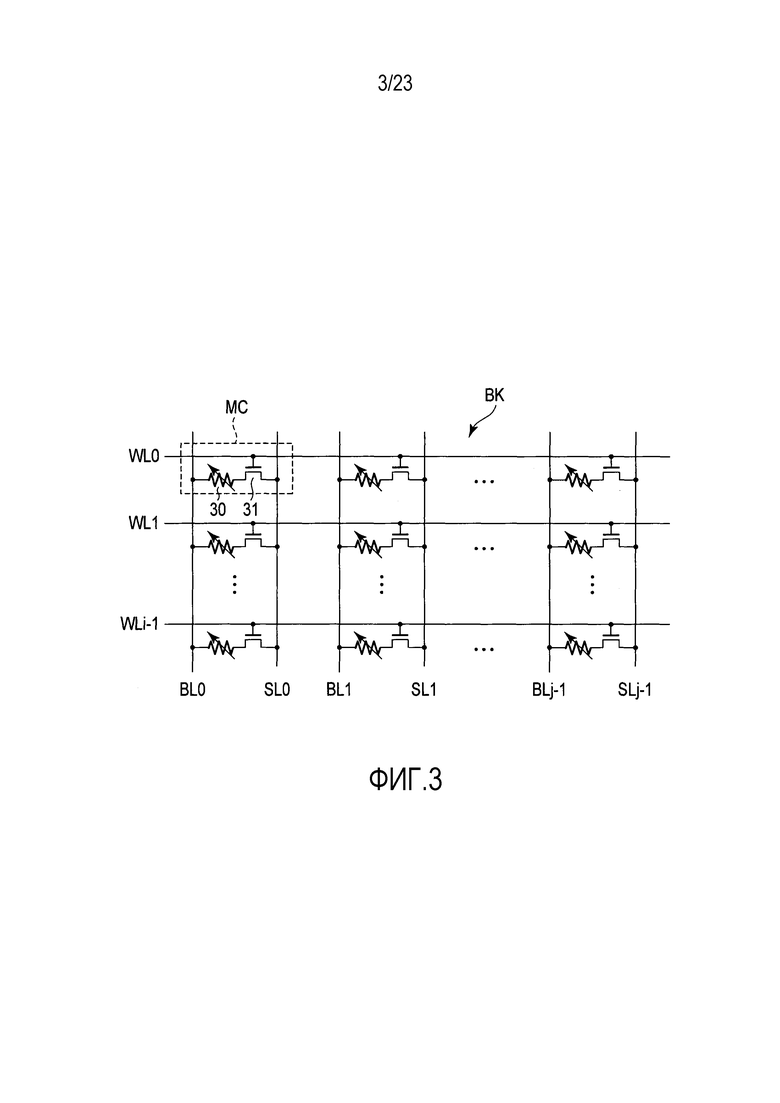

Фиг. 3 представляет собой принципиальную схему массива ячеек памяти, включенных в один блок памяти;

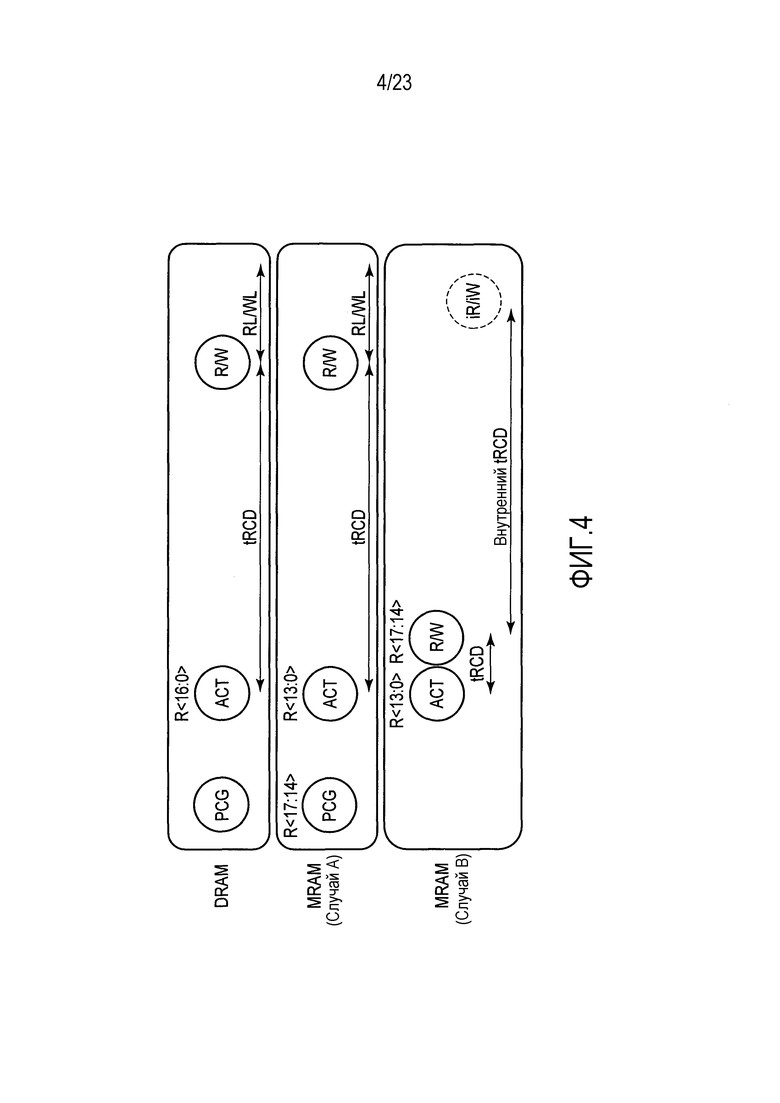

Фиг. 4 представляет собой временную диаграмму, касающуюся команд и адресов;

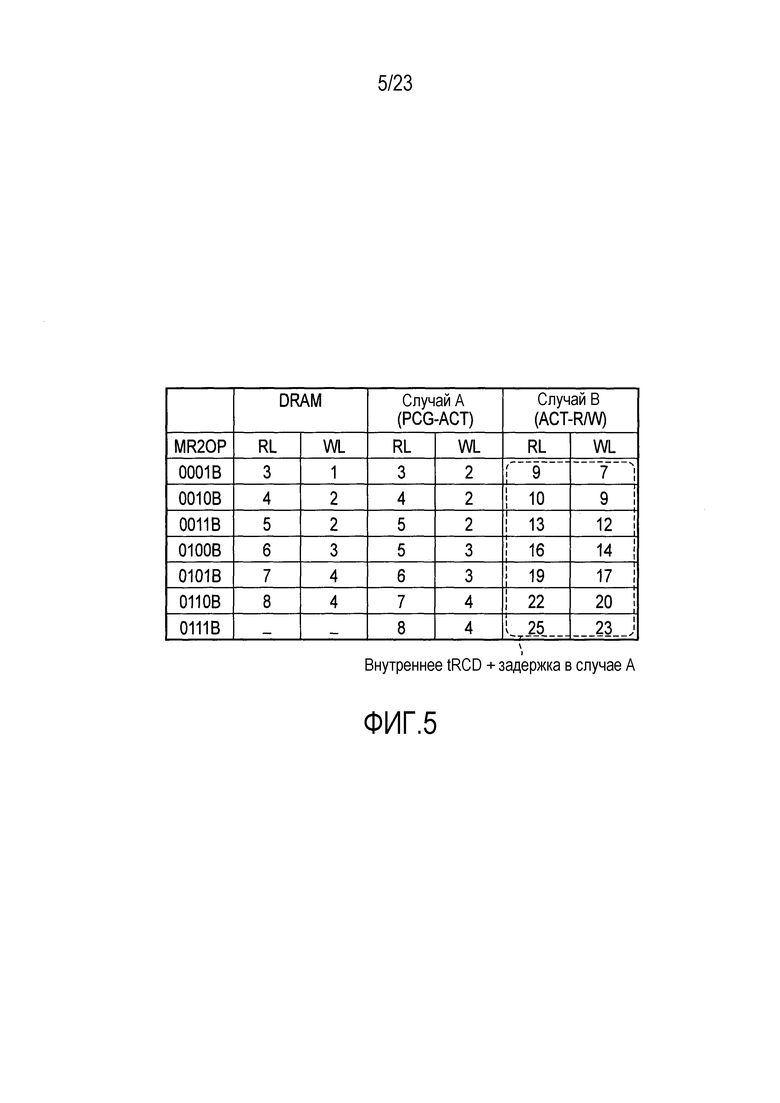

Фиг. 5 представляет собой вид, показывающий пример запаздывания считывания и запаздывания записи;

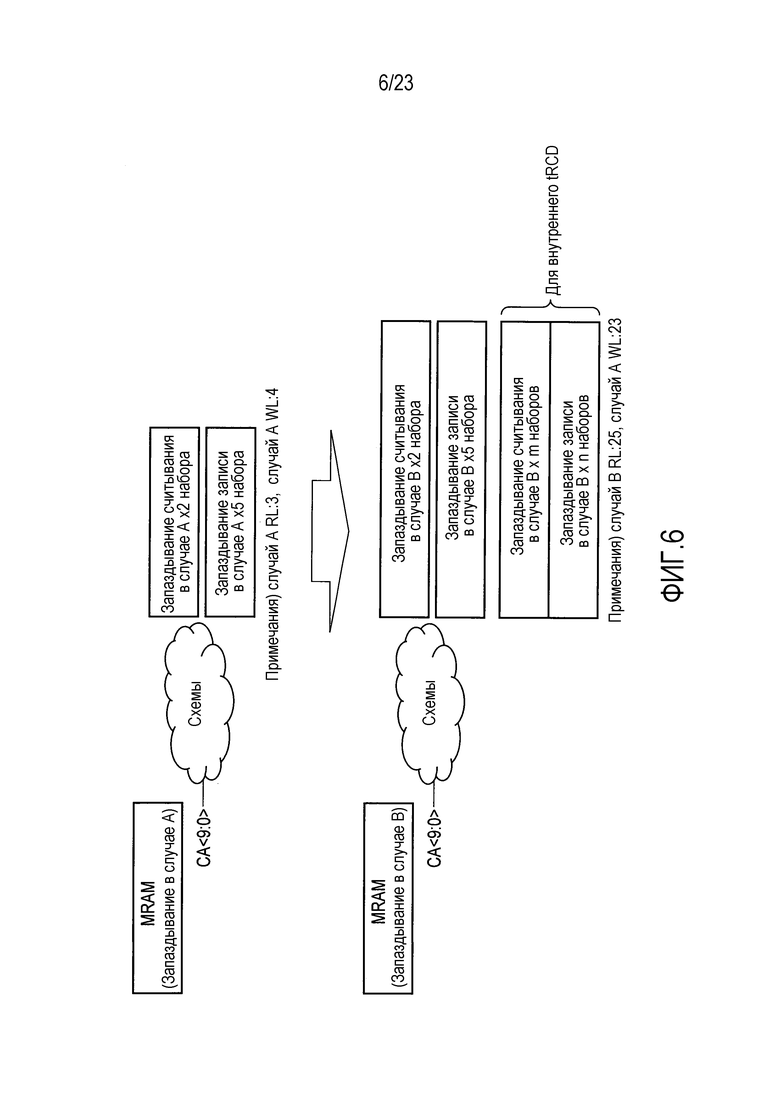

Фиг. 6 представляет собой вид, поясняющий пример количества сдвиговых регистров для запаздывания;

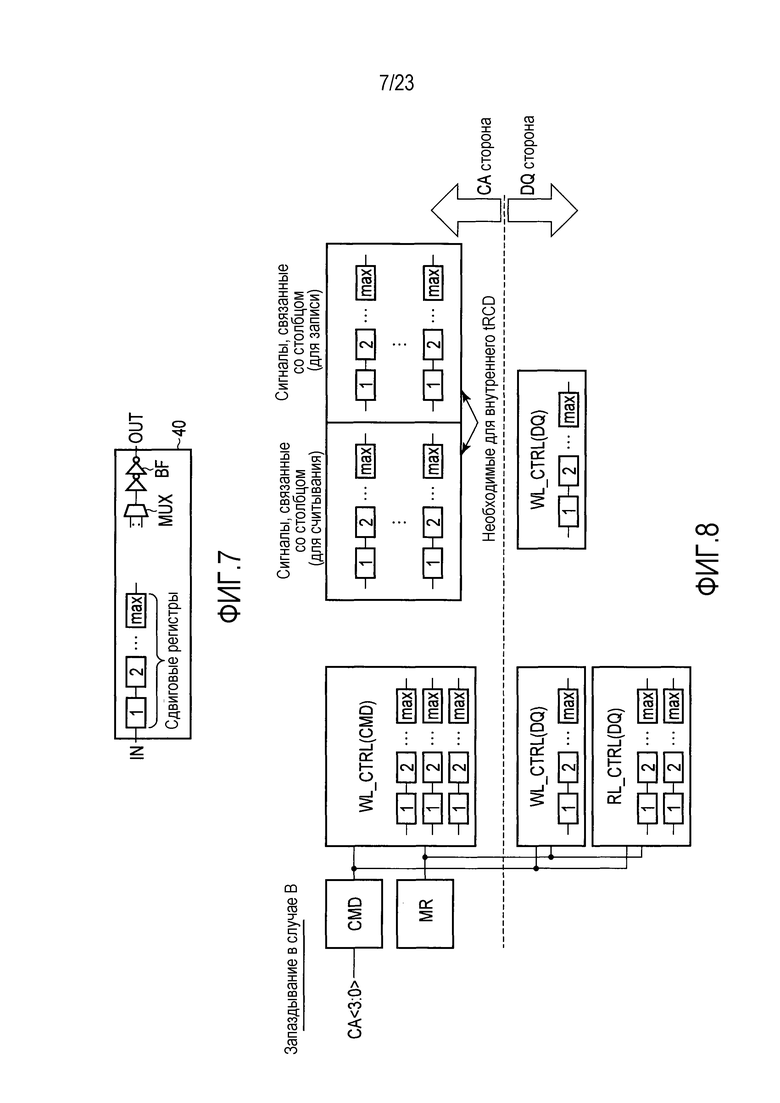

Фиг. 7 представляет собой принципиальную схему для схемы задержки для обеспечения запаздывания;

Фиг. 8 представляет собой вид, поясняющий сдвиговые регистры для запаздывания в случае B;

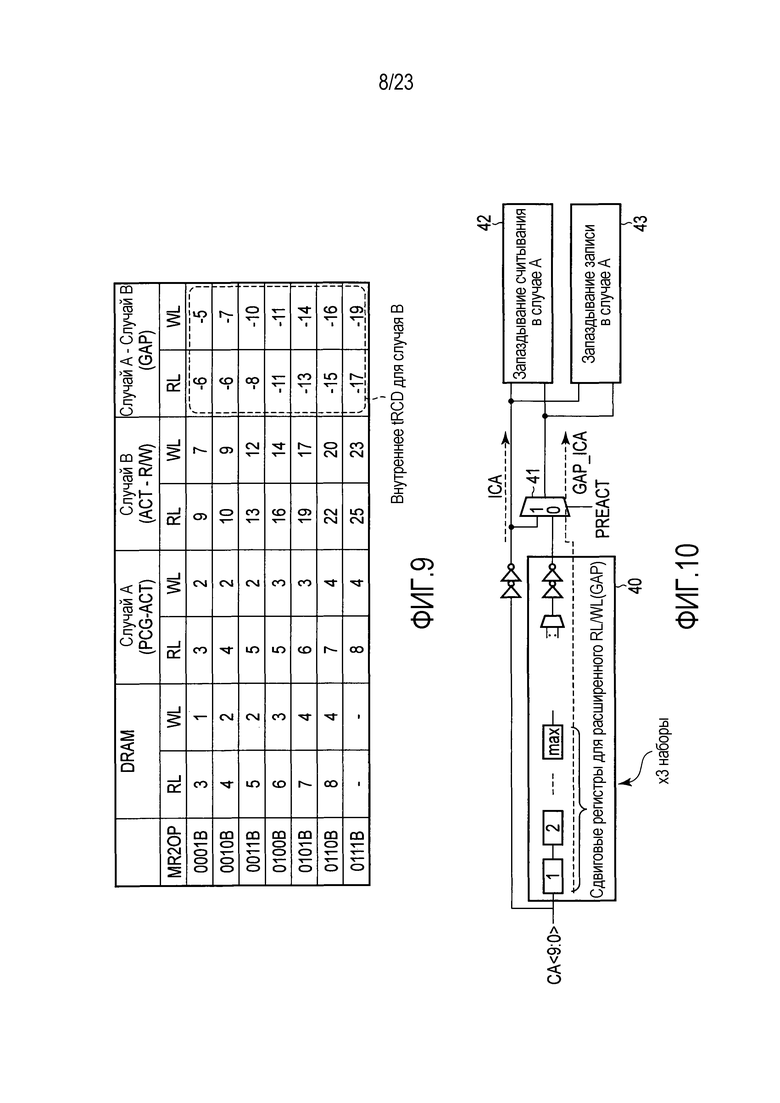

Фиг. 9 представляет собой вид, поясняющий расхождение запаздываний между случаем А и случаем В;

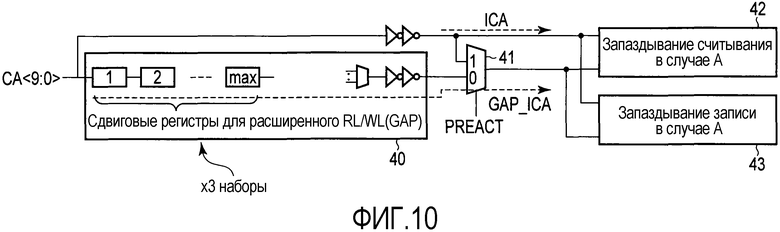

Фиг. 10 представляет собой вид, поясняющий идею первого варианта осуществления;

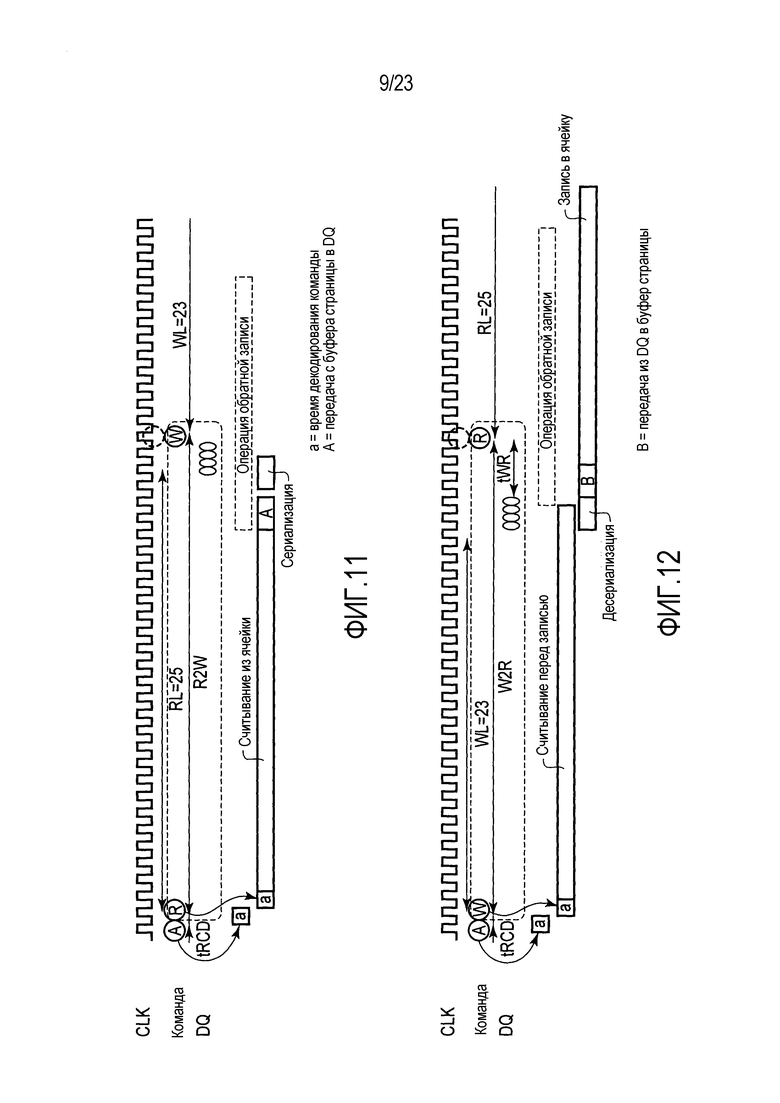

Фиг. 11 представляет собой временную диаграмму, показывающую операцию переключения от считывания к записи в соответствии со сравнительным примером;

Фиг. 12 представляет собой временную диаграмму, показывающую операцию переключения от записи к считыванию в соответствии со сравнительным примером;

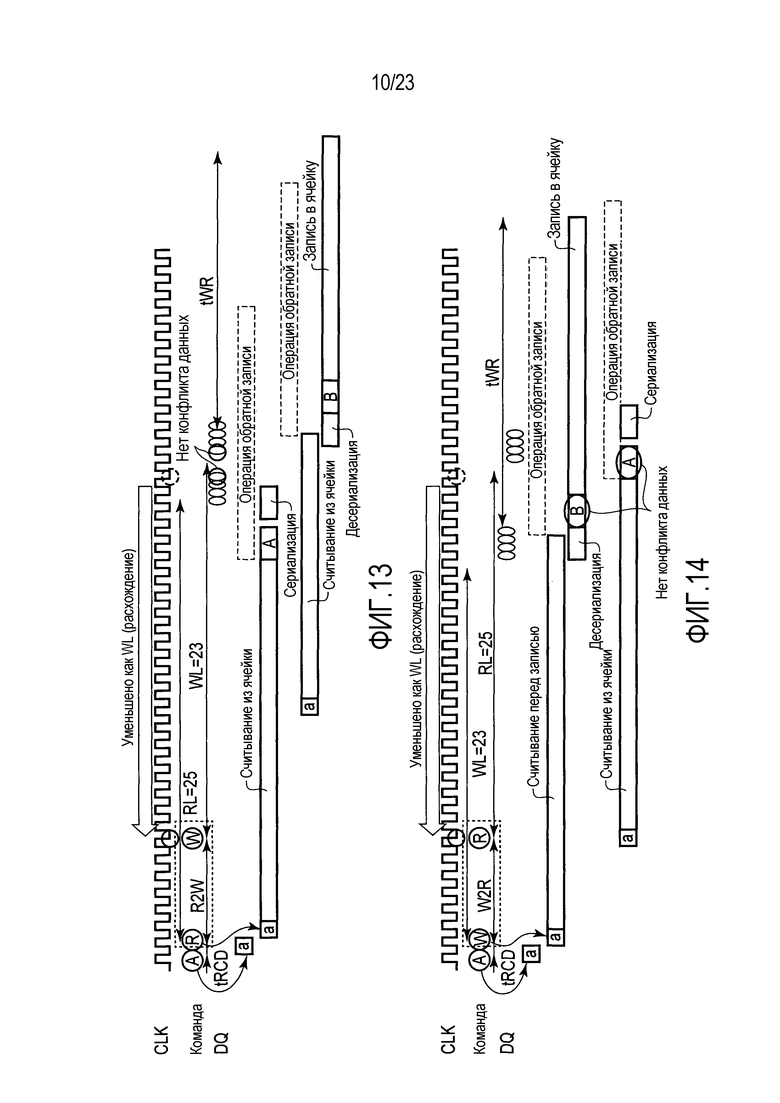

Фиг. 13 представляет собой временную диаграмму, показывающую операцию переключения от считывания к записи в соответствии с одним примером;

Фиг. 14 представляет собой временную диаграмму, показывающую операцию переключения от записи к считыванию в соответствии с одним примером;

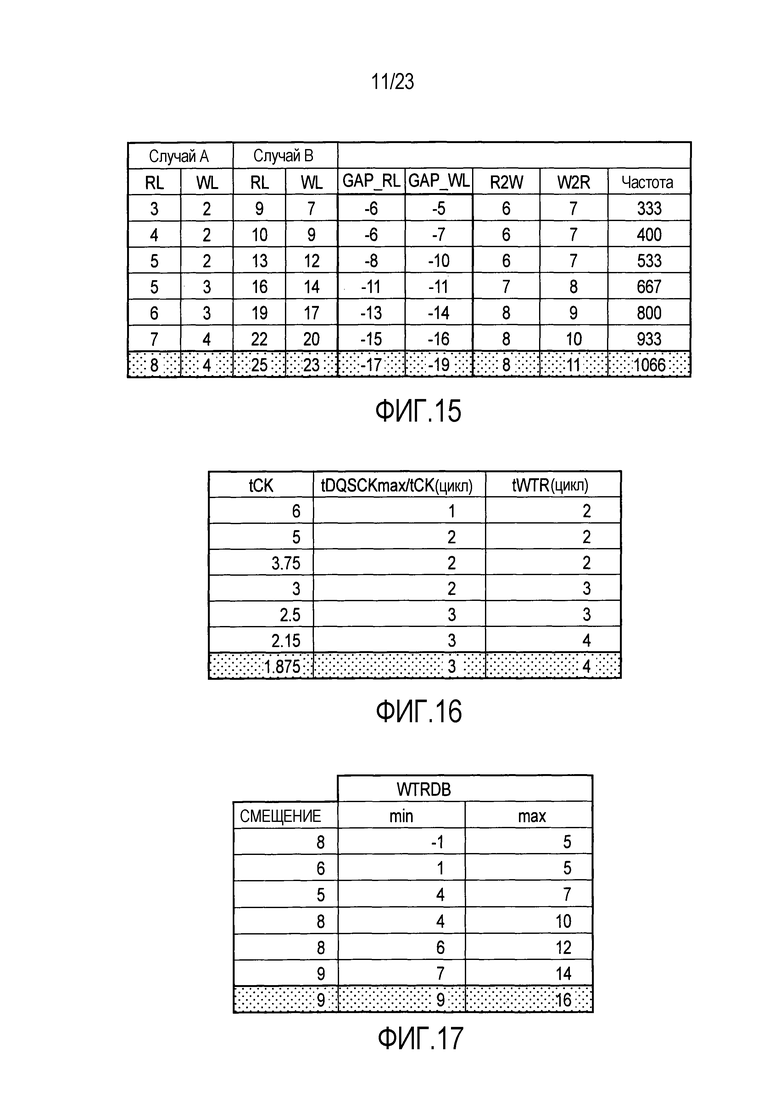

Фиг. 15 представляет собой вид, показывающий R2W и W2R во множестве режимов;

Фиг. 16 представляет собой вид для пояснения параметров;

Фиг. 17 представляет собой вид, поясняющий минимальное и максимальное время задержки сигнала WTRDB;

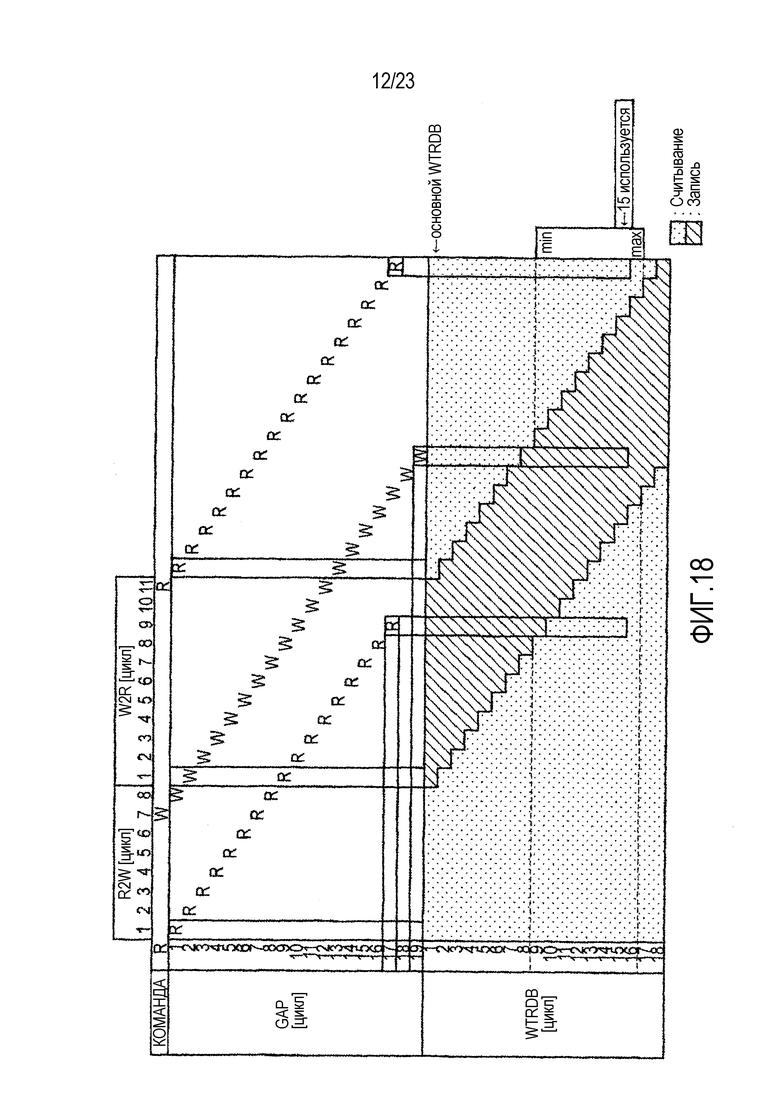

Фиг. 18 представляет собой вид, поясняющий время задержки сигнала WTRDB;

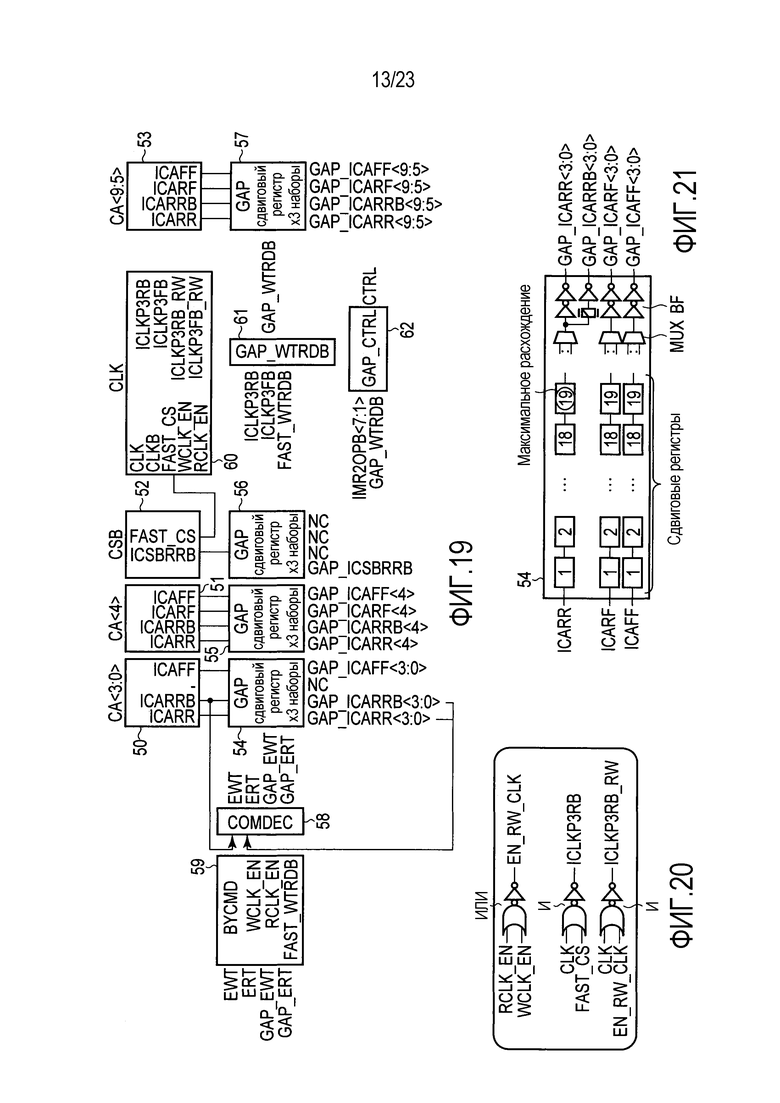

Фиг. 19 представляет собой блок-схему, показывающую пример схемной компоновки, включающей в себя сдвиговые регистры расхождения;

Фиг. 20 представляет собой принципиальную схему тактового генератора;

Фиг. 21 представляет собой принципиальную схему для схемы задержки расхождения, показанной на Фиг. 19;

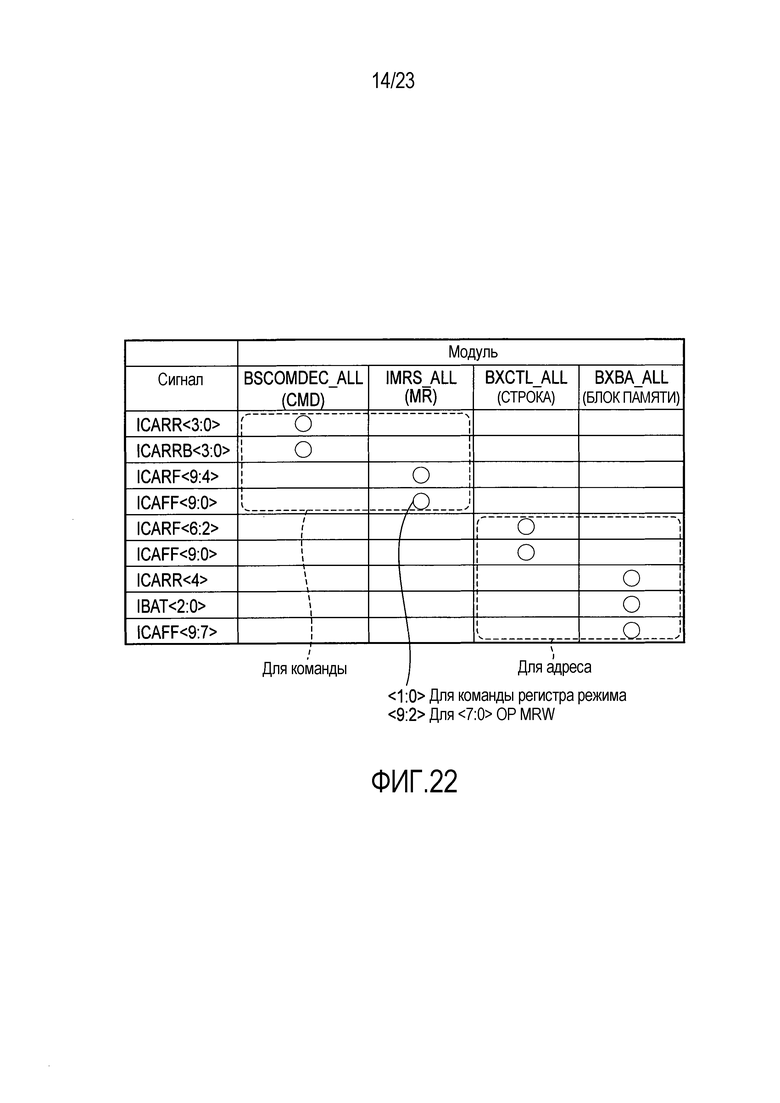

Фиг. 22 представляет собой вид, поясняющий назначение ICA для сигнала, связанного со строкой;

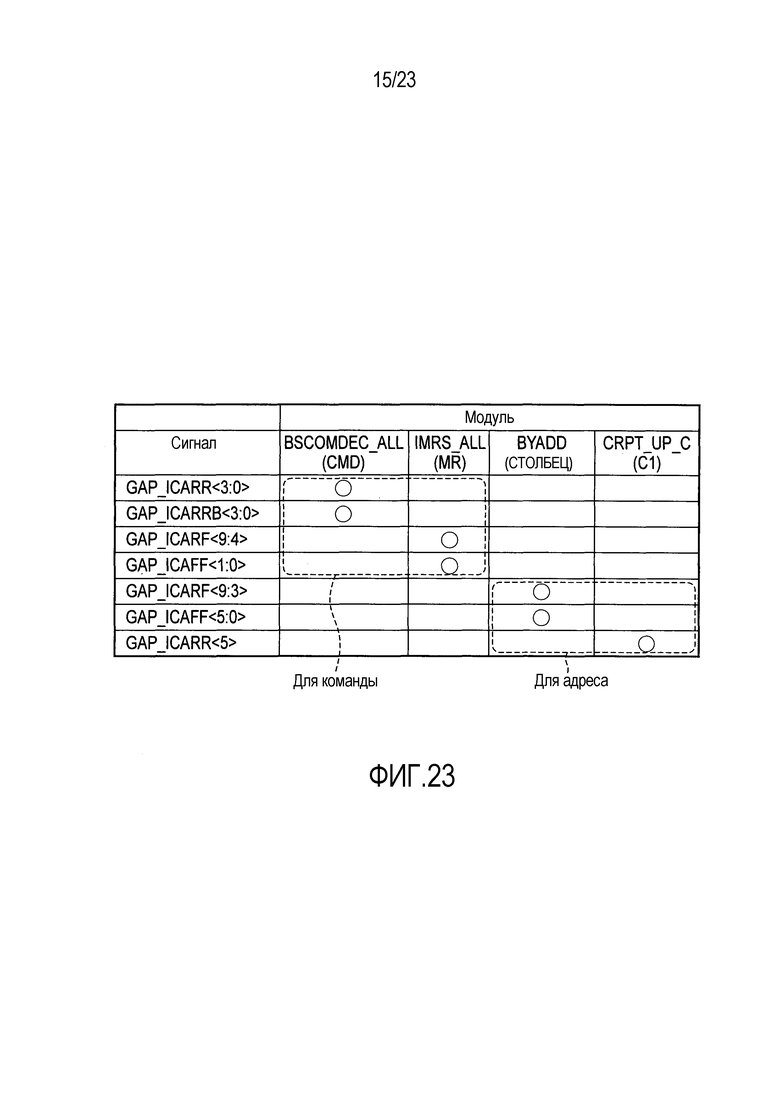

Фиг. 23 представляет собой вид, поясняющий назначение ICA для сигнала, связанного со столбцом;

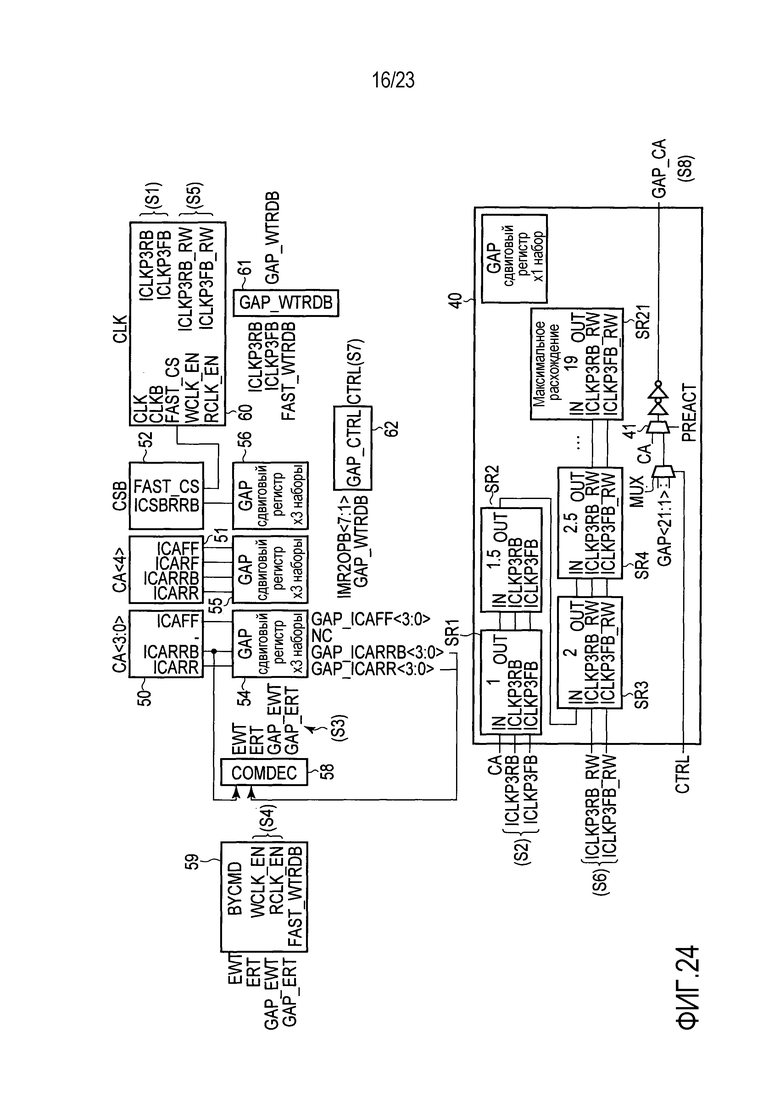

Фиг. 24 представляет собой вид, поясняющий последовательность операций в соответствии с одним примером;

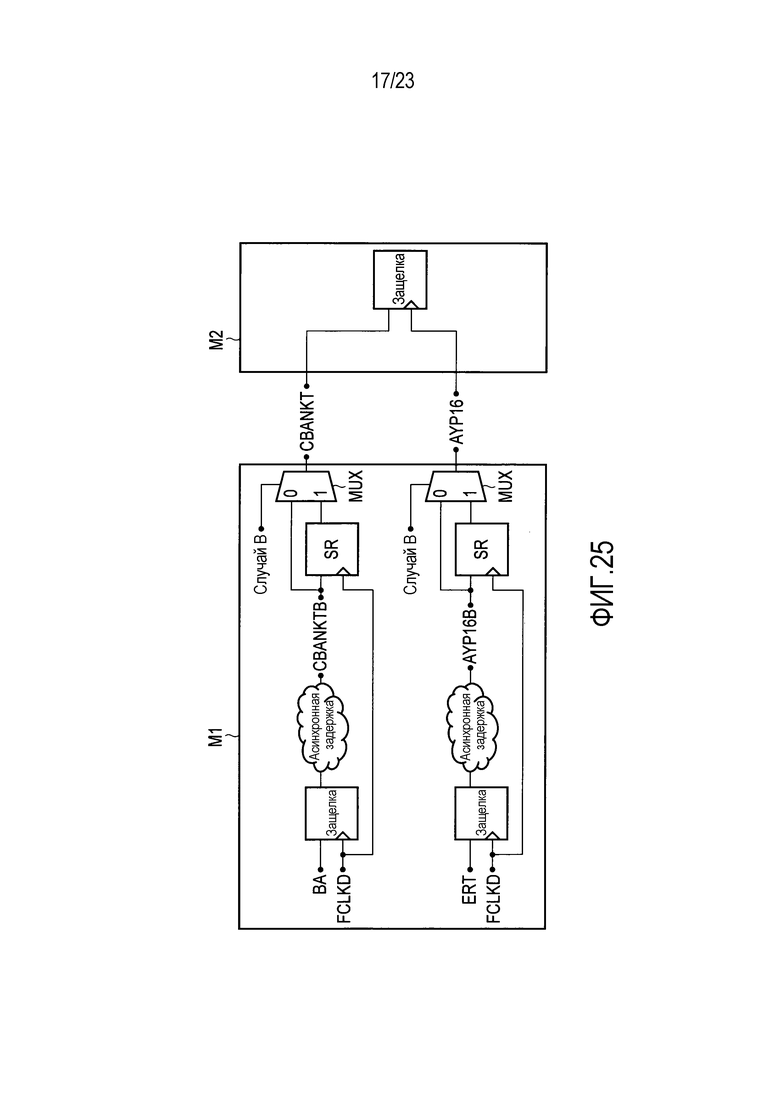

Фиг. 25 представляет собой схематический вид, поясняющий схему расположения сдвиговых регистров SR в соответствии со сравнительным примером;

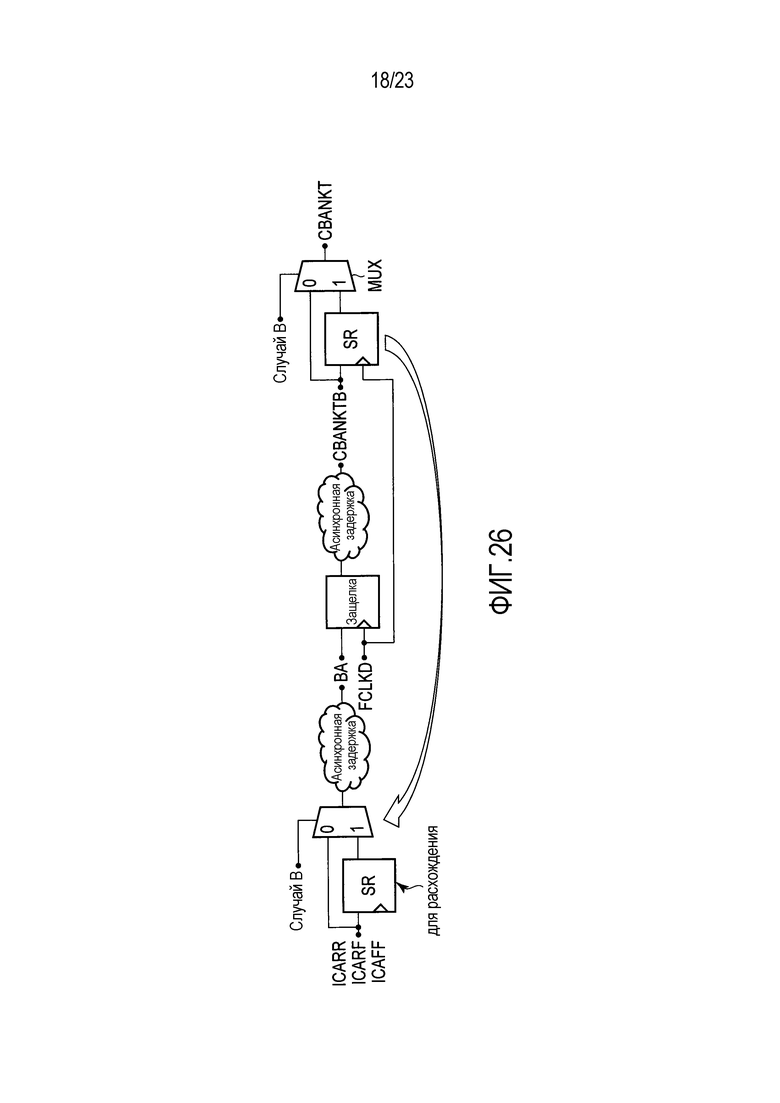

Фиг. 26 представляет собой схематический вид, поясняющий схему расположения сдвиговых регистров SR в соответствии с одним примером;

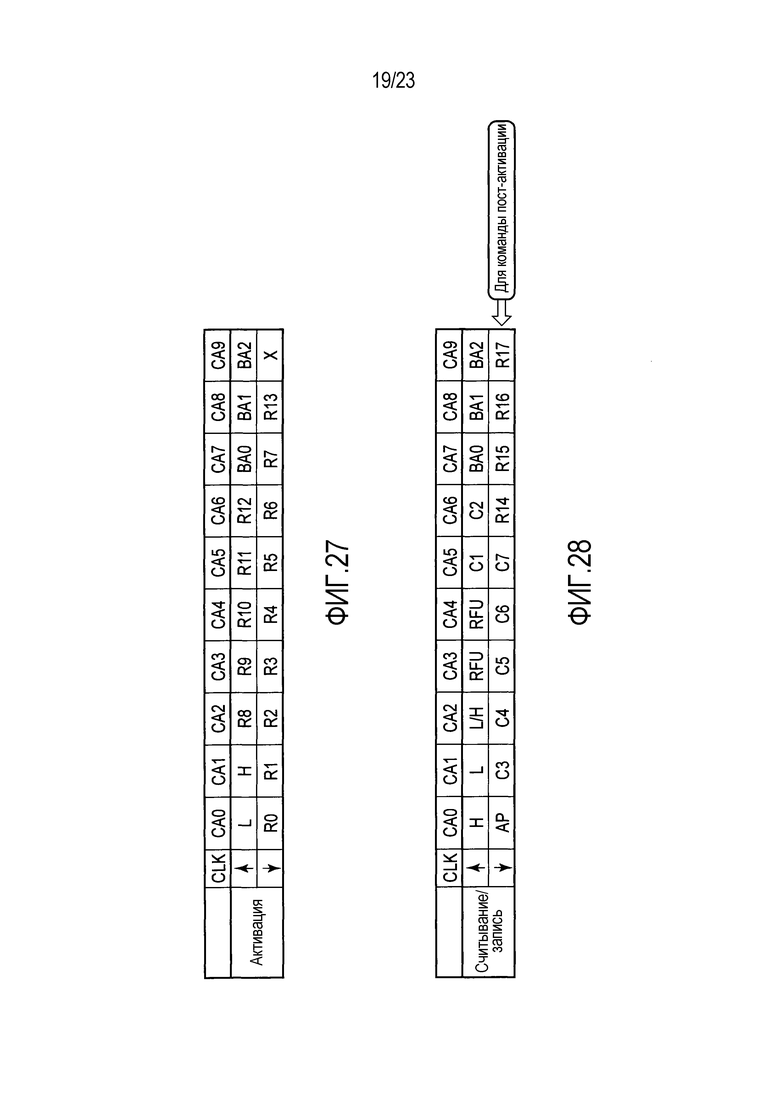

Фиг. 27 представляет собой вид, поясняющий назначение команды/адреса относительно команды активации в соответствии со вторым вариантом осуществления;

Фиг. 28 представляет собой вид, поясняющий назначение команды/адреса относительно команды считывания/записи;

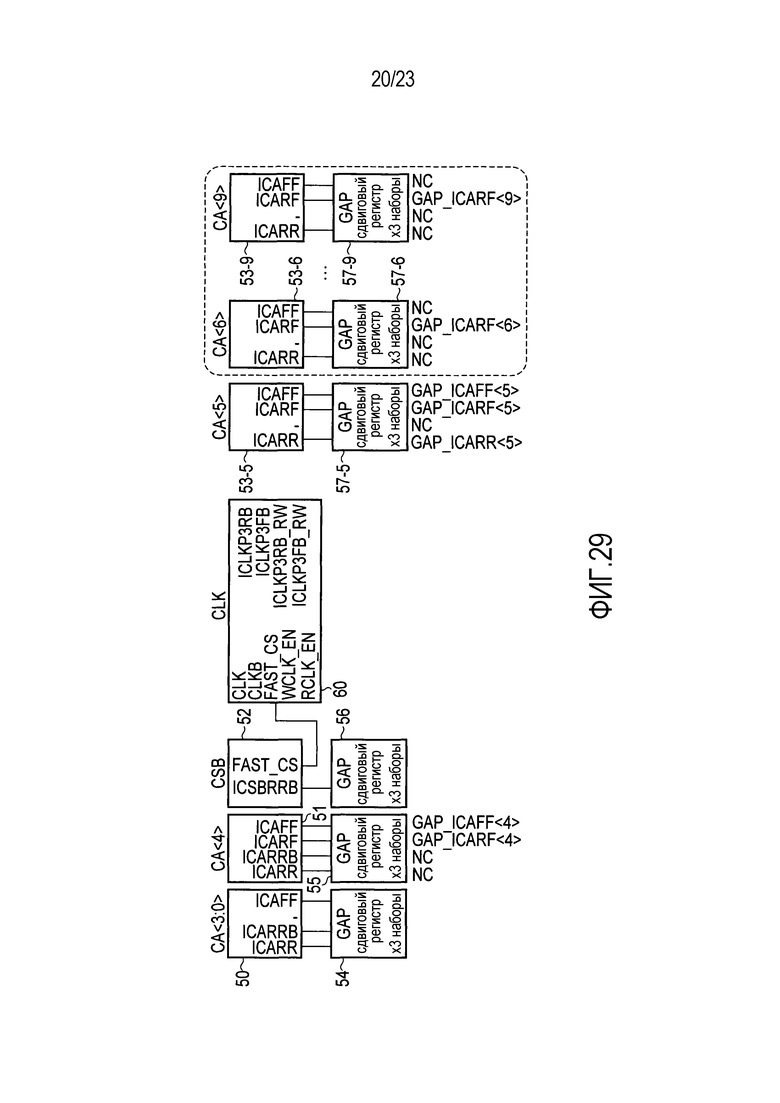

Фиг. 29 представляет собой блок-схему, показывающую компоновку сдвиговых регистров в соответствии со сравнительным примером;

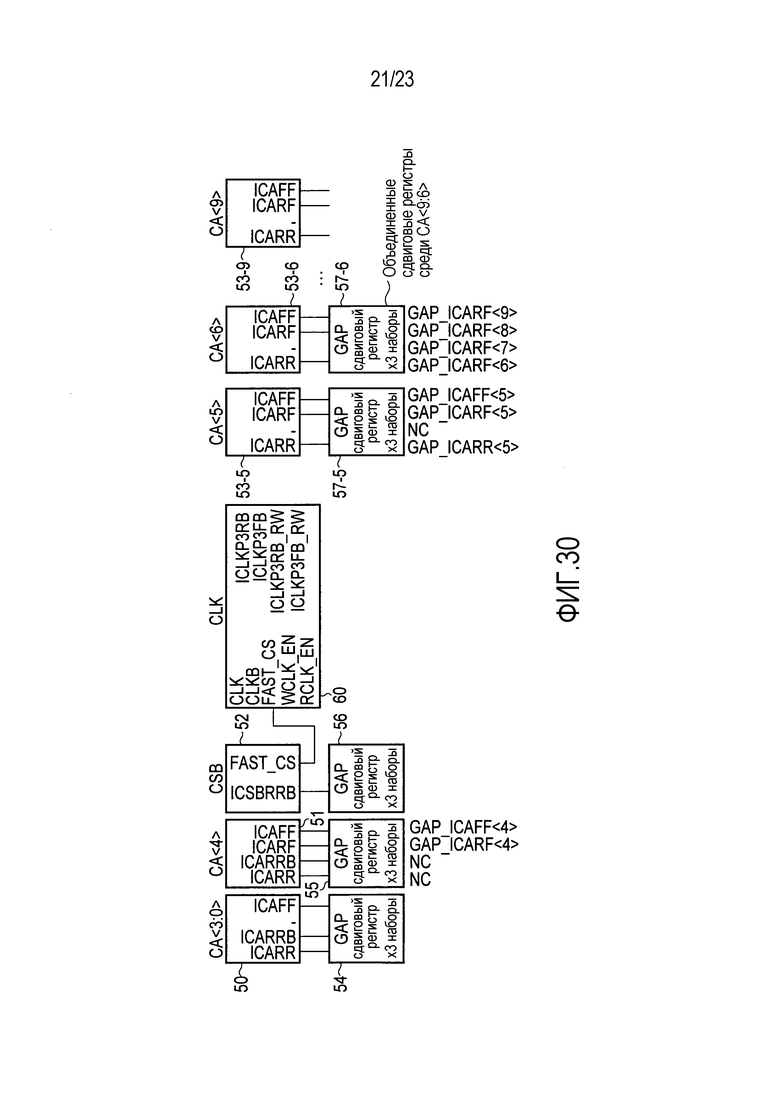

Фиг. 30 представляет собой блок-схему, показывающую компоновку сдвиговых регистров в соответствии с одним примером;

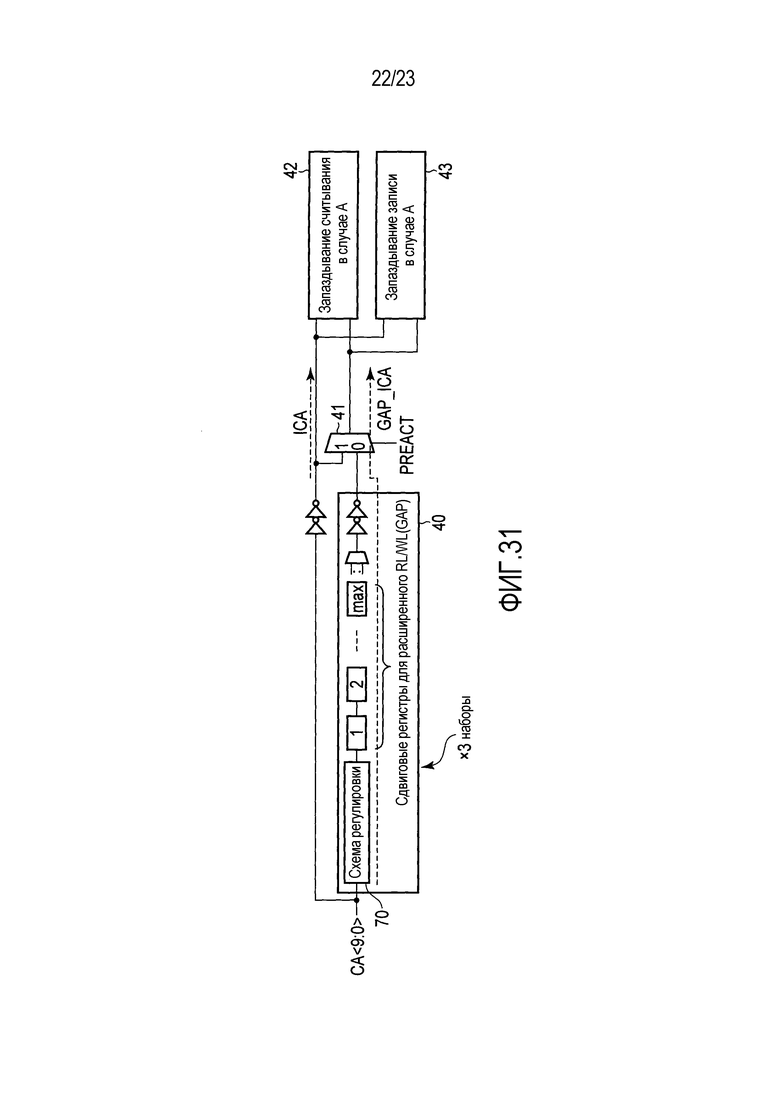

Фиг. 31 представляет собой принципиальную схему для схемы задержки в соответствии с третьим вариантом осуществления и

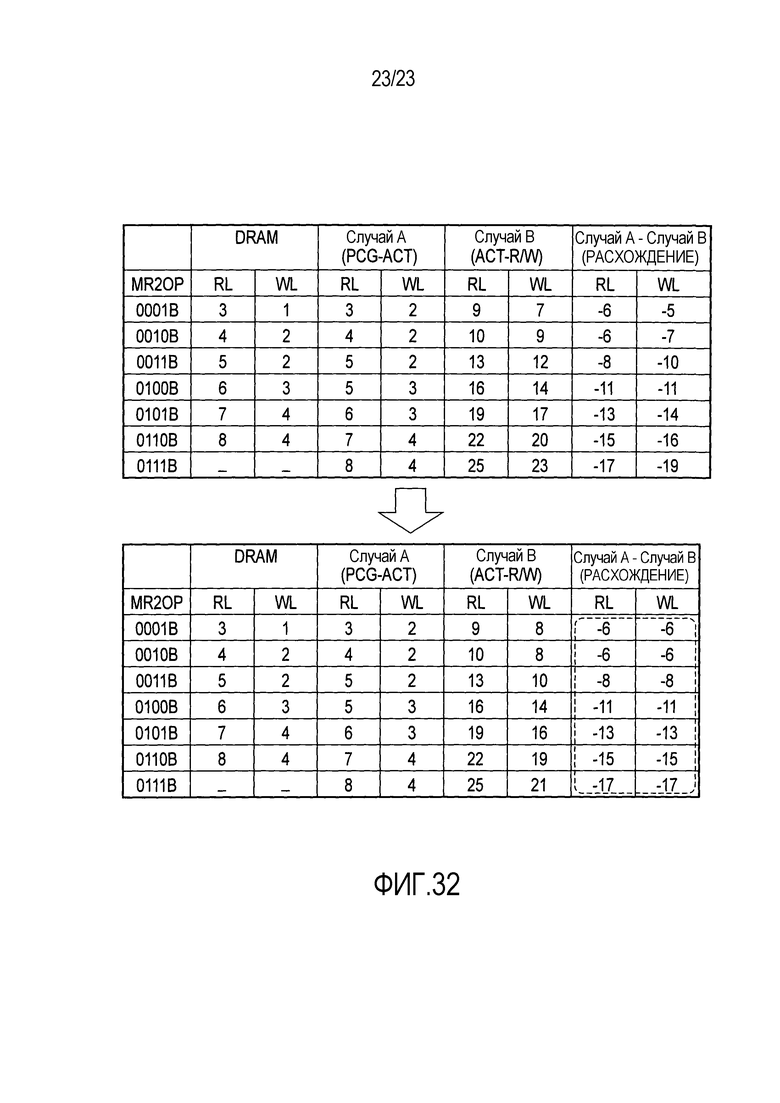

Фиг. 32 представляет собой вид, поясняющий запаздывания в соответствии с четвертым вариантом осуществления.

Осуществление изобретения

В целом, в соответствии с одним вариантом осуществления, предложено полупроводниковое запоминающее устройство, способное исполнять первый режим с первым запаздыванием и второй режим со вторым запаздыванием, большим, чем первое запаздывание, содержащее:

блок контактных площадок, выполненный с возможностью принимать извне адрес и команду;

первую схему задержки, выполненную с возможностью задерживать адрес на время, соответствующее первому запаздыванию;

вторую схему задержки, включающую в себя сдвиговые регистры, соединенные последовательно и выполненные с возможностью задерживать адрес на время, соответствующее разнице между первым запаздыванием и вторым запаздыванием; и

контроллер, выполненный с возможностью использовать первую схему задержки и вторую схему задержки при исполнении второго режима.

Варианты осуществления настоящего изобретения будут описаны далее со ссылкой на сопроводительные чертежи. Следует отметить, что в дальнейшем пояснении одинаковые ссылочные позиции обозначают элементы, имеющие одинаковые функции и компоновки, и повторное пояснение будет приводиться только при необходимости.

В этом варианте осуществления MRAM (магниторезистивная оперативная память) будет служить примером полупроводникового запоминающего устройства.

[Первый вариант осуществления]

[1. Общая компоновка полупроводникового запоминающего устройства]

Фиг. 1 представляет собой схематический вид полупроводникового запоминающего устройства 10 в соответствии с этим вариантом осуществления. Полупроводниковое запоминающее устройство 10 включает в себя сердечник 11 памяти, периферийную схему 12 и интерфейс 13.

Сердечник 11 памяти включает в себя множество ячеек памяти, выполненных с возможностью хранить данные. Периферийная схема 12 осуществляет запись/считывание данных на/из сердечника 11 памяти.

Интерфейс 13 включает в себя блок 14 контактных площадок, выполненный с возможностью принимать команды, адреса, данные и т.п. Блок 14 контактных площадок включает в себя множество контактных площадок. Интерфейс 13 принимает управляющий сигнал CNT для считывания/записи и тактовый сигнал CK, который управляет временем операций считывания/записи, от внешнего устройства (хоста) через блок 14 контактных площадок. Интерфейс 13 соединен с хостом через блок 14 контактных площадок линией CA<n:0> передачи команд/адресов и линией DQ<m:0> передачи данных, где n и m - натуральные числа.

Управляющий сигнал CNT включает в себя тактовый разрешающий сигнал CKE и сигнал CS выбора чипа. Тактовый сигнал CK используются для управления временем операций полупроводникового запоминающего устройства 10. Линия CA<n:0> передачи команд/адресов используется для передачи/приема команд и адресов. Линия DQ<m:0> передачи данных используется для передачи/приема входных данных и выходных данных.

Фиг. 2 представляет собой блок-схему, показывающую пример сердечника 11 памяти и периферийной схемы 12. Сердечник 11 памяти включает в себя блок 21 массива ячеек памяти, декодер 22 строки и декодер 23 столбца. Блок 21 массива ячеек памяти включает в себя (k+1) блоков BK0-BKk памяти, где k - натуральное число. Блоки BK0-BKk памяти можно активировать независимо. Например, когда только необходимый блок памяти активирован во время считывания/записи, потребляемая мощность может быть снижена.

Декодер 22 строки декодирует, например, адрес BA<x:0> блока памяти, что приводит к выбору одного из блоков BK0-BKk памяти, и адрес AR<y:0> строки, что приводит к выбору строки в выбранном блоке памяти.

Декодер 23 столбца декодирует, например, адрес AC<z:0> столбца, что приводит к выбору столбца в блоке 21 массива ячеек памяти.

Периферийная схема 12 включает в себя схему-защелку 24 команды/адреса, управляющую схему (контроллер) 25, схему-защелку 26 адреса, схему-защелку 27 данных и тактовый генератор 28.

Схема-защелка 24 команды/адреса принимает команду CMD и адрес ADD от хоста 15 через линию CA<n:0> передачи команд/адресов и временно сохраняет их. Команда CMD отправляется на управляющую схему 25. Управляющая схема 25 управляет внутренней работой полупроводникового запоминающего устройства 10 на основе управляющего сигнала CNT и команды CMD от хоста 15.

Помимо адреса ADD, адрес BA<x:0> блока памяти отправляется декодеру 22 строки, адрес AR<y:0> строки отправляется схеме-защелке 26 адреса, и адрес AC<z:0> столбца отправляется декодеру 23 столбца.

В этом варианте осуществления, когда вводится первая команда (например, команда активации), схема-защелка 26 адреса фиксирует часть полного адреса строки, как будет описано ниже. Оставшаяся часть полного адреса строки фиксируется схемой-защелкой 26 адреса заранее, когда первая команда (например, команда предварительной зарядки) вводится перед тем, как первая команда была введена.

Как описано выше, часть адреса строки вводится заранее перед вводом первой команды. Это делает возможным, например, объединять полупроводниковое запоминающее устройство с системой без увеличения количества выводов или уменьшения скорости работы, т.е. без изменения спецификаций, даже когда увеличивается количество битов адреса строки для выбора линии слов (строки) в блоке 21 массива ячеек памяти.

Следует отметить, что команда предварительной зарядки представляет собой команду на установку выбранного блока памяти в начальное состояние (состояние предварительной зарядки) для операции считывания или операции записи и, более конкретно, на деактивацию всех линий слов, всех линий битов и всех исходных линий. Команда активации представляет собой команду на активацию одной из множества линий слов в выбранном блоке памяти и выполнение обработки данных считывания данных из массива ячеек памяти.

Схема-защелка 27 данных временно сохраняет данные, введенные от хоста 15 через линию DQ<m:0> передачи данных, или выходные данные, считанные из выбранного блока памяти. Входные данные записываются в выбранный блок памяти.

Тактовый генератор 28 генерирует внутренний тактовый сигнал CLK, основываясь на тактовом сигнале CK от хоста 15. Внутренний тактовый сигнал CLK вводится в схему-защелку 24 команды/адреса, управляющую схему 25, схему-защелку 26 адреса и схему-защелку 27 данных и используется для управления временем их работы.

Фиг. 3 представляет собой принципиальную схему массива ячеек памяти, включенных в один блок памяти. Массив ячеек памяти формируется путем расположения множества ячеек MC памяти в виде матрицы. Множество линий WL0-WLi-1 слов, множество линий BL0-BLj-1 битов и множество исходных линий SL0-SLj-1 расположены в массиве ячеек памяти. Одна строка массива ячеек памяти соединена с одной линией WL слов. Один столбец массива ячеек памяти соединен с каждой парой из линии BL битов и исходной линии SL.

Ячейка MC памяти включает в себя магниторезистивный элемент (элемент MTJ (элемент, основанный на магнитных туннельных переходах)) 30 и выбранный транзистор 31. Выбранный транзистор 31 выполнен, например, в виде полевого МОП-транзистора с каналом n-типа (n-MOSFET).

Один вывод элемента 30 MTJ соединен с линией BL битов, а другой вывод соединен со стоком выбранного транзистора 31. Затвор выбранного транзистора 31 соединен с линией WL слов, а исток соединен с исходной линией SL.

[2. Запаздывание считывания/записи]

Фиг. 4 представляет собой временную диаграмму, касающуюся команд и адресов. Фиг. 4 иллюстрирует временные диаграммы обычных полупроводниковых запоминающих устройств (например, DRAM, MRAM (случай А) и MRAM (случай B)). PCG представляет собой команду предварительной зарядки, ACT - команду активации, R/W - команду считывания/записи, tRCD (RAS к задержке CAS) - время задержки с момента приема команды активации до момента приема команды считывания/записи, RAS - строб адреса строки, CAS - строб адреса столбца и RL/WL - запаздывание считывания/записи. Запаздывание считывания представляет собой время, необходимое для появления считанных данных в локальном интерфейсе после начала запроса считывания. Запаздывание записи представляет собой время, необходимое для появления записанных данных в локальном интерфейсе после начала запроса записи. iR/iW обозначает операцию считывания/записи (внутренняя операция считывания/записи) в MRAM.

В DRAM, показанной на Фиг. 4, адрес R строки содержит, например, 17 битов (R<16:0>). Адрес R<16:0> строки вводится вместе с командой активации и устанавливается в DRAM.

В MRAM (случай А), показанной на Фиг. 4, адрес R строки содержит, например, 18 битов (R<17:0>). MRAM имеет больший размер страницы по сравнению, например, с DRAM. По этой причине адрес строки разделен (например, разделен на старшие биты R<17:14> и младшие биты R<13:0>) и вводится в два этапа. Операция предварительной зарядки характеризуется нарастающим фронтом тактового сигнала, когда вводится команда предварительной зарядки, а операция предварительной активации характеризуется спадающим фронтом. Другими словами, команда предварительной зарядки может установить операцию предварительной зарядки и операцию предварительной активации. В операции предварительной активации старший адрес R<17:14> строки вводится и устанавливается в MRAM. В дополнение, операция активации характеризуется нарастающим фронтом и спадающим фронтом тактового сигнала, когда вводится команда активации. В операции активации младший адрес R<13:0> строки вводится и устанавливается в MRAM.

В MRAM (случай В), показанной на Фиг. 4, операция активации характеризуется нарастающим фронтом и спадающим фронтом тактового сигнала, когда вводится команда активации. В операции активации младший адрес R<13:0> строки вводится и устанавливается в MRAM. В дополнение, операция считывания/записи характеризуется нарастающим фронтом тактового сигнала, когда вводится команда считывания/записи, а операция постактивации характеризуется спадающим фронтом. Другими словами, команда считывания/записи может установить операцию считывания/записи и операцию постактивации. В операции постактивации в MRAM вводится и устанавливается старший адрес R<17:14> строки.

Фиг. 5 представляет собой вид, показывающий пример запаздывания считывания и запаздывания записи. На Фиг. 5 показаны запаздывания в множестве режимов (именуемых как режим MR2OP). DRAM соответствует JEDEC. Единицей запаздывания является один тактовый цикл (1 tCK). Запаздывание MRAM (случай В) получается добавлением внутреннего tRCD MRAM (случай В) к запаздыванию MRAM (случай А).

Фиг. 6 представляет собой вид, поясняющий пример количества сдвиговых регистров для запаздывания. Запаздывание RL считывания в случае А составляет, например, 3 tCK, а запаздывание WL записи составляет, например, 4 tCK. В случае А, например, нужно 2 набора множества сдвиговых регистров для запаздывания считывания и, например, пять наборов множества сдвиговых регистров для запаздывания записи.

В случае В запаздывание RL считывания составляет, например, 25 tCK, а запаздывание WL записи составляет, например, 23 tCK. В случае В сдвиговые регистры, соответствующие внутреннему tRCD, добавляются в каждое из запаздывания считывания и запаздывания записи. По этой причине случай В требует множества сдвиговых регистров для внутреннего tRCD в дополнение к таким же наборам сдвиговых регистров, как и в случае А.

Фиг. 7 представляет собой принципиальную схему для схемы 40 задержки для обеспечения запаздывания. Схема 40 задержки включает в себя входной вывод IN, множество сдвиговых регистров, выполненных с возможностью задержки сигнала на предопределенное время, мультиплексор MUX, буфер BF и выходной вывод OUT. Один сдвиговый регистр задерживает сигнал, например, на 1 тактовый цикл (1 tCK). В схеме 40 задержки выполнено множество сдвиговых регистров, соответствующее максимальному времени задержки. Мультиплексор MUX выбирает предопределенное количество сдвиговых регистров, которые должны быть использованы в соответствии с временем задержки линии передачи сигналов, с которой соединена схема 40 задержки.

Фиг. 8 представляет собой вид, поясняющий сдвиговые регистры для запаздывания в случае В. Следует отметить, что Фиг. 8 иллюстрирует сдвиговые регистры, соответствующие дополнительному увеличению по сравнению с исходными сдвиговыми регистрами (схема задержки). В блоке WL_CTRL управления запаздыванием записи выполнено пять наборов сдвиговых регистров. В блоке RL_CTRL управления запаздыванием считывания выполнено два набора сдвиговых регистров. Вдобавок, для множества сигналов, связанных со столбцами, обеспечено множество наборов сдвиговых регистров, выполненных с возможностью задерживать сигнал на время, соответствующее внутреннему tRCD. Как показано на Фиг. 8, случай В требует больше сдвиговых регистров в дополнение к исходным сдвиговым регистрам (схема задержки).

[3. Пример]

Фиг. 9 представляет собой вид, поясняющий расхождение запаздываний между случаем А и случаем В. Расхождение запаздываний между случаем А и случаем В получается вычитанием запаздывания в случае В из запаздывания в случае А. Другими словами, расхождение запаздываний между случаем А и случаем В соответствует внутреннему tRCD для случая В.

Фиг. 10 представляет собой вид, поясняющий идею этого варианта осуществления. Два канала ICA и GAP_ICA выполнены между контактной площадкой CA<9:0> команды/адреса и схемой 42 задержки запаздывания считывания в случае А.

Схема 40 задержки для обеспечения расхождения запаздываний, показанная на Фиг. 9, соединена с каналом GAP_ICA через мультиплексор MUX. Оба канала ICA и GAP_ICA соединены с мультиплексором MUX. Сигнал PREACT вводится в управляющий вывод мультиплексора MUX. Сигнал PREACT=H соответствует случаю А (операция предварительной активации), а сигнал PREACT=L соответствует случаю В (операция постактивации). В примере, показанном на Фиг. 9, максимальное количество сдвиговых регистров в одном наборе равно 19.

В случае А (PREACT=H) схема 40 задержки не соединена с каналом GAP_ICA, и расхождение запаздываний не добавляется (запаздывание установлено таким же, как и в канале ICA). В случае В (PREACT=L) схема 40 задержки соединена с каналом GAP_ICA, и добавляется расхождение запаздываний. Следует отметить, что схема 43 задержки запаздывания записи имеет такую же компоновку, как и схема 42 задержки запаздывания считывания.

Фиг. 11 представляет собой временную диаграмму, показывающую операцию переключения от считывания к записи в соответствии со сравнительным примером. Команды на Фиг. 11 поясняются следующим образом: А -команда активации, R - команда считывания, а W - команда записи. tWR представляет собой время восстановления записи. В этом сравнительном примере операция считывания и операция записи осуществляются раздельно.

R2W представляет собой время от команды считывания до команды записи и задается как

R2W=RL+tDQSCK+BL/2+1,

где RL - запаздывание считывания, BL - длина пакета данных, а tDQSCK - время доступа выходного DQS (строба данных) от CLK.

Фиг. 12 представляет собой временную диаграмму, показывающую операцию переключения от записи к считыванию в соответствии со сравнительным примером. W2R представляет собой время от команды записи до команды считывания и задается как

W2R=WL+1+BL/2+tWTR/tCK,

где WL - запаздывание записи, tWTR - внутренняя задержка команды переключения от записи к считыванию, tCK - тактовый цикл.

Фиг. 13 представляет собой временную диаграмму, показывающую операцию переключения от считывания к записи в соответствии с одним примером. В этом примере операция считывания и операция записи могут осуществляться параллельно. R2W задается как

R2W=RL-{WL-(BL/2+1)-tDQSCKmax/tCK}...(1)

Фиг. 14 представляет собой временную диаграмму, показывающую операцию переключения от записи к считыванию в соответствии с одним примером. W2R задается как

W2R=WL(@case A)+1+BL/2+tWTR/tCK...(2)

Сигнал, связанный со столбцом, используется как в операции считывания, так в и операции записи. В этом сравнительном примере, так как операция считывания и операция записи осуществляются раздельно, запаздывание считывания и запаздывание записи подвергаются операции «ИЛИ». С другой стороны, когда необходимо большое запаздывание, при котором запаздывание считывания и запаздывание записи перекрываются, как в этом примере, чтобы главным образом использовать управление расхождением запаздываний при считывании и записи, сигнал WTRDB, характеризующий состояние считывания и записи, также используется для управления схемой 40 задержки. В состоянии записи (операции записи) сигнал WTRDB установлен на высокий уровень. В состоянии считывания (операции считывания) сигнал WTRDB установлен на низкий уровень.

Фиг. 15 представляет собой вид, поясняющий R2W и W2R в множестве режимов. GAP_RL представляет собой значение, получаемое вычитанием RL в случае А из RL в случае В. GAP_WL представляет собой значение, получаемое вычитанием WL в случае А из WL в случае В.

Фиг. 16 представляет собой вид, поясняющий параметры tDQSCKmax/tCK и tWTR, когда меняется тактовый цикл tCK. Например, BL=4, а tCK=1,875. R2W вычисляется с использованием уравнения (1), а W2R вычисляется с использованием уравнения (2).

Фиг. 17 представляет собой вид, поясняющий минимальное (min) и максимальное (max) времена задержки сигнала WTRDB. Смещение (OFFSET), min и max задаются как

OFFSET=W2R-(|GAP_WL|-|GAP_RL|);

min=|GAP_RL|-OFFSET+1;

max=|GAP_RL|-1.

Чтобы получить min, расстояние от max вычисляется для нахождения min. Сигнал WTRDB формируется на основе сигнала считывания. По этой причине W2R является таким же, как в состоянии записи в вертикальном направлении. Так как GAP_RL и GAP_WL различны, разность вычитается из W2R. Значение смещения вычитается из GAP_RL, выступающего в качестве опорного значения. В этом случае значение равно +1, потому что GAP_RL также включено.

Чтобы получить max, когда выбрано состояние считывания, так как сигнал WTRDB формируется на основе сигнала считывания, было обнаружено, что запаздывание W2R совпадает с циклом сигнала WTRDB. По этой причине max равно |GAP_RL|. Тем не менее, это значение равно -1, принимая во внимание время передачи внутреннего сигнала.

Фиг. 18 представляет собой вид, поясняющий время задержки сигнала WTRDB. На Фиг. 18 абсцисса обозначает интервал команды, а ордината обозначает расхождение запаздываний (количество сдвиговых регистров). Время задержки сигнала WTRDB из опорного значения установлено в пределах диапазона между min и max на Фиг. 18. Это делает возможным обычное использование сигнала WTRDB в операции считывания и в операции записи за счет управления схемой 40 задержки для обеспечения расхождения, используя задержанный сигнал WTRDB, даже когда перекрываются запаздывание считывания и запаздывание записи.

[4. Пример схемной компоновки]

Далее будет описан подробный пример схемной компоновки. Фиг. 19 представляет собой блок-схему, показывающую пример схемной компоновки, включающей в себя сдвиговые регистры расхождения. NC на Фиг. 19 указывает на отсутствие соединения.

Схема-защелка 50 фиксирует сигнал от контактной площадки CA<3:0> команды/адреса. Схема-защелка 51 фиксирует сигнал от контактной площадки CA<4> команды/адреса. Схема-защелка 52 фиксирует сигнал выбора чипа от контактной площадки CSB выбора чипа. Схема-защелка 53 фиксирует сигнал от контактной площадки CA<9:5> команды/адреса. Выходы из схем-защелок 50-53 соединены с вводами схем 54-57 задержки расхождения соответственно. Сигналы ICARR, ICARF и ICAFF представляют собой сигналы, вводимые с соответствующих контактных площадок. Различны только времена, при которых схемами-защелками принимаются эти сигналы. Сигнал ICARRB представляет собой инвертированный сигнал от сигнала ICARR.

Декодер 58 команды декодирует команду записи и команду считывания, введенные из схемы-защелки 50, и генерирует сигналы EWT и ERT. Декодер 58 команды также декодирует команду записи и команду считывания, введенные из схемы 54 задержки расхождения, и генерирует сигналы GAP_EWT и GAP_ERT. Схема 59 генерации сигналов принимает сигналы от декодера 58 команды и генерирует сигналы WCLK_EN, RCLK_EN и FAST_WTRDB. Сигнал FAST_WTRDB генерируется с использованием сигналов EWT и ERT. Сигнал WCLK_EN генерируется с использованием сигнала GAP_EWT. Сигнал RCLK_EN генерируется с использованием сигнала GAP_ERT.

Тактовый генератор 60 генерирует различные виды тактовых сигналов. Фиг. 20 представляет собой принципиальную схему тактового генератора 60. Как показано на Фиг. 20, сигналы WCLK_EN и RCLK_EN подвергаются операции «ИЛИ» для получения сигнала EN_RW_CLK. Тактовый сигнал CLK и сигнал FAST_CS подвергаются операции «И» для получения тактового сигнала ICLKP3RB. Тактовый сигнал CLK и сигнал EN_RW_CLK подвергаются операции «И» для получения тактового сигнала ICLKP3RB_RW.

Схема 61 генерации сигналов принимает тактовые сигналы ICLKP3RB и ICLKP3FB и сигнал FAST_WTRDB и генерирует сигнал GAP_WTRDB. Схема 62 задержки расхождения принимает сигнал IMR2OPB<7:1> режима и сигнал GAP_WTRDB и генерирует сигнал CTRL, задерживая сигнал GAP_WTRDB на предопределенное время в соответствии с сигналом IMR2OPB<7:1> режима. Время, на которое задерживается сигнал GAP_WTRDB, определяется на основании Фиг. 18. Схема 62 задержки расхождения сформирована из множества сдвиговых регистров, соединенных последовательно.

Следует отметить, что на Фиг. 19 схемы-защелки 50-53 и схемы 54-57 задержки расхождения включены, например, в интерфейс 13, показанный на Фиг. 1. Декодер 58 команды, схемы 59 и 61 генерации сигналов и схема 62 задержки расхождения включены, например, в управляющую схему 25, показанную на Фиг. 2. Тактовый генератор 60 включен, например, в тактовый генератор 28, показанный на Фиг. 2.

Фиг. 21 представляет собой принципиальную схему для схемы 54 задержки расхождения, показанной на Фиг. 19. Схема 54 задержки расхождения включает в себя три набора сдвиговых регистров. Каждый набор имеет такую же компоновку, как и в основной схеме 40 задержки, показанной на Фиг. 7. Каждый набор включает в себя столько сдвиговых регистров, каково максимальное число расхождений. Схемы 55-57 задержки расхождения также имеют такую же компоновку, как и схема 54 задержки расхождения.

Фиг. 22 представляет собой вид, поясняющий назначение ICA для сигнала, связанного со строкой. Фиг. 23 представляет собой вид, поясняющий назначение ICA для сигнала, связанного со столбцом. CMD является командой, а MR - регистром режима. OP<7:0> MRW сигнала указывает опцию записи регистра режима. С1 является сигналом, используемым для изменения порядка сигналов.

Как и сигнал, связанный со строкой на Фиг. 22, сигнал контактной площадки <9:0> команды/адреса используется без использования сдвиговых регистров расхождения. Сигнал, связанный со столбцом, показанный на Фиг. 23, представляет собой сигнал, задержанный на время задержки сдвиговых регистров расхождения. Как описано выше, в этом варианте осуществления операцией в отношении сигнала, связанного со строкой, управляют с использованием исходного сигнала (сигнала, который не прошел через схему задержки расхождения). С другой стороны, операцией в отношении сигнала, связанного со столбцом, управляют с использованием сигнала, задержанного схемой задержки расхождения.

Фиг. 24 представляет собой вид, поясняющий последовательность операций в соответствии с одним примером. Фиг. 24 иллюстрирует один набор схемы 40 задержки, содержащейся в схеме 54 или 55 задержки расхождения.

Когда сигнал FAST_CS утверждается, тактовый генератор 60 генерирует тактовые сигналы ICLKP3RB и ICLKP3FB (этап S1). Сигнал FAST_CS утверждается, когда сигнал CSB выбора чипа утвержден. Сдвиговые регистры SR1 и SR2 функционируют в соответствии с тактовыми сигналами ICLKP3RB и ICLKP3FB и задерживают сигнал СА на 2 tCK (этап S2).

Далее декодер 58 команды декодирует команду (этап S3). Схема 59 генерации сигналов генерирует сигналы WCLK_EN, RCLK_EN и FAST_WTRDB (этап S4). Сигнал WCLK_EN утвержден, когда сигнал GAP_EWT утвержден. Сигнал RCLK_EN утвержден, когда сигнал RCLK_EN утвержден. Далее тактовый генератор 60 генерирует тактовые сигналы ICLKP3RB_RW и ICLKP3FB_RW, когда сигнал WCLK_EN или RCLK_EN утвержден (этап S5).

Сдвиговые регистры SR3-SR21 функционируют в соответствии с тактовыми сигналами ICLKP3RB_RW и ICLKP3FB_RW и задерживают сигнал на предопределенное время (этап S6). В этом варианте осуществления два вида тактовых сигналов ICLKP3RB и ICLKP3RB_RW подаются в схему 40 задержки. Сдвиговые регистры SR3-SR21 осуществляют функционирование перед сдвиговыми регистрами SR1 и SR2. Это делает возможным обеспечить запас времени настройки сдвигового регистра SR1 на первом каскаде.

После этого схема 62 задержки расхождения генерирует CTRL (этап S7). Мультиплексор MUX активирует канал запаздывания расхождения, созданного сдвиговыми регистрами SR1-SR21, когда утвержден сигнал CTRL. Мультиплексор 41 выбирает канал мультиплексора MUX, когда сигнал PREACT=L (случай B). Мультиплексор 41 выводит через буфер сигнал GAP_CA, запаздывание для которого добавлено сдвиговыми регистрами расхождения.

[5. Схемное расположение сдвиговых регистров]

Далее будет описан пример компоновки в отношении схемного расположения сдвиговых регистров расхождения, когда спецификации обоих случаев А и В реализованы в полупроводниковом запоминающем устройстве 10. У случая А и случая В разные запаздывания.

Фиг. 25 представляет собой схематический вид, поясняющий схемное расположение сдвиговых регистров SR согласно сравнительному примеру. Например, сигналы CBANKT и AYP16 отправляются от модуля М1 к модулю М2. Сдвиговые регистры SR расхождения вставлены после асинхронной задержки. Сигнал AYP16 в случае А имеет время задержки, отличное от времени задержки сигнала CBANKT. Разница времен задержки указывает запас времени настройки модуля М2.

Так как сигнал AYP16 в случае В и сигнал CBANKT в случае В отрегулированы тактовым сигналом FCLKD на последнем каскаде модуля М2, потеря, соответствующая расхождению асинхронной задержки, возникает во времени задержки. Следовательно, в модуле М2 запас времени настройки схемы-защелки на первом каскаде снижается.

Фиг. 26 представляет собой схематический вид, поясняющий схемное расположение сдвиговых регистров SR согласно одному примеру. Мультиплексор и сдвиговые регистры расхождения, выполненные с возможностью регулировки запаздываний множества сигналов, ICARR, ICARF и ICAFF, скомпонованы вместе рядом с контактной площадкой CA команды/адреса. Можно управлять сдвиговыми регистрами расхождения, используя тактовый сигнал, отличный от тактового сигнала FCLKD. Это может улучшить запас времени настройки.

[6. Эффекты]

Когда необходимо большое запаздывание, создается опорное запаздывание, и схема задержки (включающая в себя множество сдвиговых регистров), выполненная с возможностью создавать запаздывание, соответствующее расхождению от опорного запаздывания, скомпонована рядом с контактной площадкой СА (каскад перед декодером команды). Это делает возможным уменьшение количества сдвиговых регистров, используемых для запаздывания на всем чипе.

Когда сигнал WTRDB, характеризующий состояние считывания и записи, аналогичным образом задерживается схемой задержки, может обычно использоваться запаздывание, соответствующее расхождению между считыванием и записью. Это делает возможным дальнейшее уменьшение количества сдвиговых регистров, используемых для запаздывания.

[Второй вариант осуществления]

Сначала будет описано назначение команды/адреса. Фиг. 27 представляет собой вид, поясняющий назначение команды/адреса относительно команды активации. Фиг. 28 представляет собой вид, поясняющий назначение команды/адреса относительно команды считывания/записи.

Как показано на Фиг. 27 и Фиг. 28, стрелки в столбце тактового сигнала CLK обозначают нарастающий фронт и спадающий фронт тактового сигнала. CA0-CA9 обозначают команды и адреса, вводимые с контактной площадки команды/адреса (линии передачи команд/адресов). Адрес BA блока памяти, который обозначает некоторый блок памяти, включает в себя, например, 3 бита (BA0-BA2). Адрес R строки включает в себя, например, 18 битов (R0-R17). Из битов R0-R17 полного адреса строки первый адрес строки (часть полного адреса строки), вводимый вместе с командой активации, включает в себя, например, младшие биты R0-R13. Из битов R0-R17 полного адреса строки второй адрес строки (оставшаяся часть полного адреса строки), вводимый вместе с командой считывания/записи, включает в себя, например, старшие биты R14-R17. Адрес С столбца включает в себя, например, 7 битов (C1-C7).

Как показано на Фиг. 27, операция активации характеризуется нарастающим фронтом и спадающим фронтом тактового сигнала CLK, когда введена команда активации. Команда активации утверждает сигнал CS выбора чипа и определяется с использованием CA0=L и CA1=H при нарастающем фронте тактового сигнала CLK. При нарастающем фронте тактового сигнала CLK биты R8-R12 адреса строки вводятся с контактных площадок CA2-CA6, а биты BA0-BA2 адреса блока памяти вводятся с контактных площадок CA7-CA9. При спадающем фронте тактового сигнала CLK биты R0-R7 и R13 адреса строки вводятся с контактных площадок CA0-CA8. "X" обозначает "не важно".

Как показано на Фиг. 28, операция считывания/записи характеризуется нарастающим фронтом тактового сигнала CLK, когда введена команда считывания/записи, а операция постактивации характеризуется спадающим фронтом тактового сигнала CLK. Другими словами, команда считывания/записи может задавать операцию считывания/записи и операцию постактивации. Команда считывания утверждает сигнал CS выбора чипа и определяется с использованием CA0=H, CA1=L и CA2=L при нарастающем фронте тактового сигнала CLK. Команда записи утверждает сигнал CS выбора чипа и определяется с использованием CA0=H, CA1=L и CA2=H при нарастающем фронте тактового сигнала CLK.

В операции считывания/записи биты С1 и С2 адреса столбца вводятся с контактных площадок СА5 и СА6, а биты ВА0-ВА2 адреса блока памяти вводятся с контактных площадок СА7-СА9.

В операции постактивации биты С3-С7 адреса столбца вводятся с контактных площадок СА1-СА7, а старшие биты R14-R17 адреса строки вводятся с контактных площадок СА6-СА9. На Фиг. 28 "RFU" обозначает "зарезервировано для будущего использования", а "AP" - флаг, который определяет предварительную автозарядку.

Фиг. 29 представляет собой блок-схему, показывающую компоновку сдвиговых регистров в соответствии со сравнительным примером. Следует отметить, что Фиг. 29 показывает детали части, относящейся к контактной площадке CA<9:4> команды/адреса.

Схемы 57-5-57-9 задержки соединены со схемами-защелками 53-5-53-9 для контактных площадок CA<5>-CA<9> команды/адреса. В операции считывания/записи каждая из схем 57-5-57-9 задержки обрабатывает только один сигнал, GAP_ICARF.

Фиг. 30 представляет собой блок-схему, показывающую компоновку сдвиговых регистров в соответствии с одним примером. В этом примере схемы задержки для сигнала GAP_ICARF<9:6> объединены среди контактных площадок CA<5>-CA<9> команды/адреса. Объединенная схема 57-6 задержки включает в себя четыре набора сдвиговых регистров для сигнала GAP_ICARF<9:6>.

В соответствии со вторым вариантом осуществления, так как необязательные сдвиговые регистры могут быть устранены, площадь схемы задержки запаздывания может быть уменьшена.

[Третий вариант осуществления]

Когда полупроводниковое запоминающее устройство 10 включает в себя схему выравнивания для запаздывания, причем схему выравнивания нужно включать в каждую схему задержки запаздывания в компоновке сравнительного примера, показанного на Фиг. 8.

Фиг. 31 представляет собой принципиальную схему для схемы 40 задержки в соответствии с третьим вариантом осуществления. Как описано в первом варианте осуществления, схемы 40 задержки для расхождения скомпонованы вместе рядом с контактной площадкой CA<9:0> команды/адреса. Схема 40 задержки включает в себя схему 70 выравнивания. Схема 70 выравнивания обладает функцией настройки характеристик (например, запаздывания) полупроводникового запоминающего устройства 10.

В соответствии с третьим вариантом осуществления, так как множество схем выравнивания не требуется рассредоточивать, число схем выравнивания может быть уменьшено. Поэтому можно уменьшить площадь полупроводникового запоминающего устройства 10.

[Четвертый вариант осуществления]

В четвертом варианте осуществления будет описан способ возврата к внутреннему времени. Как показано на Фиг. 9 и описано в первом варианте осуществления, R2W (время от команды считывания до команды записи) и W2R (время от команды записи до команды считывания) меняются между случаем А и случаем В. Следовательно, время в случаях А-В предпочтительно регулируется в соответствии со случаем А.

В течение случая В R2W (время от команды считывания до команды записи) и W2R (время от команды записи до команды считывания) регулируются следующим образом:

R2W=RL-{WL-(BL/2+1)-tDQSCKmax/tCK}+(|GAP_WL|-|GAP_RL|);

W2R=WL(@case A)+1+BL/2+tWTR/tCK+(|GAP_WL|-|GAP_RL|).

Запаздывания, вычисляемые с помощью этих уравнений, осуществляются с использованием сдвиговых регистров. Это делает возможным осуществление возврата к внутреннему времени в случае В.

В качестве способа возврата к внутреннему времени можно установить одинаковое значение для запаздывания считывания расхождения и запаздывания записи расхождения. Фиг. 32 представляет собой вид, поясняющий запаздывания. Запаздывание GAP_RL считывания расхождения и запаздывание GAP_WL записи расхождения установлены в одинаковое значение. Это устраняет необходимость различать запаздывание расхождения между считыванием и записью. Поэтому можно управлять схемой 40 задержки без использования сигнала WTRDB, характеризующего состояние считывания и записи.

Следует отметить, что MRAM, описанная в вышеуказанных вариантах осуществления, может быть магниторезистивным оперативным запоминающим устройством с технологией переноса спинового момента (STT MRAM).

В вышеуказанных вариантах осуществления MRAM, использующая магниторезистивный элемент, служило примером полупроводникового запоминающего устройства. Тем не менее, настоящее изобретение этим не ограничивается и применимо к различным видам полупроводниковых запоминающих устройств вне зависимости от того, являются ли они энергозависимой памятью или энергонезависимой памятью. Настоящее изобретение также применимо к резистивным запоминающим устройствам, похожим на MRAM, например ReRAM (резистивная память с произвольным доступом) или PCRAM (оперативная память с изменением фазовых состояний).

Хотя были описаны конкретные варианты осуществления, эти варианты осуществления были представлены только в качестве примера и не предназначены для ограничения объема изобретений. В действительности, новые варианты осуществления, описанные в данном документе, могут быть воплощены во множестве других форм; кроме того, различные исключения, замены и изменения в форме вариантов осуществления, описанных в данном документе, могут быть сделаны без отступления от сущности изобретений. Приложенная формула изобретения и ее эквиваленты предназначены для охвата таких форм или модификаций, какие будут подпадать под объем и сущность изобретений.

| название | год | авторы | номер документа |

|---|---|---|---|

| ПОЛУПРОВОДНИКОВОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 2014 |

|

RU2634217C2 |

| ПОЛУПРОВОДНИКОВОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 2014 |

|

RU2643629C2 |

| УСТРОЙСТВО ПАМЯТИ И СПОСОБ УПРАВЛЕНИЯ ИМ | 2016 |

|

RU2669872C1 |

| ПОЛУПРОВОДНИКОВАЯ ПАМЯТЬ | 1993 |

|

RU2156506C2 |

| СОВМЕСТИМОСТЬ ОДНОПРОВОДНОЙ И ТРЕХПРОВОДНОЙ ШИН | 2005 |

|

RU2352980C2 |

| УСТРОЙСТВО ПАМЯТИ И СИСТЕМА ПАМЯТИ | 2015 |

|

RU2682843C1 |

| УСТРОЙСТВА ВЫБРОСА ТЕКУЧЕЙ СРЕДЫ, ВКЛЮЧАЮЩИЕ В СЕБЯ ПЕРВУЮ ПАМЯТЬ И ВТОРУЮ ПАМЯТЬ | 2019 |

|

RU2779068C1 |

| ЭНЕРГОНЕЗАВИСИМОЕ ОПЕРАТИВНОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 2014 |

|

RU2622869C2 |

| Устройство для отображения информации на газоразрядной индикаторной панели | 1989 |

|

SU1675935A1 |

| ПОЛУПРОВОДНИКОВОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 2006 |

|

RU2391722C2 |

Изобретение относится к вычислительной технике. Технический результат заключается в уменьшении количества сдвиговых регистров, используемых для запаздывания. Полупроводниковое запоминающее устройство, способное исполнять первый режим с первым запаздыванием и второй режим со вторым запаздыванием, большим, чем первое запаздывание, содержит блок контактных площадок, выполненный с возможностью принимать извне адрес и команду; первую схему задержки, выполненную с возможностью задерживать адрес на время, соответствующее первому запаздыванию; вторую схему задержки, включающую в себя сдвиговые регистры, соединенные последовательно и выполненные с возможностью задерживать адрес на время, соответствующее разнице между первым запаздыванием и вторым запаздыванием; и контроллер, выполненный с возможностью использовать первую схему задержки и вторую схему задержки при исполнении второго режима, причем первый режим и второй режим являются операциями записи или операциями считывания, и контроллер способен исполнять один из первого режима и второго режима. 11 з.п. ф-лы, 32 ил.

1. Полупроводниковое запоминающее устройство, способное исполнять первый режим с первым запаздыванием и второй режим со вторым запаздыванием, большим, чем первое запаздывание, содержащее:

блок контактных площадок, выполненный с возможностью принимать извне адрес и команду;

первую схему задержки, выполненную с возможностью задерживать адрес на время, соответствующее первому запаздыванию;

вторую схему задержки, включающую в себя сдвиговые регистры, соединенные последовательно и выполненные с возможностью задерживать адрес на время, соответствующее разнице между первым запаздыванием и вторым запаздыванием; и

контроллер, выполненный с возможностью использовать первую схему задержки и вторую схему задержки при исполнении второго режима,

причем первый режим и второй режим являются операциями записи или операциями считывания, и

контроллер способен исполнять один из первого режима и второго режима.

2. Устройство по п. 1, в котором контроллер обходит вторую схему задержки при исполнении первого режима.

3. Устройство по п. 1, дополнительно содержащее:

схему генерации сигналов, выполненную с возможностью генерации управляющего сигнала для идентификации операции считывания в соответствии с командой считывания и операции записи в соответствии с командой записи; и

третью схему задержки, выполненную с возможностью задержки управляющего сигнала на предопределенное время,

при этом контроллер управляет второй схемой задержки с использованием задержанного управляющего сигнала.

4. Устройство по п. 1, дополнительно содержащее тактовый генератор, выполненный с возможностью генерировать первый тактовый сигнал и второй тактовый сигнал, который запускается в более поздний момент времени, чем первый тактовый сигнал,

при этом сдвиговые регистры разделены на предшествующую часть каскада и последующую часть каскада,

упомянутая предшествующая часть каскада начинает операцию в ответ на первый тактовый сигнал и

упомянутая последующая часть каскада начинает операцию в ответ на второй тактовый сигнал.

5. Устройство по п. 4, в котором

первый тактовый сигнал запускается после приема сигнала разрешения чипа и

второй тактовый сигнал запускается после приема одной из команды считывания и команды записи.

6. Устройство по п. 1, в котором

контроллер раздельно управляет адресом строки и адресом столбца,

адрес строки обходит вторую схему задержки и

адрес столбца задерживается второй схемой задержки.

7. Устройство по п. 1, в котором контроллер

управляет операцией с использованием адреса строки, основываясь на команде, введенной в блок контактных площадок, и

управляет операцией с использованием адреса столбца, основываясь на команде, задержанной второй схемой задержки.

8. Устройство по п. 1, в котором

блок контактных площадок содержит первую контактную площадку и вторую контактную площадку и

схема задержки для первой контактной площадки и схема задержки для второй площадки скомпонованы вместе.

9. Устройство по п. 1, в котором

каждое из первого запаздывания и второго запаздывания имеет запаздывание считывания в операции считывания и запаздывание записи в операции записи и

вторая схема задержки устанавливает такое же время задержки, как и запаздывание считывания и запаздывание записи.

10. Устройство по п. 1, в котором вторая схема задержки содержит схему выравнивания.

11. Устройство по п. 1, дополнительно содержащее массив ячеек памяти, выполненный с возможностью хранить данные,

при этом массив ячеек памяти сформирован из MRAM.

12. Устройство по п. 1, при этом полупроводниковое запоминающее устройство содержит магниторезистивное оперативное запоминающее устройство с технологией переноса спинового момента (STT MRAM).

| Приспособление для суммирования отрезков прямых линий | 1923 |

|

SU2010A1 |

| Способ приготовления лака | 1924 |

|

SU2011A1 |

| Изложница с суживающимся книзу сечением и с вертикально перемещающимся днищем | 1924 |

|

SU2012A1 |

| Приспособление для суммирования отрезков прямых линий | 1923 |

|

SU2010A1 |

| Способ приготовления лака | 1924 |

|

SU2011A1 |

| ПОЛУПРОВОДНИКОВАЯ ПАМЯТЬ | 1993 |

|

RU2156506C2 |

Авторы

Даты

2018-01-17—Публикация

2014-07-29—Подача