Перекрестная ссылка на родственные заявки

Данная заявка основана и испрашивает приоритеты предварительной заявки США № 61/870,727, поданной 27 августа 2013 года, и заявки на патент США № 14/201,618, поданной 7 марта 2014 года, содержимое которых полностью включено в данную заявку посредством ссылки.

Область техники, к которой относится изобретение

Варианты осуществления, описанные в данном документе, относятся в целом к полупроводниковому запоминающему устройству.

Уровень техники

MRAM (магниторезистивная оперативная память) представляет собой запоминающее устройство, которое использует магнитный элемент, обладающий магниторезистивным эффектом, в качестве ячейки памяти для хранения информации, и привлекает к себе внимание как энергонезависимое запоминающее устройство следующего поколения, выполненное с возможностью высокоскоростной работы и обладающее большой емкостью. Кроме того, были проведены научные исследования и разработки MRAM для получения памяти, которая заменит энергозависимую память, такую как DRAM или SRAM. В этом случае желательно, чтобы MRAM управлялась с использованием тех же спецификаций, что и DRAM или SRAM, для уменьшения стоимости разработки и обеспечения легкой замены.

Краткое описание чертежей

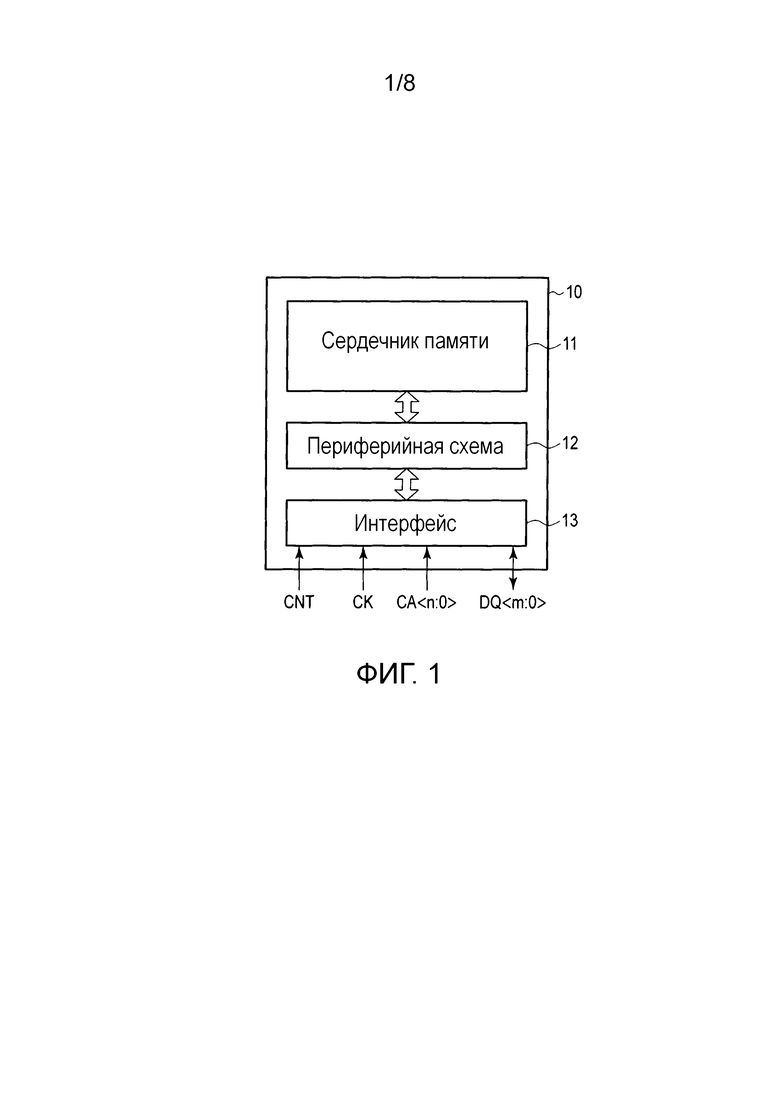

Фиг. 1 представляет собой схематический вид полупроводникового запоминающего устройства согласно одному варианту осуществления;

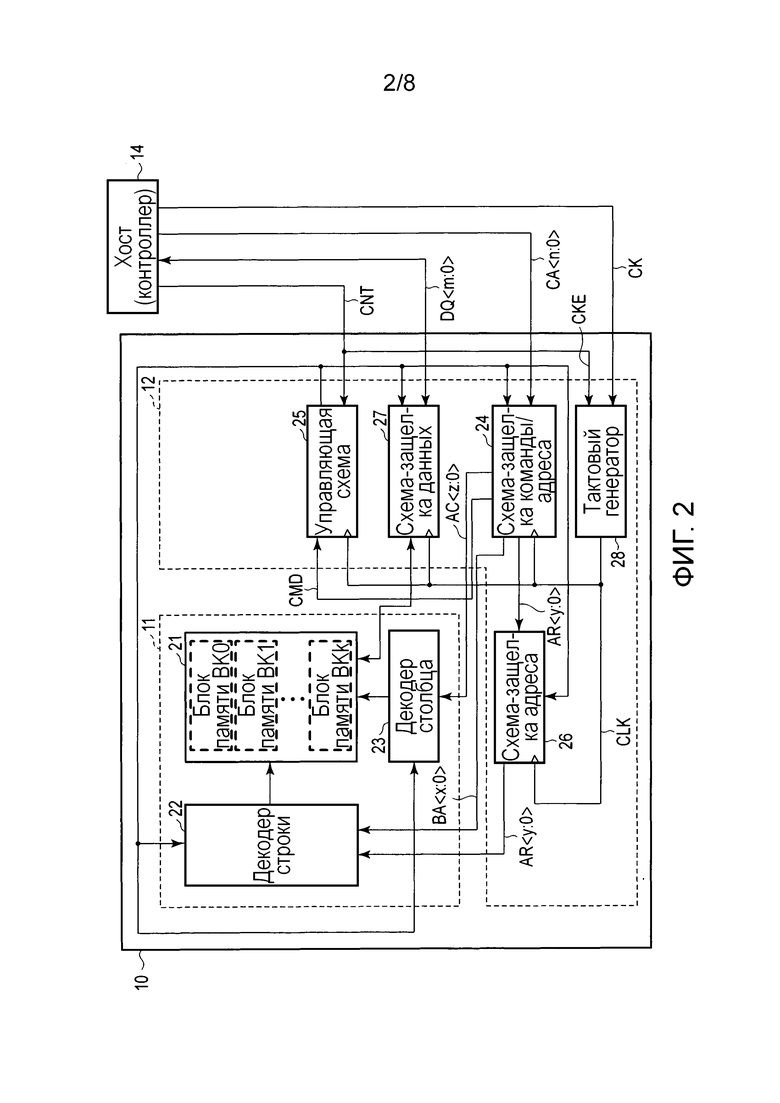

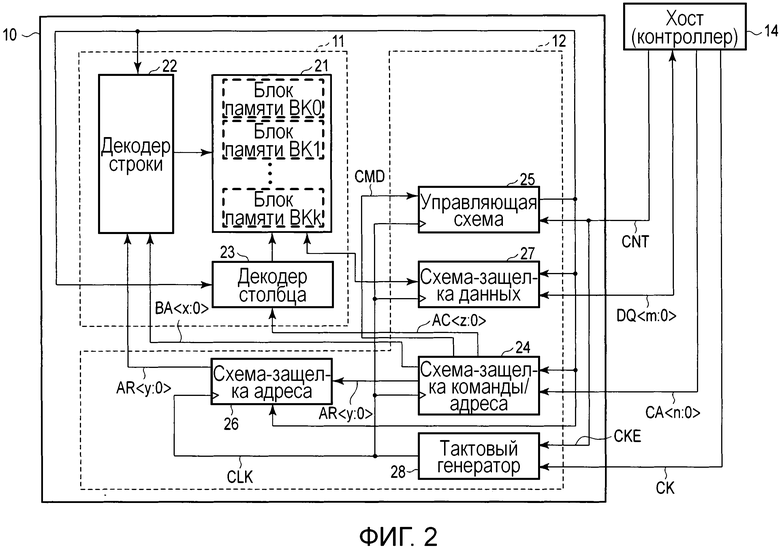

Фиг. 2 представляет собой блок-схему, показывающую примеры сердечника 11 памяти и его периферийной схемы;

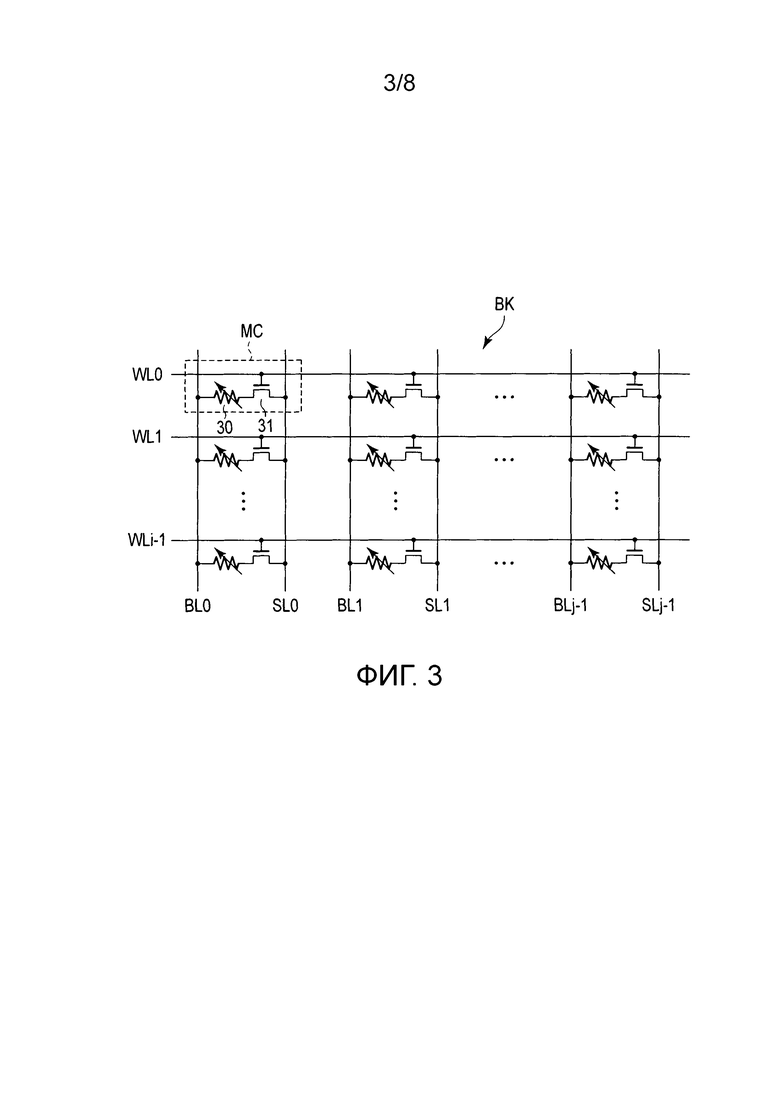

Фиг. 3 представляет собой блок-схему массива ячеек памяти, включенного в один блок памяти;

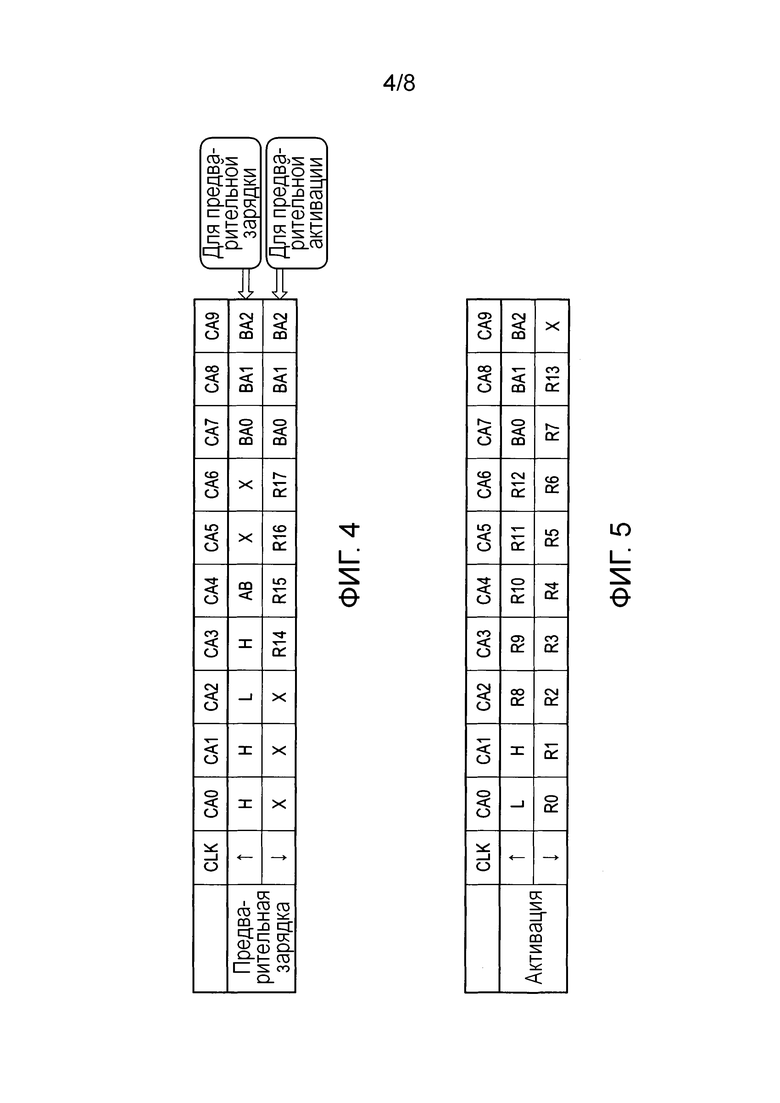

Фиг. 4 представляет собой вид, иллюстрирующий назначение команды/адреса относительно команды предварительной зарядки;

Фиг. 5 представляет собой вид, иллюстрирующий назначение команды/адреса относительно команды активации;

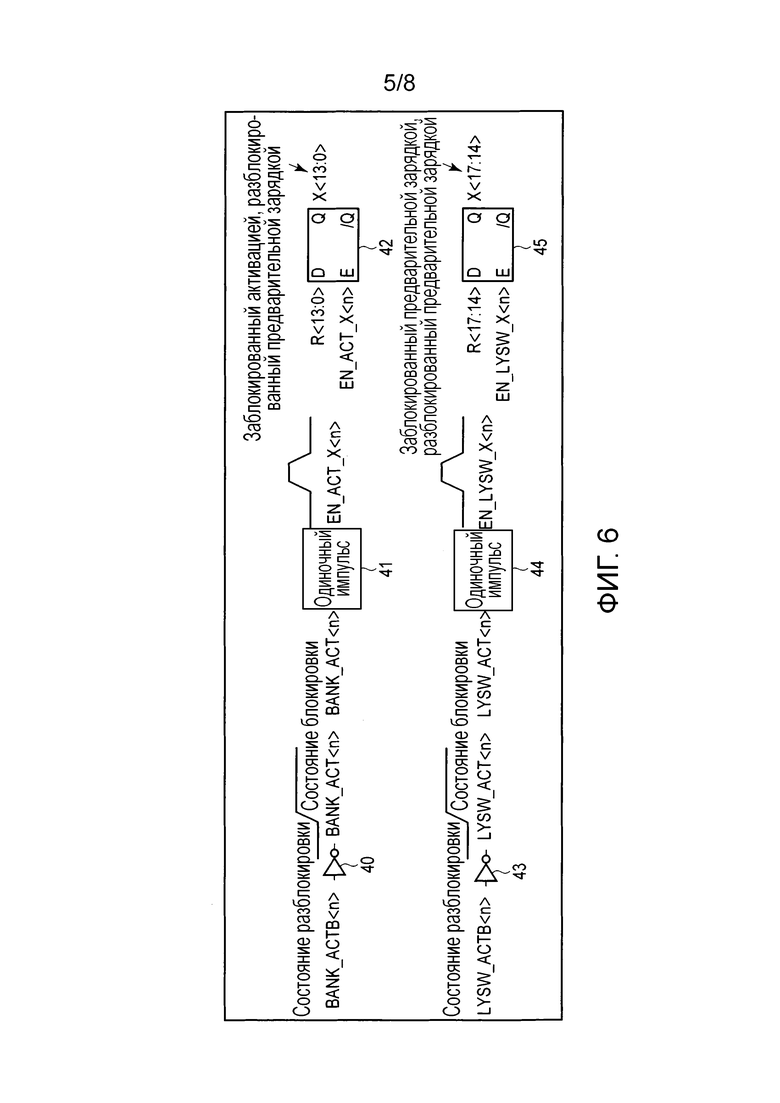

Фиг. 6 представляет собой вид, иллюстрирующий операции согласно сравнительному примеру 1;

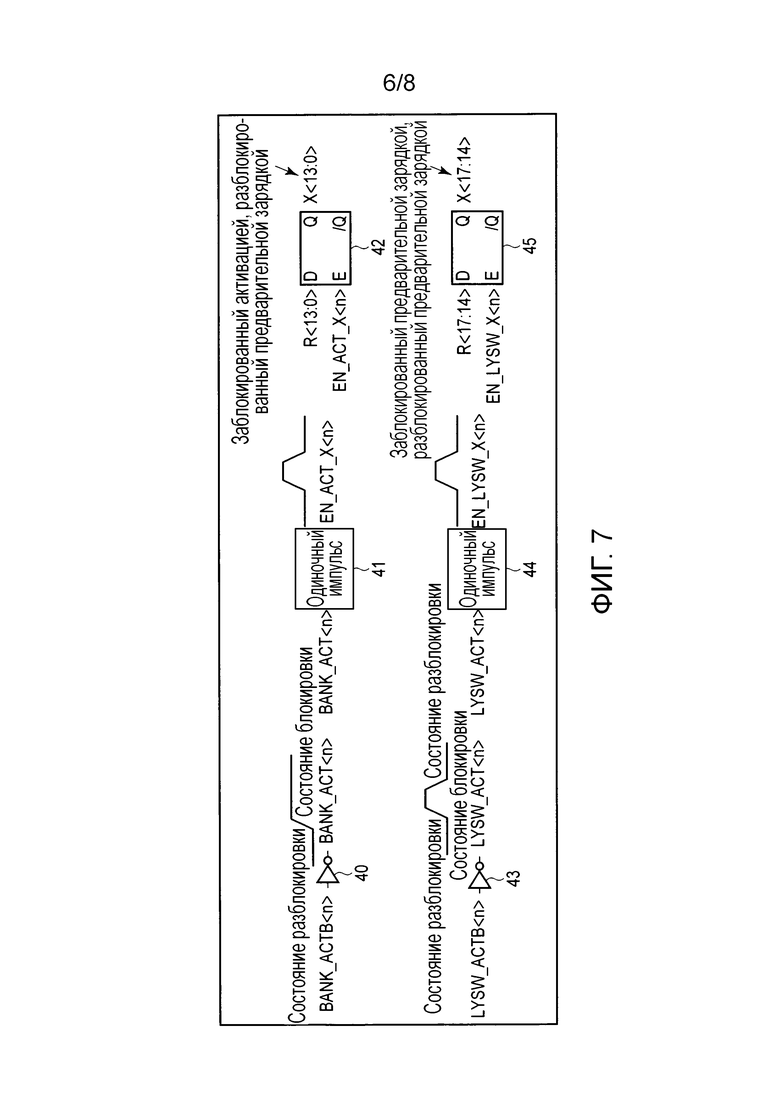

Фиг. 7 представляет собой вид, иллюстрирующий операции согласно сравнительному примеру 2;

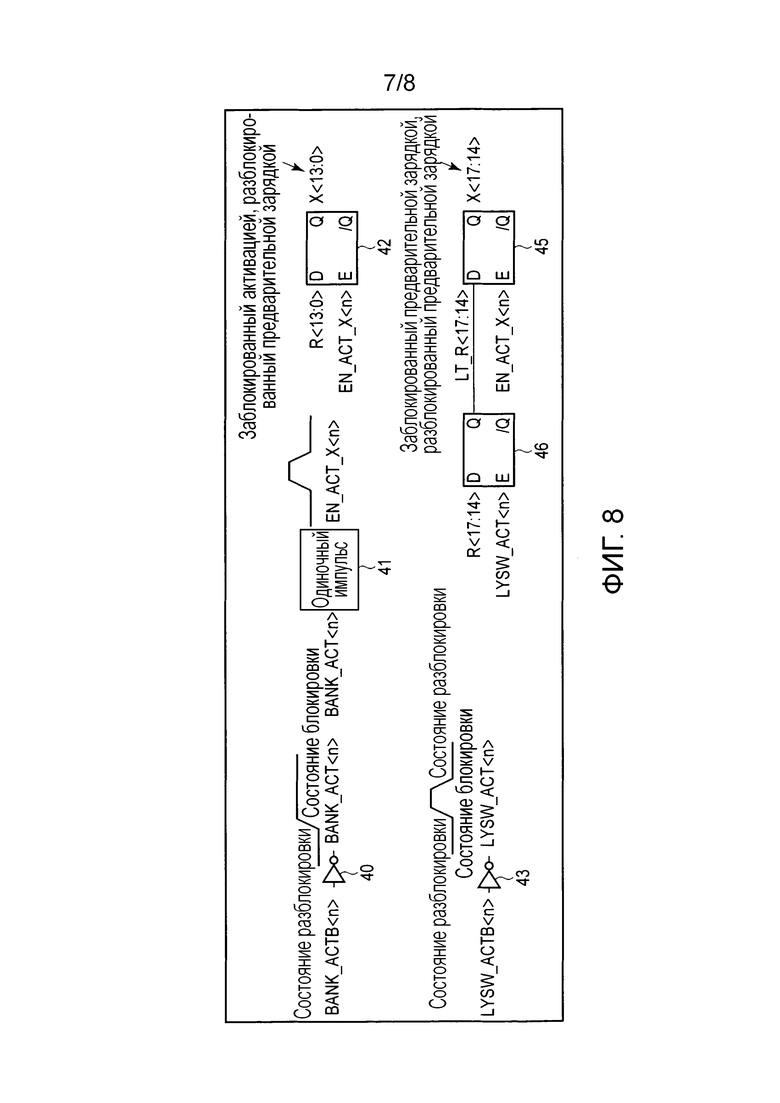

Фиг. 8 представляет собой вид, иллюстрирующий операции согласно одному примеру;

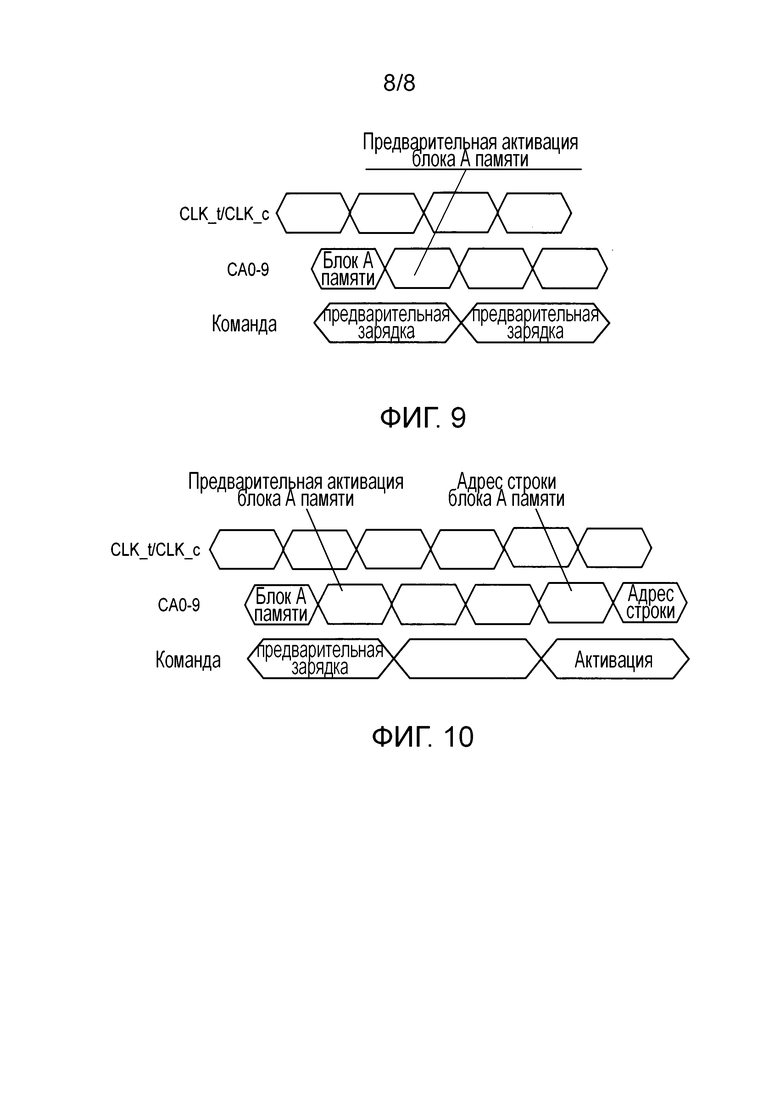

Фиг. 9 представляет собой временную диаграмму согласно одному примеру вводимой команды; и

Фиг. 10 представляет собой временную диаграмму согласно другим примерам вводимой команды.

Осуществление изобретения

В целом, согласно одному варианту осуществления предложено полупроводниковое запоминающее устройство, содержащее:

блоки памяти, каждый из которых включает в себя массив ячеек памяти;

линии слов, соединенные со строками каждого из блоков памяти;

схему-защелку адреса, выполненную с возможностью фиксировать полный адрес для определения одной из линий слов, причем полный адрес включает в себя первый адрес и второй адрес; и

управляющую схему, выполненную с возможностью игнорировать операцию сброса для первого адреса в качестве цели операции установки и переписывать первый адрес в соответствии с операцией установки при приеме первой команды для определения операции сброса для блока памяти и операции установки для первого адреса.

Вариант осуществления изобретения будет далее пояснен со ссылкой на сопроводительные чертежи. Следует отметить, что в нижеприведенном пояснении одинаковые ссылочные позиции обозначают элементы, обладающие одинаковыми функциями и расположениями, и повторное пояснение будет приводиться только при необходимости.

Этот вариант осуществления будет пояснен с использованием MRAM (магниторезистивной оперативной памяти) в качестве примера полупроводникового запоминающего устройства.

Фиг. 1 представляет собой схематический вид, показывающий полупроводниковое запоминающее устройство 10 согласно этому варианту осуществления. Полупроводниковое запоминающее устройство 10 включает в себя сердечник 11 памяти, периферийную схему 12 и интерфейс 13.

Сердечник 11 памяти включает в себя множество ячеек памяти для хранения данных. Периферийная схема 12 выполняет запись данных, считывание данных и т.п. для сердечника 11 памяти.

Интерфейс 13 принимает управляющий сигнал CNT для считывания/записи и тактовый сигнал CK для управления временами операций считывания/записи от внешнего устройства (хоста). Интерфейс 13 также соединен с хостом посредством линии CA<n:0> команд/адресов и линии DQ<m:0> данных, где n и m – натуральные числа.

Управляющий сигнал CNT включает в себя тактовый разрешающий сигнал CKE и сигнал CS выбора чипа, и т.п. Тактовый сигнал CK используется для управления временами операций полупроводникового запоминающего устройства 10. Линия CA<n:0> команд/адресов используется для передачи/приема команд и адресов. Линия DQ<m:0> данных используется для передачи/приема входных данных и выходных данных.

Фиг. 2 представляет собой блок-схему, показывающую примеры сердечника 11 памяти и периферийной схемы 12. Сердечник 11 памяти включает в себя блок 21 массива ячеек памяти, декодер 22 строки и декодер 23 столбца. Блок 21 массива ячеек памяти включает в себя (k+1) блоков BK0-BKk памяти, где k – натуральное число. Блоки BK0-BKk памяти могут активироваться независимо друг от друга. Например, потребляемая мощность может быть снижена путем активации только необходимого блока памяти во время считывания/записи.

Декодер 22 строки декодирует, например, адрес BA<x:0> блока памяти для выбора одного из блоков BK0-BKk памяти и адрес AR<y:0> строки для выбора строки в выбранном блоке памяти.

Декодер 23 столбца декодирует, например, адрес AC<z:0> столбца для выбора столбца в блоке 21 массива ячеек памяти.

Периферийная схема 12 включает в себя схему-защелку 24 команды/адреса, управляющую схему 25, схему-защелку 26 адреса, схему-защелку 27 данных и тактовый генератор 28.

Схема-защелка 24 команды/адреса принимает команду CMD и адрес ADD от хоста 14 через линию CA<n:0> команд/адресов и временно сохраняет их. Команда CMD поступает в управляющую схему 25. На основе управляющего сигнала CNT и команды CMD от хоста 14 управляющая схема 25 управляет внутренней работой полупроводникового запоминающего устройства 10.

Из адреса ADD адрес BA<x:0> блока памяти поступает в декодер 22 строки, адрес AR<y:0> строки поступает в схему-защелку 26 адреса, и адрес AC<z:0> столбца поступает в декодер 23 столбца.

В этом варианте осуществления, как будет описано далее, схема-защелка 26 адреса фиксирует часть полного адреса строки, когда вводится команда активации, а также фиксирует другую часть полного адреса строки заранее, когда вводится команда предварительной зарядки, которая вводится перед командой активации.

Таким образом, часть адреса строки вводится перед вводом команды активации. Следовательно, даже когда увеличивается, например, количество битов адреса строки для выбора линии слова (строки) в блоке 21 массива ячеек памяти, полупроводниковое запоминающее устройство может быть включено в состав системы без увеличения количества выводов и уменьшения скорости работы, т.е. без изменения спецификаций.

Следует отметить, что команда предварительной зарядки представляет собой команду для установки выбранного блока памяти в начальное состояние (состояние предварительной зарядки) для операции считывания или операции записи. В частности, все линии слов, все линии битов и исходные линии являются деактивированными. Команда активации представляет собой команду для выполнения процесса считывания данных из массива ячеек памяти путем активации одной из множества линий слов в выбранном блоке памяти.

Схема-защелка 27 данных временно сохраняет входные данные, которые вводятся от хоста 14 через линию DQ<m:0> данных, или выходные данные, которые считываются из выбранного блока памяти. Входные данные записываются в выбранный блок памяти.

Тактовый генератор 28 генерирует внутренний тактовый сигнал CLK на основе тактового сигнала CK от хоста 14. Внутренний тактовый сигнал CLK вводится в схему-защелку 24 команды/адреса, управляющую схему 25, схему-защелку 26 адреса и схему-защелку 27 данных и используется для управления рабочими временами этих схем.

Фиг. 3 представляет собой блок-схему массива ячеек памяти, включенного в один блок памяти. Этот массив ячеек памяти сформирован расположением множества ячеек MC памяти в виде матрицы. Массив ячеек памяти включает в себя множество линий WL0-WLi-1 слов, множество линий BL0-BLj-1 битов и множество исходных линий SL0-SLj-1. Одна строка массива ячеек памяти соединена с одной линией WL слов, и один столбец массива ячеек памяти соединен с парой из одной линии BL битов и одной исходной линии SL.

Ячейка MC памяти включает в себя магниторезистивный элемент (элемент MTJ (элемент, основанный на магнитных туннельных переходах)) 30 и выбранный транзистор 31. Выбранный транзистор 31 выполнен, например, в виде полевого МОП-транзистора (MOSFET) с каналом n-типа.

Один вывод элемента 30 MTJ соединен с линией BL битов, а другой вывод соединен со стоком выбранного транзистора 31. Затвор выбранного транзистора 31 соединен с линией WL слов, и его исток соединен с исходной линией SL.

<Назначение команды/адреса>

Далее будет пояснено назначение команды/адреса. Фиг. 4 представляет собой вид, иллюстрирующий назначение команды/адреса относительно команды предварительной зарядки. Фиг. 5 представляет собой вид, иллюстрирующий назначение команды/адреса относительно команды активации.

На Фиг. 4 и 5 стрелки в столбце тактового сигнала CLK обозначают нарастающий фронт и спадающий фронт тактового сигнала. Ссылочные позиции CA0-CA9 обозначают команды и адреса, вводимые с контактных площадок команды/адреса (линий команд/адресов). Количество контактных площадок команды/адреса является примерным и этим не ограничивается. Адрес BA блока памяти для определения некоторого блока памяти имеет, например, 3 бита (BA0-BA2). Адрес R строки имеет, например, 18 битов (R0-R17). Из битов R0-R17 полного адреса строки первый адрес строки (часть полного адреса строки), вводимый вместе с командой предварительной зарядки, имеет, например, старшие биты R14-R17. Из битов R0-R17 полного адреса строки второй адрес строки (другая часть полного адреса строки), вводимый вместе с командой активации, имеет, например, младшие биты R0-R13.

На Фиг. 4 операция предварительной зарядки определяется при нарастающем фронте тактового сигнала CLK, когда вводится команда предварительной зарядки, и команда предварительной активации определяется при спадающем фронте тактового сигнала CLK. Другими словами, команда предварительной зарядки может задавать операцию предварительной зарядки и операцию предварительной активации. Команду предварительной зарядки задают, подтверждая сигнал CS выбора чипа и используя CA0=H, CA1=H, CA2=L и CA3=H при нарастающем фронте тактового сигнала CLK.

В операции предварительной зарядки флаг AB для определения того, следует ли выполнять предварительную зарядку всех блоков памяти, вводится с контактной площадки CA4, а адреса BA0-BA2 блока памяти вводятся с контактных площадок CA7-CA9. "X" обозначает "не важно".

В операции предварительной активации старшие адреса R14-R17 строки вводятся с контактных площадок CA3-CA6, а адреса BA0-BA2 блока памяти вводятся с контактных площадок CA7-CA9. В этом варианте осуществления адреса BA0-BA2 блока памяти могут быть определены в каждой из операции предварительной зарядки и операции предварительной активации. Следовательно, для одной и той же команды предварительной зарядки операция предварительной зарядки и операция предварительной активации могут выполняться в разных блоках памяти.

Как показано на Фиг. 5, операция активации определяется при нарастающем фронте и спадающем фронте тактового сигнала CLK, когда вводится команда активации. Команду активации задают, подтверждая сигнал CS выбора чипа и используя CA0=L и CA1=H при нарастающем фронте тактового сигнала CLK. Кроме того, при нарастающем фронте тактового сигнала CLK адреса R8-R12 строки вводятся с контактных площадок CA2-CA6, а адреса BA0-BA2 блока памяти вводятся с контактных площадок CA7-CA9. При спадающем фронте тактового сигнала CLK адреса R0-R13 строки вводятся с контактных площадок CA0-CA8.

<Сравнительный пример 1>

Ниже будут пояснены операции согласно сравнительному примеру 1. Сравнительный пример 1 представляет собой пример, в котором различны адрес блока памяти операции предварительной зарядки и адрес блока памяти операции предварительной активации. Фиг. 6 представляет собой вид, иллюстрирующий операцию сравнительного примера 1.

Сигнал BANK_ACTB<n> генерируется внутри полупроводникового запоминающего устройства 10, где n – порядковый номер блока памяти. Сигнал BANK_ACTB<n> генерируется с использованием команды активации и адресов BA0-BA2 блока памяти. Инверторная схема 40 инвертирует логический результат сигнала BANK_ACTB<n> и выводит сигнал BANK_ACT<n>. Когда вводится команда активации, сигнал BANK_ACT<N> выбранного блока памяти изменяется с низкого уровня на высокий уровень. В ответ на сигнал BANK_ACT<n> адрес R<13:0> строки изменяется с состояния разблокировки на состояние блокировки. Генератор 41 импульсов (одиночного импульса) принимает сигнал BANK_ACT<n> и генерирует разрешающий сигнал EN_ACT_X<n>, содержащий один импульс.

Адрес R<13:0> строки подается на входной вывод D схемы-защелки 42, а разрешающий сигнал EN_ACT_X<n> подается на разрешающий вывод E схемы-защелки 42. Когда разрешающий сигнал EN_ACT_X<n> подтвержден, схема-защелка 42 фиксирует адрес R<13:0> строки и выводит фиксированный адрес X<13:0> строки. Другими словами, адрес X<13:0> строки блокируется одноимпульсным разрешающим сигналом EN_ACT_X<n>. С другой стороны, адрес X<13:0> строки не блокируется операцией предварительной зарядки.

Сигнал LYSW_ACTB<n> генерируется внутри полупроводникового запоминающего устройства 10. Сигнал LYSW_ACTB<n> генерируется с использованием команды предварительной зарядки и адресов BA0-BA2 блока памяти. Инверторная схема 43 инвертирует логический результат сигнала LYSW_ACTB<n> и выводит сигнал LYSW_ACT<n>. Когда операция предварительной зарядки и операция предварительной активации последовательно задаются (при нарастающем фронте и спадающем фронте одного тактового сигнала) для двух разных блоков памяти, сигнал LYSW_ACT<n> изменяется с низкого уровня на высокий уровень в каждом из двух блоков памяти. В ответ на сигнал LYSW_ACT<n> адрес R<17:14> строки изменяется с состояния разблокировки на состояние блокировки. Генератор 44 импульсов (одиночного импульса) принимает сигнал LYSW_ACT<n> и генерирует разрешающий сигнал EN_LYSW_X<n>, содержащий один импульс.

Адрес R<17:14> строки подается на входной вывод D схемы-защелки 45, а разрешающий сигнал EN_LYSW_X<n> подается на разрешающий вывод Е схемы-защелки 45. Когда разрешающий сигнал EN_LYSW_X<n> подтвержден, схема-защелка 45 фиксирует адрес R<17:14> строки и выводит фиксированный адрес X<17:14> строки. Другими словами, адрес X<17:14> строки блокируется одноимпульсным разрешающим сигналом EN_LYSW_X<n>. С другой стороны, адрес X<17:14> строки не блокируется операцией предварительной зарядки.

Как описано ранее, сравнительный пример 1 представляет собой пример, в котором различны адрес блока памяти операции предварительной зарядки и адрес блока памяти операции предварительной активации. Когда операция предварительной активации выполняется в сравнительном примере 1, адрес R<17:14> строки блока памяти блокируется командой предварительной зарядки. Следовательно, команда предварительной зарядки не может использоваться в качестве сигнала для сброса адреса R<17:14> строки после включения источника питания.

<Сравнительный пример 2>

Ниже будут пояснены операции согласно сравнительному примеру 2. Сравнительный пример 2 представляет собой пример, в котором адрес блока памяти операции предварительной зарядки и адрес блока памяти операции предварительной активации являются одинаковыми. Фиг. 7 представляет собой вид, иллюстрирующий работу согласно сравнительному примеру 2. Операции блокировки и разблокировки адреса R<13:0> строки являются такими же, как и в сравнительном примере 1.

Когда операция предварительной зарядки и операция предварительной активации последовательно задаются (при нарастающем фронте и спадающем фронте одного тактового сигнала) для одного и того же блока памяти, сигнал LYSW_ACT<n> изменяется в следующем порядке: низкий уровень, высокий уровень и низкий уровень. В ответ на сигнал LYSW_ACT<n> адрес R<17:14> строки изменяется в следующем порядке: состояние разблокировки, состояние блокировки и состояние разблокировки. Другими словами, адрес X<17:14> строки, выводимый из схемы-защелки 45, не блокируется операцией предварительной зарядки, определяемой одной и той же командой предварительной зарядки, и блокируется операцией предварительной активации.

В сравнительном примере 2 адрес блока памяти операции предварительной зарядки и адрес блока памяти операции предварительной активации являются одинаковыми. Это асинхронная конструкция, в которой адрес R<17:14> строки устанавливается после сброса блока памяти, приводя к строгим временным рамкам.

<Пример>

Далее будет пояснен пример. Фиг. 8 представляет собой вид, иллюстрирующий работу согласно этому примеру. Операции блокировки и разблокировки адреса R<13:0> строки являются такими же, как в сравнительном примере 1.

Как показано на Фиг. 8, добавлена предварительная схема-защелка 46. Адрес R<17:14> строки подается на входной вывод D предварительной схемы-защелки 46, а сигнал LYSW_ACT<n> подается на разрешающий вывод E предварительной схемы-защелки 46. Когда сигнал LYSW_ACT<n> подтвержден, предварительная схема-защелка 46 фиксирует адрес R<17:14> строки и выводит фиксированный адрес LT_R<17:14> строки.

Адрес LT_R<17:14> строки подается на входной вывод D схемы-защелки 45, а разрешающий сигнал EN_ACT_X<n> подается на разрешающий вывод Е схемы-защелки 45. Когда разрешающий сигнал EN_ACT_X<n> подтвержден, схема-защелка 45 фиксирует адрес LT_R<17:14> строки и выводит фиксированный адрес X<17:14> строки.

За счет вышеописанной работы предварительная схема-защелка 46 может перезаписывать адрес LT_R<17:14> строки. Другими словами, поскольку разрешающий сигнал LYSW_ACT<n> для предварительной схемы-защелки 46 поддерживается подтвержденным до следующей операции предварительной зарядки, адрес LT_R<17:14> строки не блокируется командой предварительной зарядки, а перезаписывается всегда, когда выполняется операция предварительной активации. Это решает проблему сравнительного примера 1.

Также, когда вводится команда активации, схема-защелка 45 фиксирует адрес LT_R<17:14> строки и выводит фиксированный адрес X<17:14> строки. Т.е. адрес X<17:14> строки блокируется разрешающим сигналом EN_ACT_X<n>, содержащим один импульс. Другими словами, адрес X<17:14> строки блокируется в ответ на команду активации. Это решает проблему сравнительного примера 2.

Следует отметить, что инверторная схема 40 для генерации сигнала BANK_ACT<n> и инверторная схема 43 для генерации сигнала LYSW_ACT<n> включены в состав, например, интерфейса 13, показанного на Фиг. 1. Генератор 41 импульсов для генерации разрешающего сигнала EN_ACT_X<n> и генератор 44 импульсов для генерации разрешающего сигнала EN_LYSW_X<n> включены в состав, например, управляющей схемы 25, показанной на Фиг. 2. Схемы-защелки 42 и 45 и предварительная схема-защелка 46 включены в состав, например, схемы-защелки 26 адреса, показанной на Фиг. 2.

Фиг. 9 представляет собой временную диаграмму, показывающую пример вводимой команды. Как показано на Фиг. 9, тактовые сигналы CLK_t и CLK_c представляют собой комплементарные тактовые сигналы.

Команда предварительной зарядки вводится в блок А памяти. В ответ на эту команду предварительной зарядки операция предварительной зарядки определяется при нарастающем фронте тактового сигнала, а операция предварительной активации определяется при спадающем фронте тактового сигнала.

Когда команда, как показано на Фиг. 9, вводится в этом примере, операция предварительной зарядки игнорируется, и только операция предварительной активации выполняется для адреса строки предварительной активации. В этой операции предварительной активации адрес строки предварительной активации перезаписывается в схеме-защелке 26 адреса. Это восстанавливает внутренние времена полупроводникового запоминающего устройства 10.

Фиг. 10 представляет собой временную диаграмму, показывающую другие примеры вводимой команды. Команда предварительной зарядки вводится в блок А памяти. В ответ на эту команду предварительной зарядки операция предварительной зарядки определяется при нарастающем фронте тактового сигнала, а операция предварительной активации определяется при спадающем фронте тактового сигнала. Далее команда активации вводится в блок А памяти, и определяется операция активации. В этой операции активации схема-защелка 26 адреса блокирует адрес строки при нарастающем фронте и спадающем фронте тактового сигнала. Когда команды, как показано на Фиг. 10, вводятся в этом примере, полный адрес строки блокируется операцией активации.

Следует отметить, что в вышеупомянутом примере MRAM, использующая магниторезистивный элемент, была приведена в качестве примера полупроводникового запоминающего устройства. Тем не менее изобретение этим не ограничивается и применимо к различным видам полупроводниковых запоминающих устройств, включая энергозависимые или энергонезависимые запоминающие устройства. Изобретение также применимо к резистивному запоминающему устройству такого же типа, как MRAM, например ReRAM (резистивная память с произвольным доступом) или PCRAM (оперативная память с изменением фазовых состояний).

Хотя были описаны конкретные варианты осуществления, эти варианты осуществления были представлены только в качестве примера и не предназначены для ограничения объема изобретений. В действительности, новые варианты осуществления, описанные в данном документе, могут быть воплощены во множестве других форм; кроме того, различные исключения, замены и изменения в форме вариантов осуществления, описанных в данном документе, могут быть сделаны без отступления от сущности изобретений. Приложенная формула изобретения и ее эквиваленты предназначены для охвата таких форм или модификаций, какие будут подпадать под объем и сущность изобретений.

| название | год | авторы | номер документа |

|---|---|---|---|

| ПОЛУПРОВОДНИКОВОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 2014 |

|

RU2643629C2 |

| ПОЛУПРОВОДНИКОВОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 2014 |

|

RU2641478C2 |

| ЭНЕРГОНЕЗАВИСИМОЕ ОПЕРАТИВНОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 2014 |

|

RU2622869C2 |

| ПОЛУПРОВОДНИКОВОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 2006 |

|

RU2391722C2 |

| ПОЛУПРОВОДНИКОВАЯ ПАМЯТЬ | 1993 |

|

RU2156506C2 |

| УСТРОЙСТВО ПАМЯТИ И СПОСОБ УПРАВЛЕНИЯ ИМ | 2016 |

|

RU2669872C1 |

| СПОСОБ И УСТРОЙСТВО ДЛЯ НЕЯВНОЙ ПРЕДВАРИТЕЛЬНОЙ ЗАРЯДКИ ДИНАМИЧЕСКОЙ ОПЕРАТИВНОЙ ПАМЯТИ (DRAM) | 2004 |

|

RU2331118C2 |

| ЗАЩИЩЕННАЯ ПАМЯТЬ С МНОЖЕСТВОМ УРОВНЕЙ ЗАЩИТЫ | 1998 |

|

RU2214008C2 |

| ПОЛУПРОВОДНИКОВОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 2014 |

|

RU2618368C2 |

| Устройство для отображения информации | 1986 |

|

SU1441450A1 |

Изобретение относится к полупроводниковым запоминающим устройствам. Техническим результатом является реализация запоминающего устройства, выполненного с возможностью высокоскоростной работы и обладающего большой емкостью. Устройство содержит блоки памяти, каждый из которых включает в себя массив ячеек памяти; линии слов, соединенные со строками каждого из блоков памяти; схему-защелку адреса, выполненную с возможностью фиксировать полный адрес для определения одной из линий слов, причем полный адрес включает в себя первый адрес и второй адрес; и управляющую схему, выполненную с возможностью игнорировать операцию сброса для первого адреса в качестве цели операции установки и перезаписывать первый адрес в соответствии с операцией установки при приеме первой команды для определения операции сброса для блока памяти и операции установки для первого адреса. 13 з.п. ф-лы, 10 ил.

1. Полупроводниковое запоминающее устройство, содержащее:

блоки памяти, каждый из которых включает в себя массив ячеек памяти;

линии слов, соединенные со строками каждого из блоков памяти;

схему-защелку адреса, выполненную с возможностью фиксировать полный адрес для определения одной из линий слов, причем полный адрес включает в себя первый адрес и второй адрес; и

управляющую схему, выполненную с возможностью игнорировать операцию сброса для первого адреса в качестве цели операции установки и перезаписывать первый адрес в соответствии с операцией установки при приеме первой команды для определения операции сброса для блока памяти и операции установки для первого адреса.

2. Устройство по п. 1, в котором управляющая схема блокирует первый адрес при приеме второй команды для определения операции установки для второго адреса.

3. Устройство по п. 2, дополнительно содержащее:

первую схему-защелку, выполненную с возможностью предварительно фиксировать перезаписанный первый адрес; и

вторую схему-защелку, выполненную с возможностью фиксировать выходной сигнал из первой схемы-защелки в момент времени, при котором принимается вторая команда.

4. Устройство по п. 3, дополнительно содержащее генератор импульсов, выполненный с возможностью генерировать один импульс при приеме второй команды;

при этом вторая схема-защелка выполняет операцию фиксирования в соответствии с импульсом генератора импульсов.

5. Устройство по п. 2, в котором управляющая схема блокирует второй адрес при приеме второй команды.

6. Устройство по п. 5, дополнительно содержащее третью схему-защелку, выполненную с возможностью фиксировать второй адрес.

7. Устройство по п. 6, дополнительно содержащее генератор импульсов, выполненный с возможностью генерировать один импульс при приеме второй команды;

при этом третья схема-защелка выполняет операцию фиксирования в соответствии с импульсом генератора импульсов.

8. Устройство по п. 1, в котором

операция сброса выполняется при нарастающем фронте тактового сигнала; и

операция установки выполняется при спадающем фронте тактового сигнала.

9. Устройство по п. 1, в котором

первая команда вводится при нарастающем фронте тактового сигнала; и

первый адрес вводится при спадающем фронте тактового сигнала.

10. Устройство по п. 1, в котором второй адрес вводится при нарастающем фронте и спадающем фронте тактового сигнала.

11. Устройство по п. 1, дополнительно содержащее контактные площадки, которые должны использоваться для приема первого адреса и второго адреса от внешнего устройства и совместно использоваться первым адресом и вторым адресом.

12. Устройство по п. 1, в котором первая команда является командой предварительной зарядки.

13. Устройство по п. 2, в котором вторая команда является командой активации.

14. Устройство по п. 1, в котором массив ячеек памяти включает в себя магниторезистивный элемент.

| US 2003088753 A1, 08.05.2003 | |||

| US 2004120212 A1, 24.06.2004 | |||

| US 2012033480 A1, 09.02.2012 | |||

| УСТРОЙСТВО МАГНИТОРЕЗИСТИВНОЙ ОПЕРАТИВНОЙ ПАМЯТИ С СОВМЕСТНО ИСПОЛЬЗУЕМОЙ ЛИНИЕЙ ИСТОКА | 2008 |

|

RU2455711C2 |

Авторы

Даты

2017-10-24—Публикация

2014-07-29—Подача