Предлагаемое устройство для вычисления квадратного корня из суммы квадратов двух двоичных чисел относится к области вычислительной техники и предназначено для использования в специализированных вычислительных устройствах.

Известно устройство [А.с. 404082 СССР, 1971] для вычисления корня квадратного из суммы квадратов двух чисел. Оно содержит счетчики, схему анализа, блок управления, логические элементы, однако обладает недостаточно высоким быстродействием.

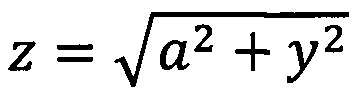

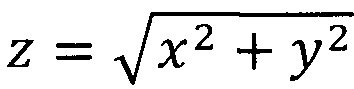

Наиболее близким по технической сущности к предложенному является устройство для вычисления функции вида  [А.с. 645154 СССР, 1979], содержащее счетчики, схему сравнения, блок управления, элементы И, причем выходы первого и второго счетчиков подключены ко входам первого и второго элементов И соответственно и ко входам схемы сравнения, кроме того, в него введены делители частоты, блоки утроения числа импульсов, элемент НЕ, входы делителей частоты являются входами устройства, а выходы соединены со входами первого и второго счетчиков и с соответствующими входами блоков утроения числа импульсов, выход первого из которых подключен ко входам третьего и четвертого счетчиков, а выход второго - к другим входам третьего и через элемент НЕ - четвертого счетчиков, выходы которых соединены со входами соответствующих элементов И и со входами схемы сравнения, выход которой соединен со входом блока управления, выходы которого соединены со вторыми входами счетчиков и элементов И, выходы которых являются выходами устройства.

[А.с. 645154 СССР, 1979], содержащее счетчики, схему сравнения, блок управления, элементы И, причем выходы первого и второго счетчиков подключены ко входам первого и второго элементов И соответственно и ко входам схемы сравнения, кроме того, в него введены делители частоты, блоки утроения числа импульсов, элемент НЕ, входы делителей частоты являются входами устройства, а выходы соединены со входами первого и второго счетчиков и с соответствующими входами блоков утроения числа импульсов, выход первого из которых подключен ко входам третьего и четвертого счетчиков, а выход второго - к другим входам третьего и через элемент НЕ - четвертого счетчиков, выходы которых соединены со входами соответствующих элементов И и со входами схемы сравнения, выход которой соединен со входом блока управления, выходы которого соединены со вторыми входами счетчиков и элементов И, выходы которых являются выходами устройства.

Недостаток данного устройства состоит в том, что вычисление искомой величины идет с большой погрешностью (5÷6%).

Задачей настоящего изобретения является повышение точности функционирования устройства.

Технический результат - возможность получения более точного значения квадратного корня из суммы квадратов двух двоичных чисел, уменьшение погрешности вычислений.

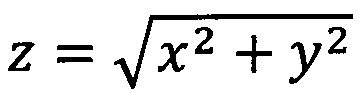

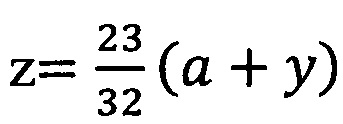

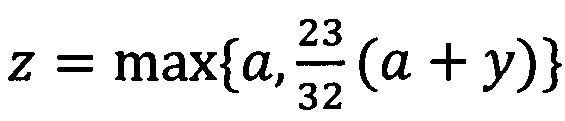

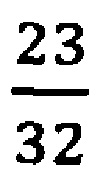

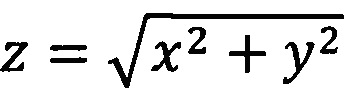

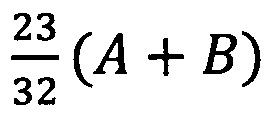

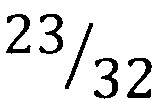

Технический результат достигается предложенным устройством для вычисления функции вида  , которое содержит счетчики, схему сравнения, блок управления, элементы И, причем выходы первого и второго счетчиков подключены ко входам первого и второго элементов И соответственно и ко входам схемы сравнения, кроме того, содержит делители частоты, элемент НЕ, входами устройства являются входы первого и второго делителей частоты, выходы которых соединены со входами первого и второго счетчиков, выходы которых соединены со входами одноименных элементов И и со входами схемы сравнения, выход которой соединен со входом блока управления, выходы которого соединены со вторыми входами четырех счетчиков и четырех элементов И, выходы которых являются выходами устройства, в устройство дополнительно введены два блока пересчета импульсов, связанные четырехпроводной шиной по входу с первым и вторым делителями частоты, при этом выход первого блока пересчета импульсов связан со входами третьего и четвертого счетчиков, выход второго блока пересчета импульсов - с другими входами третьего и через элемент НЕ - четвертого счетчика. При этом коэффициент пересчета сделан равным

, которое содержит счетчики, схему сравнения, блок управления, элементы И, причем выходы первого и второго счетчиков подключены ко входам первого и второго элементов И соответственно и ко входам схемы сравнения, кроме того, содержит делители частоты, элемент НЕ, входами устройства являются входы первого и второго делителей частоты, выходы которых соединены со входами первого и второго счетчиков, выходы которых соединены со входами одноименных элементов И и со входами схемы сравнения, выход которой соединен со входом блока управления, выходы которого соединены со вторыми входами четырех счетчиков и четырех элементов И, выходы которых являются выходами устройства, в устройство дополнительно введены два блока пересчета импульсов, связанные четырехпроводной шиной по входу с первым и вторым делителями частоты, при этом выход первого блока пересчета импульсов связан со входами третьего и четвертого счетчиков, выход второго блока пересчета импульсов - с другими входами третьего и через элемент НЕ - четвертого счетчика. При этом коэффициент пересчета сделан равным  .

.

Введение двух блоков пересчета импульсов с их связями с другими блоками устройства позволило повысить точность его функционирования.

Предложенное устройство имеет изобретательский уровень, так как из опубликованных научных данных и существующих решений явным образом не следует, что заявляемая совокупность блоков, узлов и связей между ними позволяют повысить точность функционирования устройства при вычислении функции  .

.

Предложенное вычислительное устройство промышленно применимо, поскольку его техническая реализация возможна с использованием типовых элементов микроэлектронной техники (интегральных логических схем).

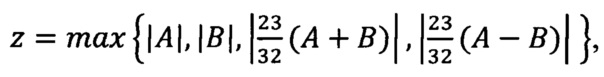

К предложенному устройству имеет отношение приближенный алгоритм вычисления квадратного корня из суммы квадратов двух чисел.

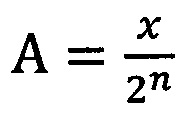

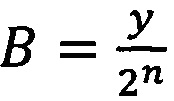

где А и В - числовые последовательности, пропорциональные x и y соответственно.

Все вычисления производятся за одну операцию, включающую в себя две микрооперации:

1) сравнение чисел - |А| и |В| и определение наибольшего из них;

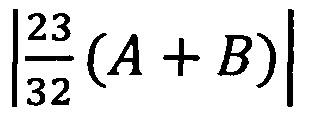

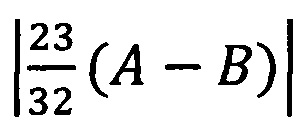

2) сравнение числа, определенного в первой микрооперации, с числом  и

и  и определение наибольшего из данных чисел.

и определение наибольшего из данных чисел.

Результат вычисления z равен наибольшему числу, определенному во время второй микрооперации.

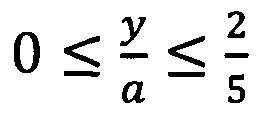

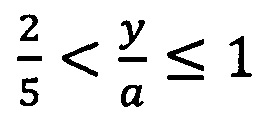

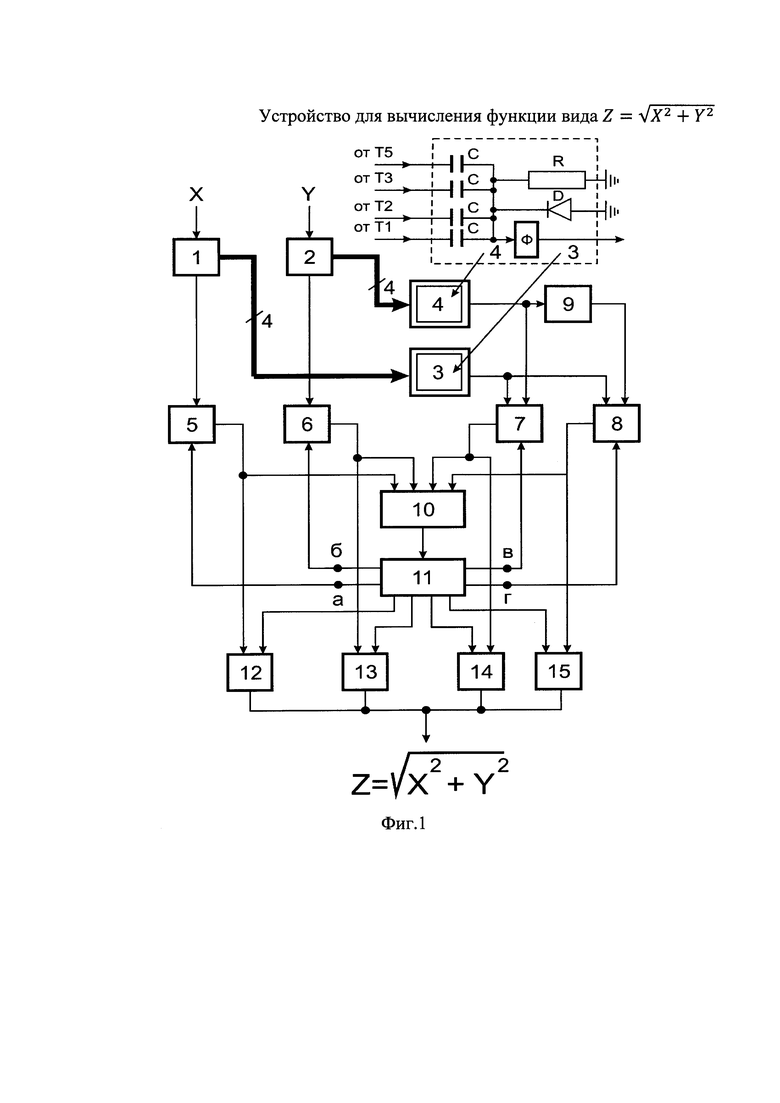

Возможность аппроксимации выражения  в соответствии с приведенным алгоритмом рассматривается на примере аппроксимации выражения

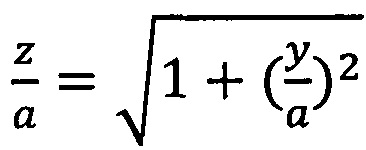

в соответствии с приведенным алгоритмом рассматривается на примере аппроксимации выражения  , где 0≤y≤а. При фиксированном а выражение принимает вид

, где 0≤y≤а. При фиксированном а выражение принимает вид  . Это есть монотонно возрастающая функция от

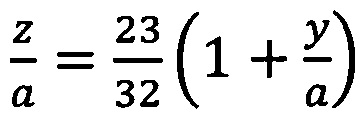

. Это есть монотонно возрастающая функция от  , график которой приведен на фиг. 2 (расчетная кривая - теория). Заменим построенную кривую ломаной (кривая - заявка), уравнения одного из звеньев которой

, график которой приведен на фиг. 2 (расчетная кривая - теория). Заменим построенную кривую ломаной (кривая - заявка), уравнения одного из звеньев которой  или z=а, а другого

или z=а, а другого  или

или  .

.

Аналитически уравнение аппроксимированной ломаной может быть записано в виде  . Так как в приведенном устройстве предусмотрено поступление входных переменных с разными знаками, в алгоритм вычисления дополнительно включено вычисление

. Так как в приведенном устройстве предусмотрено поступление входных переменных с разными знаками, в алгоритм вычисления дополнительно включено вычисление  разности числовых последовательностей.

разности числовых последовательностей.

Максимальная относительная ошибка аппроксимирующей ломаной в интервале  не превышает 3%. В интервале

не превышает 3%. В интервале  не превышает 0,5%.

не превышает 0,5%.

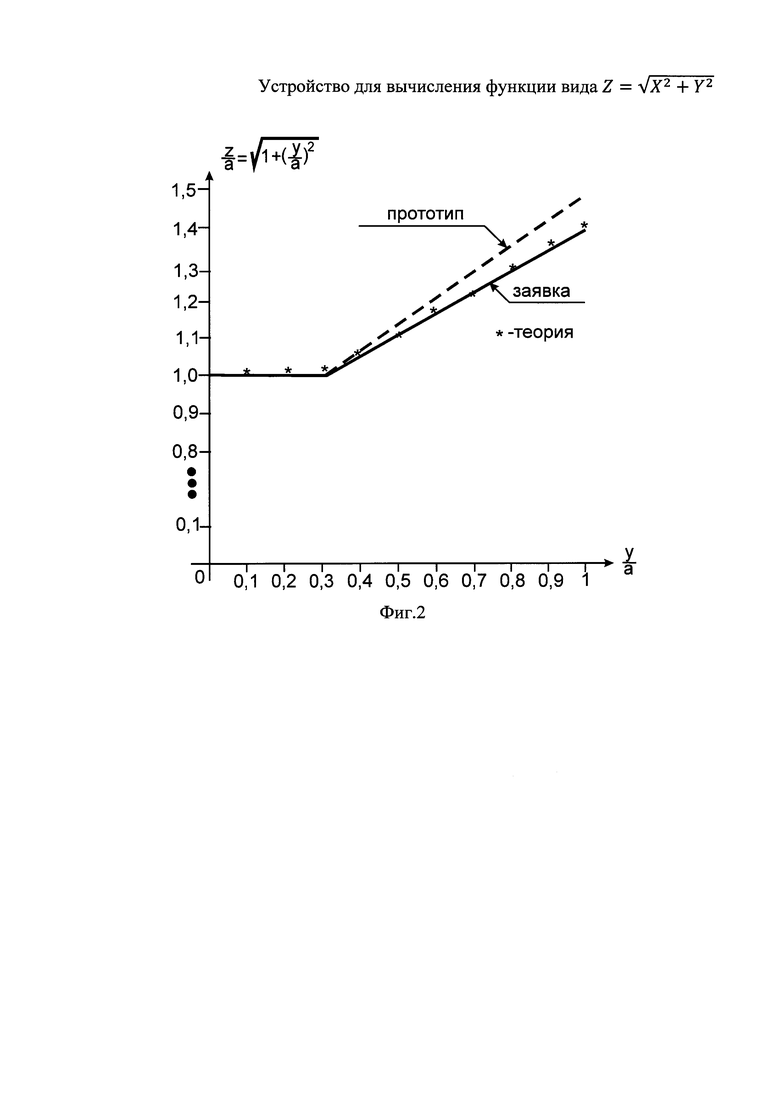

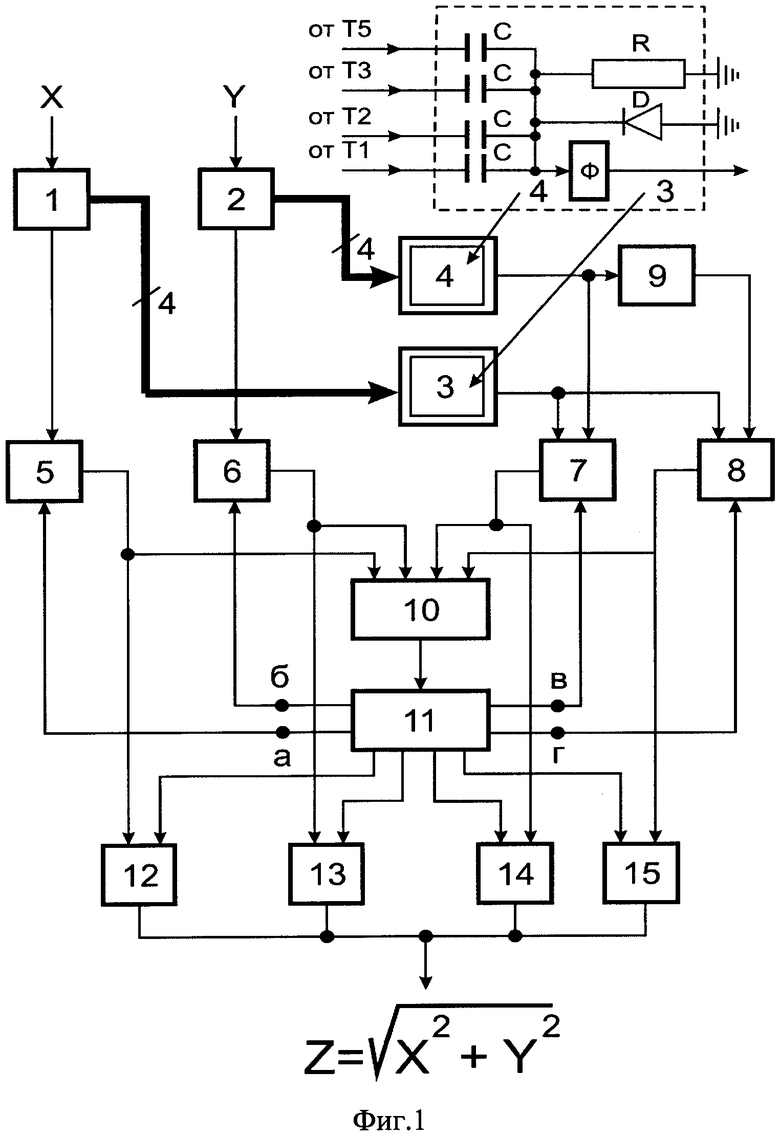

На фиг. 1 представлена структурная схема устройства для вычисления функции  , а на фиг. 2 - график расчетной и аппроксимирующей кривых для прототипа и для заявленного устройства.

, а на фиг. 2 - график расчетной и аппроксимирующей кривых для прототипа и для заявленного устройства.

Оно содержит делители 1, 2 частоты, первый 3 и второй 4 блоки пересчета импульсов, счетчики 5-8, элемент 9 НЕ, схему 10 сравнения, блок 11 управления, элементы 12-15 И. Причем выходы первого 5 и второго 6 счетчиков подключены к входам первого 12 и второго 13 элементов И соответственно и ко входам схемы 10 сравнения, входы делителей 1, 2 частоты являются входами устройства, а их выходы соединены со входами первого 5 и второго 6 счетчиков. Управляющие выходы а, б, в, г блока 11 управления связаны с управляющими входами первого 5, второго 6, третьего 7 и четвертого 8 счетчиков соответственно. Входы блоков 3, 4 пересчета импульсов связаны с делителями 1, 2 частоты, при этом выход первого блока пересчета импульсов 3 связан со входами третьего 7 и четвертого 8 счетчиков, а выход второго блока пересчета импульсов 4 связан с другими входами третьего 7 и через элемент НЕ четвертого 8 счетчиков. Выходы этих блоков связали с третьим 7 и через элемент 9 НЕ - с четвертым счетчиками соответственно. Выходы всех четырех счетчиков 5-8 связаны с четырьмя входами схемы 10 сравнения и с первыми входами четырех элементов 12-15 И, выходы которых объединены по схеме "монтажное ИЛИ" и образуют выход устройства. Причем вторые входы четырех элементов 12-15 И связаны с четырьмя выходами блока 11 управления, вход которого связан с выходом схемы 10 сравнения.

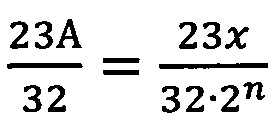

Четырехпроводные шины, связывающие первый 3 и второй 4 блоки пересчета импульсов с первым 1 и вторым 2 делителями частоты, подключены к первому, второму, третьему и пятому старшему разряду каждого из делителей 1, 2 частоты (16+4+2+1=23).

Блоки 3, 4 пересчета импульсов состоят из 4-х дифференцирующих цепочек CR, диода D, объединенных по схеме "монтажное ИЛИ", и формирователя Ф импульсов, связанного с выходом блоков 3, 4.

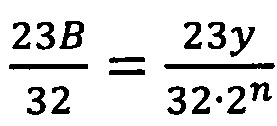

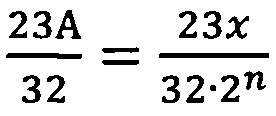

Устройство работает следующим образом. На входы устройства поступают двоичные последовательности импульсов x и y, которые могут быть как положительными, так и отрицательными. В делителях 1, 2 последовательности импульсов делятся на 2n, где n - число разрядов делителя. На выходах делителей образуются сравниваемые сигналы  и

и  . Эти сигналы накапливаются в счетчиках 5, 6 и являются сравниваемыми сигналами для первой микрооперации сравнения. Для осуществления второй микрооперации сравнения формируются сигналы

. Эти сигналы накапливаются в счетчиках 5, 6 и являются сравниваемыми сигналами для первой микрооперации сравнения. Для осуществления второй микрооперации сравнения формируются сигналы  и

и  - выполняется умножение на

- выполняется умножение на  суммы и разности сигналов.

суммы и разности сигналов.

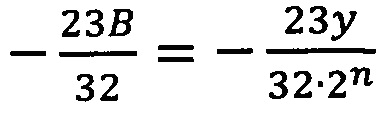

Для этого в блоках 3, 4 пересчета импульсов происходит умножение сигналов А и В, на входы счетчика 7 суммы поступают сигналы  и

и  , а на входы счетчика 8 разности - сигналы

, а на входы счетчика 8 разности - сигналы  и

и  .

.

Таким образом, в счетчиках 7 и 8 образуются соответственно сумма и разность сигналов  и

и  , которые подаются для дальнейшего сравнения в схеме 10 сравнения.

, которые подаются для дальнейшего сравнения в схеме 10 сравнения.

В схеме 10 сравнения происходит сравнение и определение максимальных сигналов. Для упрощения устройства сравнение осуществляется за 2 микрооперации. В первой микрооперации определяется максимальный сигнал из чисел, находящихся в счетчиках 5 и 6, т.е. из чисел А и В.

Во время второй микрооперации при наличии тактовых импульсов по результатам сравнения в первой микрооперации и в зависимости от знаков сравниваемых чисел формируются импульсы управления, которые подключают ко входам схемы сравнения два из четырех исходных счетчиков 5, 6, 7, 8.

Варианты подключения следующие:

1 вариант. Если в результате первой микрооперации сравнения определилось, что число в счетчике 5 больше числа в счетчике 6, т.е. А>В и при условии, что знаки сравниваемых чисел одинаковы на выходах а и b блока 11 управления, формируются импульсы управления, посредством которых во время второй микрооперации сравниваются числа A и  .

.

2 вариант. Если в результате первой микрооперации сравнения определилось, что В>А и знаки сравниваемых чисел одинаковы, то во время второй микрооперации сравниваются числа A и  .

.

3 вариант. Если в результате первой микрооперации сравнения определилось, что А>В и знаки сравниваемых чисел разные, то во время второй микрооперации происходит сравнение чисел А и  .

.

4 вариант. Если в результате первой микрооперации сравнения определилось, что В>А и знаки сравниваемых чисел разные, то во время второй микрооперации происходит сравнения чисел В и  .

.

Максимальное число, определенное во время второй микрооперации, переписывается из счетчика, в котором оно хранится, через элементы И 12, 13, 14, 15 И на выходную шину z.

Предложенное устройство позволяет снизить максимальную относительную погрешность вычислений с 6,07% (у прототипа) до 0,5-3,0%, а среднюю относительную погрешность в 2,8 раза.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления функции вида | 1976 |

|

SU645154A1 |

| Делительно-множительное устройство | 1980 |

|

SU868757A1 |

| Генератор случайного процесса | 1983 |

|

SU1113800A1 |

| Генератор случайных чисел | 1987 |

|

SU1524048A1 |

| Вероятностный коррелометр | 1979 |

|

SU1023338A1 |

| Делитель частоты следования импульсов с переменным коэффициентом деления | 1983 |

|

SU1092730A1 |

| Анализатор спектра | 1981 |

|

SU1002977A2 |

| Устройство для регистрации информации | 1985 |

|

SU1304170A1 |

| СПОСОБ И УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ И ПРИЕМА СИГНАЛОВ С ОГРАНИЧЕННЫМ СПЕКТРОМ (ВАРИАНТЫ) | 2004 |

|

RU2265278C1 |

| Генератор случайного процесса | 1985 |

|

SU1739374A1 |

Изобретение относится к области вычислительной техники и предназначено для использования в специализированных вычислительных устройствах. Техническим результатом является повышение точности функционирования устройства. Устройство содержит счетчики, схему сравнения, блок управления, элементы И, делители частоты, элемент НЕ, блоки пересчета импульсов. 2 ил.

Устройство для вычисления функции вида  , содержащее счетчики, схему сравнения, блок управления, элементы И, причем выходы первого и второго счетчиков подключены ко входам первого и второго элементов И соответственно и ко входам схемы сравнения, кроме того, содержащее делители частоты, элемент НЕ, входами устройства являются входы первого и второго делителей частоты, выходы которых соединены со входами одноименных счетчиков, выходы которых соединены со входами одноименных элементов И и со входами схемы сравнения, выход которой соединен со входом блока управления, выходы которого соединены со вторыми входами счетчиков и элементов И, выходы которых являются выходами устройства, отличающееся тем, что дополнительно содержит два блока пересчета импульсов, каждый из которых связан четырехпроводной шиной по входу с первым и вторым делителями частоты соответственно, а по выходу - с третьим и - через элемент НЕ - с четвертыми счетчиками, причем коммутация каждого из четырех проводов с первым, вторым, третьим и пятым разрядами каждого из делителей частоты обеспечивает коэффициент пересчета, равный

, содержащее счетчики, схему сравнения, блок управления, элементы И, причем выходы первого и второго счетчиков подключены ко входам первого и второго элементов И соответственно и ко входам схемы сравнения, кроме того, содержащее делители частоты, элемент НЕ, входами устройства являются входы первого и второго делителей частоты, выходы которых соединены со входами одноименных счетчиков, выходы которых соединены со входами одноименных элементов И и со входами схемы сравнения, выход которой соединен со входом блока управления, выходы которого соединены со вторыми входами счетчиков и элементов И, выходы которых являются выходами устройства, отличающееся тем, что дополнительно содержит два блока пересчета импульсов, каждый из которых связан четырехпроводной шиной по входу с первым и вторым делителями частоты соответственно, а по выходу - с третьим и - через элемент НЕ - с четвертыми счетчиками, причем коммутация каждого из четырех проводов с первым, вторым, третьим и пятым разрядами каждого из делителей частоты обеспечивает коэффициент пересчета, равный  .

.

| Устройство для вычисления функции вида | 1976 |

|

SU645154A1 |

| УСТРОЙСТВО для ВЫЧИСЛЕНИЯ ФУНКЦИИ ВИДАZ =. KV'X^ + у | 0 |

|

SU404082A1 |

| Устройство для вычисления функции вида @ | 1983 |

|

SU1115050A1 |

| УСТРОЙСТВО ДЛЯ ИЗВЛЕЧЕНИЯ КВАДРАТНОГО КОРНЯ ИЗ СУММЫ КВАДРАТОВ ДВУХ ВЕЛИЧИН | 1992 |

|

RU2045777C1 |

| US 5459683 A, 17.10.1995 | |||

| US 5862068 A, 19.01.1999 | |||

| US 6658445 B1, 02.12.2003. | |||

Авторы

Даты

2017-07-14—Публикация

2016-05-17—Подача