1

выходы распределителя импульсов соединены соответственно с первым, вторым и третьим вхрдами первого элемента ИЛИ, шестнадцатый выход распределителя импульсов соединен с вторым входом первого элемента ЗИ-ИЛИ и вторым входом второго элемента ЗИ-ИЛИ, семнадцатый выход распределителя импульсов соединен с третьим входом первого элемента 2И-ИЛИ и третьим входом второго элемента 2И-ИЛИ, восемнадцатый выход распределителя импульсов соединен с третьим входом первого элемента ЗИ-ИЛИ и третьим входом второго элемента ЗИ-ИЛИ, выход первого элемента ЗИ-ИЛИ соединен с вторыми входами элементов ИЛИ третьей группы, выход второго элемента ЗИ-ИЛИ соединен с вторыми входами элементов И четвертой группы, выход первого элемента И соединен с входом считывания-первого регистра операнда, выход второго элемента И соединен с входом считывания второго регистра операнда, выход первого элемента 2И-ИЛИ соединен с входом записи первого регистра операнда, выход второго элемента 2И-ШШ соединен с входом записи второго регистра операнда, выход первого элемента ИЛИ соединен с входом сдвига регистра сдвига, выход второго элемента ИЛИ соединен с входом суммирования накапливающего сумматора, выход третьего элемента ИЛИ соединен с входом обнуления накапливающего сумматора, входы первого операнда уст5050

ройства соединены соответственно с первыми входами элементов ИЛИ второй группы, входы второго операнда устройства- соединены соответственно с первыми входами элементов ИЛИ третьей группы, выходы.накапливающего сумматора соединены соответственно с вторыми входами элементов ИЛИ второй и третьей групп, выходы элементов ИЛИ второй Группы соединены с разрядными входами первого регистра операнда, выходы элементов ИЛИ третьей группы соединены с разрядными входами второго регистраоперанда, выходы первого регистра операнда соединены соответственно с первыми входами схемы сравнения, выходы второго регистра операнда соединены соответственно с вторыми входами схемы сравнения, прямой выход схемы сравнения соединен с вторым входом триггера и четвертым входом первого элемента ЗИ-ИЛИ, инверсный выход схемы сравнения соединен с четвертым входом второго элемента ЗИ-ИЛИ, первый выход триггера соединен с пятым входом первого элемента ЗИ-ИЛИ, пятым входом второго элемента ЗИ-ИЛИ, вторым входом второго элемента И, четвертым входом второго элемента 2И-ИЛИ, второй выход триггера соединен с шестым входом первого элемента ЗИ-ИЛИ, шестым входом второго элемента ЗИ-ИЛИ , вторым входом первого элемента И , четв.ертым входом первого элемента 2И-ИЛИ,

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой измеритель центра тяжести видеосигналов | 1990 |

|

SU1723559A1 |

| Устройство для вычисления квадратного корня | 1983 |

|

SU1141407A1 |

| Устройство для извлечения квадратного корня | 1985 |

|

SU1259257A1 |

| Устройство для извлечения квадратного корня | 1984 |

|

SU1246091A1 |

| Анализатор спектра Фурье | 1985 |

|

SU1302293A1 |

| Устройство для вычисления сумм произведений | 1982 |

|

SU1056184A2 |

| СПОСОБ ЦИФРОВОЙ ОБРАБОТКИ СИГНАЛОВ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2000 |

|

RU2163391C1 |

| Устройство для вычисления квадратного корня из суммы квадратов двух чисел | 1977 |

|

SU627477A1 |

| Устройство для обработки выражений языков программирования | 1981 |

|

SU1016790A1 |

| Устройство для отображения информации на экране электронно-лучевой трубки | 1988 |

|

SU1606991A1 |

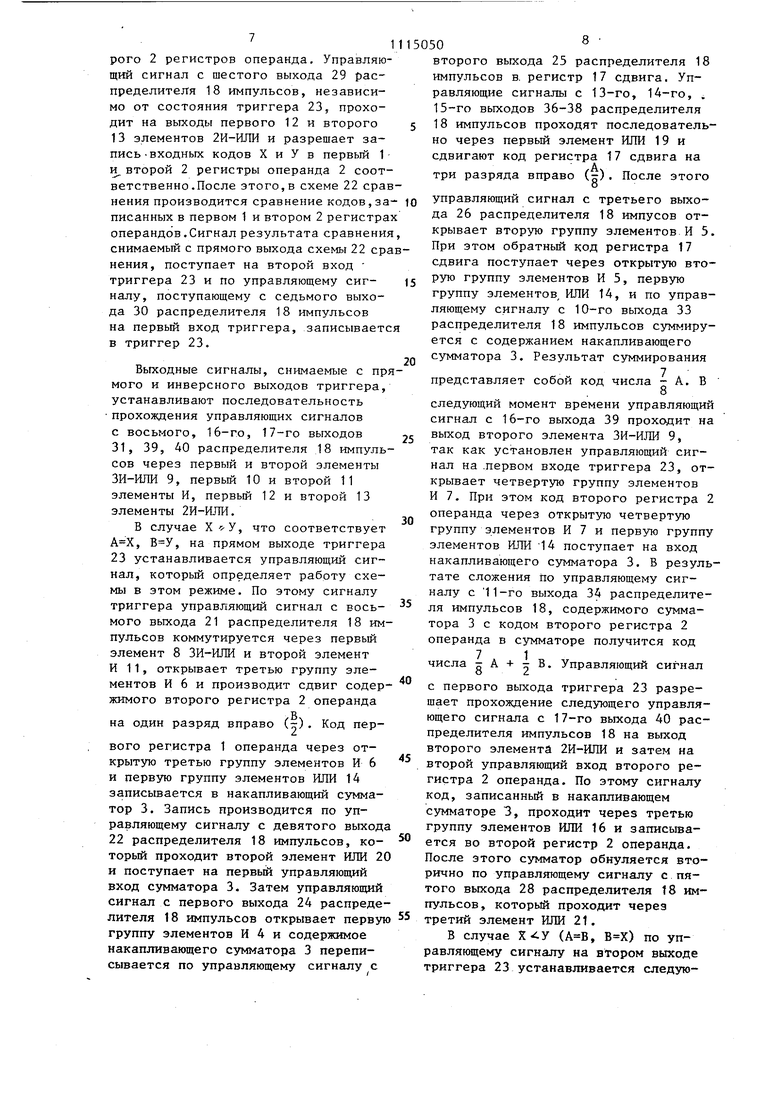

УСТРОЙСТВОЛШЯ ВЫЧИСЛЕНИЯ ФУНКЦИИ ВИДА , содержащее первый и второй регистры операнда, накапливающий сумматор, первую, вторую, третью и четвертую группы элементов И, первую группу элементов ИЛИ, регистр сдвига, распределитель импульсов, причем первый выход распределителя импульсов соединен с первыми входами элементов И первой группы, второй выход распределителя импульсов соединен с входом записи регистра сдвига, третий выход распределителя импульсов соединен с первыми входами элементов И второй группы, выходы первого регистра операнда соединены соответственно с первыми входами элементов И третьей группы, выходы второго регистра операнда соединены соответственно с первыми входами элементов И четвертой группы, выходы элементов И второй, третьей и четвертой групп соединены соответственно с первыми, вторыми и третьими входами элемецтов ИЛИ первой группы, выходы элементов ИЛИ первой группы соединены соответственно с информационньми входами накапливающего сумматора, выходы которого соединены соответственно с вторьми входами элементов И первой группы, выходы элементов И первой группы соединены соответственно с разрядными входами регистра сдвига, выходы которого соединены соответственно с вторыми входами элементов И второй группы, отличающееся тем, что, с целью повышения точности, в него введены первый и второй элементы ЗИ-ИЛИ, первый и второй элементы И, первый и второй элементы 2И-РШИ, § вторая и третья группы элементов HLTMj (Л первый, второй и третий элементы ИЛИ, схема сравнения, триггер, причем четвертый и пятый выходы .распределителя импульсов соединены соответственно с первым и BTopbw входами третьего элемента ИЛИ, тестой выход распределителя импульсов соединен с первым и вторым входами первого элемента 2И-ИПИ и с первым и :п вторьи входами второго элемента 2ИИЛИ, седьмой выход распределителя о :л импульсов соединен с первым.входом триггера, восьмой выход распределио теля импульсов соединен с первым входом первого элемента ЗИ-ИЛИ, первьм входом второго элемента ЗИ-ИЛИ, первым входом первого элемента И, первым входом второго элемента И, девятый, десятый, одиннадцатый, двенадцатый выходы распределителя импульсов соединены соответственно с первым вторым, третьим и четвертым входами второго элемента ИЛИ, тринадцатый, четырнадцатый и пятнадцатый

Изобретение относится к вычислительной технике, в частности к устройствам для вычисления функций BWда 7x2 +у2.

Известно устройство, предназначенн для вычисления функции вида.Ух2 у2 содержащее два делителя частоты, два блока утроения числа, четыре счетчика, элемент НЕ, схему сравнения, блок управления, элементй И. Устройство fij выполняет вычисления в соответствии с алгоритмом

2-так 1А1,1Ы,1|(Д4б)| Д(д-6)||,

где А - код числа Х; В - код числа У.

Устройство позволяет достаточно быстро вычислить функцию 2 , но имеет довольно большую погрешность вычисления (максимальная ошибка измерения 6,07%).

Наиболее близким по технической сущности к предполагаемому является устройство, содержащее два регистра операндов, накапливающий суммато четыре группы элементов И, группу элементов ИЛИ, регистр сдвига, распределитель импульсов, выходы которого с первого по восьмой подключен соответственно к входу обнуления сумматора, к управляющим входам эле ментов И первой, второй и третьей группы, регистра сдвига, элементов И четвертой группы. Устройство выполняет вычисления в соответствии с формулой 1,,5.1МТуТг{Аи((ЬКО,;Г|/А1-|В|| где А и В - коды чисел X и У соответственно. Как видно из приведенной выше фо мулы для вычисления функции требует ся выполнить всего несколько тарных операций. Максимальная погрешность вычисления функции состав ляет 5,72% 2j. К недостаткам прототипа следует отнести большую погрешность вычисления и наличие масштабногокоэффициента (1,5), так как использование такого устройства в автоматических вычислительных системах потребует дополнительных аппаратурных затрат. Цель изобретения - повьш1ение точ ности вычисления. Поставленная цель достигается тем, что в устройство для вычислени содержащее первый и второй регистры операнда, накапливающий сумматор, первую, вторую, третью и четвертую группы элементов И, перву группу элементов ИЛИ, регистр сдвига, распределитель импульсов, причем первый выход распределителя импульсов соединен с первыми входами элементов И первой группы, второй выход распределителя импульсов соединен с входом записи регистра сдвига, третий выход распределителя импульсов соединен с первыми входами элементов И второй группы, выходы первого регистра операнда соединены соответственно с первыми входами элементов И третьей группы, вы ходы второго регистра операнда соединены соответственно с первыми вхо дами элементов И четвертой группы, выходы элементов И второй, третьей и четвертой групп соединены соответ свенно с первыми, вторыми и третьими входами элементов ИЛИ первой 504 группы, выходы элементов ИЛИ первой группы соединены соответственно с информационньгми входами накапливающего сумматора, выходы которого сое- динены соответственно с вторыми входами элементов И первой группы, выходы элементов И первой группы соединены соответственно с разрядными входами регистра сдвига, выходы которого соединены соответственно с вторыми входами элементов И второй группы, введены первый и второй элементы ЗИ-ШШ, первый и второй элементы И, первый и второй элементы 2И-ИЛИ, вторая и третья группы элементов ИЛИ, первБгй, второй и третий элементы ИЛИ, схема сравнения, триггер, причем четвертый и пятый выходы распределителя импульсов соединены соответственно с первым и вторым входами третьего элемента ИЛИ, шестой выход распределителя импульсов соединен с первым и вторым входами первого элемента 2И-ИЛИ и первым и вторым входами второго элемента 2И-ИЛИ, седьмой выход распределителя импульсов соединен с первым входом триггера, восьмой выход распределителя импульсов соединен с первым входом первого элемента ЗИ-ИЛИ, первым входом второго элемента ЗИ-ИЛИ, первым входом первого элемента И, первым входом второго элемента И, девятый, десятый, одиннадцатый, двенадцатый выходы распределителя импульсов соединены соответственно с первым, вторым, третьим и четвертым входами второго элемента ИЛИ, тринадцатый, четырнадцатый и пятнадцатый выходы распределителя импульсов соединены соответственно с первым, вторым и третьим входами первого элемента ИЛИ, шестнадцатый выход распределителя импульсов соединен с вторым входом первого элемента ЗИ-ИЛИ и вторым входом второго элемента ЗИ-ИЛИ, семнадцатый выход распределителя импульсов соеди нен с третьим входом первого элемента 2И-Ш1И и третьим входом второго элемента 2И-Ш1И, восемнадцатый выход распределителя импульсов соединен с третьим входом первого элемента ЗИ-ИЛИ и третьим входом второго элемента ЗИ-ШШ, выход первого элемента ЗИ-ШШ соединен с вторыми входами элементов ШШ третьей группы, выход второго элемента ЗИ-ИЛИ i1 соединен с вторым входом элемента И четвертой группы, выход первого элемента И соединен-, с входом считывания первого регистраоперанда, вьгхоД второго элемента И соединен с входом считывания второго регистра операнда, выход первого элемента 2И-ИЛИ соединен с входом записи первого регистра операнда, выход второго элемента 2И-ИЛИ соединен с входом записи второго регистра операнда, выход первого элемента ИЛИ соединен с входом сдвига регистра сдвига, выход второго элемента ИЛИ соединен с входом суммирования накапливающего сумматора, выход третьего элемента ИЛИ соединен входом обнуления накаливающего сумматора, входы первого операнда устройства соединены соответственно с первыми входами элементов ИЛИ второй группы, входы второго операнда устройства соединены соответственно с первыми входами элементов ИЛИ третьей группы, выходы накапливающего сумматора соединены соответственно с вторыми входами элементов ИЛИ второй и третьей групп выходы элементов ИЛИ второй группы соединены с разрядными входами первого регистра операнда, выходы элементов ИЛИ третьей группы соединены с разрядньми входами второго регист ра операнда, выходы первого регистр операнда соединены соответственно с первыми входами схемы сравнения, выходы второго регистра операнда соединены соответственно с вторыми входами схемы сравнения, прямой выход схемы сравнения соединен с вторым входом триггера и четвертым вхо дом первого элемента ЗИ-ИЛИ, инверсный выход схемы сравнения соединен с четвертым входом второго элемента , первый выход триггера соеди нен с пятым входом первого элемента ЗИ-ИЛИ, пятым входом второго элемен та ЗИ-ИЛИ, вторым входом второго элемента И, четвертым входом второг элемента 2И-ИЛИ, второй выход триггера соединен с шестым входом перво го элемента ЗИ-ИЛИ, шестым входом второго элемента ЗИ-ИЛИ, вторым вхо дом первого элемента И, четвертым входом первр,го элемента 2И-ЧШИ. На чертеже представлена блок-схе ма устройства. i Устройство для вычисления корня квадратного из суммы квадратов двух 50 чисел содержит первый 1 и второй 2 регистры операнда, накапливающий сумматор 3; первую, вторую, третью, четвертую группы элементов И 4-7; первый элемент ЗИ-ИЛИ 8, второй элемент ЗИ-ИЛИ 9; первьй элемент И 10; второй элемент И 11; первый элемейт 2И-ИЛИ 12; второй элемент 2И-ИЛИ 13; первую группу элементов ИЛИ 14; вторую группу элементов ИЛИ 15; третью группу элементов ИЛИ 16; регистр 17 сдвига; распределитель 18 импульсов; первый элемент ИЛИ 19; второй элемент ИЛИ 20; третий элемент ИЛИ 21; схему 22 сравнения; триггер 23. В предлагаемом устройстве реализуется следующий алгоритм вычисления: определяется максимальное и минимальное значения операндов X и У А макс (х,у| (1) В мин ( X ,у| (2) вычисляется значение функции jc( I{ftl4l|Blj ау (-3J Устройство работает следующим образом. Управляющий сигнал распределителя 18 импульсов в каждый момент времени присутствует только на одном из выходов и в .течение периода времени вычисления функции +У появляется на выходных распределителя 18 импульсов (эти выходы являются выходами регистра последовательного сдвига) в следующей последовательности: четвертый выход 27, шестой выход 29, седьмой выход 30, восьмой выход 31, девятый выход 32, первый выход 24, второй выход 25, 13-й выход 36, 14-й выход 37, 15-й выход 38, третий выход 36, 10-й выход 33, 16-й выход 39, 11-й выход 34, 17-й выход 40, пятый выход 28, 18-й выход 41, 12-й выход 35. В начальный момент времени управляющий сигнал с четвертого выхода 27 распределителя 18 импульсов проходит через третий элемент ИЖ 21 на вход обнуления содержимого накапливающего сумматора 3. На первые входы второй группы 15 и третьей группы элементов ИЛИ 16 поступают коды чисел X и У соответственно. С выходов второй группы 15 и третьей группы элементов ИЛИ 16 коды X и У поступают на входы первого 1 и второго 2 регистров операнда. Управляющий сигнал с шестого выхода 29 распределителя 18 импульсов, независимо от состояния триггера 23, проходит на выходы первого 12 и второго 13 элементов 2И-ИЛИ и разрешает запись-входных кодов X и У в первый 1 и второй 2 регистры операнда 2 соответственно.После этого, в схеме 22 срав нения производится сравнение кодов, за писанных в первом 1 и втором 2 регистра операндов.Сигнал результата сравнени снимаемьм с прямого выхода схемы 22 ср нения, поступает на второй вход триггера 23 и по управляющему сигналу, поступающему с седьмого выхода 30 распределителя 18 импульсов на первый вход триггера, записывает в триггер 23. Выходные сигналы, снимаемые с пр мого и инверсного выходов триггера, устанавливают последовательность прохождения управляющих сигналов с восьмого, 16-го, 17-го выходов 31, 39, 40 распределителя 18 импуль сов через первый и второй элементы ЗИ-ИЛИ 9, первый 10 и второй 11 элементы И, первый 12 и второй 13 элементы 2И-ИЛИ. В случае , что соответствует , , на прямом выходе триггера 23 устанавливается управляющий сигнал, который определяет работу схемы в этом режиме. По этому сигналу триггера управляющий сигнал с восьмого выхода 21 распределителя 18 им пульсов коммутируется через первый элемент 8 ЗИ-ИЛИ и второй элемент И 11, открывает третью группу элементов И 6 и производит сдвиг содер жимого второго регистра 2 операнда R на один разряд вправо (-г) . Код первого регистра 1 операнда через открытую третью группу элементов И 6 и nepBjrra группу элементов ИЛИ 14 записывается в накапливающий сумматор 3. Запись производится по управляющему сигналу с девятого выход 22 распределителя 18 импульсов, который проходит второй элемент ИЛИ 2 и поступает на первый управляющий вход сумматора 3. Затем управляющий сигнал с первого выхода 24 распреде лителя 18 импульсов открывает перву

группу элементов И 4 и содержимое накапливающего сумматора 3 переписывается по управляющему сигналу с

В случае (, ) по управлякнцему сигналу на втором выходе триггера 23 устанавливается следуювторого выхода 25 распределителя 18 импульсов в. регистр 17 сдвига. Управляющие сигналы с 13-го, 14-го, . 15-го выходов 36-38 распределителя 18 импульсов проходят последовательно через первый элемент ИЛИ 19 и сдвигают код регистра 17 сдвига на три разряда вправо (-). После этого управляющий сигнал с третьего выхода 26 распределителя 18 импусов открывает вторую группу элементов И 5. При этом обратный код регистра 17 сдвига поступает через открытую вторую группу элементов И 5, первую группу элементов, ИЛИ 14, и по управляющему сигналу с 10-го выхода 33 распределителя 18 импульсов суммируется с содержанием накапливающего сумматора 3. Результат суммирования представляет собой код числа - А. В следующий момент времени управляющий сигнал с 16-го выхода 39 проходит на выход второго элемента ЗИ-ИЛИ 9, так как установлен управляющий сигнал на .первом входе триггера 23, открывает четвертую группу элементов И 7, При этом код второго регистра 2 операнда через открытую четвертую группу элементов И 7 и первую группу элементов ИЛИ 14 поступает на вход накапливающего сзгмматора 3. В результате сложения по управляющему сигналу с 11-го выхода 34 распределителя импульсов 18, содержимого сумматора 3 с кодом второго регистра 2 операнда в сумматоре получится код Управляющий сигнал с первого выхода триггера 23 разрешает прохождение следующего управляющего сигнала с 17-го выхода 40 распределителя импульсов 18 на выход второго элемента 2И-ИЛИ и затем на второй управляющий вход второго регистра 2 операнда. По этому сигналу код, записанный в накапливающем сумматоре 3, проходит через третью группу элементов ИЛИ 16 и записывается во второй регистр 2 операнда. После этого сумматор обнуляется вторично по управляющему сигналу с пятого выхода 28 распределителя tS импульсов, который проходит через третий элемент ИЛИ 21. 9 щее прохождение управляющих сигнало распределителя 18 импульсов: сигнал с восьмого 31 коммутируе ся на выход второго элемента ЗИ-ИЖ и первого элемента И 10; сигнал с 16-го выхода 39 коммутируется на вы ход первого элемента ЗИ-ИЛИ 8; сигнал с 17-гр выхода 40 коммутируется на выход первого элемента 2И-Ш1И 12 В остальном работа устройства пр X У происходит аналогично рассмотренному вьше случают (X У), в соответствии с указанной коммутацией управляющих сигналов распределителя 18 импульсов. После вьшолнения приведенных выше операций в устройстве производится второе сравнение кодов чисел, записанных в первом 1 и втором ,2 регистрах операндов. Выходные сигналы схемы 22 сравнения коммутируют прохождение управляющего сигнала с 18-го выхода 4.1 распределителя 18 импульсов таким образом, чтобы на вход сумматора поступал наибольший из кодов, записанный в регистры опе рандов . Так при А + i В (,) I82 по сигналу на первом выходе схемы 2 0О сравнения управляющий сигнал с 18-го выхода 21 распределителя 18 импульсов проходит на выход первого элемента ЗИ-ИЛИ 8 и открывает третью группу элементов И 6. При + -Впо о 2. сигналу на втором выходе схемы 22 сравнения управляющий сигнал с 18-го выхода 41 распределителя 18 импульсов проходит на выход второго элемента ЗИ-ИЛИ 9 и открывает четвертую группу элементов И 7. Аналогично происходит работа для случая А У, В X. Наибольший код регистров 1 и 2 операндов записьшается в накапливающий сумматор 3 по управляющему сигналу с 12-го выхода 35 распределителя 18 импульсов, который проходит через второй элемент ИЛИ 20, Код числа, помещенного в накапливающий сумматор 3, будет соответствовать функции вида 2 Максимальное значение относительной погрешности предлагаемого устройства составляет 2,99%. Использование предлагаемого устройства приведет к существенному повышению эффективности цифровых автоматических измерительных устройств за счет увеличения точности до 2,99% и оперативности вычисления функции вида 2. Ух +у2 .

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для вычисления функции вида | 1976 |

|

SU645154A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для вычисления квадратного корня из суммы квадратов двух чисел | 1977 |

|

SU627477A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1984-09-23—Публикация

1983-05-06—Подача