Изобретение относится к вычислительной технике и может быть использовано для построения средств автоматики, функциональных узлов систем управления и др.

Известны двоичные вычитатели (см., например, рис.9.11в на стр. 220 в книге Токхейм Р. Основы цифровой электроники. М.: Мир, 1988г.), которые содержат логические элементы и формируют двоичный код разности трех одноразрядных двоичных чисел, задаваемых двоичными сигналами, и бит, определяющий ее знак.

К причине, препятствующей достижению указанного ниже технического результата при использовании известных двоичных вычитателей, относятся ограниченные функциональные возможности, обусловленные тем, что не допускается обработка трех двухразрядных двоичных чисел.

Наиболее близким устройством того же назначения к заявленному изобретению по совокупности признаков является принятый за прототип двоичный вычитатель (патент РФ 2709653, кл. G06F7/50, 2019г.), который содержит четыре элемента исключающее ИЛИ, элемент И, элемент ИЛИ, два мажоритарных элемента и формирует двоичный код разности трех двухразрядных двоичных чисел, задаваемых двоичными сигналами, и бит, определяющий ее знак.

К причине, препятствующей достижению указанного ниже технического результата при использовании прототипа, относятся большие аппаратурные затраты, обусловленные тем, что прототип дополнительно содержит три элемента НЕ.

Техническим результатом изобретения является уменьшение аппаратурных затрат при сохранении функциональных возможностей прототипа.

Указанный технический результат при осуществлении изобретения достигается тем, что в двоичном вычитателе, содержащем четыре элемента исключающее ИЛИ, элемент И, элемент ИЛИ и два мажоритарных элемента, второй вход i-го (

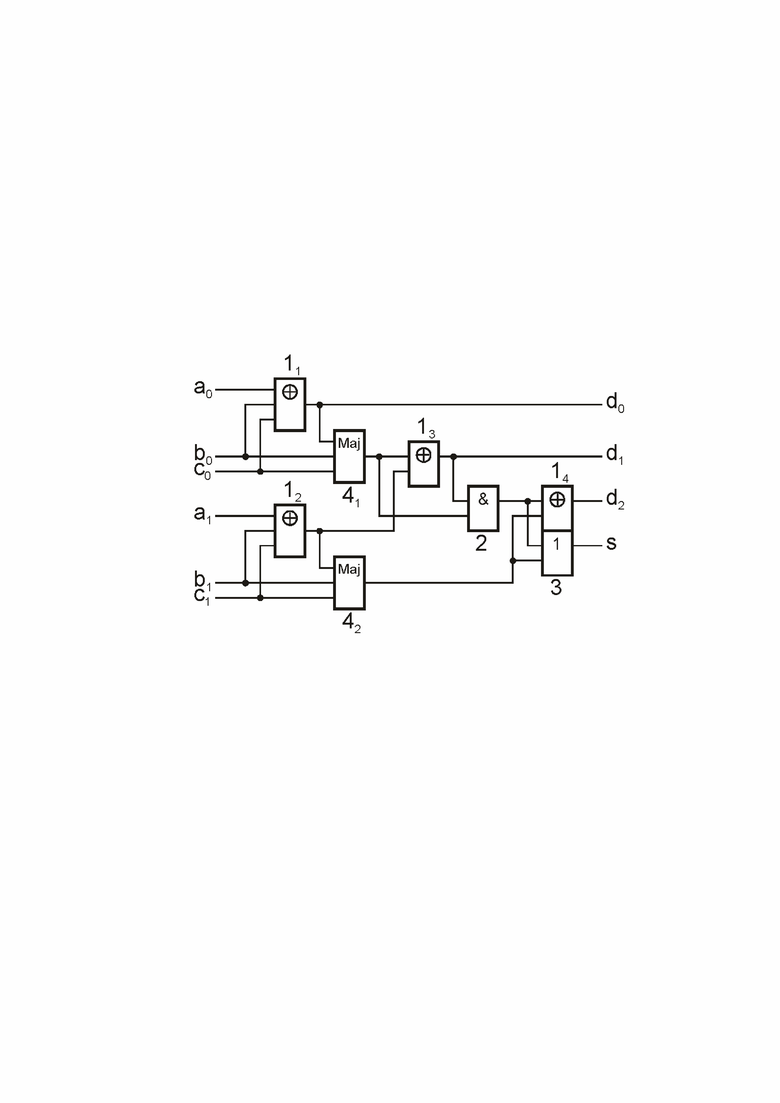

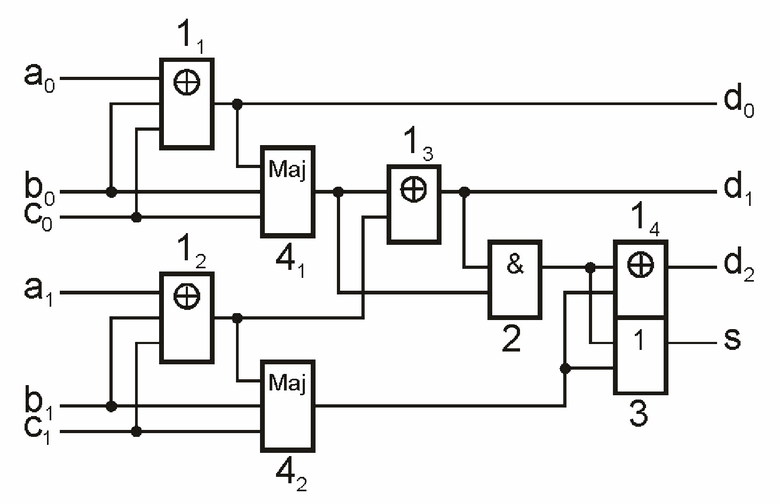

На чертеже представлена схема предлагаемого двоичного вычитателя.

Двоичный вычитатель содержит элементы исключающее ИЛИ 11,…,14, элемент И 2, элемент ИЛИ 3 и мажоритарные элементы 41, 42, причем второй, третий входы элемента 1i (

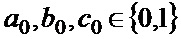

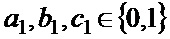

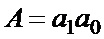

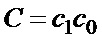

Работа предлагаемого двоичного вычитателя осуществляется следующим образом. На его первый, второй, третий и четвертый, пятый, шестой входы подаются соответственно двоичные сигналы

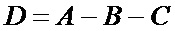

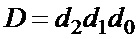

Согласно представленной таблице имеем

Вышеизложенные сведения позволяют сделать вывод, что предлагаемый двоичный вычитатель формирует двоичный код разности трех двухразрядных двоичных чисел, задаваемых двоичными сигналами, и бит, определяющий ее знак, и обладает меньшими по сравнению с прототипом аппаратурными затратами.

| название | год | авторы | номер документа |

|---|---|---|---|

| МАЖОРИТАРНЫЙ МОДУЛЬ | 2022 |

|

RU2789750C1 |

| ДВОИЧНЫЙ ВЫЧИТАТЕЛЬ | 2019 |

|

RU2709653C1 |

| УСТРОЙСТВО ДЛЯ ДЕТЕКТИРОВАНИЯ В БЛОКАХ ДАННЫХ ГРУПП ЕДИНИЧНЫХ БИТ В ЗАДАННЫХ ГРАНИЦАХ | 2024 |

|

RU2828235C1 |

| Устройство для умножения | 1987 |

|

SU1501043A1 |

| Счетчик | 1978 |

|

SU801252A1 |

| УСТРОЙСТВО ДЛЯ ДЕТЕКТИРОВАНИЯ ГРУПП ЕДИНИЧНЫХ БИТ И МАКСИМАЛЬНОЙ ГРУППЫ В БЛОКАХ ДАННЫХ | 2023 |

|

RU2800039C1 |

| СПОСОБ И УСТРОЙСТВО СУММИРОВАНИЯ ДВОИЧНО-ДЕСЯТИЧНЫХ ЧИСЕЛ | 2007 |

|

RU2402803C2 |

| Устройство для умножения | 1978 |

|

SU763897A1 |

| Трехканальное мажоритарное устройство | 1979 |

|

SU847322A1 |

| Устройство для выбора среднего по величине числа | 1981 |

|

SU1005336A1 |

Изобретение относится к вычислительной технике. Технический результат заключается в обеспечении формирования двоичного кода разности трех двухразрядных двоичных чисел, задаваемых двоичными сигналами, и бита, определяющего ее знак, и уменьшении аппаратурных затрат при сохранении функциональных возможностей. Двоичный вычитатель содержит четыре элемента: исключающее ИЛИ, элемент И, элемент ИЛИ и два мажоритарных элемента. 1 ил., 1 табл.

Двоичный вычитатель, содержащий четыре элемента: исключающее ИЛИ, элемент И, элемент ИЛИ и два мажоритарных элемента, причем второй вход i-го (

| ДВОИЧНЫЙ ВЫЧИТАТЕЛЬ | 2019 |

|

RU2709653C1 |

| ДВОИЧНЫЙ ВЫЧИТАТЕЛЬ | 2016 |

|

RU2629453C1 |

| ДВОИЧНЫЙ ВЫЧИТАТЕЛЬ | 2015 |

|

RU2621375C1 |

| Станок для придания концам круглых радиаторных трубок шестигранного сечения | 1924 |

|

SU2019A1 |

| US 4685079 A, 04.08.1987. | |||

Авторы

Даты

2023-02-07—Публикация

2022-03-18—Подача