1Изобретение относится к автоматике и вычислительной технике предназначено для вычитания из десятичного числа двух последовательностей импульсов и может быть использовано в различных областях техники и промьш ленности для построения устройств дискретной автоматики, цифровых вычислительных устройств и устройств измерения остаточного запаса в процессе расхода однотипной продукции любой физической природы.

Цель.изобретения - расширение фунциональных возможностей путем одноврменного счета по двум каналам.

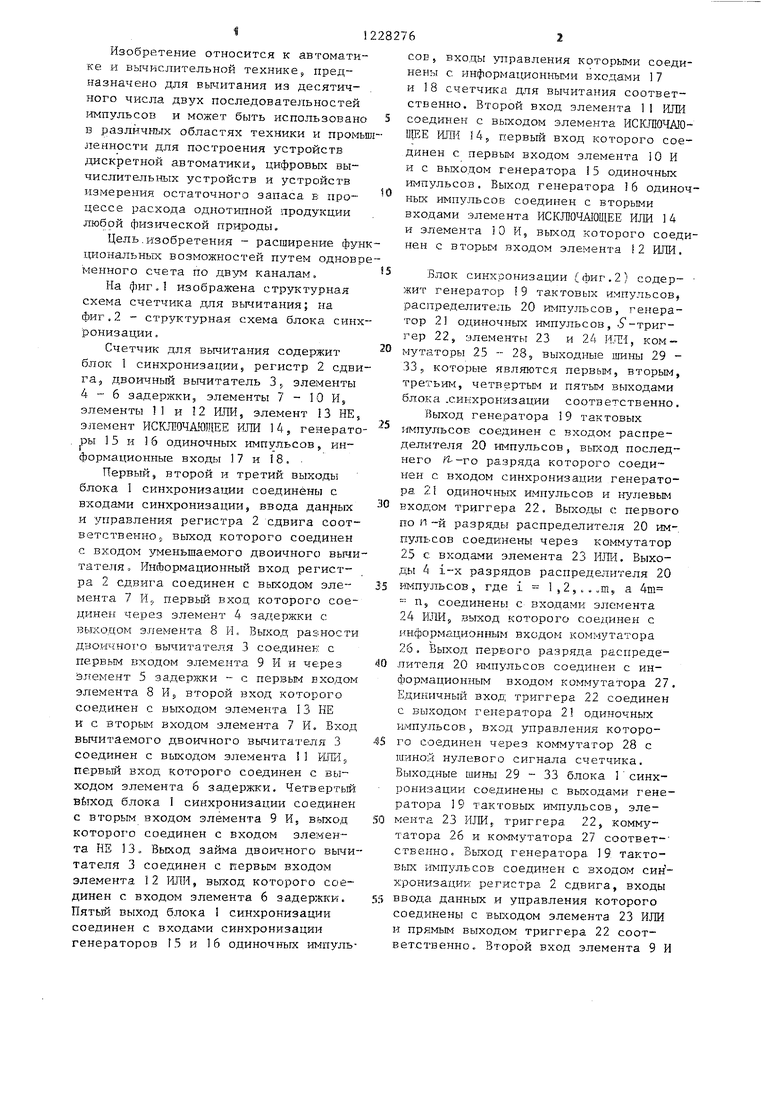

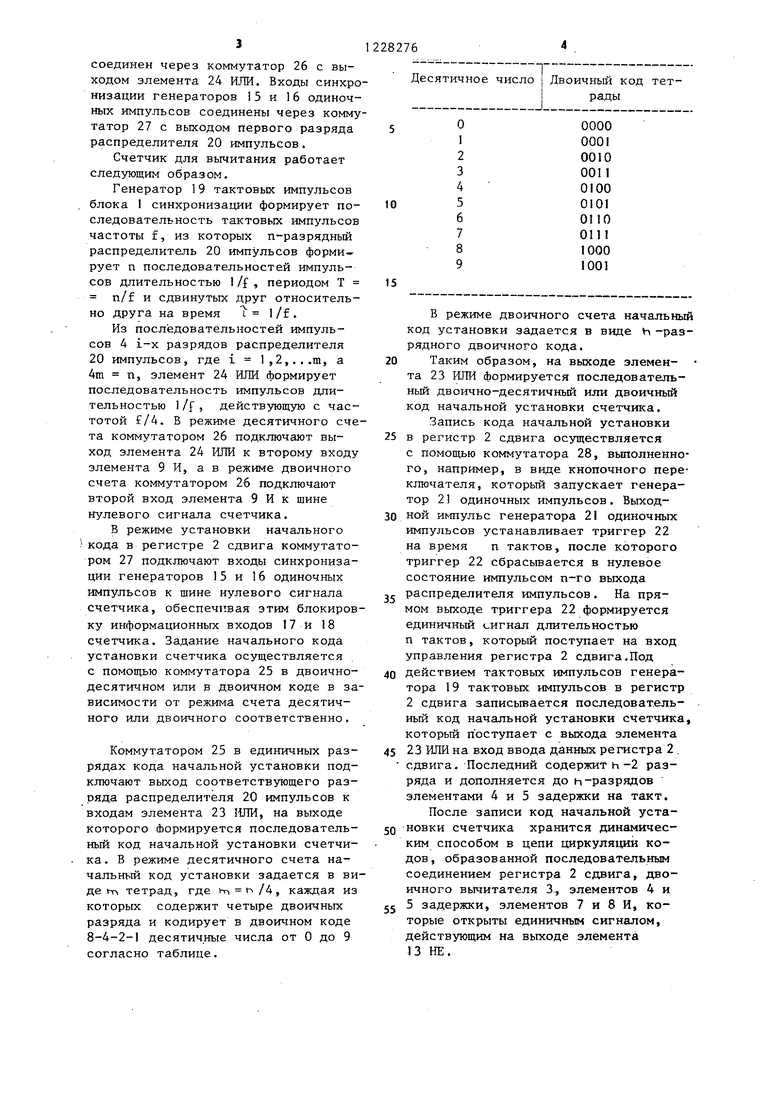

На фиг, изображена структурная схема счетчика для вычитания; на фиг.2 - структурная схема блока синхронизации .

Счетчик для вычитания содержит блок 1 синхронизации, регистр 2 сдвига, двоичный вычитатель 3,, элементы 4-6 задержки, элементы 7 - 10 И, элементы 11 и 12 ИЛИ, элемент 13 НЕ, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 14, генераторы 15 и 16 одиночных импульсов 5 информационные входы 17 и i 8. .

Первый, второй и третий выходы блока 1 синхронизации соединены с входами синхронизации, ввода данных и управления регистра 2 сдвига соответственно,) выход которого соединен с входом зл еньшаемого двоичного вычи тателя. Информационный вход регистра 2 сдвига соединен с выходом элемента 7 PI, первый вход которого соединен через элемент 4 задержки с выходом элемента 8 И. Выход разности двоичного вычитателя 3 соединен с первым входом элемента 9 И и через з.тгемент 5 задержки - с первым входом элемента 8 Hj второй вход которого соединен с выходом элемента 13 НЕ и с вторььч входом элемента 7 И. Вход вычитаемого двоичного вычитатехгя 3 соединен с выходом элемента 11 ИЛйэ первьй вход которого соединен с выходом элемента 6 задержки. Четвертый блока I синхронизации соединен с вторым входом элемента 9 И, выход которого соединен с входом элемента НЕ 13. Выход займа двоичного вычи татепя 3 соединен с первым входом элемента 12 ИЛИ, выход которого соединен с входом элемента 6 задержки. Пятый выход блока I синхронизации соединен с входами синхронизации генераторов 15 и 16 одиночных

0

5

0

5

0

5

0

0

сов, входы управления которыми соединены с информационными входами 17 и 18 счетчика для вычитания соответственно. Второй вход элемента 1 1 -ШИ соединен с выходом элемента ИСКЛЮЧАЮ- DfEE 1-ШТ 14, первый вход которого соединен с первым входом элемента 10 И и с вькодом генератора 15 одиночных М гаульсов. Выход генератора 16 одиночных импульсов соединен с вторыми входами элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 14 и элемента 10 И, выход которого соединен с вторьм входом элемента 12 ИЛИ.

Блок синхронизации (фиг.2) содер- жит генератор 19 тактовых импульсов, распределитель 20 импульсов, генератор 21 одиночных импульсов, .5 -триг- гер 22, элементы 23 и 24 ИЛИ, коммутаторы 25 -- 28, выходные шины 29 - 335 которые являются первым, вторьм, третьш-1, четвертым и пятым выходами блока .синхронизации соответственно.

Выход генератора 19 тактовых импульсов соединен с входом распределителя 20 импульсов, выход последнего П- -го разряда которого соединен с входом синхронизации генератора 21 одиночных импульсов и нулевым входом триггера 22. Выходы с первого по и-и разряды распределителя 20 импульсов соединены через коммутатор 25 с входами элемента 23 ИЛИ. Выходы 4 i-x разрядов распределителя 20 импульсов, где i 1,2,..„т5 а 4т п, соединены с входами элемента 24 ИЛИ, выход которого соединен с информационюлм входом коммутатора 26. Выход первого разряда распределителя 20 импульсов соединен с информационным входом коммутатора 27. Единичный вход триггера 22 соединен с }зыходом генератора 21 одиночных ампульсов, вход управления которого соединен через коммутатор 28 с шиной нулевого сигнала счетчика. Выходные шины 29 - 33 блока 1 синхронизации соединены с вьгходами генератора 19 тактовых импульсов, элемента 23 ИЛИ, триггера 22, коммутатора 26 и коммутатора 27 соответ- ственно. Выход генератора 19 тактовых импульсов соединен с входом син - хронизацик регистра 2 сдвига, входы ввода данных и управления которого соединены с выходом элемента 23 ИЛИ и прямыь выходом триггера 22 соответственно. Второй вход элемента 9 И

соединен через коммутатор 26 с выходом элемента 24 ИЛИ. Входы синхронизации генераторов 15 и 16 одиночных импульсов соединены через коммутатор 27 с выходом первого разряда распределителя 20 импульсов.

Счетчик для вычитания работает следующим образом.

Генератор 19 тактовых импульсов блока 1 синхронизации формирует последовательность тактовых импульсов частоты f, из которых п-разрядный распределитель 20 импульсов формирует п последовательностей импульсов длительностью 1/f, периодом Т n/f и сдвинутых друг относительно друга на время 7 1 /f .

Из последовательностей импульсов 4 i-x разрядов распределителя 20 импульсов, где i l,2,...m, а 4m п, элемент 24 ИЛИ формирует последовательность импульсов длительностью 1/f, действующую с частотой /4. В режиме десятичного счета коммутатором 26 подключают выход элемента 24 ИЛИ к второму входу элемента 9 И, а в режиме двоичного счета коммутатором 26 подключают второй вход элемента 9 И к шине нулевого сигнала счетчика.

В режиме установки начального кода в регистре 2 сдвига коммутатором 27 подключают входы синхронизации генераторов 15 и 16 одиночных импульсов к шине нулевого сигнала счетчика, обеспечивая этим блокировку информационных входов 17 И 18 счетчика. Задание начального кода установки счетчика осуществляется с помощью коммутатора 25 в двоично- десятичном или в двоичном коде в зависимости от режима счета десятичного или двоичного соответственно.

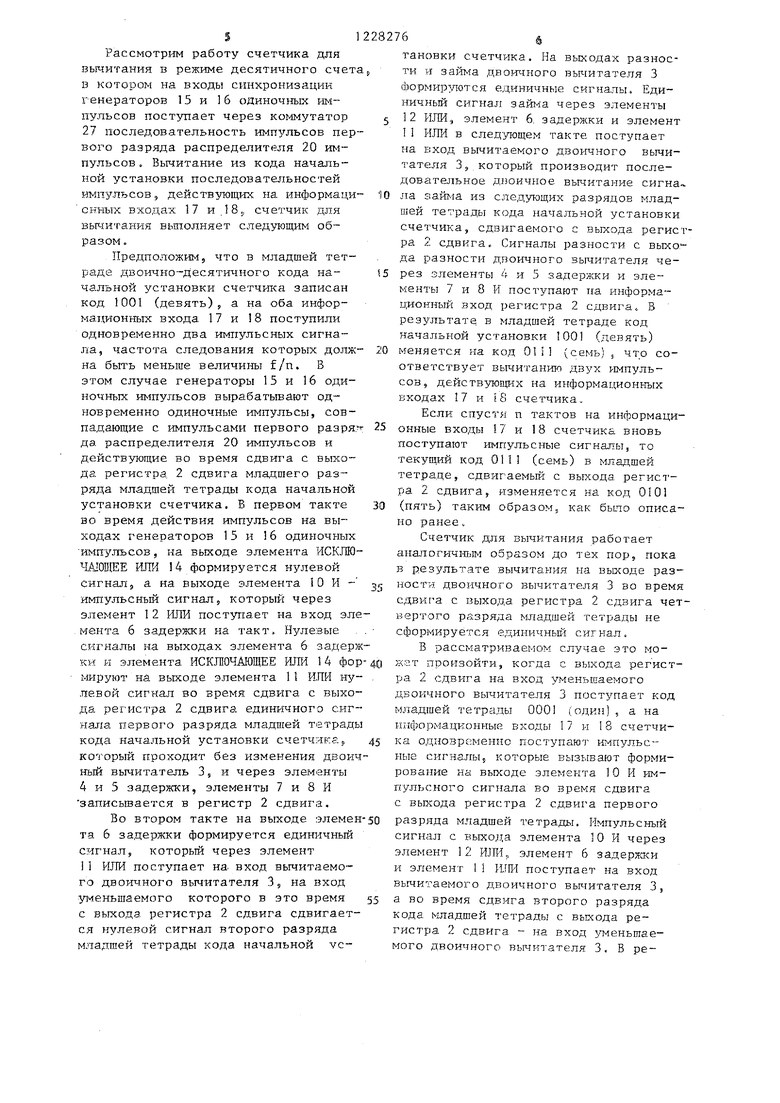

Коммутатором 25 в единичных разрядах кода начальной установки подключают выход соответствующего разряда распределителя 20 импульсов к входам элемента 23 IlTOi, на выходе которого Формируется последовательный код начальной установки счетчика . В режиме десятичного счета начальный код установки задается в виде 1-р, тетрад, где н-, г. /4, каждая из которых содержит четыре двоичных разряда и кодирует в двоичном коде 8-4-2-1 десятичные числа от О до 9 согласно таблице.

В режиме двоичного счета начальный код установки задается в виде h -разрядного двоичного кода.

Таким образом, на выходе элемента 23 ИЛИ формируется последовательный двоично-десятичный или двоичный код начальной установки счетчика. Запись кода начальной установки

в регистр 2 сдвига осуществляется с помощью коммутатора 28, выполненного, например, в виде кнопочного переключателя, который запускает генератор 21 одиночных импульсов. Выходной импульс генератора 21 одиночных импульсов устанавливает триггер 22 на время п тактов, после которого триггер 22 сбрасьгоается в нулевое состояние импульсом п-го выхода

распределителя импульсов. На прямом выходе триггера 22 формируется единичный сигнал длительностью п тактов, который поступает на вход управления регистра 2 сдвига.Под

действием тактовых импульсов генератора 19 тактовых импульсов в регистр 2 сдвига записьшается последовательный код начальной установки счетчика, который поступает с выхода элемента

23 ИЛИ на вход ввода данных регистра 2 . сдвига. Последний содержитh-2 разряда и дополняется до и-разрядов элементами 4 и 5 задержки на такт. После записи код начальной установки счетчика храьштся динамическим способом в цепи циркуляции кодов, образованной последовательным соединением регистра 2 сдвига, двоичного вычитателя 3, элементов 4 и

5 задержки, элементов 7 и 8 И, которые открыты единичным сигналом, действующим на выходе элемента 13 НЕ.

Рассмотрим работу счетчика для вьЕЧитания в режиме десятичного счета в котором на входы С11нхроиизации генераторов 15 и 16 одиночных импульсов поступает через коммутатор 27 последовательность импульсов первого разряда распред(шителя 20 иъ5- пульсов. Вычитание на кода начальной установки последовательностей импульсов 5 действующих на информационных входах 17 и 18,. счетчик для вычитания выполняет следующим образом .

Предположим, что в младшей тетраде двоично-десятичного кода начальной установки счетчика записан код 1001 (девять)J а на оба информационных входа 17 и 18 поступили одновременно два импульсных сигнала, частота следования которых должна быть меньше величины f/n. В этом случае генераторы 15 и 16 одиночных импульсов вырабатьшают одновременно одиночные импульсы, совпадающие с импульсами первого да распределителя 20 импульсов и действующие во время сдвига с выхода регистра. 2 сдвига младшего разряда младшей тетрады кода начальной установки счетчика. В первом такте во время действия импульсов на выходах генераторов 15 и 16 одиночных импу-гльсов, на выходе элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 4 формируется нулевой сигнал, а на выходе элемента 10 И - импульсный сигналS который через элемент 12 ИЛИ поступает на вход элемента 6 задержки на такт. Нулевые сигналы на выходах элемента 6 задержи элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 14 фор-40 жат произойти, когда с выхода регистра 2 сдвига на вход уменьшаемого двоичного вычитателя 3 поступает код ладшей тетрады 000 (один) , а на информадионные входы 17 и 18 счетчика одновременно поступают ш-тульс- ные сигналы,, которые вызывают формирование на вьпгаде элемента 10 И импульсного сигнала во время сдвига с выхода регистра 2 сдвига первого разряда младшей тетрады. Импульсный сигнал с выхода элемента 10 И через элемент 12 ШП1, элемент 6 задержки и элемент 1 1 ШШ поступает на вход вычитаемого двоичного вычитателя 3, а во время сдвига второго разряда кода младшей тетрады с вькода регистра 2 сдвига - на вход т еньгаае- мого двоичного вычитателя 3. В реKVI

ыируют на выходе элемента 11 ИЛИ нулевой сигнал во время сдвига с выхода регистра 2 сдвига единичного сигнала первого разряда младшей тетрады кода начальной установки счетчикаj 45 который проходит без изменения двоичный вьгчитатель 3, и через элементы 4 и 5 задержки, элементы 7 и 8 И записьшается в регистр 2 сдвига.

Во втором такте на выходе элемен-50 та 6 задержки формируется единичный сигнал, которьй через элемент 11 ИЛИ поступает на вход вычитаемого двоичного вычитателя 3, на вход у У1еньщаемого которого в это время 55 с выхода регистра 2 сдвига сдвигается нулевой сигнал второго разряда младшей тетрады кода начальной vc0

5

0

5

0

;

тановки счетчика. На выходах разности и займа двоичного вьиитателя 3 а)Ормир ;лотся единичные сигналы. Единичный сигнал через элементы 12 Р1ЛИ, элемент 6. задержки и элемент I1 ИЛИ в следующем такте поступает на вход вычитаемого двоичного вычи- тателя 3, который производит последовательное двоичное вычитание сигна- ла займа из следующих разрядов младшей тетрады кода начальной установки счетчика, сдвигаемого с выхода регистра ;; сдвига. Сигналы разности с выхо - да разности двоичного вычитателя через элементы 4 и 5 задержки и элементы 7 и 8 И поступают на. информационный вход регистра 2 сдвига. В результате в младп1ей тетраде код начальной установки 1001 (девять) меняется на код 01J1 (семь) j что соответствует вычитанию двух импульсов, действующих на информационных входах 17 и fS счетчика.

Если спустя п тактов на информади- онные входы 17 и 18 счетчика вновь поступают импульсные сигналы, то текущий код 01П (семь) в младшей тетраде, сдвигаемый с выхода регистра 2 сдвига, изменяется на код 0101 (пять) таким образом, как бьшо описано ранее.

Счетчик для вычитания работает аналогичным образом до тех пор, пока в результате вычитания на вькоде разности двоичного вычитателя 3 во время сдвига с выхода регистра 2 сдвига четвертого разряда млади ей тетрады не сформируется единичньш сигнал

В рассматриваемом случае это мозультате двоичного вычитания, которое последовательно во времени выполняется двоичным вычитателем 3, на его выходе разности формируется эап- рещенньй код 1111. В этом случае во время сдвига четвертого разряда младшей тетрады с выхода регистра 2 сдвига на выходе элемента 24 ИЛИ блока 1 синхронизации формируется импульсный сигнал, который через коммутатор 26 поступает на второй вход элемента 9 И.

Так как на выходе разности двоичного вычитателя 3 в это время действует единичный сигнал четвертого разряда запрещенного кода 1111, то на выходе элемента 9 И формируется импульсный сигнал, который через элемент 13 НЕ блокирует элементы 7 и 8 И, запрещая этим передачу единичного сигнала второго разряда запрещенного кода младшей тетрады с выхода элемента 4 задержки на информационный вход регистра 2 сдвига и единичного сигнала третьего разряда запрещенного кода младшей тетрады с выхода элемента 5 задержки на вход элемента 4 задержки..В результате в регистр 2 сдвига запи- сьшается в младшей тетраде вместо запрещенного кода 1111 текущий код результата IOOI (девять).Поскольку в процессе Лормирования двоичным вычитателем 3 запрещенного кода 1111 формируется сигнал займа из четвертого разряда младшей тетрады, который через элемент 12 l-fflH, элемент 6 задержки и элемент 11 ИЛИ поступает на вход вычитаемого двоичного вычитателя 3 во время сдвига с выхода регистра 2 сдвига первого разряда второй тетрады кода начальной установки счетчика, то двоичный вычитатель 3 уменьшает код начальной установки счетчика на одну единицу.

Дальнейшие вычисления во всех тетрадах двоично-десятичного кода, сдвигаемого с выхода регистра 2 сдвига, осутдествляется аналогичным образом в случае одновременного поступления на информационные входы 17 и 18 импульсных сигналов.

Если импульсные сигналы на информационные входы 17 и 18 поступают последовательно во времени или только на один из информационных входов 17 или 18 счетчика, то элемент 10 И блокируется нулевым сигналом выхода например, генератора 15 одиночных

импульсов, а на выходе элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 14 формируется им- пульсньш сигнал выхода, например, генератора 16 одиночных импульсов. Импульсный сигнал с выхода элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 14 поступает через элемент 1 1 ИШ-Г на вход вычитаемого двоичного вычитателя 3 во время сдвига с выхода регистра 2 сдвига первого разряда младшей тетрады текущего двоично-десятичного кода. Двоичный вычитатель 3 уменьшает текущий код младшей тетрады на единицу младшего разряда, а результат вычитания записывается через элементы 4 и 5 задержки и элементы 7 и 8 И в регистр 2 сдвига.

Дальнейшие вычисления выполняются счетчиком для вычитания аналогичным образом до окончания действия последовательности импульсов на информационных входах 17 и 18 счетчика.

В этом случае на выходах генераторов 15 и 16 одиночных импульсов формируются нулевые сигналы, которые поддерживают на входе вычитаемого двоичного вычитателя 3 нулевой сигнал. Двоично-десятичный код результата вычитания из кода начальной установки счетчика двух последовательностей импульсов Фиксируется динамическим способом в цепи циркуляции кодов через регистр 2 сдвига, двоич- ньй вычитатель 3, элементы 4 и 5 задержки и элементы 7 и 8 И, В режиме двоичного счета с помощью к6 мyтaтo- ра 26 блока 1 синхронизации блокируют элемент 9 И, который через элемент 13 НЕ поддерживает элементы 7 и 8 И в открытом состоянии, В результате двоичный код результата вычитания с выхода разности двоичного вычитателя 3 записьшается без изменения в регистр 2 сдвига через элемен1Ъ1 4 и 5 задержки и элементы 7 и 8 И.

Формула изобретения

Счетчик для вычитания, содержащий регистр сдвига, двоичный вычитатель, первый, второй и третий элементы задержки, первый, второй, третий и четвертый элементы И, первый элемент ИЛИ, элемент НЕ и блок синхронизации, содержащий генератор тактовых импульсов, распределитель импульсов, генератор одиночных импульсов, триггер, два элемента ИЛИ и четыре коммутатора, выход генератора тактовых импульсов соединен с входами синхронизации; регистра сдвига и распределителя импульсов, выходы п разрядов которого, где п - количество разрядов регистра сдвига, соединены через первый коммутатор с входами первого элемента ИЛИ блока синхрониза-ции, выход которого подключен к входу ввода данных регистра сдвига, выход п-го разряда распределителя импульсов соединен с нулевым входом триггера и с входом синхронизации генератора одиночных импульсов блока синхронизации, вход зтгравления которого соединен через второй коммутатор с шиной нулевого сигнала счетчика5 выход генератора одиночных импульсов блока синхронизации соединен с единичным входом триггера, прямой выход которого соединен с входом управления регистра сдвига, выходы 4 i-x разрядов распределителя импульсов5 где i 1,2,,, m, а 4m - n, соединены с входами второго элемента ИЛИ блока синхронизации, .выход которого через третий коммутатор подключен к первому входу пер- iBoro элемента И, выход первого разряда распределителя импульсов соеди- нен с информационным входом четвертого коммутатора блока синхронизации, выход регистра сдвига - с входом уменьшаемого двоичного вычита- теля5 информационный вход регистра сдвига - с выходом второго элемента И, первый вход которого соединен через первый элемент задержки с выходом третьего элемента И, выход разности двоичного вычитателя соеди-- йен с вторым входом первого элемента И и через второй элемент задержки -- с первым входом третьего элемента И, второй вход которого объединен с вторьм входом второго элемента И и соединен через элемент НЕ с выходом первого элемента И, вход вычитаемого двоичного вычитателя соединен с выходом первого элемента ИЛИ счетчика, первый вход которого соедииен с выходом третьего элемента задержки от личающийся тем, что, с целью расширения функциональных возможностей путем одновременного счета по двум Каналам, в

5 него введены второй и третий генераторы одиночные импульсов, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ и второй элемент ИЛИ, иртеы выход займа двоичного вычитателя соединен с первым входом второ0 го элемента ИЛИ счетчика, выход которого соединен с входом третьего элемента задержки, второй вход первого элемента ИЛИ счетчика соединен с выходом элемента ИСКЛЮЧАЮП1ЕЕ ИЛИ,

5 первьй вход которого объединен с первым; входом четвертого элемента Ни соединен с выходом второго генератора одиночных импульсов,выход третьего генератора одиночных импульсов сое0 динен с вторьми входами элемента ИСКЛЮЧАЮЩЕЕ ИЛИ и четвертого элемента И, выход которого соединен с вторым входом второго элемента ИЛИ счетчи;ка, выход четвертого коммутас тора блока синхронизации соединен с входами синхронизации второго и третьего генераторов одиночных импуль сов, входы управления которыми являются соответственно первым и вторым информационными входами счетчика.

фие.2

| название | год | авторы | номер документа |

|---|---|---|---|

| Генератор циклов | 1981 |

|

SU964616A1 |

| Устройство для контроля экспоненциальных процессов | 1984 |

|

SU1282087A1 |

| Устройство для вычисления показателя экспоненциальной функции | 1986 |

|

SU1335990A1 |

| Функциональный преобразователь | 1982 |

|

SU1100621A1 |

| Преобразователь двоично-десятичного кода в двоичный код | 1985 |

|

SU1292188A1 |

| Устройство для вычисления показателя экспоненциальной функции | 1985 |

|

SU1270770A1 |

| Устройство для допускового контроля объекта | 1984 |

|

SU1246060A1 |

| Квадратор | 1987 |

|

SU1501049A1 |

| Устройство для контроля родовой деятельности | 1988 |

|

SU1605259A1 |

| Генератор двоичных чисел | 1984 |

|

SU1201827A1 |

Изобретение относится к области автоматики и вычислительной техники. Цель изобретения - расширение функциональных возможностей. Счетчик содержит блок I синхронизации, регистр 2 сдвига, двоичный вычита- тель 3, элементы 4-6 задержки, элементы 7-10 И, элементы 11 и 12 ИЛИ, элемент 13 НЕ, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 14, генераторы 15 и 16 одиночных импульсов и информационные входы 17 и 18. В описании приведена структурная схема блока I синхронизации. Введение в устройство генераторов одиночных импульсов, элемента ИСКЛЮЧАЮПЩЕ ИЛИ, элемента 12 ИЛИ и образование новых связей с элементами устройства позволяет производить счет одновременно по двум каналам.2 ил. 1 табл. (Л to to СХ) го Од ft

| РЕВЕРСИВНЫЙ ДЕСЯТИЧНЫЙ СЧЕТЧИК | 0 |

|

SU374643A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Десятичный вычитающий счетчик | 1979 |

|

SU809584A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Авторское свидетельство СССР № 756645, кл | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1986-04-30—Публикация

1984-01-26—Подача