1

Изобретение относится к области вычислительной техники и может быть использовано в качестве пифрового генератора значений логарифмической функции.

Известно устройство 1, позволяюш,ее вычислять логарифмы по алгоритмам цифра за цифрой. Оно содержит блок постоянной памяти, сумматоры, регистры, блоки управления. Недостатком такого устройства является низкое быстродействие.

Наиболее близким ио технической сущности и достигаемому результату к изобретению является устройство 2, содержащее блок управления, регистры старших и младщих разрядов аргумента, выходами соединенные соответственно с первым и вторым блоками постоянной памяти, выходы которых соединены с первыми входами сумматора и коммутатора соответственно, второй вход сумматора соединен с выходом коммутатора, а выход - со входом выходного регистра.

Однако такое устройство при достаточно высоком быстродействии имеет больщие объемы блоков постоянной памяти.

Целью изобретения является уменьщение суммарной информационной емкости блоков постоянной памяти, т. е. уменьшение оборудования.

Поставлеиная цель достигается тем, что в предлагаемое устройство дополнительно введены третий блок постоянной намяти, сдвпгатель, блок управления сдвигателем, триггер, который своим входом подсоединен к выходу знакового разряда сумматора, выход

5 сумматора соединен со входом третьего блока постоянной памяти, выход которого соединен через сдвигатель со вторым входом коммутатора, управляющий вход сдвигателя соединен с выходом блока управления сдвига10 телем, первый и второй входы которого соединены соответственно с выходом триггера и выходом регистра младшихразрядов аргумента, нри этом блок управления подсоединен к управляющего входу коммутатора.

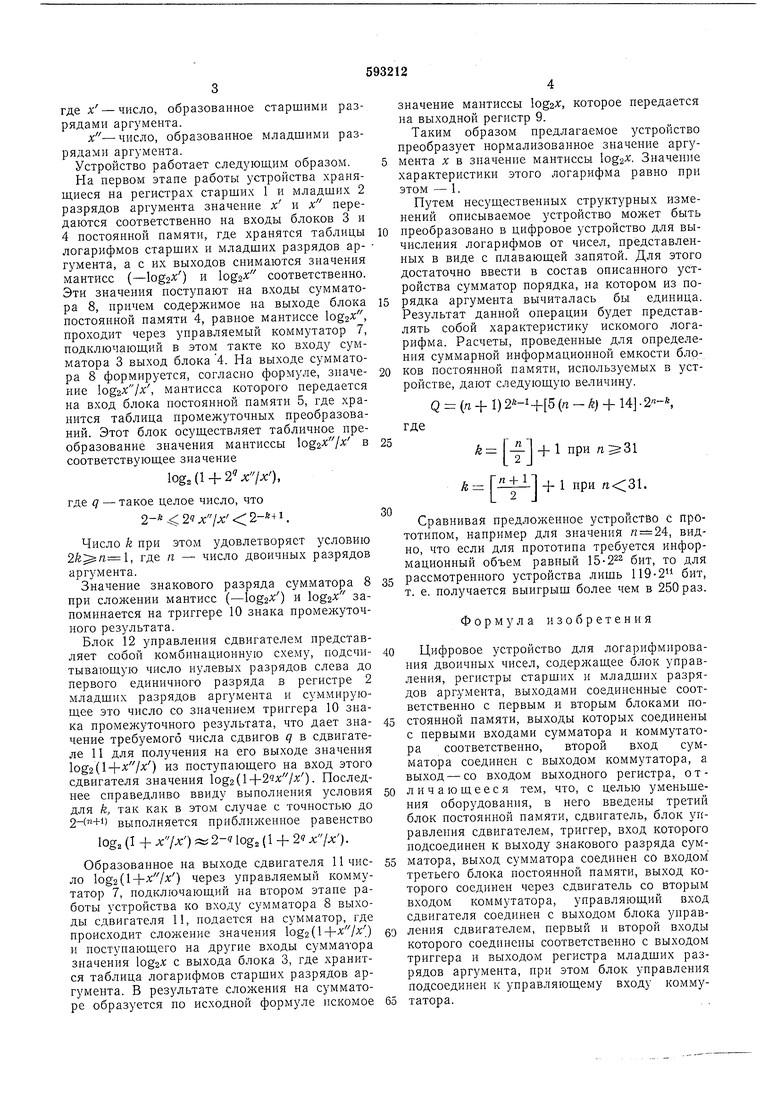

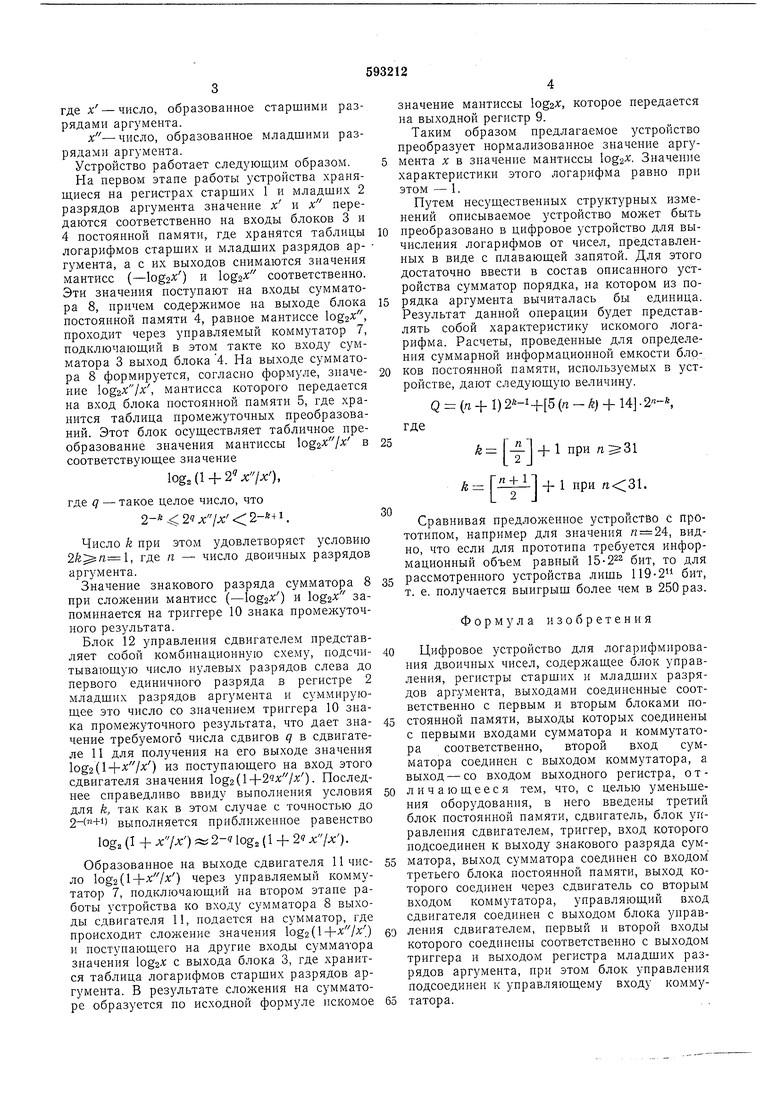

15 На чертеже представлена блок-схема устройства.

Устройство содержит регистры старших 1 и младших 2 разрядов аргумента, блоки постоянной памяти 3-5, блок управления 6, коммутатор 7, сумматор 8, выходной регистр 9, триггер 10, сдвпгатель И, блок 12 управления сдвигателем.

Вычисление двоичного логарифма от нор25 мализованного аргумента х () производится в предлагаемом устройстве па ососнове соотношений

log, (X + X) : lOg.X + log. (1 + )

30logs log., X - logj.,

где л; - число, образованное старшими разрядами аргумеита.

х.-число, образованное младшими разрядами аргумента.

Устройство работает следующим образом.

На первом этапе работы устройства храняш,иеся на регистрах старших 1 и младших 2 разрядов аргумента значение к и к передаются соответственно на входы блоков 3 и 4 постоянной памяти, где хранятся таблицы логарифмов старших и младших разрядов аргумента, а с их выходов снимаются значения мантисс (-loga ;) и соответственно. Эти значения поступают на входы сумматора 8, причем содержимое на выходе блока постоянной памяти 4, равиое мантиссе log2J;, проходит через управляемый коммутатор 7, подключаюш,ий в этом такте ко входу сумматора 3 выход блока 4. На выходе сумматора 8 формируется, согласно , значение 1о§2х7л;, мантисса которого передается на вход блока постоянной памяти 5, где хранится таблица промежуточных преобразований. Этот блок осуществляет табличное преобразование значения мантиссы в соответствующее значение

log,(l + ), где q - такое целое число, что

2- 2- .

Число k при этом удовлетворяет условию , где п - число двоичных разрядов аргумента.

Значение знакового разряда сумматора 8 при слолсении мантисс (-loga ;) и log2A; запоминается на триггере 10 знака промежуточного результата.

Блок 12 управления сдвигателем представляет собой комбинационную схему, подсчитывающую число нулевых разрядов слева до первого единичного разряда в регистре 2 младших разрядов аргумента и суммирующее это число со значением триггера 10 знака промежуточного результата, что дает значение требуемого числа сдвигов q в сдвигателе 11 для получения на его выходе значения Iog2() из поступающего на вход этого сдвигателя значения log2(l+29A;7 ). Последнее справедливо ввиду выполнения условия для k, так как в этом случае с точностью до 2-(+1) выполняется приближенное равенство

log, (I + ) 2-9 log, (1 + 2 х,1к.

Образованное на выходе сдвигателя 11 число log2(l+xV ) через управляемый коммутатор 7, подключающий на втором этапе работы устройства ко входу сумматора 8 выходы сдвигателя И, подается на сумматор, где происходит сложение значения Iog2( и постунающего на другие входы сумматора значения logax с выхода блока 3, где хранится таблица логарифмов старщих разрядов аргумента. В результате сложения на сумматоре образуется по исходной формуле искомое

значение мантиссы log2X, которое передается на выходной регистр 9.

Таким образом предлагаемое устройство

преобразует нормализованное значение аргумента х в значение мантиссы log2X Значение

характеристики этого логарифма равно при

этом - 1.

Путем несущественных структурных изменений описываемое устройство может быть

преобразовано в цифровое устройство для вычисления логарифмов от чисел, представленных в виде с плавающей запятой. Для этого достаточно ввести в состав описанного устройства сумматор порядка, на котором из порядка аргумента вычиталась бы единица. Результат данной операции будет представлять собой характеристику искомого логарифма. Расчеты, проведенные для определения суммарной информационной емкости блоков постоянной памяти, используемых в устройстве, дают следующую величину.

Q (га + I) (« - /fe) + 14. 2«где

: + 1 при k + 1 при .

Сравнивая предложенное устройство с прототипом, например для значения п 24, видно, что если для прототипа требуется информационный объем равный 15-222 бит, то для рассмотренного устройства лищь 1192 бит, т. е. получается выигрыщ более чем в 250 раз.

Формула изобретения

Цифровое устройство для логарифмирования двоичных чисел, содержащее блок управления, регистры старших и младших разрядов аргумента, выходами соединенные соответственно с первым и вторым блоками постоянкой памяти, выходы которых соединены с первыми входами сумматора и коммутатора соответственно, второй вход сумматора соединен с выходом коммутатора, а выход - со входом выходного регистра, отл и чающееся тем, что, с целью уменьшения оборудования, в него введены третий блок постоянной памяти, сдвигатель, блок управления сдвигателем, триггер, вход которого подсоединен к выходу знакового разряда сумматора, выход сумматора соединен со входом третьего блока постоянной памяти, выход которого соединен через сдвигатель со вторым входом коммутатора, управляющий вход сдвигателя соединен с выходом блока управления сдвигателем, первый и второй входы которого соединены соответственно с выходом триггера и выходом регистра младщих разрядов аргумента, при этом блок управления подсоединен к управляющему входу коммутатора.

Источники информации, принятые во внимание при экспертизе

1. Байков В. Д., Смолов В. Б. «Аппаратурная реализация элементарных функций в ЦВМ, из-во ЛГУ, Л., 1975.

2. Авторское свидетельство СССР №342193, кл. G 06G 7/26, 1972.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для логарифмирования двоичных чисел | 2015 |

|

RU2614932C1 |

| Цифровое устройство для логарифми-РОВАНия дВОичНыХ чиСЕл | 1979 |

|

SU813414A2 |

| Цифровое вычислительное устройство | 1973 |

|

SU474012A2 |

| Цифровой генератор логарифмической функции | 1980 |

|

SU942006A1 |

| Устройство для логарифмирования массивов двоичных чисел | 1979 |

|

SU926654A1 |

| Устройство для вычисления функций Z @ = @ @ @ / @ и Z @ = @ @ @ / @ | 1988 |

|

SU1539771A1 |

| Устройство для вычисления элементарных функций | 1983 |

|

SU1160429A1 |

| Множительное устройство | 1978 |

|

SU824206A1 |

| Арифметическое устройство | 1978 |

|

SU687982A1 |

| Конвейерное устройство для потенцирования массивов двоичных чисел | 1984 |

|

SU1191909A1 |

Авторы

Даты

1978-02-15—Публикация

1976-05-20—Подача