Изобретение относится к вычислительной технике и предназначено для использования в высокоскоростных универсальных и специализированных вычислительных устройствах, служащих для обработки больших массивов данных.

Известно цифровое логарифмирующее устройство, содержащее входной регистр, блок вычисления характеристики, сдвигающий регистр, блоквьвделения остатка, результирующий регистр, блок деления, два деаифратора, блок умножения, блок априорной информации, сумматор С11.

Недостатком этого устройства является низкое быстродействие.

Наиболее близким по технической сущности к предлагаемому является цифровое устройство для логарифмирования двоичных чисел 2, содержащее ре;гистры старших и младашх разрядов аргумента, три блока постоянной памяти, блок управления, коммутатор, сумматор, выходной регистр, триггер, сдвигатель, блок управления сдвигателем. Быстродействие известного устройства не превышает

Т-, 2t(yM+2tebi6+tcAa. где t(y - время суммирования на

сумматоре;

6bi5 время выборки из памяти; tcAB время сдвига промежуточного результата.

Недостатком известного устрой10ства является низкое быстродействие при обработке массивов чисел.

Цель изобретения - повышение быстродействия при обработке массивов чисел.

15

Поставленная цель достигается тем, что в устройство для логарифмирования массивов двоичных чисел, содержащее регистры старших и младших разрядов аргумента, три блока, памяти,

20 блок синхронизации, первый сумматор, выходной регистр, триггер, сдвигатель, блок управления сдвигателем, причем выход регистра старших разрядов аргумента соединен со входом 25 первого блока памяти, а выход регистра младших разрядов аргумента соединен со входом второго блока памяти заход знакового разряда первого сумматора соединен со входом

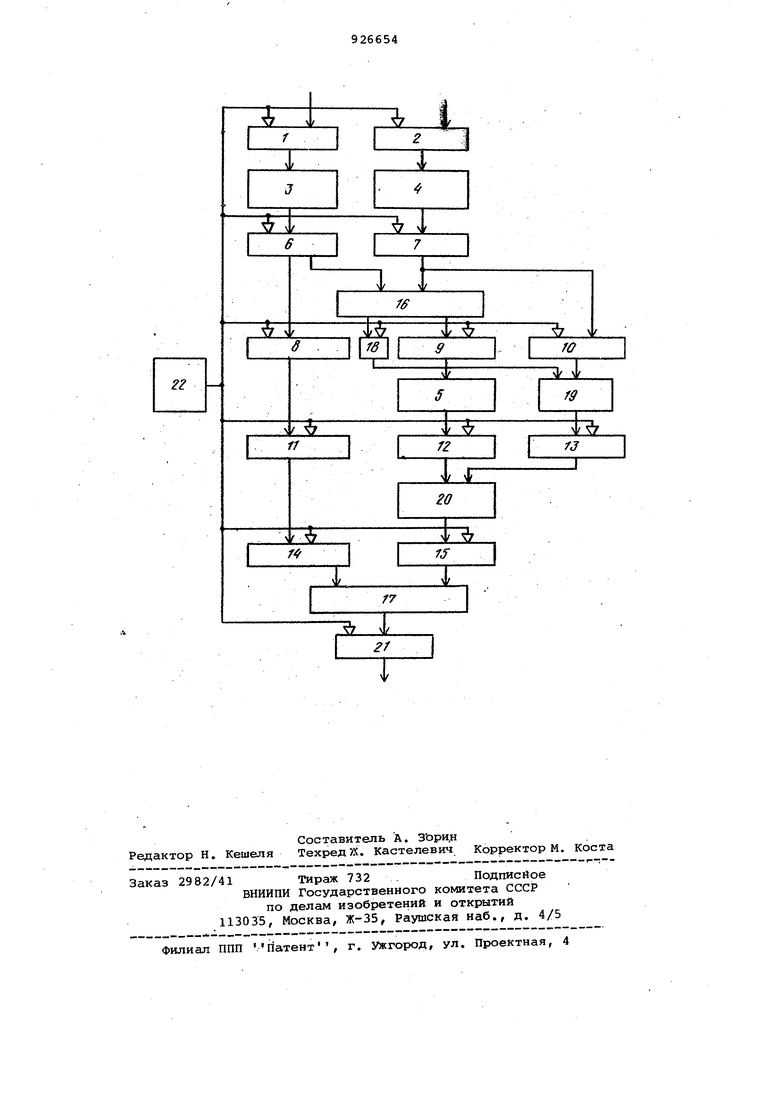

30 триггера, соединенного выходом с управляюйщм входом блока управления сдвигателем, дополнительно введены десять регистров и второй сумматор причем информационный вход первого регистра соединен с выходом первого блока памяти, прямой выход первого регистра соединен с информационным входом второго регистра, инверсный выход первого регистра - с первым входом первого сумматора, второй вход которого соединен с информационным входом третьего регистра и вы ходом четвертого регистра, информационный вход которого соединен с выходом второго блока памяти, выход первого сумматора соединен с ин формационным входом пятого регистра выход которого соединен со входом третьего блока памяти, выход которо соединен со входом шестого регистра выход которого соединен с информационным входом сдвигателя, управляющий вход которого через седьмой регистр соединен с выходом блока управления сдвигателем, информационный вход которого соединен с выходом третьего регистра, выход сдви гателя соединен с информационным входом восьмого регистра, выход которого соединен с первым входом вто рого суммато за, второй вход которог соединен с .выходом девятого регистра, соединенного входом через десятый регистр с выходом второго регис ра, выход второго сумматора соедине со входом выходного регистра, управляющие входы всех регистров и Триггера соединены с выходом блока синхрони э ации. На чертеже представлена блок-схе ма устройства. Устройство содержит регистр 1 ста1Я1Шх разрядов аргумента, регистр 2 младийх разрядов аргумента, блоки 3-5 памяти, регистры 6-15, сумматоры 16 и 17, триггер 18, блок i9. управления сдвигателем, сдвигатель 20, выходной регистр 21 и блок 22 синхронизации. Регистры 6-15 предназначены для кратковременного запоминания резуль татов промежуточных вычислений и для обеспечения конвейерного способ обработки. Вычисление двоичного логарифма от нормализованного аргумента X ( i i X 1) производится на основе соотношений (x+х ) eogq,.(l + v .+ ЕГ) и еод, |г еодгг х , где х - число, образованное старшими разрядами аргумента; х - число, образованное младшими разрядами аргумента. Устройство работает следующим образом. В первом такте работы устройства в регистры старших 1 и младших 2 разрядов аргумента поступают соответственно значения х и .Эти числа передаются соответственно на входы блоков 3 и 4 памяти, где хранятся таблицы логарифмов старших и младших разрядов аргумента, а с их выходов снимс1ются значения togqx и соответственно. Во втором такте эти значения записываются в регистры 6, 7 и поступают на входы сумматора l6, причем содержимое регистра 6 поступает с инверсных его выходов. На выходе суг,рлатора 16 формируется значение . в третьем такте значение мантиссы, полученное в сумматоре, поступает в регистр 9, а содержимое регистров 6 и 7 - в регистрал 8 и 10 соответственно. Значение знакового разряда сумматора 16 запоминается в триггере 18 (знака промежуточного результата). Содержимое регистра 9 передается на вход блока 5 памяти, где хранится таблица промежуточных преобразований. Этот блок осуществляет табличное преобразование значения мантиссы в соответствующее значение + 2 где q - такое целое число, что .-К. /. 2 2 Число k при этом удовлетворяет условию 2k у п-1, где п - число двоичных разрядов аргумента. В том же такте содержимое триггера 18 и регистра .10 поступают на блок 19 управления.сдвигателем, который представляет собой комбинационную схему, подсчитывающую число нулевых разрядов слева до первого единичного разряда в регистре 10 и суммирующую это -число со значением триггера 18, что дает значение требуемого числа сдвигов q в сдвигателё 20 для получения на его выходе значения Bogri {l Ir) из -, поступающего на вход., этого сдвигателя значения eogtj(l-t-2 -| ) . В четвертом такте значение регистра 8 переписывается в регистр 11, значение с -выхода блока 5 памяти записывается в регистр 12, а число ч из блока 19 управления сдвигателем записывается в регистр 13. В сдвигателё 20 осуществляется сдвиг на 1 разрядов значения togQ() и на его,,выходе получается значение 2ogQ(l+-|r)f что справедливо ввиду выполнения условия для К, та.к как в этом случае с точностью до 2 выполняется приближенное равенство.

«09(1+) ( ).

В пятом такте образованное на выходе сдвигателя 20 число записывается в регистр 15, а число Eogij x из регистра 11 записывается в регистр 14. Эти числа поступгиот на сумматор 17, где происх сэдит сложение значений Bogrj U + - ) и togiL х , в ;результате чего в сумматоре 17 образуется по исходной формуле искомое значение . в шестом такте это значение передается на выходной регистр 21 и из него - на выход устройства. Тактовые импульсы, управляющие работой устройства, генерируют блок 22 синхронизации.

Таким образом, предлагаемое устройство преобразует нормализованное значение аргумента х в значение eog(.

Предлагаемое устройство работает по конвейерному, принципу, позтому в каждом такте в устройство можно вводить новый операнд. При обработк массивов чисел в каждом такте на выходе устройства появляется результат вычисления. Длительность такта определяется задержкой в наиболее медленном узле устройства, которым в данном случае является суглматор. Поэтому при обработке массивов данных быстродействие устройства равно Т tcVM

Формула Изобретения

Устройство для логарифмирований массивов двоичных чисел, содержащее регистры старших и младших разр5шов аргумента, три блока памяти, блок синхронизадии, перилй сумматор, выходной регистр, триггер, сдвигателэ блок управления сдвигателем, пЕжчем выход регистра старших разрядов аргумента соединен со входом первого блока памяти, а выход регистра младших разрядов аргумента соединен со входом второго блока памяти, выход

знакового разряда первого сумматора соединен со входом триггера, соединенного выходом с управляющим входом блока управления сдвигателем, отличающееся тем, что, с целью повышения быстродействия, в устройство введены десять регистров и второй сумматор, причем информационный вход первого регистра соединен с выходом .первого блока памяти,

0 прямой выход первого регистра соединен с информационным входом второго регистра, инверсный выход первоI4D регистра - с первым входом п.ер вого с ячматора, второй вход которого соединен с информационным входом третьего регистра и выходом четвертого регистра, инфо1 4ационный вход которого соединен с выходом второго блока памяти, выход первого суьола0 тора соединен с информационным входом пятого регистра, выход которого соединен со входе третьего блока памяти, выход которого соединен со входом шестого регистра, выход ко5 торогчэ соединен с информационным входом сдвигателя, управляющий вход которого через седьмой регистр соединен с выходом блока управления сдвигателем, информационный вход

- которого соединен с выходом третьего регистра,, выход сдвигателя соединен с информационным входс восьмого регистра, выход которого соединен с первым входом второго сумматора, второЛ вход которого сое5динен с выходом девятого регистра, соело1нениого входсж через десятый регистр с выходом второго регистра, выход второго cytouiaTopa соединен со входом выходного регистра, управляющие входы всех регистров и триггера соединены с выходс У1 блока синхронизации.

Источиики информации, S принятые во внимание при экспертизе

1.Авторское свидетельство СССР 624233, кл. G Об F 15/20, 1978.

2.Авторское свидетельство СССР 593212, кл. G 06 F 7/38 1978 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для логарифмирования | 1981 |

|

SU962926A1 |

| Устройство для логарифмирования двоичных чисел | 2015 |

|

RU2614932C1 |

| Устройство для логарифмирования двоичных чисел | 1981 |

|

SU1059572A1 |

| Цифровое устройство для логарифмирования двоичных чисел | 1976 |

|

SU593212A1 |

| Цифровое устройство для логарифми-РОВАНия дВОичНыХ чиСЕл | 1979 |

|

SU813414A2 |

| Цифровой генератор логарифмической функции | 1980 |

|

SU942006A1 |

| Устройство для логарифмирования двоичных чисел | 1980 |

|

SU924705A1 |

| Конвейерное устройство для потенцирования массивов двоичных чисел | 1984 |

|

SU1191909A1 |

| Конвейерное устройство для вычисления функции @ | 1984 |

|

SU1179326A1 |

| Устройство для деления | 1981 |

|

SU987621A1 |

ж

Т

Авторы

Даты

1982-05-07—Публикация

1979-12-25—Подача