(5) ЦИФРОВОЕ ЛОГАРИФМИРУЮЩЕЕ УСТРОЙСТВО

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для умножения | 1985 |

|

SU1278838A1 |

| Цифровой анализатор спектра | 1987 |

|

SU1413545A1 |

| Цифровой функциональный преобразователь | 1983 |

|

SU1107136A1 |

| Делительное устройство | 1982 |

|

SU1104508A1 |

| Вычислительное устройство | 1975 |

|

SU705478A1 |

| Преобразователь координат | 1988 |

|

SU1566345A1 |

| Устройство для решения уравнений математической физики | 1986 |

|

SU1363260A1 |

| Цифровой функциональный преобразователь | 1986 |

|

SU1339554A1 |

| Устройство для вычисления гиперболических функций | 1980 |

|

SU957208A1 |

| Арифметическое устройство для вычисления коэффициентов Фурье | 1986 |

|

SU1388893A1 |

Изобретение относится к цифровой вычислительной технике и может бытА использовано в ЦВМ, работающих в позиционных системах счисления с фикси рованной запятой. Известно логарифмирующее устройст во, содержащее генератор тактовых, импульсов, регистр сдвига, регистр характеристик логарифмов, счетчик.и схему сравнения. Это устройство срез нительно просто l . Недостаток устройства - низкая точность воспроизведений логарифмической функции. Наиболее близким к предлагаемому по технической сущности является устройство, содержащее два сумматора сдвиговый регистр, блок управления, элемент ИЛИ, элемент И, запоминающий блок, регистр, триггер, причем сумма тор соединен со сдвиговым регистром, выход которого подключен ко входу сумматора, другими входами сумматор связан со входом элемента ИЛИ, входом элемента И и входом блока управления, выход элемента И подключен к третьему входу блока управления, выход запоминающего блока связан со входом регистра, выход которого соединен со входом второго сумматора, выход блока управления подключен ко входам сдвигающего регистра, регистра, запоминающего блока, триггера и обоих сумматоров 2. Недостатком данного устройства является невысокое быстродействие. Цель изобретения - увеличение быстродействия. Поставленная Цель достигается тем, что в устройство, содержащее первый и второй сумматоры, блок управления и блок памяти, управляющий вход которого соединен с первым выходом блока управления, второй выход которого соединен с тактовыми входами первого и второго сумматоров, первый ,информационный вход и первый выход первого сумматора соединенны со3Э

ответственно с входом аргумента устройства и входом блока управления, информационный вход и выход второго сумматора соединены соответственно с выходом блока памяти и выходом устройства, дополнительно введены блок сдвига, умножитель и блок управляющей переменной, первый и второй управляющий входы которого соединены с третьим и четвертым выходами блока управления соответственно, пятый выход которого соединен с входом выдачи первого сумматора, второй информационный вход и второй выход которого соединены соответственно с выходом умножителя и информационным входом блока сдвига, управляющий вход которого подключен к пятому выходу блока управления, первый выход, которого соединен с управляющим вхо дом умножителя, первый и второй информационные входы которого соединены с выходами соответственно блока сдвига и блока управляющей переменной, первый выход первого сумматора подключен через блок управляющей, переменной к адресному входу блока памяти, при этом блок управляющей переменной содержит элемент ИЛИ,две группы элементов И и два дешифратора, входы которых соединены соответственно с выходами чётных и нечетных элементов И первой группы, первые и вторые информационные входы элементов И которой соединены соответственно с входом блока и выходом элемента ИЛИ, входы которого соединены с входом блока, выходы дешифр торов являются выходом блока, первый и второй управляющие входы которого соединены соответственно с управляющими входами элементов И первой и второй групп, информаци-ониые входы элементов И второй группы соединены со входом блока, причем блок управле ния содержит генератор импульсов, два элемента задержки, три элемента И, триггер и регистр сдвига, выход которого является пятым выходом блока управления, вход регистра сдвига соединен с выходом первого элемента И, информационные входы которого соединены с входом блока управления управляющий вход первого элемента И соединен с выходом первого элемента задержки и вторым выходом блока управления, первый выход которого соединен с выходом второго элемента задержки и входом второго элемента за9A64

держки, выход генератора импульсов соединен с входом второго элемента задержки и первыми «входами второго и третьего элементов И, вторые входы

5 которых соединены о.прямым и инверсным выходами триггера, вход которого соединен с выходом второго элемента И и третьим выходом блока управления, четвертый выход которого соединен с

10 выходом третьего элемента И.

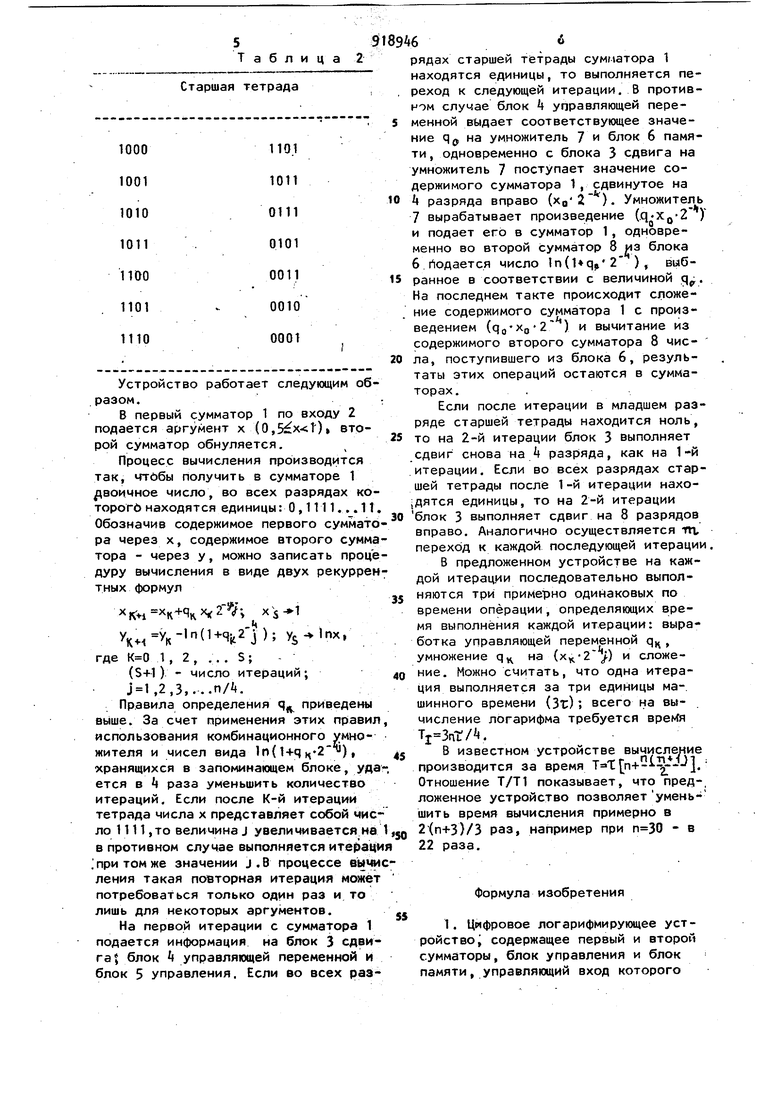

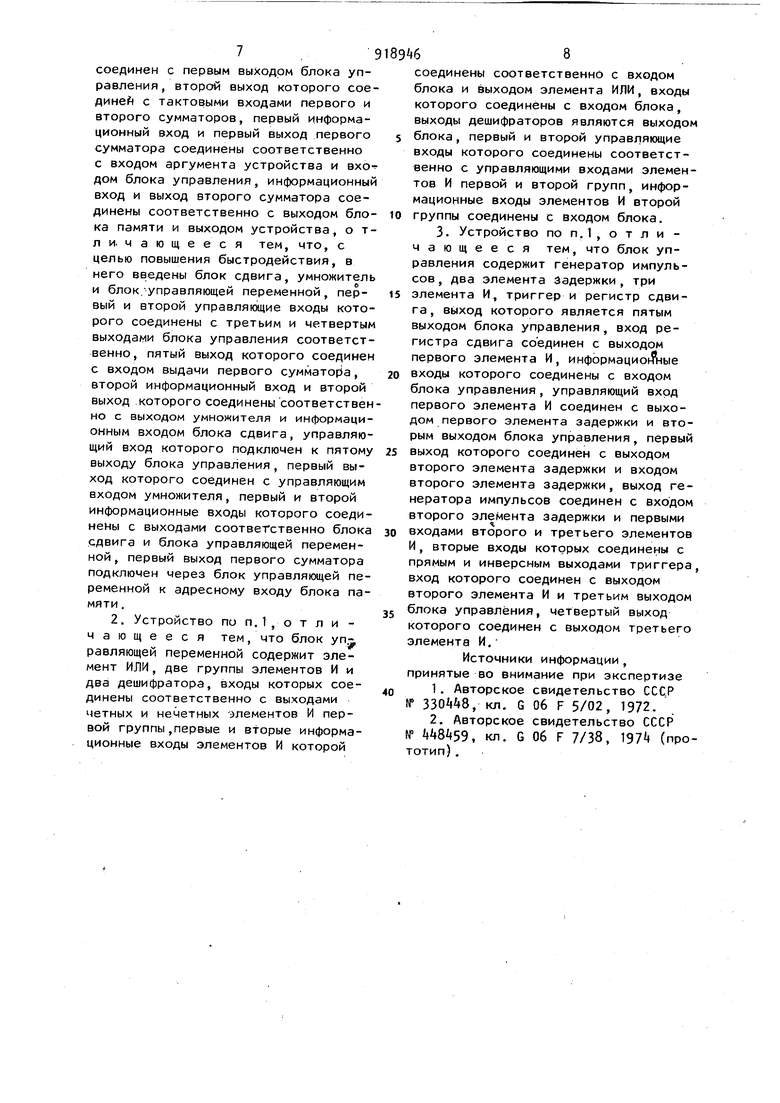

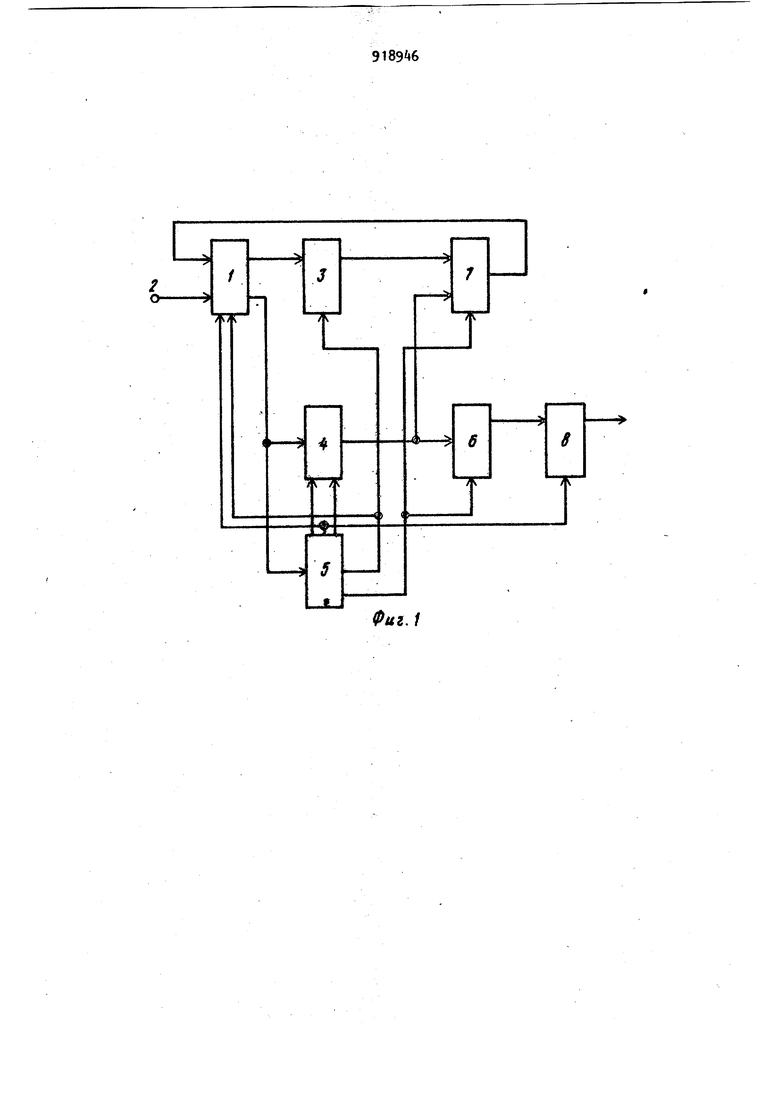

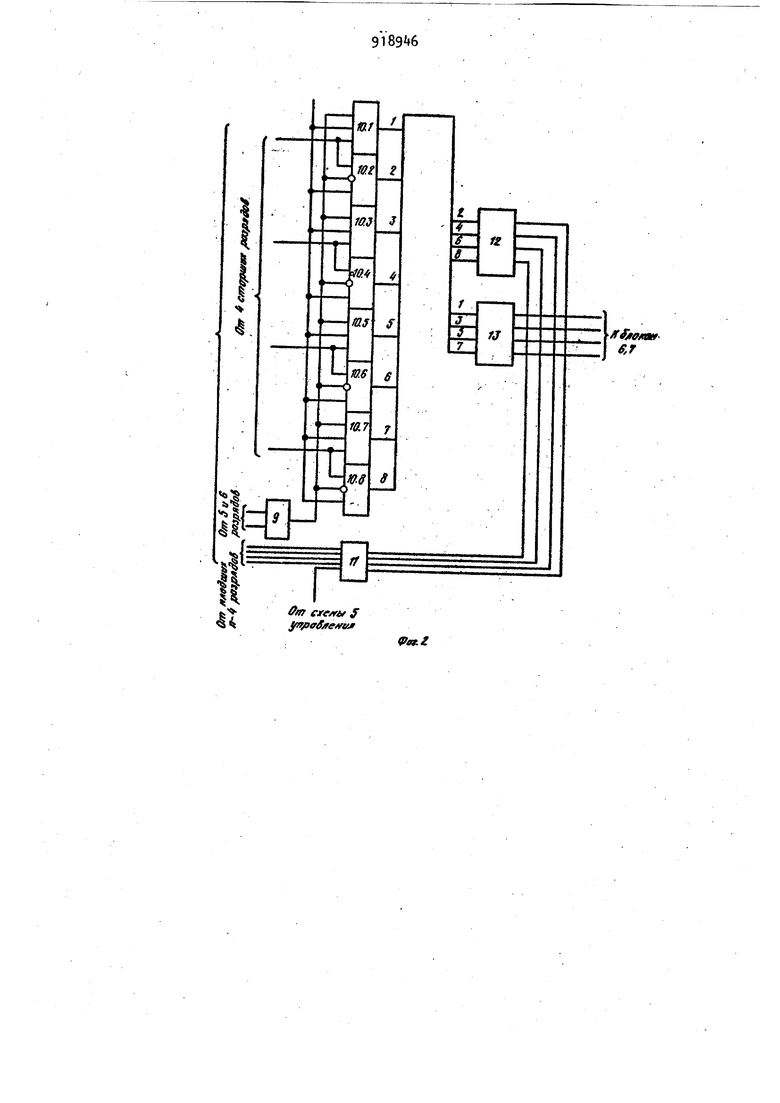

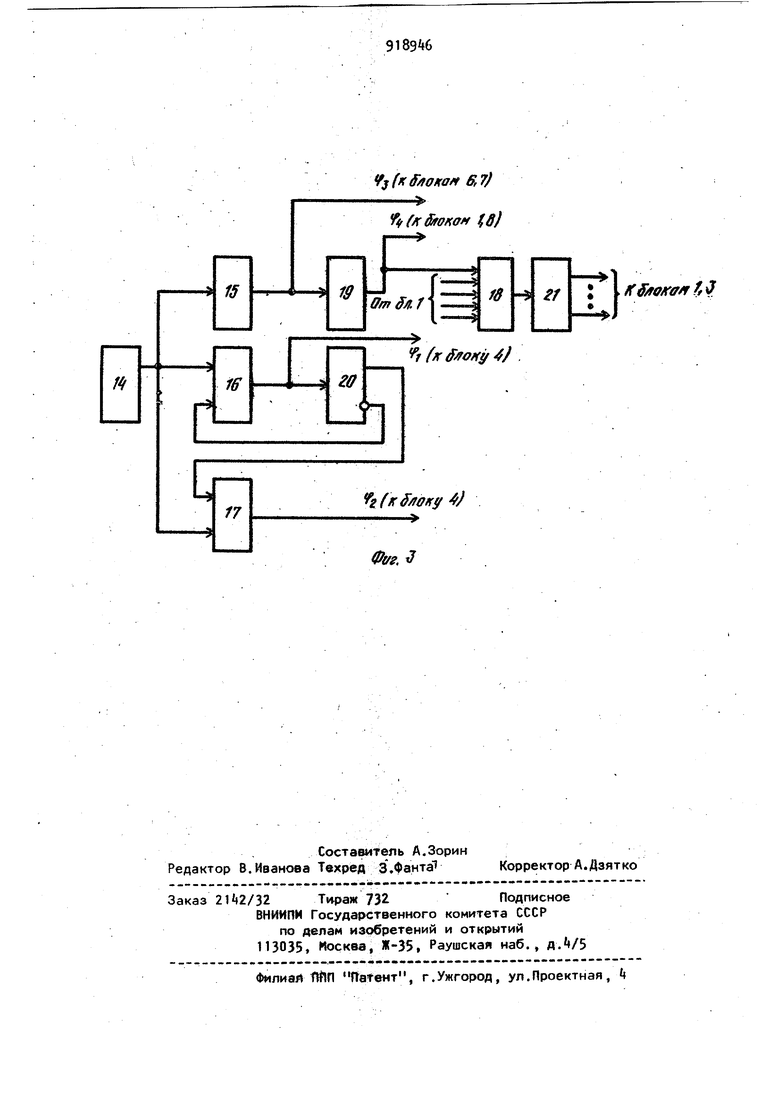

На фиг.1 представлена блок-схема устройства; на фиг.2 - блок управляющей переменной; на фиг.З - блок управления.

5 Цифровое логарифмирующее устройство содержит сумматор 1, вход 2 устройства, блок 3 сдвига, блок k управляющей переменной, блок 5 управления, блок 6 памяти, умнож1 ель

20 7 и сумматор 8.

Блок А управляющей переменной.содержит элемент 9 ИЛИ, группы 10 и 11 элементов И, дешифраторы 12 и 13. Блок 5 управления содержит генератор }Ц импульсов, элемент 15

задержки. Элементы 16-18 И, элемент 19 задержки, триггер 20 и регистр 21 сдвига.

Блок k управляющей переменной

30 предназначен для выработки четырехразрядных двоичных чисел в соответ. ствии со следующими правилами:

На каждой К-й итерации, кроме первой, Чк-1 определяется как обратный код от j-и тетрады, считая слева, содержимого первого сумматора.

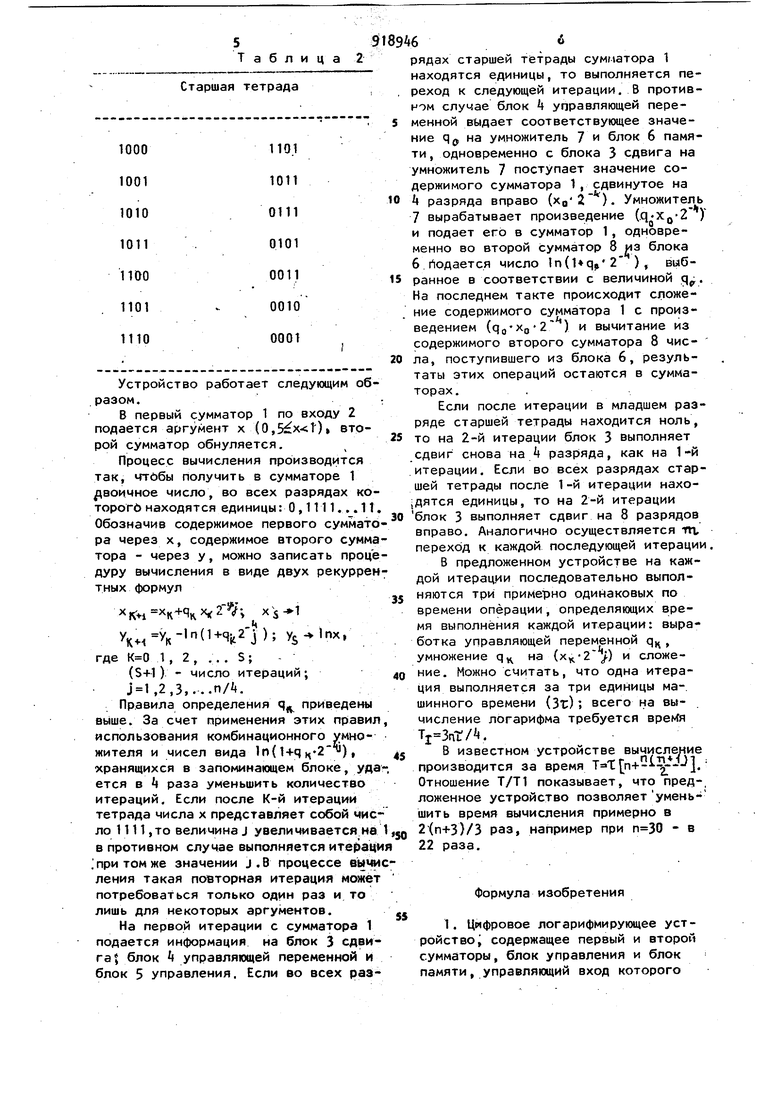

На первой итерации q определяется в соответствии с табл.1, если в пятом и шестом разрядах, считая сле40, ва, содержимого первого сумматора находятся нули, в противном случае Цд. определяется по табл.2.

Таблица 1

45

50

55 Таблица 2 Старшая тетрада Устройство работает следующим образом . В первый сумматор 1 по входу 2 подается аргумент х (0,) второй сумматор обнуляется. Процесс вычисления производится так, чтобы получить в сумматоре 1 двоичное число, во всех разрядах которогб находятся единицы: 0,1111... 11. Обозначив содержимое первого суммато ра через х, содержимое второго сумма тора - через у, можно записать проце дуру вычисления в виде двух рекуррен тных формул С+1 К+Чк ч2/; , где 1, 2, .. . S; (S+1 ) - число итераций; j 1,2,3,...nA. Правила определения q приведены вЫше. За счет применения этих правил использования комбинационного умножителя и чисел вида 1п{ Hq (2) , хранящихся в запоминающем блоке, уда ется в k раза уменьшить количество итераций. Если после К-й итерации тетрада числа х представляет собой число 1111 ,то величина j увеличивается на в противном случае выполняется итераци ;при том же значении j.В процессе вычи ления такая повторная итерация может потребоваться только один раз и то лишь для некоторых аргументов. На первой итерации с cyMMatopa 1 подается информация на блок 3 сдвига J блок управляющей переменной и блок 5 управления. Если во всех раз96 рядах старшей тетрады сумматора 1 находятся единицы, то выполняется переход к следующей итерации. В противном случае блок k управляющей переменной выдает соответствующее значение Я на умножитель 7 и блок 6 памяти, одновременно с блока 3 сдвига на умножитель 7 поступает значение содержимого сумматора 1, сдвинутое на I разряда вправо (хо2 ). Умножитель 7 вырабатывает произведение (. ) и подает его в сумматор 1, одновременно во второй сумматор 8 из блока 6 подается число ln( ), выбранное в соответствии с величиной q. На последнем такте происходит сложение содержимого сумматора 1 с произведением (qoXoZ ) и вычитание из содержимого второго сумматора 8 числа, поступившего из блока 6, результаты этих операций остаются в сумматорах. . Если после итерации в младшем разряде старшей тетрады находится ноль, то на 2-й итерации блок 3 выполняет сдвиг снова на k разряда, как на 1-й итерации. Если во всех разрядах старшей тетрады после 1-и итерации находятся единицы, то на 2-й итерации выполняет сдвиг на 8 разрядов Аналогично осуществляется та последующей итерации. В предложенном устройстве на кажj к дои итерации последовательно выполняются три примерно одинаковых по времени операции, определяющих время выполнения каждой итерации: выработка управляющей переменной q , умножение q на () и сложение. Можно считать, что одна итерация выполняется за три единицы ма-. шинного времени (Зт;); всего на вычисление логарифма требуется V3nT/. в известном устройстве вычисл ие производится за время . Отношение Т/Т1 показывает, что пред-, ложенное устройство позволяетуменьшить время вычисления примерно в 2(п+3)/3 раз, например при - в 22 раза. Формула изобретения 1. Цифровое логарифмирующее устройство содержащее первый и второй сумматоры, блок управления и блок памяти, управляющий вход которого

соединены соответственно с входом блока и выходом элемента ИЛИ, входы которого соединены с входом блока, выходы дешифраторов являются выходом 5 блока, первый и второй управляющие входы которого соединены соответственно с управляющими входами элементов И первой и второй групп, информационные входы элементов И второй

10 группы соединены с входом блока.

15 элемента И, триггер и регистр сдвига , выход которого является пятым выходом блока управления, вход регистра сдвига соединен с выходом первого элемента И, информацио 1 1ые

20 входы которого соединены с входом блока управления, управляющий вход первого элемента И соединен с выходом первого элемента задержки и вторым выходом блока управления, первый

25 выход которого соединен с выходом второго элемента задержки и входом второго элемента задержки, выход генератора импульсов соединен с входом второго элемента задержки и первыми

0 входами второго и третьего элементов И, вторые входы которых соединены с прямым и инверсным выходами триггера, вход которого соединен с выходом второго элемента И и третьим выходом

5 блока управления, четвертый выход которого соединен с выходом третьего элемента И.

Источники информации, принятые во внимание при экспертизе

0 1. Авторское свидетельство СССР If , кл. G Об F 5/02, 1972.

Фиг.1

15

19

го

Iff

rtJ

3

17

fj(Kf/iOKaft 6,7)

.5

f(/fSroKOff

Г;

lfS/№/ffffrt

fd

h 2f

ff/l.f.

fj fjf ffffOHif 4f .

zfrffflOlfff 4}

фуг. t7

Авторы

Даты

1982-04-07—Публикация

1980-06-27—Подача