Уровень техники

В последние годы производители запоминающих устройств производили запоминающие устройства, в которых чипы памяти расположены в виде стека друг на друге, тем самым, увеличивается равномерность, и при этом сокращается длина выводов соответствующих запоминающих устройств. Например, в обычном процессе производства каждое такое запоминающее устройство может включать в себя первый чип памяти и второй чип памяти, причем первый чип памяти выполнен с возможностью расположения сверху его над вторым чипом памяти. И первый, и второй чипы памяти могут быть реализованы в виде динамической оперативной памяти произвольного доступа (DRAM), включающей в себя один или несколько блоков памяти и соответствующие трансиверы и логическую схему управления/адресации. Каждое запоминающее устройство также может включать в себя шину управления/адресации, имеющую заданное число управляющих битов/битов адресации, шину данных, имеющую заданное число битов данных, и несколько каналов, соответствующих шине управления/адресации и шине данных и в первом, и во втором чипах памяти. В таких запоминающих устройствах и первый, и второй чипы памяти могут соответствовать отдельному рангу памяти, и сложенные в стек первый и второй чипы памяти могут представлять двухранговую стековую память, имеющую такое же число каналов, что и первый или второй чип памяти.

Каждое запоминающее устройство, из описанных выше, может быть реализовано в системной памяти, которая включает в себя контроллер памяти, имеющий интерфейс памяти с соединениями шины управления/адресации и шины данных для взаимодействия с шиной управления/адресации и шиной данных запоминающего устройства соответственно. Кроме того, шина данных может быть разделена, чтобы сопрягаться с несколькими каналами в соответствующем первом и втором чипах памяти, и шина управления/адресации аналогично может быть разделена, чтобы сопрягаться с логической схемой управления/адресации в соответствующем первом и втором чипе памяти.

Краткое описание чертежей

На сопровождающих чертежах, которые включены в этот документ и составляют часть этого описании, показан один или несколько вариантов осуществления, описанных в этом документе, и вместе с подробным описанием чертежи объясняют эти варианты осуществления. На чертежах:

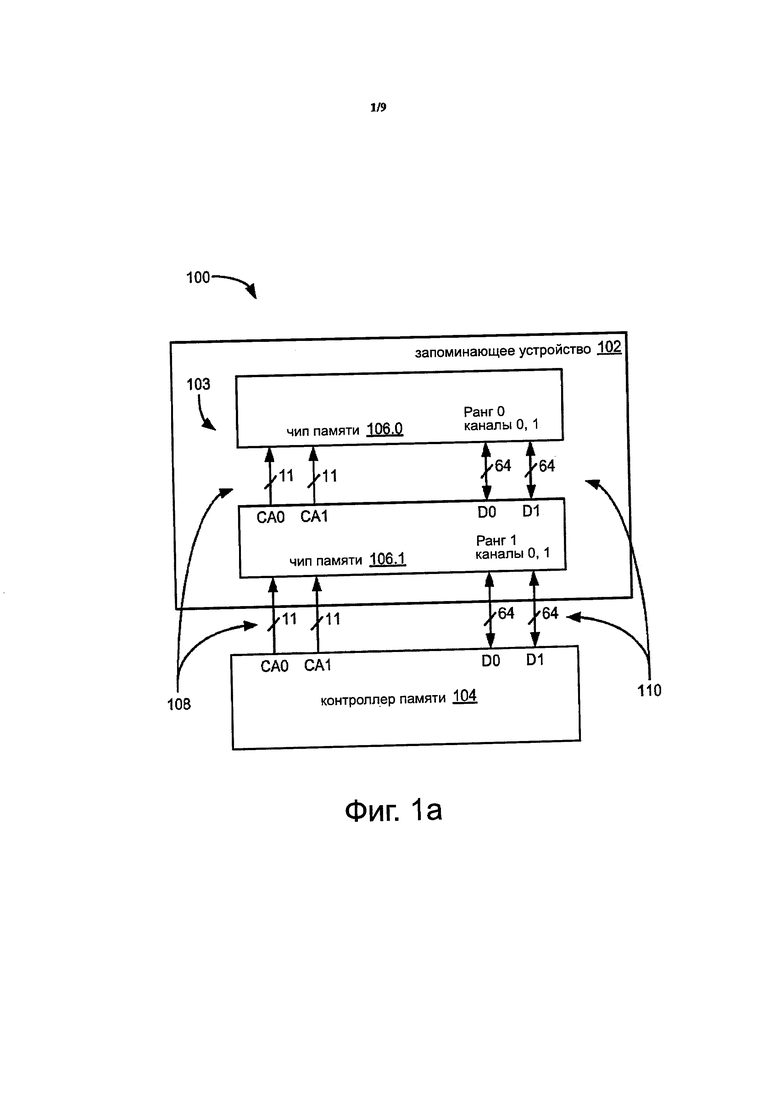

на фиг. 1а приведена блок-схема системной памяти, которая включает в себя запоминающее устройство, имеющее двухранговый стек памяти, и контроллер памяти, соединенный с двухранговым стеком памяти;

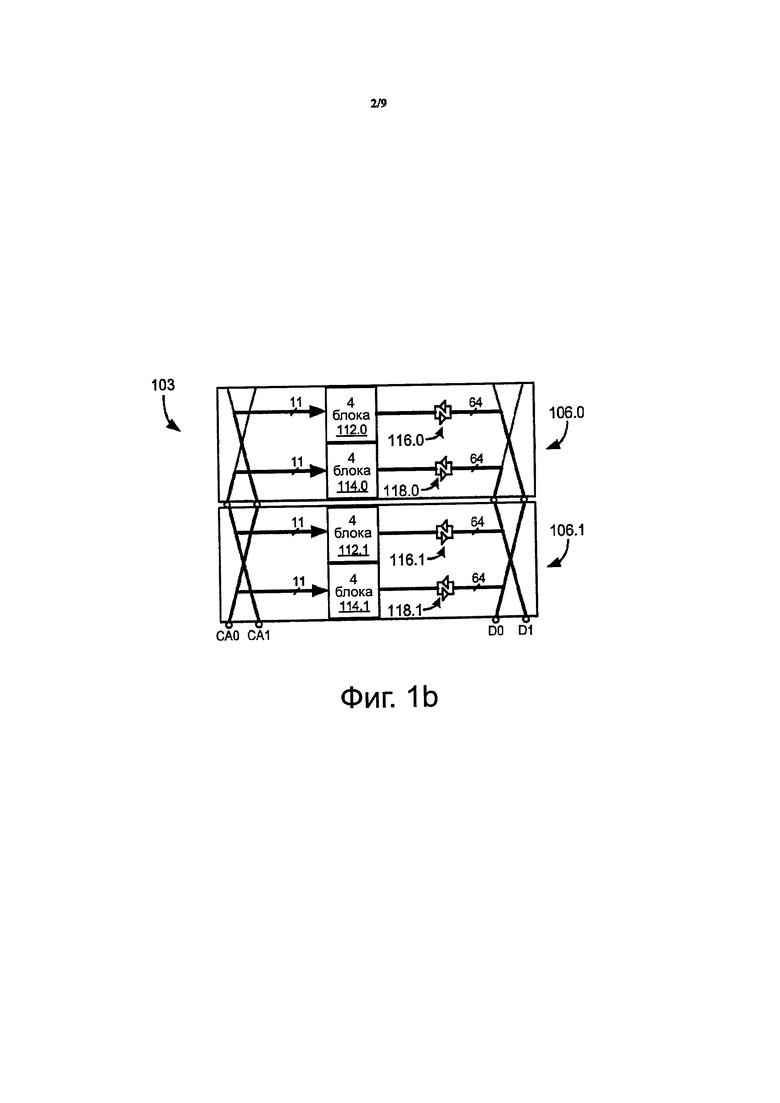

на фиг. 1b приведена блок-схема двухрангового стека памяти, входящего в запоминающее устройство, показанное на фиг. 1а;

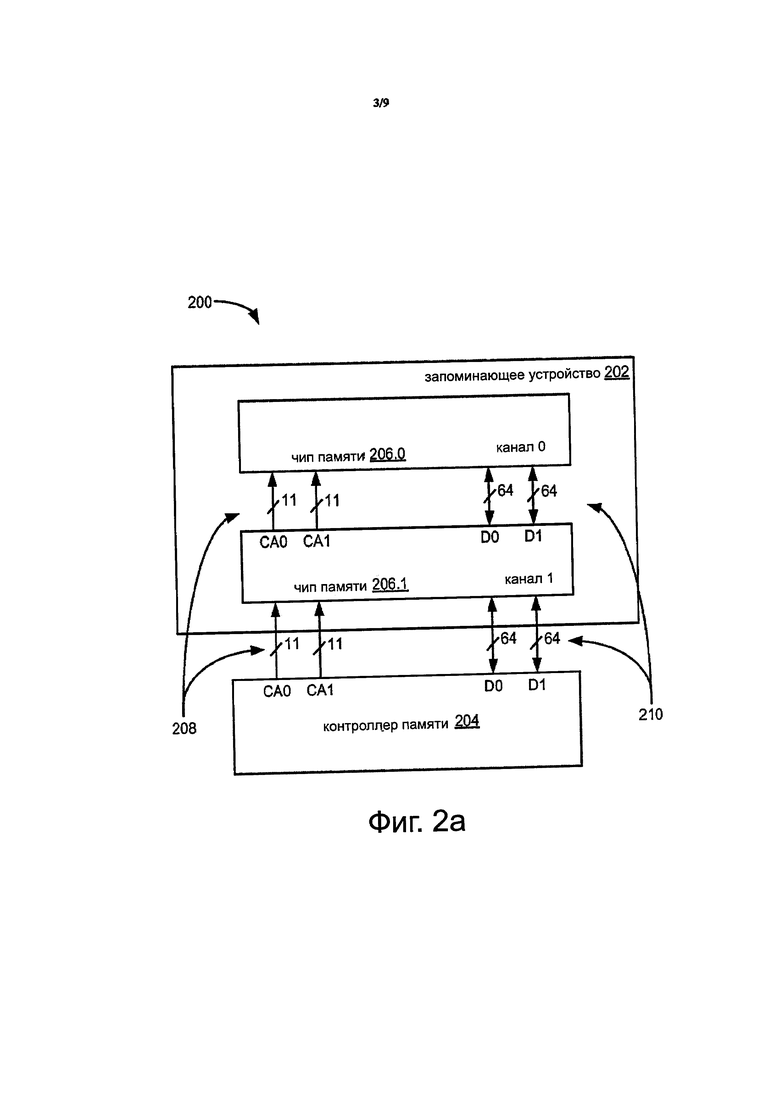

на фиг. 2а приведена блок-схема примера системной памяти для увеличения скорости передачи данных и полосы пропускания системной памяти, показанной на фиг. 1а, при этом системная память на фиг. 2а включает в себя запоминающее устройство, имеющее несколько расположенных друг над другом чипов памяти и контроллер памяти, соединенный со стековым запоминающим устройством, в соответствии с настоящей заявкой;

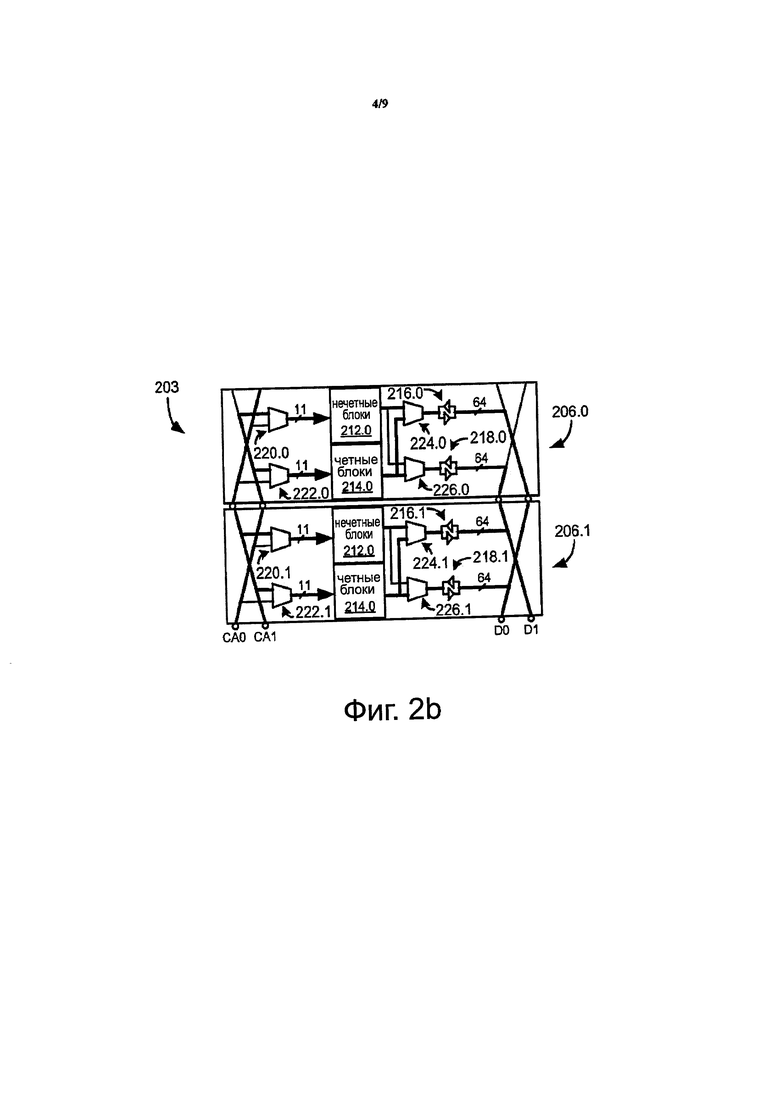

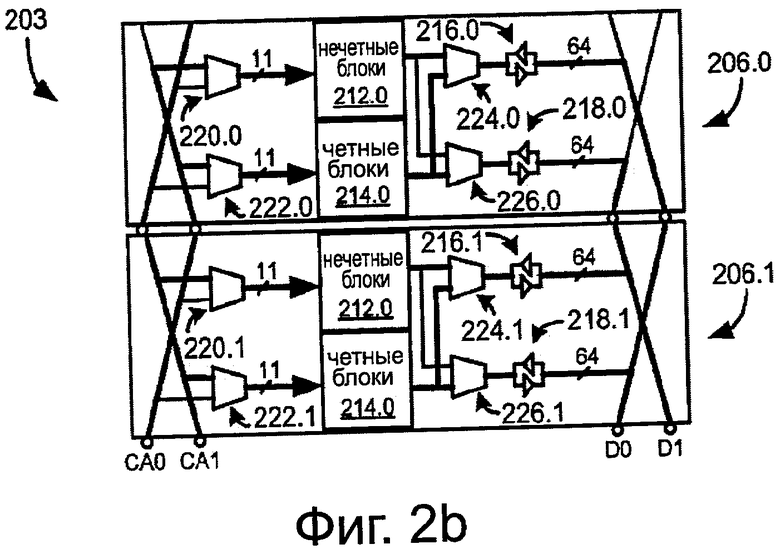

на фиг. 2b приведена блок-схема выполненных в виде стека чипов памяти, входящих в запоминающее устройство, показанное на фиг. 2а;

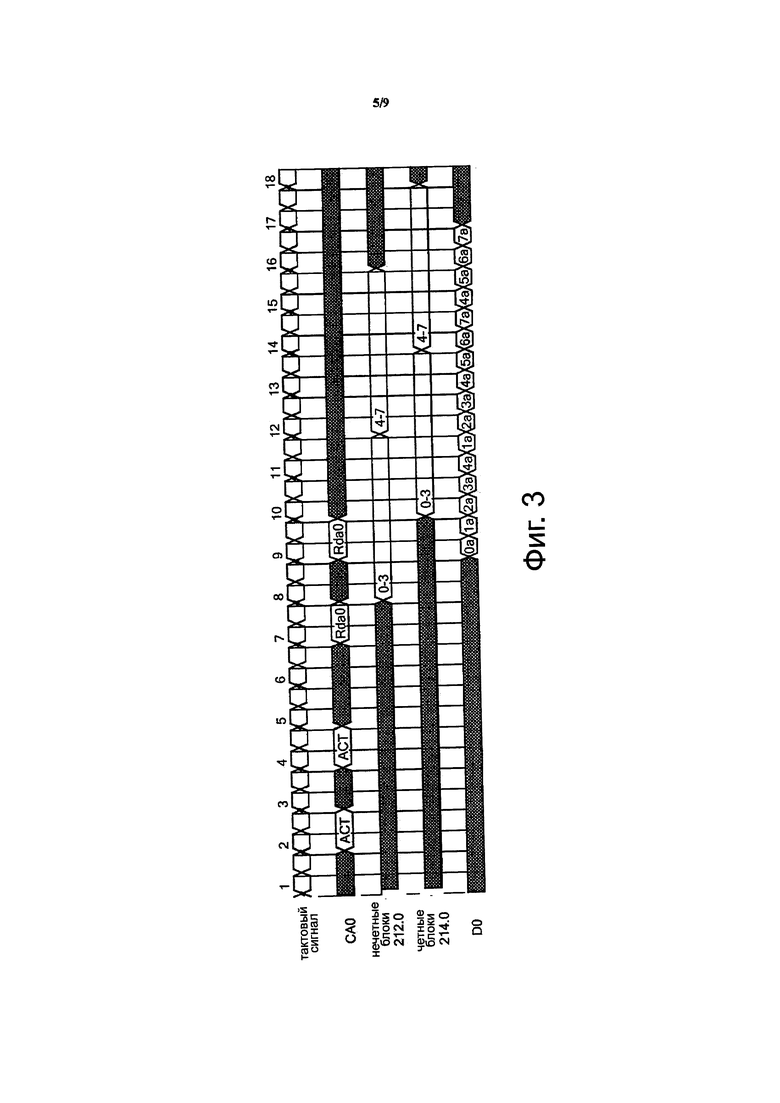

на фиг. 3 приведена временная диаграмма, показывающая пример работы выполненных в виде стека чипов памяти в запоминающем устройстве, показанном на фиг. 2а;

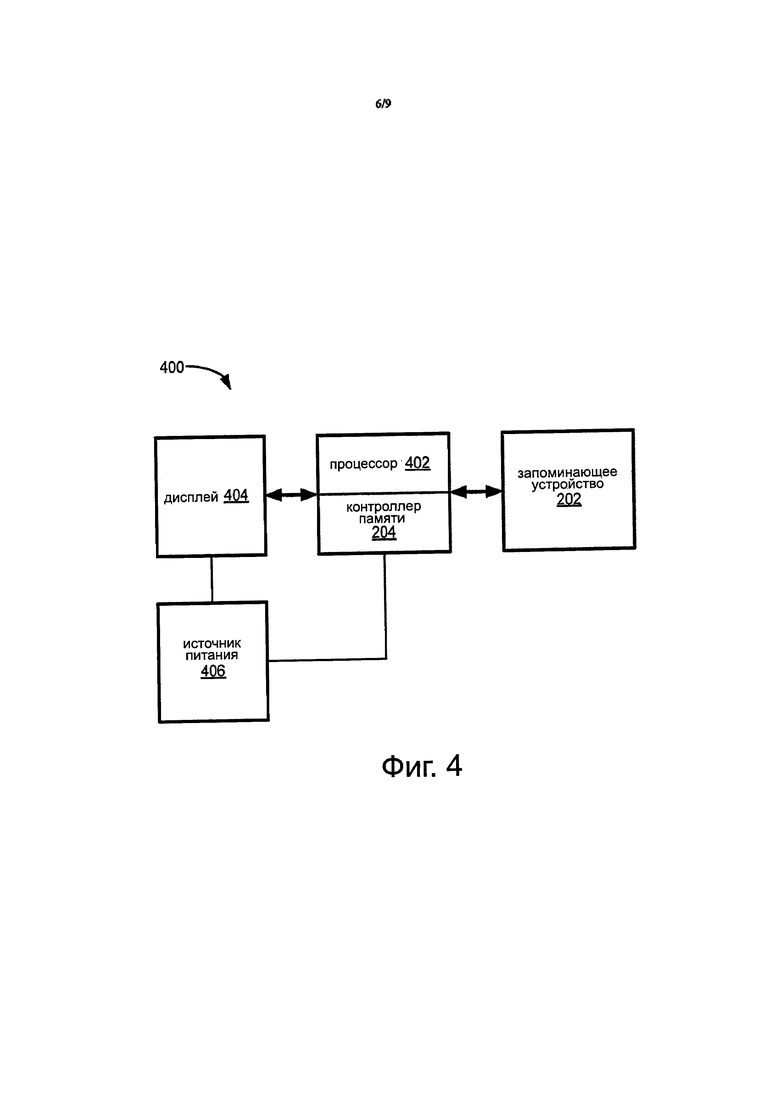

на фиг. 4 показана блок-схема примера вычислительной системы, в которую входит запоминающее устройство и контроллер памяти, показанные на фиг. 2а;

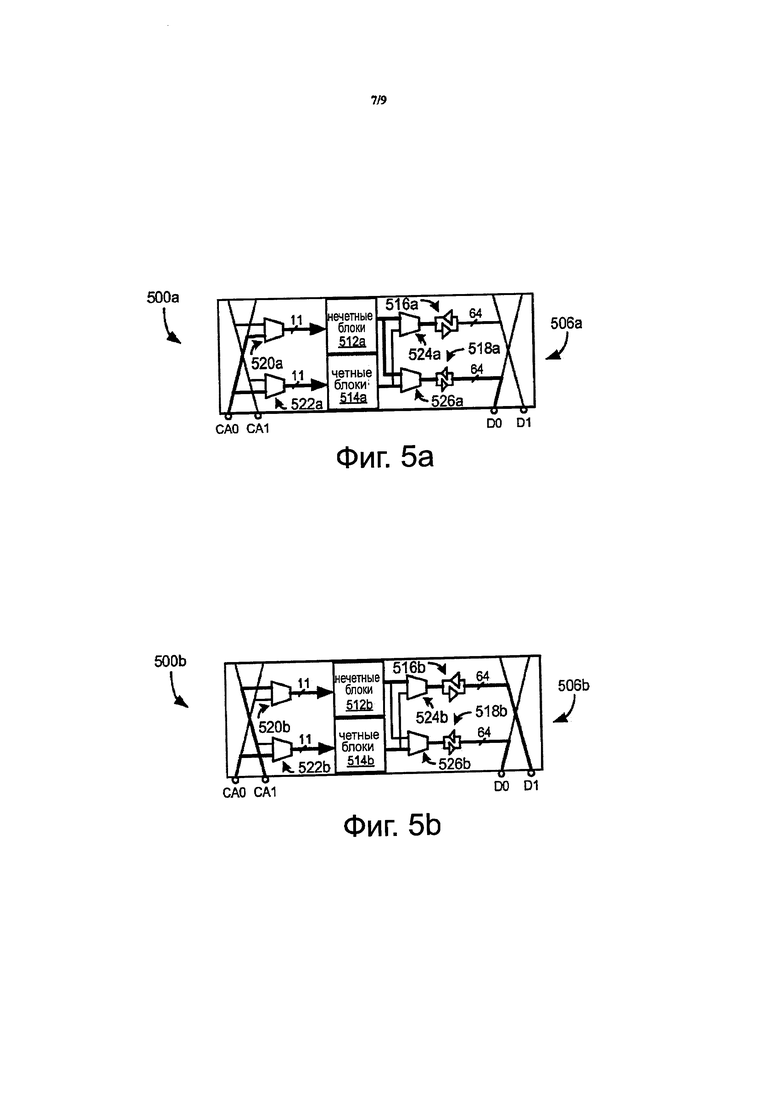

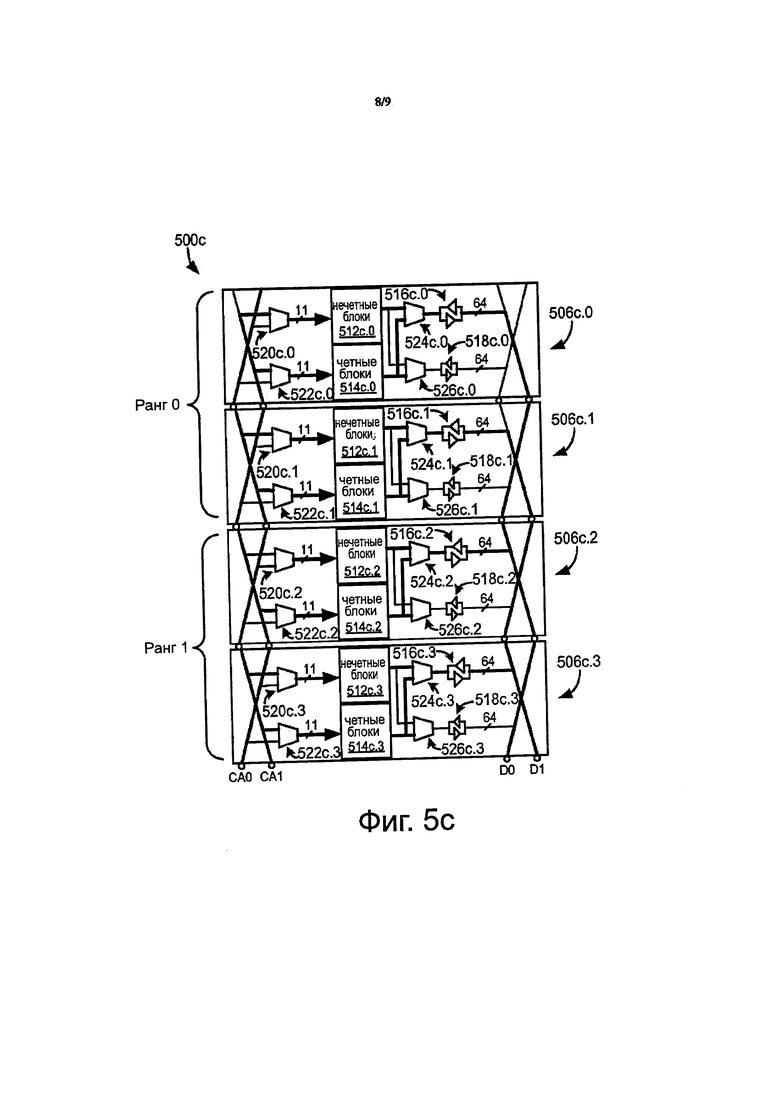

на фиг. 5а, 5b и 5с показаны блок-схемы альтернативных примеров осуществления выполненных в виде стека чипов памяти, показанных на фиг. 2b; и

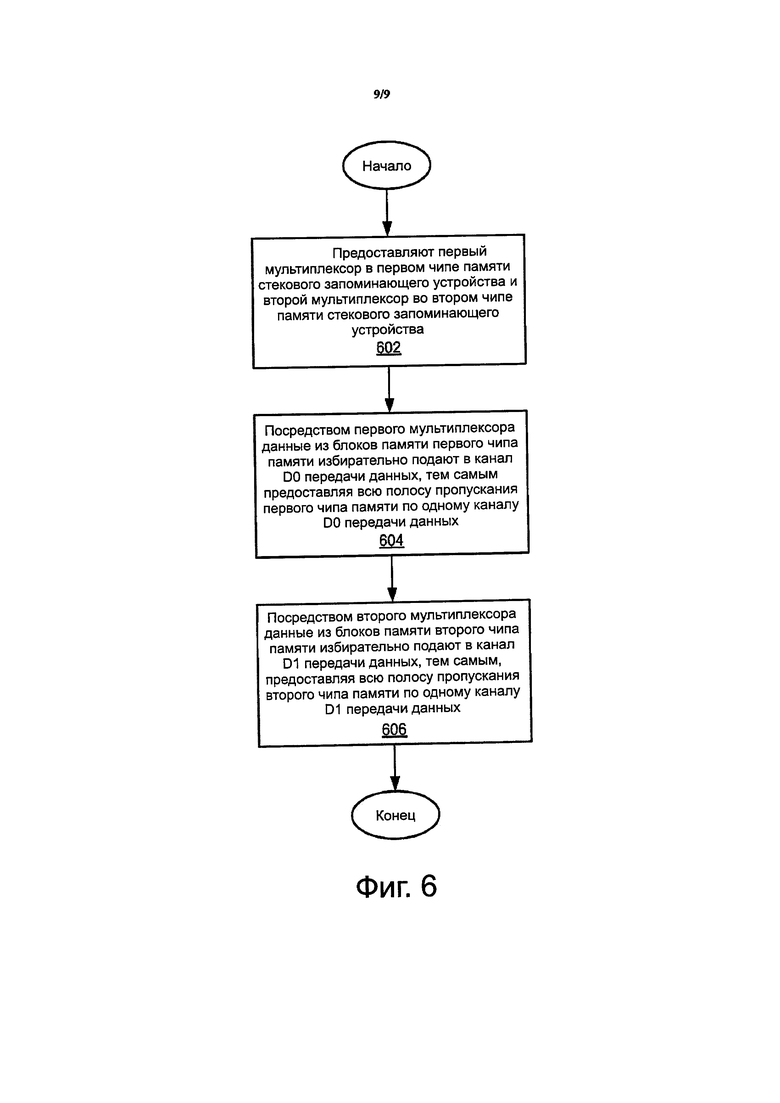

на фиг. 6 показана блок-схема последовательности операций примера способа работы системной памяти, показанной на фиг. 2а.

Подробное описание изобретения

Описаны устройство и способы увеличения скорости передачи данных и полосы пропускания системной памяти, включающей в себя выполненные в виде стека чипы памяти. Системная память включает в себя запоминающее устройство, имеющее несколько чипов памяти, расположенных в виде стека, контроллер памяти, соединенный с выполненными в виде стека чипами памяти, и разделенную на части шину данных. Каждый чип памяти включает в себя одну, две или больше групп блоков памяти. При конфигурировании каждого чипа памяти так, чтобы он предоставлял всю свою полосу пропускания по разным разделам канала передачи данных, системная память может без существенных издержек достичь повышенной скорости передачи данных и увеличенной полосы пропускания по сравнению с обычными конфигурациями системной памяти, которые включают в себя выполненные в виде стека чипы памяти.

В подробном описании настоящей заявки будет использоваться следующая терминология в соответствии с изложенными ниже определениями. Термин "стек" используют для обозначения всех чипов памяти в запоминающем устройстве, взятых вместе как один узел. Термин "слой" используют для обозначения одного чипа памяти в стеке чипов памяти. Термин "канал" используют для обозначения множества физически отдельных выводов в интерфейсе памяти, которые независимо управляют разделом запоминающего устройства. Термин "ранг" используют для обозначения нескольких слоев, многоточечно соединенных с одним каналом, в стеке чипов памяти. Термин "полоса пропускания" используют для обозначения максимальной скорости передачи данных, умноженной на общую ширину шины данных запоминающего устройства.

Отметим, что каждый чип памяти в стеке чипов памяти может быть разделен на нечетные блоки памяти и четные блоки памяти, которые поддерживают специфические совмещаемые операции. Также отметим, что интерфейс памяти может поддерживать четыре (4), восемь (8) или любое другое подходящее число физических каналов. Каждый канал может содержать все управляющие сигналы, сигналы передачи данных, тактовые сигналы, необходимые для того, чтобы независимо управлять разделом запоминающего устройства. Каждый канал может иметь различные открытые страницы памяти, может независимо синхронизироваться и может находиться в различных состояниях энергопотребления. Физический канал также включает в себя сигналы ввода/вывода (I/O), сигнал мощности и "земля".

На фиг. 1а изображена системная память 100, которая включает в себя запоминающее устройство 102, имеющее двухранговый стек 103 памяти, и контроллер 104 памяти, соединенный с двухранговым стеком 103 памяти. Например, системная память 100 может быть выполнена в соответствии со стандартном Объединенного инженерного совета по электронным устройствам (JEDEC) для высокоскоростной мобильной динамической памяти с произвольным доступом (DRAM), а именно, JESD229 Wide I/O Single Data Rate (SDR), декабрь 2011, или с самой последней версией. Как показано на фиг. 1а, двухранговый стек 103 памяти включает в себя первый чип 106.0 памяти и второй чип 106.1 памяти, причем первый чип 106.0 памяти расположен сверху на втором чипе 106.1 памяти. Например, каждый из чипов 106.0, 106.1 памяти может быт реализован в виде динамической памяти с произвольным доступом (DRAM), статической памяти с произвольным доступом (SRAM) или любой другой подходящей памяти. Системная память 100 также включает в себя шину 108 управления/адресации (СА), имеющую заданное число битов СА (напр., 11 битов CA0 + 11 битов CA1 = 22 битов СА, или любое другое подходящее число битов СА), и шину 110 данных (D), имеющую заданное число битов D (напр., 64 бита D0 + 64 бита D1 = 128 битов D, или любое другое подходящее число битов D). В запоминающем устройстве 102 чипы 106.0, 106.1 памяти могут соответствовать отдельным рангам памяти 0, 1 соответственно, и чипы 106.0, 106.1 памяти в виде стека могут представлять двухранговую стековую память 103, которая может иметь такое же число каналов (напр., 2 канала или любое другое подходящее число каналов), что и один из чипов 106.0, 106.1 памяти.

Как также показано на фиг. 1а, контроллер 104 памяти имеет интерфейс памяти с выводами шины управления/адресации (СА) и шины данных (D) для взаимодействия с шинами 108, 110 управления/адресации (СА) и данных (D) соответственно системной памяти 100. Шина 110 данных (D) может быть разделена на два 64-битовых канала данных D0, D1 для сопряжения с двумя каналами 0, 1 двухранговой стековой 103 памяти, а шина 108 управления/адресации (СА) может быть разделена на два 11-битовых канала CA0, CA1 управления/адресации для сопряжения с логической схемой управления/адресации чипа 106.0, 106.1 памяти в двухранговой стековой памяти 103. Отметим, что каждый чип 106.0, 106.1 памяти может иметь любое другое подходящее число каналов передачи данных и/или управления/адресации, имеющих любое другое подходящее число битов данных и/или управления/адресации.

На фиг. 1b показан подробный вид двухранговой стековой памяти 103, входящей в устройство 102 памяти, показанное на фиг. 1а. Как показано на фиг. 1b, двухранговая стековая память 103 включает в себя первый и второй чипы 106.0, 106.1 памяти в виде стека. Чип 106.0 памяти может включать в себя две группы блоков 112.0, 114.0 памяти, где каждая группа блоков 112.0, 114.0 памяти может включать в себя четыре блока памяти. В двухранговой стековой памяти 103 группа блоков 112.0 памяти соединена с 11-битовым каналом CA0 управления/адресации, а группа блоков 114.0 памяти соединена с 11-битовым каналом CA1 управления/адресации. Чип 106.0 памяти также включает в себя два трансивера 116.0, 118.0 для соединения групп блоков 112.0, 114.0 памяти с 64-битовыми каналами D0, D1 передачи данных соответственно.

Аналогично, чип 106.1 памяти может включать в себя две группы блоков 112.1, 114.1 памяти, где каждая группа блоков 112.1, 114.1 памяти может включать в себя четыре блока памяти. В двухранговой стековой памяти 103 группа блоков 112.1 памяти соединена с 11-битовым каналом CA0 управления/адресации, а группа блоков 114.1 памяти соединена с 11-битовым каналом CA0 управления/адресации. Чип 106.1 памяти также включает в себя два трансивера 116.1, 118.1для соединения групп блоков 112.1, 114.1 памяти с 64-битовыми каналами D1, D0 передачи данных соответственно.

Соответственно, используя две пары трансиверов 116.0, 118.0 и 116.1, 118.1, соответствующие чипы 106.0, 106.1 памяти в двухранговой стековой памяти 103 системной памяти 100 могут принимать данные, передаваемые контроллером 104 памяти по 64-битовым каналам D0, D1 передачи данных, а также передавать данные по 64-битовым каналам D0, D1 передачи данных в конфигурации "точка-две точки" (Р22Р). В одном варианте осуществления такая Р22Р конфигурация чипов 106.0, 106.1 памяти может по двум 64-битовым каналам D0, D1 передачи данных предоставить полосу пропускания примерно до 68 гигабайт (GB) в секунду (с) при уменьшенном использовании канала памяти из-за присущих издержек переключений рангов.

На фиг. 2а показан пример системной памяти 200 для увеличения скорости передачи данных и полосы пропускания системной памяти 100, показанной на фиг. 1а, в соответствии с настоящей заявкой. Как показано на фиг. 2а, системная память 200 включает в себя запоминающее устройство 202, имеющее несколько чипов 206.0, 206.1 памяти в виде стека, и контроллер 204 памяти, соединенный с выполненными в виде стека чипами 206.0, 206.1 памяти. Например, каждый из чипов 206.0, 206.1 памяти может быт реализован в виде динамической памяти с произвольным доступом (DRAM), статической памяти с произвольным доступом (SRAM) или любой другой подходящей памяти. Системная память 200 также включает в себя шину 208 управления/адресации (СА), имеющую заданное число битов СА (напр., 11 битов CA0 + 11 битов CA1 = 22 битов СА, или любое другое подходящее число битов СА), и шину 210 данных (D), имеющую заданное число битов D (напр., 64 бита D0 + 64 бита D1 = 128 битов D, или любое другое подходящее число битов D).

Как также показано на фиг. 2а, контроллер 204 памяти имеет интерфейс памяти с выводами шины управления/адресации (СА) и данных (D) для взаимодействия с шинами 208, 210 управления/адресации (СА) и данных (D) соответственно системной памяти 200. Шина 210 данных (D) может быть разделена на два 64-битовых канала D0, D1 передачи данных для сопряжения с двумя каналами 0, 1 выполненных в виде стека чипов 206.0, 206.1 памяти, а шина 108 управления/адресации (СА) может быть разделена на два 11-битовых канала CA0, CA1 управления/адресации для сопряжения с логической схемой управления/адресации чипов 206.0, 206.1 памяти. Отметим, что соединения "чип-чип" 11-битовых каналов CA0, CA1 управления/адресации и 64-битовых каналов D0, D1 передачи данных могут быть выполнены посредством любого подходящего процесса формирования выводов, как известно специалистам в области техники. Отметим также, что каждый чип 206.0, 206.1 памяти может иметь любое другое подходящее число каналов передачи данных и/или управления/адресации, имеющих любое другое подходящее число битов данных и/или управления/адресации.

На фиг. 2b показан подробный вид чипов 206.0, 206.1 стековой памяти, входящей в устройство 202 памяти, показанное на фиг. 2а. Как показано на фиг. 2b, чип 206.0 памяти может включать в себя одну, две или более групп блоков памяти, таких как группа нечетных блоков 212.0 памяти и группа четных блоков 214.0 памяти. Чип 206.0 памяти также включает в себя два трансивера 216.0, 218.0, соединенные с 64-битовыми каналами D0, D1 передачи данных соответственно. Кроме того, чип 206.0 памяти включает в себя два мультиплексора 220.0, 222.0 для выборочного соединения 11-битовых каналов CA0, CA1 управления/адресации с соответствующими группами нечетных и четных блоков 212.0, 214.0 памяти, и два мультиплексора 224.0, 226.0 для выборочного соединения групп нечетных и четных блоков 212.0, 214.0 памяти с трансиверами 216.0, 218.0 соответственно.

В показанном варианте осуществления чипа 206.0 памяти группа нечетных блоков 212.0 памяти посредством мультиплексора 220.0 выборочно соединен с 11-битовым каналом CA0 управления/адресации, а группа блоков четных блоков 214.0 памяти посредством мультиплексора 222.0 выборочно соединена с 11-битовым каналом CA0 управления/адресации. Каждая группа нечетных и четных блоков 212.0, 214.0 памяти также посредством мультиплексора 224.0 выборочно соединена с трансивером 216.0, который, в свою очередь, соединен с 64-битовым каналом D0 передачи данных. В показанном варианте осуществления мультиплексор 226.0 эффективно выключен и, поэтому, не передает никакие данные из групп нечетных и четных блоков 212.0, 214.0 памяти на трансивер 218.0, который, как описано выше, соединен с 64-битовым каналом D1 передачи данных. Поэтому, чип 206.0 памяти выполнен с возможностью предоставлять всю свою полосу пропускания по единственному 64-битовому каналу D0 передачи данных.

Как показано на фиг. 2b, чип 206.1 памяти может включать в себя одну, две или более групп блоков памяти, таких как группа нечетных блоков 212.1 памяти и группа четных блоков 214.1 памяти. Чип 206.1 памяти также включает в себя два трансивера 216.1, 218.1, соединенные с 64-битовыми каналами D1, D0 передачи данных соответственно. Кроме того, чип 206.1 памяти включает в себя два мультиплексора 220.1, 222.1 для выборочного соединения 11-битовых каналов CA1, CA0 управления/адресации с соответствующими группами нечетных и четных блоков 212.1, 214.1 памяти, и два мультиплексора 224.1, 226.1 для выборочного соединения групп нечетных и четных блоков 212.1, 214.1 памяти с трансиверами 216.1, 218.1 соответственно.

В показанном варианте осуществления чипа 206.1 памяти группы нечетных блоков 212.1 памяти посредством мультиплексора 220.1 выборочно соединен с 11-битовым каналом CA1 управления/адресации, а группа блоков четных блоков 214.1 памяти посредством мультиплексора 222.1 выборочно соединена с 11-битовым каналом CA1 управления/адресации. Каждая группа нечетных и четных блоков 212.1, 214.1 памяти также посредством мультиплексора 224.1 выборочно соединена с трансивером 216.1, который, в свою очередь, соединен с 64-битовым каналом D1 передачи данных. В показанном варианте осуществления мультиплексор 226.1 эффективно выключен и, поэтому, не передает никакие данные из групп нечетных и четных блоков 212.1, 214.1 памяти на трансивер 218.1, который, как описано выше, соединен с 64-битовым каналом D0 передачи данных. Поэтому, чип 206.1 памяти выполнен с возможностью предоставлять всю свою полосу пропускания по единственному 64-битовому каналу D1 передачи данных.

Соответственно, с использованием мультиплексора 224.0 и трансивера 216.0 чип 206.0 памяти может принимать данные, предоставляемые контроллером 204 памяти по 64-битовому каналу D0 передачи данных, а также передавать данные по единственному 64-битовому каналу D0 передачи данных. Аналогично, с использованием мультиплексора 224.1 и трансивера 216.1 чип 206.1 памяти может принимать данные, предоставляемые контроллером 204 памяти по 64-битовому каналу D1 передачи данных, а также передавать данные по единственному 64-битовому каналу D1 передачи данных. Поэтому, чип 206.0, 206.1 памяти может принимать данные по соответствующим 64-битовым каналам D0, D1 передачи данных и передавать данные по соответствующим каналам D0, D1 передачи данных в конфигурации "точка-точка" (Р2Р).

В одном варианте осуществления Р2Р конфигурация чипов 206.0, 206.1 памяти может предоставлять по соответствующим каналам D0, D1 передачи данных пиковую полосу пропускания примерно до 136 Гб/с, что примерно в два раза больше пиковой полосы пропускания (т.е. удвоенная скорость передачи данных и полоса пропускания), чем может предоставить Р22Р конфигурация чипов 106.0, 106.1 памяти в системной памяти 100. Системная память 200 может достичь такой увеличенной скорости передачи данных и полосы пропускания с увеличенным использованием канала памяти путем устранения издержек переключения рангов системной памяти 100.

Отметим, что для того, чтобы поддерживать удвоенную скорость передачи данных (DDR), которую можно обеспечить по 64-битовому каналу D0 передачи данных, трансивер 216.0 может быть сконфигурирован так, чтобы его емкость передачи была по меньшей мере примерно в два раза больше, чем у трансивера 218.0. Аналогично, чтобы поддерживать DDR, которую можно обеспечить по 64-битовому каналу D1 передачи данных, трансивер 216.1 может быть сконфигурирован так, чтобы его емкость передачи была по меньшей мере в два раза больше, чем у трансивера 218.1. Выражение "емкость передачи" используется в этом документе для обозначения способности трансиверов 216.0, 218.0, 216.1, 218.1 передавать данные по соответствующим 64-битовым каналам D0, D1 передачи данных с мощностью передачи, необходимой для предоставления желаемой полосы пропускания для Р2Р конфигурации чипов 206.0, 206.1 памяти.

На фиг. 3 показан пример временной диаграммы предоставления всей полосы пропускания чипа 206.0 памяти по единственному 64-битовому каналу D0 передачи данных. Отметим, что можно построить аналогичную временную диаграмму, чтобы показать предоставление всей полосы пропускания чипа 206.1 памяти по единственному 64-битовому каналу D1 передачи данных. Как показано на фиг.3, команды адресации (ACT) могут быть переданы по 11-битовому каналу CA0 управления/адресации в течение тактов 2 и 4 системного тактового генератора (CLOCK) для адресации ячеек памяти в нечетных и четных блоках 212.0, 214.0 памяти, а команды управления (Rda0, Rda1) могут быть переданы по 11-битовому каналу CAO во время тактов 7 и 9 тактового генератора CLOCK для чтения данных из ячеек памяти в нечетных и четных блоках 212.0, 214.0 памяти. Как также показано на фиг.3, нечетный блок 212.0 памяти может предоставить свои байты 0-3 данных из адресованных ячеек памяти в тактах 8-11 тактового генератора CLOCK, и может предоставить свои байты 4-7 данных из адресованных ячеек памяти во время тактов 12-15 тактового генератора CLOCK. Аналогично, четный блок 214.0 памяти может предоставить свои байты 0-3 данных из адресованных ячеек памяти в тактах 10-13 тактового генератора CLOCK, и может предоставить свои байты 4-7 данных из адресованных ячеек памяти во время тактов 14-17 тактового генератора CLOCK. Как описано выше, каждая группа нечетных и четных блоков 212.0, 214.0 памяти посредством мультиплексора 224.0 выборочно соединена с трансивером 216.0, который, в свою очередь, соединен с 64-битовым каналом D0 передачи данных.

В одном варианте осуществления контроллер 204 памяти может управлять мультиплексором 224.0 так, чтобы попеременно предоставлять трансиверу 216.0 байты 0-3 данных (D0) из нечетного блока 212.0 памяти и байты 0-3 данных (D0) из четного блока 214.0 памяти, как показано данными, передаваемыми по 64-битовому каналу D0 передачи данных во время тактов 9-12 тактового генератора CLOCK. Контроллер 204 памяти также может управлять мультиплексором 224.4 так, чтобы попеременно предоставлять трансиверу 216.4 байты 0-7 данных (D0) из нечетного блока 212.0 памяти и байты 0-7 данных (D0) из четного блока 214.0 памяти, как показано данными, передаваемыми по 64-битовому каналу D0 передачи данных во время тактов 13-16 тактового генератора CLOCK. Отметим, что на временной диаграмме, показанной на фиг. 3, временные соотношения между байтами 0-7 данных из нечетного блока 212.0 памяти, байтами 0-7 данных из четного блока 214.0 памяти, а также чередующимися байтами 0-3, 4-7 данных из соответствующих нечетных и четных блоков 212.0, 214.0 памяти сжаты для простоты иллюстрации. Также отметим, что явные иллюстрации управления мультиплексором 224.0 (и мультиплексором 224.1) посредством контроллера 204 памяти не приведены на фиг. 2b для ясности.

На фиг. 4 показан пример вычислительной системы 400, которая включает в себя запоминающее устройство 202 и контроллер 204 памяти, показанные на фиг. 2а. Как показано на фиг. 4, вычислительная система 400 также включает в себя по меньшей мере один процессор 402, в который встроен контроллер 204 памяти. В одном варианте осуществления процессор 402 и контроллер 204 памяти могут быть выполнены в виде отдельных устройств. Блок процессор/контроллер памяти 402, 204 соединен с системной памятью 202 и по меньшей мере одним периферийным устройством, таким как дисплей 404. Вычислительная система 400 также включает в себя источник 406 питания, который подает подходящее напряжение на блок процессор/контроллер памяти 402, 204 и дисплей 404, а также на запоминающее устройство 202 через блок процессор/контроллер памяти 402, 204. Например, вычислительная система 400 может представлять собой любой подходящий тип ресурса, такой как настольный компьютер, ноутбук, планшетный компьютер, мобильное устройство, смартфон, сотовый телефон, камера или любое другое подходящее вычислительное или компьютеризированное устройство, которое использует память для хранения данных.

Процессор 402 может выполнять инструкции, хранящиеся по меньшей мере в одном постоянном носителе информации, таком как запоминающее устройство 202 или любой другой подходящий носитель информации, для выполнения различных процессов в вычислительной системе 400, включая один или несколько процессов для управления действиями запоминающего устройства 202 и/или любого другого подходящего запоминающего устройства.

Запоминающее устройство 202 может включать в себя один или несколько запоминающих компонентов, таких как энергозависимая или энергонезависимая память, которая может быть реализована в виде SRAM, DRAM или любой другой подходящей энергозависимой или энергонезависимой памяти. Память 202 также может быть выполнена с возможностью хранить операционную систему, выполняемую процессором 402, и одно или несколько приложений, которые могут быть запущены операционной системой. В ответ на запрос, сгенерированный одним из приложений, процессор 402 в соединении с контроллером 204 памяти может исполнять операционную систему для выполнения операций записи/чтения данных в запоминающем устройстве 202 и/или любом другом подходящем запоминающем устройстве.

Хотя выше описаны примеры осуществления раскрытого устройства и способов, можно выполнить другие альтернативные варианты осуществления или вариации. Например, на фиг. 5а, 5b и 5с показаны альтернативные примеры осуществления 500а 500b, 500 с соответственно чипов 206.0, 206.1 памяти, показанных на фиг. 2b. Как показано на фиг. 5а, альтернативный вариант 500а осуществления включает в себя один чип 506а памяти, имеющий одну, две или более групп блоков памяти, таких как группа нечетных блоков 512а памяти и группа четных блоков 514а памяти. Чип 506а памяти также включает в себя два трансивера 516а, 518а, соединенные с 64-битовыми каналами D1, D0 передачи данных соответственно. Кроме того, чип 506а памяти включает в себя два мультиплексора 520а, 522а для выборочного соединения 11-битовых каналов CA0, CA1 управления/адресации с соответствующими группами нечетных и четных блоков 512а, 514а памяти, и два мультиплексора 524а, 526а для выборочного соединения групп нечетных и четных блоков 512а, 514а памяти с трансиверами 516а, 518а соответственно.

В показанном варианте осуществления чипа 506а памяти группа нечетных блоков 512а памяти посредством мультиплексора 520а выборочно соединена с 11-битовым каналом CA0 управления/адресации, а группа блоков четных блоков 514а памяти посредством мультиплексора 522а выборочно соединена с 11-битовым каналом CA0 управления/адресации. Каждая группа нечетных и четных блоков 512а, 514а памяти также посредством мультиплексора 526а выборочно соединена с трансивером 518а, который, в свою очередь, соединен с 64-битовым каналом D0 передачи данных. В показанном на фиг. 5а варианте осуществления мультиплексор 524а эффективно выключен и, поэтому, не передает никакие данные из групп нечетных и четных блоков 512а, 514а памяти на трансивер 516а, который, как описано выше, соединен с 64-битовым каналом D1 передачи данных. Поэтому, чип 506а памяти, показанный на фиг. 5а, выполнен с возможностью предоставлять всю свою полосу пропускания по единственному 64-битовому каналу D0 передачи данных.

Как показано на фиг. 5b, альтернативный вариант 500b осуществления включает в себя один чип 506b памяти, имеющий одну, две или более групп блоков памяти, таких как группа нечетных блоков 512b памяти и группа четных блоков 514b памяти. Чип 506b памяти также включает в себя два трансивера 516b, 518b, соединенные с 64-битовыми каналами D1, D0 передачи данных соответственно. Кроме того, чип 506b памяти включает в себя два мультиплексора 520b, 522b для выборочного соединения 11-битовых каналов CA0, CA1 управления/адресации с соответствующими группами нечетных и четных блоков 512b, 514b памяти, и два мультиплексора 524b, 526b для выборочного соединения групп нечетных и четных блоков 512b, 514b памяти с трансиверами 516b, 518b соответственно.

В показанном варианте осуществления чипа 506b памяти группа нечетных блоков 512b памяти посредством мультиплексора 520b выборочно соединена с 11-битовым каналом CA1 управления/адресации, а группа блоков четных блоков 514b памяти посредством мультиплексора 522b выборочно соединена с 11-битовым каналом CA0 управления/адресации. Группа нечетных блоков 512b памяти посредством мультиплексора 524b выборочно соединена с трансивером 516b, который, в свою очередь, соединен с 64-битовым каналом D1 передачи данных. Группа четных блоков 514b памяти посредством мультиплексора 526b выборочно соединена с трансивером 518b, который, в свою очередь, соединен с 64-битовым каналом D0 передачи данных. Поэтому, чип 506b памяти, показанный на фиг. 5b, выполнен с возможностью предоставлять половину свой полосы пропускания из группы нечетных блоков 512b памяти по 64-битовому каналу D1 передачи данных, и предоставлять половину своей полосы пропускания из группы четных блоков 514b памяти по 64-битовому каналу D0 передачи данных.

Как показано на фиг. 5с, альтернативный вариант 500с осуществления представляет собой двухранговый стек памяти (ранг 0, ранг 1), который включает в себя две пары выполненных в виде стека чипов памяти 506с.0, 506с.1 и 506с.2, 506с.3, где каждая пара выполненных в виде стека чипов 506с.0, 506с. и 506с.2, 506с.3 сконфигурирована как выполненные в виде стека чипы 206.0, 206.1 памяти, показанные на фиг. 2b. Как показано на фиг.5 с, группы нечетных и четных блоков 512с.0, 514с.0 памяти в чипе 506с.0 памяти выборочно соединены посредством соответствующих мультиплексоров 520с.0, 522с.0 с 11-битовым каналом CA0 управления/адресации, а группы нечетных и четных блоков 512с.1, 514с.1 памяти в чипе 506с.1 памяти выборочно соединены посредством соответствующих мультиплексоров 520с.1, 522с.1 с 11-битовым каналом CA1 управления/адресации. Аналогично, группы нечетных и четных блоков 512с.2, 514с.2 памяти в чипе 506с.2 памяти выборочно соединены посредством соответствующих мультиплексоров 520с.2, 522с.2 с 11-битовым каналом CA0 управления/адресации, а группы нечетных и четных блоков 512с.3, 514с.3 памяти в чипе 506с.3 памяти выборочно соединены посредством соответствующих мультиплексоров 520с.3, 522с.3 с 11-битовьгм каналом CA1 управления/адресации. Группы нечетных и четных блоков 512с.0, 514с.0 памяти в чипе 506с.0 памяти также выборочно соединены посредством мультиплексора 524с.0 и трансивера 516с.0 с 64-битовым каналом D0 передачи данных, а группы нечетных и четных блоков 512с.1, 514с.1 памяти в чипе 506с.1 памяти также выборочно соединены посредством мультиплексора 524с.1 и трансивера 516с.1 с 64-битовым каналом D1 передачи данных. Аналогично, группы нечетных и четных блоков 512с.2, 514с.2 памяти в чипе 506с.2 памяти также выборочно соединены посредством мультиплексора 524с.2 и трансивера 516с.2 с 64-битовым каналом D0 передачи данных, а группы нечетных и четных блоков 512с.3, 514с.3 памяти в чипе 506с.3 памяти также выборочно соединены посредством мультиплексора 524с.3 и трансивера 516с.3 с 64-битовым каналом D1 передачи данных. Поэтому, чип 506 с памяти, показанный на фиг. 5с, выполнен с возможностью предоставлять половину своей полосы пропускания из групп нечетных и четных блоков 512с.0, 514с.0 и 512с.2, 514с.2 памяти в соответствующих чипах 506с.0, 506с.2 памяти по 64-битовому каналу D0 передачи данных, а также предоставлять половину своей полосы пропускания из групп нечетных и четных блоков 512с.1, 514с.1 и 512с.3, 514с.3 памяти в соответствующих чипах 506с.1, 506с.3 памяти по 64-битовому каналу D1 передачи данных

Ниже со ссылкой на фиг. 2а, 2b и 6 описан способ работы системной памяти 200, включающей в себя выполненные в виде стека первый и второй чипы 206.0, 206.1 памяти. Как показано в блоке 602 (см. фиг. 6), первый мультиплексор, такой как мультиплексор 224.0 (см. фиг. 2b), выполняют в первом чипе памяти, таком как чип 206.0 памяти (см. фиг. 2а и 2b), а второй мультиплексор, такой как мультиплексор 224.1 (см. фиг. 2b), выполняют во втором чипе памяти, таком как второй чип 206.1 памяти (см. фиг. 2а и 2b). Как показано в блоке 604, данные из нечетных и четных блоков 212.0, 214.0 памяти первого чипа 206.0 памяти посредством первого мультиплексора 224.0 подают на 64-битовый канал D0 передачи данных, тем самым, предоставляя всю полосу пропускания первого чипа 206.0 памяти по одному 64-битовому каналу D0 передачи данных. Как показано в блоке 606, данные из нечетных и четных блоков 212.1, 214.1 памяти первого чипа 206.1 памяти посредством второго мультиплексора 224.1 подают на 64-битовый канал D1 передачи данных, тем самым, предоставляя всю полосу пропускания первого чипа 206.1 памяти по одному 64-битовому каналу D1 передачи данных.

В соответствии с примерами осуществления описанного устройства и способов, описанных в этом документе, предложен первый вариант осуществления стекового запоминающего устройства, который включает в себя по меньшей мере первый чип памяти и второй чип памяти, где первый чип памяти расположен на втором чипе памяти в виде стека. И первый, и второй чипы памяти включают в себя по меньшей мере первый блок памяти и второй блок памяти и по меньшей мере первый канал передачи данных и второй канал передачи данных. И первый и второй канал передачи данных выборочно могут быть соединены с первым блоком памяти и вторым блоком памяти, входящими в первый чип памяти, и выборочно могут быть соединены с первым блоком памяти и вторым блоком памяти, входящим во второй чип памяти. Первый и второй блоки памяти, входящие в первый чип памяти, могут предоставлять данные в первый канал из первого и второго каналов передачи данных, и первый и второй блоки памяти, входящие во второй чип памяти, могут предоставлять данные во второй канал из первого и второго каналов передачи данных.

В одном аспекте и первый и второй чипы памяти также включают в себя первый мультиплексор. Первый мультиплексор, входящий в первый чип памяти может выборочно передавать данные из первого и второго блоков памяти первого чипа памяти в первый канал из первого и второго каналов передачи данных, а первый мультиплексор, входящий во второй чип памяти может выборочно передавать данные из первого и второго блоков памяти второго чипа памяти во второй канал из первого и второго каналов передачи данных. Первый мультиплексор, входящий в первый чип памяти также может выборочно попеременно передавать данные из первого и второго блоков памяти первого чипа памяти в первый канал из первого и второго каналов передачи данных. Аналогично, первый мультиплексор, входящий во второй чип памяти также может выборочно попеременно передавать данные из первого и второго блоков памяти второго чипа памяти во второй канал из первого и второго каналов передачи данных.

В еще одном аспекте и первый и второй чипы памяти также включают в себя первый трансивер. Первый трансивер, входящий в первый чип памяти соединен между первым мультиплексором первого чипа памяти и первым каналом из первого и второго каналов передачи данных, а первый трансивер, входящий во второй чип памяти соединен между первым мультиплексором второго чипа памяти и вторым каналом из первого и второго каналов передачи данных.

В другом аспекте и первый, и второй чипы памяти также включают в себя второй мультиплексор. Второй мультиплексор, входящий в первый чип памяти, может выборочно передавать данные из первого и второго блоков памяти первого чипа памяти во второй канал из первого и второго каналов передачи данных, а второй мультиплексор, входящий во второй чип памяти, может выборочно передавать данные из первого и второго блоков памяти второго чипа памяти в первый канал из первого и второго каналов передачи данных. И первый, и второй чипы памяти также включают в себя второй трансивер. Второй трансивер, входящий в первый чип памяти, соединен между вторым мультиплексором первого чипа памяти и вторым каналом из первого и второго каналов передачи данных, а второй трансивер, входящий во второй чип памяти, соединен между вторым мультиплексором второго чипа памяти и первым каналом из первого и второго каналов передачи данных. И для первого, и для второго чипа памяти первый и второй трансиверы обладают соответствующей емкостью передачи, и емкость передачи первого трансивера по меньшей мере примерно в два раза больше емкости передачи второго трансивера.

В еще одном аспекте стековое запоминающее устройство также включает в себя по меньшей мере первый канал управления и адресации и второй канал управления и адресации. И первый и второй канал управления и адресации выборочно могут быть соединены с первым блоком памяти и вторым блоком памяти, входящими в первый чип памяти, и выборочно могут быть соединены с первым блоком памяти и вторым блоком памяти, входящими во второй чип памяти. И первый, и второй чипы памяти также включают в себя третий мультиплексор. Третий мультиплексор, входящий в первый чип памяти может выборочно подавать команды управления и адресации от первого канала из первого и второго каналов управления и адресации в первый блок памяти первого чипа памяти, и третий мультиплексор, входящий во второй чип памяти может выборочно подавать команды управления и адресации от второго канала из первого и второго каналов управления и адресации в первый блок памяти второго чипа памяти. И первый, и второй чипы памяти также включают в себя четвертый мультиплексор. Четвертый мультиплексор, входящий в первый чип памяти может выборочно подавать команды управления и адресации от первого канал из первого и второго каналов управления и адресации во второй блок памяти первого чипа памяти, и четвертый мультиплексор, входящий во второй чип памяти может выборочно подавать команды управления и адресации от второго канала из первого и второго каналов управления и адресации во второй блок памяти второго чипа памяти.

В еще одном аспекте предложена вычислительная система, которая включает в себя системную шину, дисплей, соединенный с системной шиной, контроллер памяти, соединенный с системной шиной, и стековое запоминающее устройство, сконфигурированное в соответствии с этим первым вариантом осуществления, в котором контроллер памяти управляет стековым запоминающим устройством. В этом первом варианте осуществления первый и второй чип памяти могут быть сконфигурированы в виде одного из следующего: динамическая память с произвольным доступом (DRAM) и статическая память с произвольным доступом (SRAM).

Во втором варианте осуществления предложен чип памяти для составления стека, который включает в себя по меньшей мере первый блок памяти и второй блок памяти и по меньшей мере первый канал передачи данных и второй канал передачи данных. И первый, и второй канал передачи данных может выборочно соединяться с первым блоком памяти и вторым блоком памяти, а первый и второй блоки памяти могут передавать данные в тот же первый или второй канал.

В одном аспекте чип памяти также включает в себя первый мультиплексор, который может выборочно передавать данные из первого и второго блоков памяти в тот же первый или второй канал передачи данных. Первый мультиплексор также может выборочно попеременно передавать данные из первого и второго блоков памяти в тот же первый или второй канал передачи данных. В другом аспекте чип памяти также включает в себя первый трансивер, соединенный между первым мультиплексором и тем же первым или вторым каналом передачи данных.

В еще одном аспекте чип памяти также включает в себя второй мультиплексор, который может выборочно передавать данные из первого и второго блоков памяти в другой первый или второй канал передачи данных, и второй трансивер, соединенный между вторым мультиплексором и другим первым или вторым каналом передачи данных. Первый и второй трансиверы обладают соответствующей емкостью передачи, и емкость передачи первого трансивера по меньшей мере может быть примерно в два раза больше емкости передачи второго трансивера.

В еще одном аспекте чип памяти также включает в себя по меньшей мере первый канал управления и адресации и второй канал управления и адресации. И первый, и второй канал управления и адресации может выборочно соединяться с первым блоком памяти и вторым блоком памяти. Чип памяти также включает в себя третий мультиплексор, который может выборочно передавать команды управления и адресации из первого или второго канала управления и адресации в первый блок памяти, и четвертый мультиплексор, который может выборочно передавать команды управления и адресации из первого или второго канала управления и адресации во второй блок памяти.

В этом втором варианте осуществления чип памяти может быть сконфигурирован в виде одного из следующего: динамическая память с произвольным доступом (DRAM) и статическая память с произвольным доступом (SRAM).

В третьем варианте осуществления в стековом запоминающем устройстве, включающем в себя по меньшей мере первый чип памяти, установленный в виде стека на второй чип памяти, и по меньшей мере первый канал передачи данных и второй канал передачи данных, в котором и первый, и второй чипы памяти включают в себя по меньшей мере первый блок памяти и второй блок памяти, предложен способ передачи данных в соответствующие первый и второй каналы передачи данных, который включает в себя следующее: берут первый мультиплексор в первом и втором чипах памяти, посредством первого мультиплексора в первом чипе памяти выборочно передают данные из первого и второго блоков памяти первого чипа памяти в первый канал из первого или второго канала передачи данных, и посредством первого мультиплексора во втором чипе памяти выборочно передают данные из первого и второго блоков памяти второго чипа памяти во второй канал из первого или второго канала передачи данных.

В одном аспекте выборочная передача данных из первого и второго блоков памяти первого чипа памяти в первый канал из первого и второго каналов передачи данных включает в себя чередующуюся выборочную передачу данных из первого и второго блоков памяти первого чипа памяти в первый канал из первого и второго каналов передачи данных, и выборочная передача данные из первого и второго блоков памяти второго чипа памяти во второй канал из первого и второго каналов передачи данных включает в себя чередующуюся выборочную передачу данных из первого и второго блоков памяти второго чипа памяти во второй канал из первого и второго каналов передачи данных.

В еще одном аспекте способ также включает в себя следующее: берут второй мультиплексор в первом и втором чипах памяти, посредством второго мультиплексора в первом чипе памяти выборочно передают данные из первого и второго блоков памяти первого чипа памяти во второй канал из первого или второго канала передачи данных, и посредством второго мультиплексора во втором чипе памяти выборочно передают данные из первого и второго блоков памяти второго чипа памяти в первый канал из первого или второго канала передачи данных.

В еще одном аспекте стековое запоминающее устройство также включает в себя по меньшей мере первый канал управления и адресации и второй канал управления и адресации, и способ также включает в себя следующее: берут третий мультиплексор в первом и втором чипах памяти, который посредством третьего мультиплексора в первом чипе памяти выборочно подает команды управления и адресации от первого канал из первого и второго каналов управления и адресации в первый блок памяти первого чипа памяти, и посредством третьего мультиплексора во втором чипе памяти выборочно передают команды управления и адресации от второго канал из первого и второго каналов управления и адресации в первый блок памяти второго чипа памяти.

В еще одном аспекте способ также включает в себя следующее: берут четвертый мультиплексор в первом и втором чипах памяти, который посредством четвертого мультиплексора в первом чипе памяти выборочно подает команды управления и адресации от первого канала из первого и второго каналов управления и адресации во второй блок памяти первого чипа памяти, и посредством четвертого мультиплексора во втором чипе памяти выборочно передают команды управления и адресации от второго канала из первого и второго каналов управления и адресации во второй блок памяти второго чипа памяти.

В четвертом варианте осуществления предложено стековое запоминающее устройство, которое включает в себя по меньшей мере первый блок памяти и второй блок памяти, по меньшей мере первый канал передачи данных и второй канал передачи данных, и первое средство выборочной передачи данных из одного или из обоих первого и второго блоков памяти в тот же первый или второй канал передачи данных. Первое средство для выборочной попеременной передачи данных из первого и второго блоков памяти в тот же первый или второй канал передачи данных.

В одном аспекте чип памяти также включает в себя первое средство для приема-передачи данных, соединенное между первым средством для выборочной передачи данных и тем же первым или вторым каналом передачи данных, второе средство для выборочной передачи данных из одного или обоих первого и второго блоков данных в другой первый или второй канал передачи данных, и второе средство для приема-передачи данных, соединенное между вторым средством для выборочной передачи данных и другим каналом из первого или второго канала передачи данных. Первое и второе средства приема-передачи данных обладают соответствующей емкостью передачи, и емкость передачи первого средства приема-передачи данных может быть по меньшей мере примерно в два раза больше емкости передачи второго средства приема-передачи данных.

В еще одном аспекте чип памяти также включает в себя по меньшей мере первый канал управления и адресации и второй канал управления и адресации, первое средство для выборочной передачи команд управления и адресации из первого или второго канала управления и адресации в первый блок памяти, и второе средство для выборочной передачи команд управления и адресации из первого или второго канала управления и адресации во второй блок памяти.

В этом четвертом варианте осуществления чип памяти может быть сконфигурирован в виде одного из следующего: динамическая память с произвольным доступом (DRAM) и статическая память с произвольным доступом (SRAM).

В пятом варианте осуществления предложен машинный носитель информации, который включает в себя исполняемые инструкции для передачи данных в первый канал передачи данных и второй канал передачи данных стекового запоминающего устройства, где стековое запоминающее устройство включает в себя по меньшей мере первый чип памяти, расположенный на втором чипе памяти в виде стека. И первый, и второй чипы памяти включают в себя по меньшей мере первый блок памяти и второй блок памяти и по меньшей мере первый мультиплексор и второй мультиплексор. Машинный носитель включает в себя исполняемые инструкции, чтобы посредством первого мультиплексора в первом чипе памяти выборочно передавать данные из первого и второго блоков памяти первого чипа памяти в первый канал из первого и второго каналов передачи данных, и посредством первого мультиплексора во втором чипе памяти выборочно передавать данные из первого и второго блоков памяти второго чипа памяти во второй канал из первого или второго канала передачи данных.

В одном аспекте машинный носитель информации также включает включают в себя исполняемые инструкции для попеременной выборочной передачи данных из первого и второго блоков памяти первого чипа памяти в первый канал из первого и второго каналов передачи данных, и для выборочной попеременной передачи данных из первого и второго блоков памяти второго чипа памяти во второй канал из первого и второго каналов передачи данных.

В другом аспекте машинный носитель информации также включает в себя исполняемые инструкции для того, чтобы посредством второго мультиплексора в первом чипе памяти попеременно выборочно передавать данные из первого и второго блоков памяти первого чипа памяти во второй канал из первого и второго каналов передачи данных, и посредством второго мультиплексора во втором чипе памяти выборочно передавать данные из первого и второго блоков памяти второго чипа памяти в первый канал из первого или второго канала передачи данных.

Вышеизложенное описание примеров осуществления приведено для иллюстрации, и не предполагается, что оно является исчерпывающим или ограничивает настоящую заявку конкретной описанной формой. В свете изложенных идей возможны модификации и изменения, или они могут быть получены из практического использования сформулированного изобретения. Например, хотя в этом документе были описаны последовательности действий со ссылкой на фиг. 6, в других реализациях порядок действий может быть изменен. Кроме того, независимые действия можно выполнять параллельно.

Очевидно, что один или несколько описанных в этом документе вариантов осуществления по меньшей мере частично могут быть реализованы в различных формах программного и/или аппаратного обеспечения. Программный код и/или специализированное аппаратное обеспечение, используемые для реализации вариантов осуществления, описанных в этом документе, не ограничивают сформулированное изобретение. Таким образом, работа и поведение некоторых вариантов осуществления были описаны в этом документе без ссылки на специфический программный код и/или специализированное аппаратное обеспечение, понятно, что специалист в области техники сможет спроектировать программное обеспечение и/или аппаратное обеспечение для реализации вариантов осуществления на основе приведенного здесь описания. Кроме того, определенные признаки сформулированного изобретения могут быть реализованы с использованием выполняемых компьютером инструкций, которые могут исполняться процессором или логикой обработки.

Отметим, что на фиг. 4 показан пример осуществления вычислительной системы 400, и что другие варианты осуществления вычислительной системы 400 могут включать в себя больше или меньше аппаратных компонентов, чем показано на фиг. 4. Кроме того, аппаратные компоненты могут быть расположены не так, как показано на фиг. 4. В дополнение, функции, выполняемые различными аппаратными компонентами, содержащимися в других вариантах осуществления вычислительной системы 400, могут быть распределены по соответствующим компонентам не так, как описано в этом документе.

Никакие используемые здесь элементы, действия или инструкции не следует рассматривать как критические или неотъемлемые для применения, если только это явно не указано. Также, предполагается, что используемые в этом документе формы единственного числа включают в себя один или несколько элементов. Там, где предполагается только один элемент, используют термин "один" или аналогичный. Кроме того, предполагается, что фраза "основан на" означает "основан по меньшей мере частично на", если иное не указано явно.

Предполагается, что применение не ограничено определенными вариантами осуществления, описанными в этом документе, но применение включает в себя любые и все определенные варианты осуществления и их эквиваленты, попадающие под объем нижеприведенной прилагаемой формулы изобретения.

| название | год | авторы | номер документа |

|---|---|---|---|

| ПОЛУПРОВОДНИКОВАЯ ПАМЯТЬ | 1993 |

|

RU2156506C2 |

| ДЕМОДУЛЯЦИЯ ДАННЫХ ДЛЯ СИСТЕМЫ СВЯЗИ CDMA | 2004 |

|

RU2337479C2 |

| СПОСОБ И УСТРОЙСТВО КОДИРОВАНИЯ И ДЕКОДИРОВАНИЯ ДАННЫХ В СКРУЧЕННОМ ПОЛЯРНОМ КОДЕ | 2014 |

|

RU2571587C2 |

| СТЕКОВАЯ ЭВМ С ПРЕФИКСНЫМИ КОМАНДАМИ | 2014 |

|

RU2581548C1 |

| ПОСЛЕДОВАТЕЛЬНО ПОДКЛЮЧЕННОЕ МЕЖСОЕДИНЕНИЕ ДЛЯ СУММИРОВАНИЯ МНОГИХ СИГНАЛОВ НА ОБЩЕМ КАНАЛЕ | 1995 |

|

RU2159011C2 |

| Вычислительная система | 1977 |

|

SU692400A1 |

| Стековое запоминающее устройство | 1987 |

|

SU1737456A1 |

| Процессор микропрограммируемой ЭВМ | 1979 |

|

SU860077A1 |

| Устройство стековой адресации | 1988 |

|

SU1513447A2 |

| Устройство параллельной обработки видеоинформации | 1984 |

|

SU1262527A1 |

Группа изобретений относится к запоминающим устройствам. Техническим результатом является увеличение скорости передачи данных и полосы пропускания системной памяти. Устройство содержит по меньшей мере два канала передачи данных; по меньшей мере два чипа памяти, установленных один на другой в виде стека, причем чипы памяти включают в себя по меньшей мере два блока памяти и по меньшей мере участок первого канала передачи данных и участок второго канала передачи данных; и по меньшей мере первое и второе соединение "чип-чип", причем первое соединение "чип-чип" выполнено с возможностью соединения соответствующих участков первого канала передачи данных, входящих в первый и второй чипы памяти, для образования первого канала передачи данных, а второе соединение "чип-чип" выполнено с возможностью соединения соответствующих участков второго канала передачи данных, входящих в первый и второй чипы памяти, для образования второго канала передачи данных, причем каждый из образованных таким образом каналов передачи данных выполнен с возможностью выборочного соединения с первым и вторым блоками памяти, входящими в первый чип памяти, и с первым и вторым блоками памяти, входящими во второй чип памяти, причем каждый из блоков памяти, входящих в первый чип памяти, выполнен с возможностью предоставления данных в один канал из образованных каналов передачи данных, а каждый из блоков памяти, входящих во второй чип памяти, выполнен с возможностью предоставления данных в другой канал из образованных каналов передачи данных. 4 н. и 21 з.п. ф-лы, 10 ил.

1. Стековое запоминающее устройство, содержащее:

по меньшей мере первый канал передачи данных и второй канал передачи данных;

по меньшей мере первый чип памяти и второй чип памяти, при этом первый чип памяти установлен на второй чип памяти в виде стека, причем и первый, и второй чипы памяти включают в себя по меньшей мере первый блок памяти и второй блок памяти и по меньшей мере участок первого канала передачи данных и участок второго канала передачи данных; и

по меньшей мере первое соединение "чип-чип" и второе соединение "чип-чип", причем первое соединение "чип-чип" выполнено с возможностью соединения соответствующих участков первого канала передачи данных, входящих в первый и второй чипы памяти, для образования первого канала передачи данных, а второе соединение "чип-чип" выполнено с возможностью соединения соответствующих участков второго канала передачи данных, входящих в первый и второй чипы памяти, для образования второго канала передачи данных,

причем каждый из образованных таким образом первого и второго каналов передачи данных выполнен с возможностью выборочного соединения с первым блоком памяти и вторым блоком памяти, входящими в первый чип памяти, и выполнен с возможностью выборочного соединения с первым блоком памяти и вторым блоком памяти, входящими во второй чип памяти,

причем каждый из первого и второго блоков памяти, входящих в первый чип памяти, выполнен с возможностью предоставления данных в один канал из образованных таким образом первого и второго каналов передачи данных, а каждый из первого и второго блоков памяти, входящих во второй чип памяти, выполнен с возможностью предоставления данных в другой канал из образованных таким образом первого и второго каналов передачи данных.

2. Устройство по п. 1, в котором каждый из первого и второго чипов памяти дополнительно включает в себя первый мультиплексор, причем первый мультиплексор, входящий в первый чип памяти, выполнен с возможностью выборочного предоставления данных из первого и второго блоков памяти первого чипа памяти в указанный один канал из первого и второго каналов передачи данных, а первый мультиплексор, входящий во второй чип памяти, выполнен с возможностью выборочного предоставления данных из первого и второго блоков памяти второго чипа памяти в указанный другой канал из первого и второго каналов передачи данных.

3. Устройство по п. 2, в котором первый мультиплексор, входящий в первый чип памяти, дополнительно выполнен с возможностью выборочного предоставления данных из первого и второго блоков памяти первого чипа памяти в указанный один канал из первого и второго каналов передачи данных чередующимся образом, а первый мультиплексор, входящий во второй чип памяти, дополнительно выполнен с возможностью выборочного предоставления данных из первого и второго блоков памяти второго чипа памяти в указанный другой канал из первого и второго каналов передачи данных чередующимся образом.

4. Устройство по п. 2, в котором каждый из первого и второго чипов памяти дополнительно включает в себя первый приемопередатчик, причем первый приемопередатчик, входящий в первый чип памяти, подключен между первым мультиплексором первого чипа памяти и указанным одним каналом из первого и второго каналов передачи данных, а первый приемопередатчик, входящий во второй чип памяти, подключен между первым мультиплексором второго чипа памяти и указанным другим каналом из первого и второго каналов передачи данных.

5. Устройство по п. 4, в котором каждый из первого и второго чипов памяти дополнительно включает в себя второй мультиплексор, причем второй мультиплексор, входящий в первый чип памяти, выполнен с возможностью выборочного предоставления данных из первого и второго блоков памяти первого чипа памяти в указанный другой канал из первого и второго каналов передачи данных, а второй мультиплексор, входящий во второй чип памяти, выполнен с возможностью выборочного предоставления данных из первого и второго блоков памяти второго чипа памяти в указанный один канал из первого и второго каналов передачи данных.

6. Устройство по п. 5, в котором каждый из первого и второго чипов памяти дополнительно включает в себя второй приемопередатчик, причем второй приемопередатчик, входящий в первый чип памяти, подключен между вторым мультиплексором первого чипа памяти и указанным другим каналом из первого и второго каналов передачи данных, а второй приемопередатчик, входящий во второй чип памяти, подключен между вторым мультиплексором второго чипа памяти и указанным одним каналом из первого и второго каналов передачи данных.

7. Устройство по п. 6, в котором для каждого из первого и второго чипов памяти:

каждый из первого и второго приемопередатчиков обладает связанной с ним емкостью передачи; и

емкость передачи первого приемопередатчика по меньшей мере примерно в два раза больше емкости передачи второго приемопередатчика.

8. Устройство по п. 1, дополнительно содержащее:

по меньшей мере первый канал управления и адресации и второй канал управления и адресации, причем каждый из первого и второго каналов управления и адресации выполнен с возможностью выборочного соединения с первым блоком памяти и вторым блоком памяти, входящими в первый чип памяти, и выборочного соединения с первым блоком памяти и вторым блоком памяти, входящими во второй чип памяти.

9. Устройство по п. 8, в котором каждый из первого и второго чипов памяти дополнительно включает в себя третий мультиплексор, причем третий мультиплексор, входящий в первый чип памяти, выполнен с возможностью выборочного предоставления команд управления и адресации из одного канала из первого и второго каналов управления и адресации в первый блок памяти первого чипа памяти, а третий мультиплексор, входящий во второй чип памяти, выполнен с возможностью предоставления команд управления и адресации из другого канала из первого и второго каналов управления и адресации в первый блок памяти второго чипа памяти.

10. Устройство по п. 8, в котором каждый из первого и второго чипов памяти дополнительно включает в себя четвертый мультиплексор, причем четвертый мультиплексор, входящий в первый чип памяти, выполнен с возможностью выборочного предоставления команд управления и адресации из указанного одного канала из первого и второго каналов управления и адресации во второй блок памяти первого чипа памяти, а четвертый мультиплексор, входящий во второй чип памяти, выполнен с возможностью выборочного предоставления команд управления и адресации из указанного другого канала из первого и второго каналов управления и адресации во второй блок памяти второго чипа памяти.

11. Устройство по п. 1, в котором каждый из первого и второго чипов памяти выполнен в виде динамической памяти с произвольным доступом (DRAM) или статической памяти с произвольным доступом (SRAM).

12. Составляемый в стек чип памяти, содержащий:

по меньшей мере первый блок памяти и второй блок памяти;

по меньшей мере участок первого канала передачи данных и участок второго канала передачи данных, и

по меньшей мере первое соединение "чип-чип" и второе соединение "чип-чип", причем первое соединение "чип-чип" предназначено для соединения участка первого канала передачи данных, входящего в указанный чип памяти, и участка первого канала передачи данных, входящего в другой чип памяти, для образования первого канала передачи данных, а второе соединение "чип-чип" предназначено для соединения участка второго канала передачи данных, входящего в указанный чип памяти, и участка второго канала передачи данных, входящего в указанный другой чип памяти, для образования второго канала передачи данных;

причем каждый из первого и второго каналов передачи данных выполнен с возможностью выборочного соединения с первым блоком памяти и вторым блоком памяти,

при этом первый и второй блоки памяти выполнены с возможностью предоставления данных в один и тот же канал из образованных таким образом первого и второго каналов передачи данных.

13. Чип памяти по п. 12, дополнительно содержащий:

первый мультиплексор, выполненный с возможностью выборочной передачи данных из первого и второго блоков памяти в указанный один и тот же канал из первого и второго каналов передачи данных.

14. Чип памяти по п. 13, в котором первый мультиплексор дополнительно выполнен с возможностью выборочного предоставления данных из первого и второго блоков памяти в указанный один и тот же канал из первого и второго каналов передачи данных чередующимся образом.

15. Чип памяти по п. 13, дополнительно содержащий:

первый приемопередатчик, подключенный между первым мультиплексором и указанным одним и тем же каналом из первого и второго каналов передачи данных.

16. Чип памяти по п. 15, дополнительно содержащий:

второй мультиплексор, выполненный с возможностью выборочного предоставления данных из первого и второго блоков памяти в другой канал из первого или второго каналов передачи данных; и

второй приемопередатчик, подключенный между вторым мультиплексором и указанным другим каналом из первого и второго каналов передачи данных.

17. Чип памяти по п. 16, в котором каждый из первого и второго приемопередатчиков обладает связанной с ним емкостью передачи, причем емкость передачи первого приемопередатчика по меньшей мере примерно в два раза больше емкости передачи второго приемопередатчика.

18. Чип памяти по п. 12, дополнительно содержащий:

по меньшей мере первый канал управления и адресации и второй канал управления и адресации, причем каждый из первого и второго каналов управления и адресации выполнен с возможностью выборочного соединения с первым блоком памяти и вторым блоком памяти.

19. Чип памяти по п. 18, дополнительно содержащий:

третий мультиплексор, выполненный с возможностью выборочного предоставления команд управления и адресации из одного канала из первого и второго каналов управления и адресации в первый блок памяти; и

четвертый мультиплексор, выполненный с возможностью выборочного предоставления команд управления и адресации из одного канала из первого и второго каналов управления и адресации во второй блок памяти.

20. Чип памяти по п. 12, выполненный в виде динамической памяти с произвольным доступом (DRAM) или статической памяти с произвольным доступом (SRAM).

21. Способ предоставления данных, выполняемый в стековом запоминающем устройстве, включающем в себя по меньшей мере первый чип памяти, установленный в виде стека на второй чип памяти, и по меньшей мере первый канал передачи данных и второй канал передачи данных, причем каждый из первого и второго чипов памяти включает в себя по меньшей мере первый блок памяти и второй блок памяти и по меньшей мере участок первого канала передачи данных и участок второго канала передачи данных, при этом в способе предоставляют данные в соответствующие первый и второй каналы передачи данных, при этом способ содержит этапы, на которых:

обеспечивают по меньшей мере первое соединение "чип-чип" и второе соединение "чип-чип";

соединяют при помощи первого соединения "чип-чип" соответствующие участки первого канала передачи данных, входящие в первый и второй чипы памяти, для образования первого канала передачи данных;

соединяют при помощи второго соединения "чип-чип" соответствующие участки второго канала передачи данных, входящие в первый и второй чипы памяти, для образования второго канала передачи данных;

обеспечивают первый мультиплексор в каждом из первого и второго чипов памяти,

посредством первого мультиплексора в первом чипе памяти выборочно предоставляют данные из первого и второго блоков памяти первого чипа памяти в один канал из образованных таким образом первого и второго каналов передачи данных; и

посредством первого мультиплексора во втором чипе памяти выборочно предоставляют данные из первого и второго блоков памяти второго чипа памяти в другой канал из образованных таким образом первого и второго каналов передачи данных.

22. Способ по п. 21, в котором на этапе выборочного предоставления данных из первого и второго блоков памяти первого чипа памяти в указанный один канал из первого и второго каналов передачи данных выборочно предоставляют данные из первого и второго блоков памяти первого чипа памяти в указанный один канал из первого и второго каналов передачи данных чередующимся образом, а на этапе выборочного предоставления данных из первого и второго блоков памяти второго чипа памяти в указанный другой канал из первого и второго каналов передачи данных выборочно предоставляют данные из первого и второго блоков памяти второго чипа памяти в указанный другой канал из первого и второго каналов передачи данных чередующимся образом.

23. Способ по п. 21, дополнительно содержащий этапы, на которых:

обеспечивают второй мультиплексор в каждом из первого и второго чипов памяти;

посредством второго мультиплексора в первом чипе памяти выборочно представляют данные из первого и второго блоков памяти первого чипа памяти в указанный другой канал из первого и второго каналов передачи данных;

посредством второго мультиплексора во втором чипе памяти выборочно представляют данные из первого и второго блоков памяти второго чипа памяти в указанный один канал из первого и второго каналов передачи данных.

24. Машиночитаемый носитель информации, включающий в себя исполняемые инструкции для предоставления данных в первый канал передачи данных и второй канал передачи данных стекового запоминающего устройства, причем стековое запоминающее устройство включает в себя по меньшей мере первый чип памяти, установленный в виде стека на второй чип памяти, при этом каждый из первого и второго чипов памяти включает в себя по меньшей мере первый блок памяти и второй блок памяти и по меньшей мере участок первого канала передачи данных и участок второго канала передачи данных, и по меньшей мере первый мультиплексор и второй мультиплексор, при этом машиночитаемый носитель информации содержит исполняемые инструкции:

для выборочного предоставления данных, посредством первого мультиплексора в первом чипе памяти, из первого и второго блоков памяти первого чипа памяти в один канал из первого и второго каналов передачи данных, причем каждый из первого и второго чипов памяти дополнительно включают в себя по меньшей мере первое соединение "чип-чип" и второе соединение "чип-чип", причем первое соединение "чип-чип" предназначено для соединения соответствующих участков первого канала передачи данных, входящих в первый и второй чипы памяти, для образования первого канала передачи данных, а второе соединение "чип-чип" предназначено для соединения участков второго канала передачи данных, входящих в первый и второй чипы памяти, для образования второго канала передачи данных; и

для выборочного предоставления данных, посредством первого мультиплексора во втором чипе памяти, из первого и второго блоков памяти второго чипа памяти в другой канал из образованных таким образом первого и второго каналов передачи данных.

25. Машиночитаемый носитель информации по п. 24, дополнительно содержащий исполняемые инструкции:

для выборочного предоставления данных из первого и второго блоков памяти первого чипа памяти в указанный один канал из первого и второго каналов передачи данных чередующимся образом; и

для выборочного предоставления данных из первого и второго блоков памяти второго чипа памяти в указанный другой канал из первого и второго каналов передачи данных чередующимся образом.

| Пресс для выдавливания из деревянных дисков заготовок для ниточных катушек | 1923 |

|

SU2007A1 |

| Приспособление для суммирования отрезков прямых линий | 1923 |

|

SU2010A1 |

| Изложница с суживающимся книзу сечением и с вертикально перемещающимся днищем | 1924 |

|

SU2012A1 |

| Приспособление для суммирования отрезков прямых линий | 1923 |

|

SU2010A1 |

| Логическое запоминающее устройство | 1986 |

|

SU1316047A1 |

Авторы

Даты

2017-11-27—Публикация

2014-05-29—Подача