Изобретение относится к автоматике и аналоговой вычислительной технике и может быть использовано для построения функциональных узлов аналоговых вычислительных машин, средств автоматического регулирования и управления, аналоговых процессоров. Техническим результатом является расширение функциональных возможностей управления аналоговыми вычислениями, повышение быстродействия и снижение габаритов по сравнению с цифровыми системами и устройствами. Для достижения указанного технического результата предлагается включить в цепи управления аналоговыми вычислениями проверку условий вычислений и ограничений на значения выходных сигналов, исключить цифровую и программную обработку сигналов.

Область техники.

Изобретение относится к автоматике и аналоговой вычислительной технике и может быть использовано для построения функциональных узлов аналоговых вычислительных машин, средств автоматического регулирования и управления, аналоговых процессоров.

Уровень техники.

К настоящему времени известны многочисленные варианты аналоговых процессоров, позволяющих выполнять сравнение, селекцию и ранжирование аналоговых сигналов [1, 2, 3, 4, 5]. Общим недостатком этих устройств является узкая функциональная специализация, отсутствие возможности выполнять функции логического вывода с использованием систем продукционных правил.

Наиболее близко по технической сущности к предлагаемому устройству является устройство представления и использования знаний [6], структура которого ориентирована на логический вывод в процессе интерпретации сложных информационных структур на аппаратном уровне. Устройство содержит N блоков простых отношений над понятиями, блок интерфейса, блок логического вывода, блок обработки, блок памяти.

Недостатком прототипа является высокая техническая сложность, применение цифровой и программной обработки продукционных правил, необходимость применения АЦП для обработки аналоговых сигналов, что значительно снижает возможности использования прототипа в малогабаритной и быстродействующей аппаратуре.

Задача изобретения - повышение функциональных возможностей аналоговых устройств с помощью включения в их состав схем обработки продукционных правил.

Технический результат изобретения состоит в повышении функциональных возможностей аналоговых устройств за счет введения в их состав схемных функций логической обработки продукционных правил, повышении быстродействия и уменьшения габаритов устройств, основанных на обработке знаний.

Поставленная цель в аналоговом процессоре с функциями управления вычислениями достигается тем, что в его состав включены: устройство ситуационного управления (ситуатор) проверки условия обработки, ситуатор коммутации функции, ситуатор проверки ограничений, ситуатор вывода результатов, входы аналогового блока ситуатора проверки условий подключены к входам подачи проверяемого напряжения U, ограничивающих напряжений Umin и Umax, входы логического блока ситуатора проверки условий подключены к входам подачи сигналов готовности проверяемого и ограничивающих напряжений, выход аналогового блока ситуатора проверки условий подключен к первому входу логического блока ситуатора коммутации функции, выход логического блока ситуатора проверки условий подключен ко второму входу логического блока ситуатора коммутации функции, вход аналогового блока ситуатора коммутации функции подключен к входу подачи сигнала вычисляемой функции F, третий вход логического блока ситуатора коммутации функции подключен к входу подачи сигнала готовности вычисляемой функции, выход аналогового блока ситуатора коммутации функции подключен к первому входу аналогового блока ситуатора проверки ограничений и к входу аналогового блока ситуатора вывода результатов вычислений, выход логического блока ситуатора коммутации функции подключен к первому входу логического блока проверки ограничений и к первому входу логического блока вывода результатов вычислений, второй вход аналогового блока ситуатора проверки ограничений подключен к входу подачи минимального ограничивающего напряжения Umin,огр, третий вход аналогового блока ситуатора проверки ограничений подключен к входу подачи максимального ограничивающего напряжения Umax,огр, второй вход логического блока ситуатора проверки ограничений подключен к входу подачи сигнала готовности минимального ограничивающего напряжения, третий вход логического блока ситуатора проверки ограничений подключен к входу подачи сигнала готовности максимального ограничивающего напряжения, выход аналогового блока ситуатора проверки ограничений подключен ко второму входу логического блока ситуатора вывода результатов, выход логического блока ситуатора проверки ограничений подключен к третьему входу логического блока ситуатора вывода результатов, выходы аналогового и логического блоков ситуатора вывода результатов подключены к выходам аналогового процессора.

Перечисленные отличительные признаки заявляемых изобретений позволяют повысить скорость обработки продукционных правил по сравнению с программно-цифровой обработкой, снизить техническую сложность и габариты устройства за счет перехода от цифровой обработки, требующей аналого-цифровых преобразований и применения микропроцессорной техники, к непосредственной логической обработке аналоговых сигналов, расширить функциональные возможности аналоговых устройств за счет схем управления вычислениями.

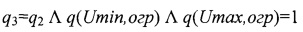

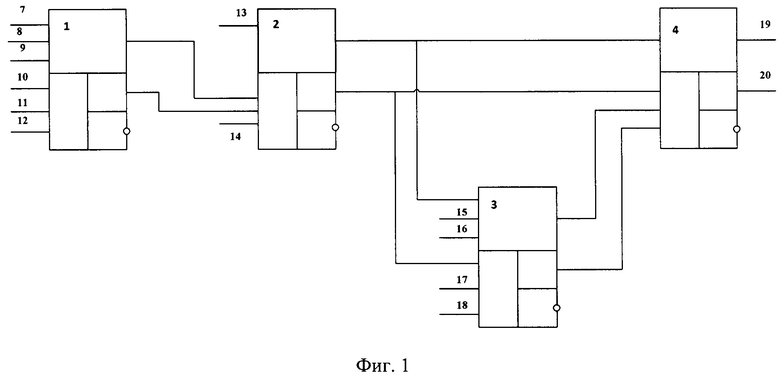

На фиг. 1 представлена структурная схема устройства.

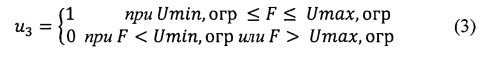

Аналоговый процессор с функциями управления вычислениями содержит устройство ситуационного управления (ситуатор) проверки условия (1), ситуатор коммутации функции (2), ситуатор проверки ограничений (3), ситуатор вывода результатов (4). Ситуатор проверки условия обработки (1) проверяет выполнение ограничений в антецедентной части продукционного правила, ситуатор коммутации функции (2) выполняет передачу аналогового сигнала на ситуатор вывода результатов (4) в случае выполнения условий вычислений, ситуатор проверки ограничений (3) сравнивает значения аналогового сигнала с ограничивающими напряжениями, ситуатор вывода результатов (4) передает на выход устройства сформированный кортеж из аналогового сигнала и логического сигнала подтверждения вычисления функции. Каждый ситуатор состоит из аналогового блока 5 и логического блока 6 (фиг. 2) [7]. Аналоговый блок 5 выполняет обработку аналоговых сигналов и передает на выход значение аналоговой функции в случае, когда условия вычисления выполнено. Логический блок 6 проверяет возможность выполнения вычислений по логическим сигналам, подтверждающим выполнение условий, и передает на выход логический сигнал подтверждения вычисления аналоговой функции.

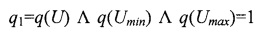

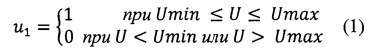

Аналоговый процессор с функциями управления вычислениями работает следующим образом (фиг. 1). На входы аналогового блока ситуатора проверки условий 1 подаются: проверяемое напряжение U (вход 7), ограничивающие напряжения Umin (вход 8) и Umax (вход 9). На входы логического блока ситуатора проверки условий 1 подаются: сигнал готовности проверяемого напряжения q(U) (вход 10), сигнал готовности ограничивающего напряжения q(Umin) (вход 11), сигнал готовности ограничивающего напряжения q(Umax) (вход 12). Ситуатор проверки условий 1 выполняет проверку условий и передает на выход аналогового блока двухуровневое напряжение u1, если сигнал готовности на выходе логического блока  . Напряжение u1 рассчитывается по правилам:

. Напряжение u1 рассчитывается по правилам:

С выхода аналогового блока ситуатора проверки условий 1 сигнал проверки u1 подается на первый вход логического блока ситуатора коммутации функции 2, с выхода логического блока ситуатора проверки условий 1 сигнал готовности q1 подается на второй вход логического блока ситуатора коммутации функции 2. На вход 13 аналогового блока ситуатора коммутации функции 2 подается аналоговый сигнал функции F. На третий вход 14 логического блока ситуатора проверки условий подается сигнал готовности qF вычисляемой функции F.

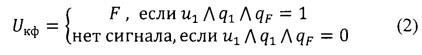

Сигнал Uкф на выходе аналогового блока ситуатора коммутации функции 2 будет иметь значение, вычисляемое по правилу:

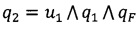

Сигнал q2 на выходе логического блока ситуатора коммутации функции 2 будет иметь значения  .

.

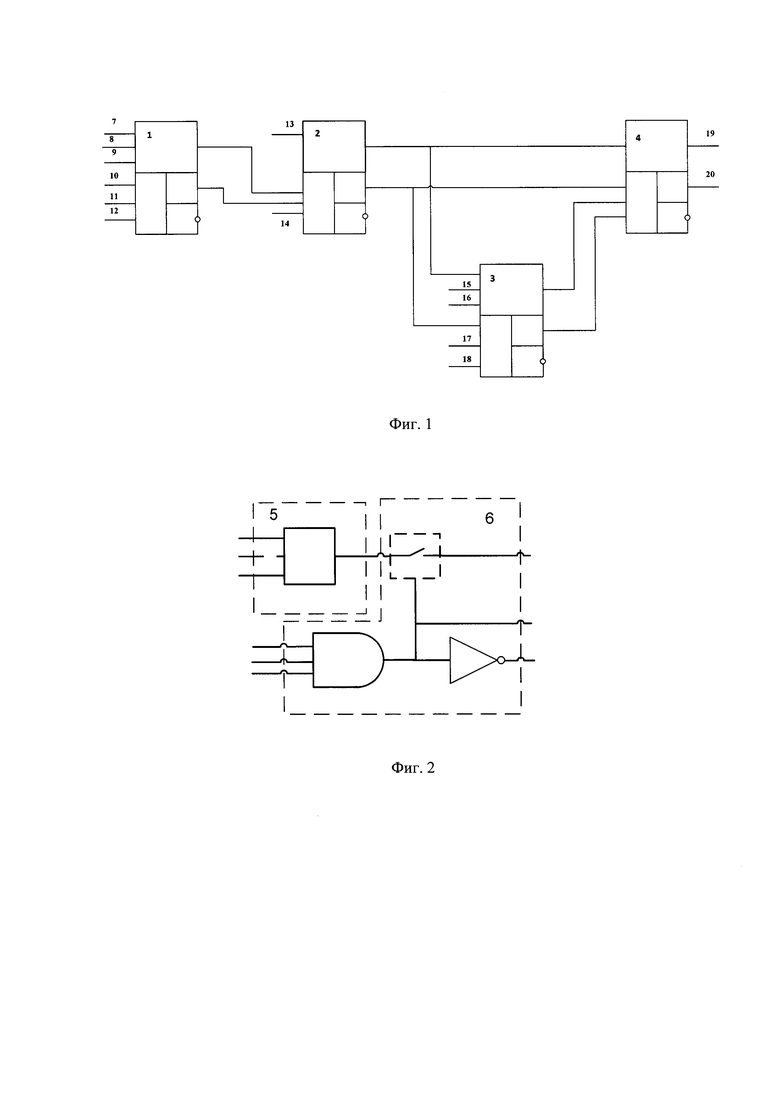

Ситуатор проверки ограничений 3 выполняет проверку значения функции F. На входы аналогового блока ситуатора проверки ограничений 3 подаются: напряжение значения функции F (первый вход), ограничивающие напряжения Umin,огр и Umax,огр на второй 15 и третий 16 входы блока. На входы логического блока ситуатора проверки ограничений 3 подаются: сигнал готовности проверяемого напряжения q2 (первый вход), сигнал готовности ограничивающего напряжения q(Umin,огр) на второй вход 17, сигнал готовности ограничивающего напряжения q(Umax,огр) на третий вход 18. Ситуатор проверки ограничений 3 выполняет проверку условий и передает на выход аналогового блока двухуровневое напряжение u3 при значении сигнала готовности q3 на выходе логического блока  по правилам:

по правилам:

С выхода аналогового блока ситуатора проверки ограничений 3 сигнал проверки u3 подается на второй вход логического блока ситуатора вывода результатов 4, с выхода логического блока ситуатора проверки ограничений 3 сигнал готовности проверки q3 подается на третий вход логического блока ситуатора вывода результатов 4. На вход аналогового блока ситуатора вывода результатов 4 подается сигнал вычисляемой функции F с выхода аналогового блока ситуатора коммутации функции 2, а на первый вход логического блока ситуатора вывода результатов 4 подается сигнал готовности q2. выхода 19 аналогового блока ситуатора вывода результатов 4 выходное напряжение функции F полается на аналоговый выход устройства, с выхода 20 логического блока ситуатора вывода результатов 4 выходное напряжение сигнала готовности QF подается на логический выход устройства.

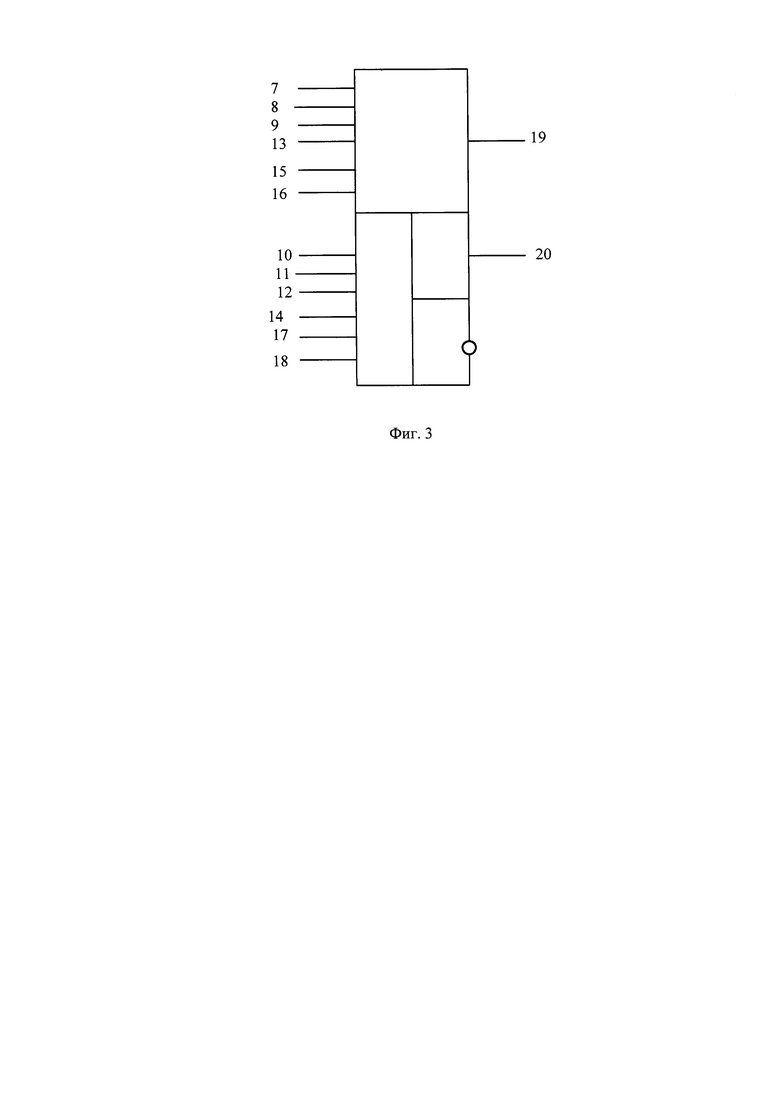

На (фиг. 3) показано изображение аналогового процессора с функциями управления вычислениями на принципиальной электрической схеме с номерами контактов подключения.

Вышеизложенные сведения позволяют сделать вывод, что предлагаемый аналоговый процессор с функциями управления вычислениями обеспечивает реализацию функций логического вывода по заданным в антецедентной части продукционного правила условиям, а также обладает меньшими по сравнению с прототипом аппаратурными затратами. Достоинством предлагаемого аналогового процессора с функциями управления вычислениями является высокая скорость обработки продукционного правила, т.к. производится только аппаратными средствами без использования программной обработки и преобразований аналогового сигнала в цифровой код.

Источники информации

1. Патент RU №2173879 кл. G06G 7/25, опубликован 20.09.2001 г.

2. Патент RU №2281551 кл. G06G 7/52, опубликован 10.08.2006 г.

3. Патент RU №2446462 кл. G06G 7/52, опубликован 27.03.2012 г.

4. Патент RU №2474875 кл. G06G 7/52, опубликован 10.02.2013 г.

5. Патент RU №2514784 кл. G06G 7/25, опубликован 10.05.2014 г.

6. Патент RU №2092895 кл. G06F 15/16, опубликован 10.10.1997 г.

7. Дембицкий Н.Л. Способ управления аналоговыми вычислениями и устройство ситуационного управления для его осуществления. RU 2541850, МПК G06G 7/25.

Изобретение относится к автоматике и аналоговой вычислительной технике и может быть использовано для построения функциональных узлов аналоговых вычислительных машин, средств автоматического регулирования и управления, аналоговых процессоров. Техническим результатом является повышение быстродействия и снижение габаритов устройства. Устройство содержит устройство ситуационного управления (ситуатор) для проверки условия вычисления, ситуатор коммутации функции, ситуатор проверки ограничений, ситуатор вывода результатов. 3 ил.

Аналоговый процессор с функциями управления вычислениями, содержащий устройство ситуационного управления (ситуатор) проверки условий обработки, ситуатор коммутации функции, ситуатор проверки ограничений, ситуатор вывода результатов, входы аналогового блока ситуатора проверки условий подключены к входам подачи проверяемого напряжения U, ограничивающих напряжений Umax и Umin, входы логического блока ситуатора проверки условий подключены к входам подачи сигналов готовности проверяемого и ограничивающих напряжений, выход аналогового блока ситуатора проверки условий подключен к первому входу логического блока ситуатора коммутации функции, выход логического блока ситуатора проверки условий подключен ко второму входу логического блока ситуатора коммутации функции, вход аналогового блока ситуатора коммутации функции подключен к входу подачи сигнала вычисляемой функции F, третий вход логического блока ситуатора коммутации функции подключен к входу подачи сигнала готовности вычисляемой функции, выход аналогового блока ситуатора коммутации функции подключен к первому входу аналогового блока ситуатора проверки ограничений и к входу аналогового блока ситуатора вывода результатов вычислений, выход логического блока ситуатора коммутации функции подключен к первому входу логического блока проверки ограничений и к первому входу логического блока вывода результатов вычислений, второй вход аналогового блока ситуатора проверки ограничений подключен к входу подачи минимального ограничивающего напряжения Umin,огр, третий вход аналогового блока ситуатора проверки ограничений подключен к входу подачи максимального ограничивающего напряжения Umax,огр, второй вход логического блока ситуатора проверки ограничений подключен к входу подачи сигнала готовности минимального ограничивающего напряжения, третий вход логического блока ситуатора проверки ограничений подключен к входу подачи сигнала готовности максимального ограничивающего напряжения, выход аналогового блока ситуатора проверки ограничений подключен ко второму входу логического блока ситуатора вывода результатов, выход логического блока ситуатора проверки ограничений подключен к третьему входу логического блока ситуатора вывода результатов, выходы аналогового и логического блоков ситуатора вывода результатов подключены к выходам аналогового процессора.

| УСТРОЙСТВО ПРЕДСТАВЛЕНИЯ И ИСПОЛЬЗОВАНИЯ ЗНАНИЙ | 1991 |

|

RU2092895C1 |

| СПОСОБ УПРАВЛЕНИЯ АНАЛОГОВЫМИ ВЫЧИСЛЕНИЯМИ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2013 |

|

RU2541850C2 |

| ЧЕТКИЙ ЛОГИЧЕСКИЙ РЕГУЛЯТОР ДЛЯ УПРАВЛЕНИЯ ТЕХНОЛОГИЧЕСКИМИ ПРОЦЕССАМИ | 2010 |

|

RU2445669C2 |

| RU 93015088 A, 20.09.1995 | |||

| US 5701400 A, 23.12.1997 | |||

| JPH09258983 A, 03.10.1997. | |||

Авторы

Даты

2018-03-16—Публикация

2017-03-22—Подача