Изобретение относится к автоматике и аналоговой вычислительной технике и может быть использовано для построения функциональных узлов аналоговых вычислительных машин, средств автоматического регулирования и управления, аналоговых процессоров. Техническим результатом является расширение функциональных возможностей управления аналоговыми вычислениями по сравнению с прототипом. Для достижения указанного технического результата предлагается включить в цепи управления аналоговыми вычислениями проверку условий вычислений и ограничений на значения выходного сигналов.

Область техники

Изобретение относится к автоматике и аналоговой вычислительной технике и может быть использовано для построения функциональных узлов аналоговых вычислительных машин, средств автоматического регулирования и управления, аналоговых процессоров.

Уровень техники

К настоящему времени известны многочисленные варианты аналоговых процессоров, позволяющих выполнять сравнение, селекцию и ранжирование аналоговых сигналов [1, 2, 3, 4, 5]. Общим недостатком этих устройств является узкая функциональная специализация, отсутствие возможности применения аналоговых процессоров в качестве универсального элемента электронных схем устройств автоматического управления. Данный недостаток приводит к необходимости применения в устройствах автоматического управления гибридных схем, в которых вначале выполняется аналого-цифровые преобразования сигналов, а затем формирование с помощью вычислительных устройств сигналов управления [6]. Применение дополнительных цифровых устройств приводит к снижению быстродействия и увеличению потребляемой мощности устройств автоматического управления, а также к ухудшению их массогабаритных характеристик.

Наиболее близким по технической сущности к предлагаемому устройству является унифицированное устройство ситуационного управления (ситуатор) для осуществления управления аналоговыми вычислениями [7], содержащее аналоговый блок, реализующий функцию обработки F(y1, y2, …, yk1), управляемый замыкающий ключ, логический блок, выполняющий логическую функцию «И» входных предикатных переменных - x1 Λ х2 … Λ xk2 (k1≤k2), инвертор. Входы аналогового блока подключены к аналоговым входам ситуатора, выход аналогового блока подключен к первому информационному контакту ключа, второй информационный контакт ключа подключен к аналоговому выходу ситуатора; логические входы ситуатора подключены к входам логического блока, выход логического блока подключен к управляющему входу ключа, к первому логическому выходу ситуатора и к инвертору, выход инвертора подключен ко второму логическому выходу ситуатора.

Недостатком прототипа является анализ вычислительного процесса исключительно по признакам подачи на входы необходимых для исчисления выходной функции входных сигналов. В прототипе не анализируются условия применения функции и ограничения на ее значения. Это сужает применимость ситуационного процессора в сложных вычислительных устройствах.

Задача изобретения - повышение функциональных возможностей аналоговых устройств с помощью включения в их состав схем логической обработки состояния вычислительного процесса и как следствие, расширение возможности применения их в сложных вычислительных устройствах.

Техническим результатом является расширение функциональных возможностей управления аналоговыми вычислениями и более глубокая структурная унификация аналоговых процессоров по сравнению с прототипом, что делает данное техническое решение универсальным средством для решения задач автоматического управления. Для достижения указанного технического результата предлагается включить в цепи управления аналоговыми вычислениями проверку условий вычислений и ограничений на значения выходных сигналов.

Поставленная цель в континуальном процессоре (КП) достигается тем, что в его состав включены: аналоговый блок вычисления выходной функции y=ƒ(x1, x2, … xn) 1 (Фиг. 1), блок вычисления логической функции условия θ(x x1, x2, … xn) 2, блок вычисления логической функции ограничения ϕ(y, x1, x2, … xn) 3, два инвертора 4, логическая схема 3-И 5, два управляемых замыкающих ключа 6, два резистора 7, аналоговые входы 8 блоков 1, 2 и 3 (Фиг. 1) подключены к аналоговым входам 9 (Фиг. 2) КП, вход первого инвертора 4 подключен к инвертирующему логическому входу 10 КП и к первому выводу первого резистора 7, выход первого инвертора 4 подключен к первому входу логической схемы 3-И 5, второй вывод первого резистора 7 заземлен, второй вход логической схемы 3-И 5 подключен к логическому входу 11 подачи сигнала готовности входных сигналов КП, третий вход логической схемы 3-И 5 подключен к выходу блока 2 вычисления логической функции условия, выход аналогового блока 1 вычисления выходной функции подключен к входному контакту первого ключа 6 и к функциональному входу 12 блока 3 вычисления логической функции ограничения, выход логической схемы 3-И 5 подключен к управляющему входу второго замыкающего ключа 6, выход блока 3 подключен к входному контакту второго ключа 6, выходной контакт второго ключа 6 подключен к входу второго инвертора 4, к первому выводу второго резистора 7, к управляющему входу первого замыкающего ключа 6 и к логическому выходу 13 КП, второй вывод второго резистора 7 заземлен, выходной контакт первого ключа 6 подключен к аналоговому выходу 14 КП, выход второго инвертора 4 подключен к инверсному логическому выходу 15 КП.

Перечисленные отличительные признаки в заявляемом изобретении позволяют расширить функциональные возможности аналоговых устройств за счет схем управления вычислениями.

На фиг. 1 представлена функциональная схема КП. Изображение устройства на принципиальной схеме показано на фиг. 2.

Расчет значения параметра y=ƒ(x1, x2, … xn) выполняется при подаче на входы 9 КП аналоговых сигналов x1, x2, … xn. Одновременно на вход 11 поступает логический сигнал готовности входных аналоговых сигналов, а на вход 10 логический сигнал в случае блокировки вычислений.

Аналоговый блок 1 вычисляет значение функции y=ƒ(x1, x2, … xn), передает исчисленное значение на первый информационный вход ключа 6 и на функциональный вход 12 блока 3.

Для того, чтобы некорректные результаты не попали на аналоговый выход 14 выполняется блокировка передачи выходного сигнала первым ключом 6, который разрывает выходную цепь. Первый ключ 6 управляется логическим сигналом, который передается через второй ключ 6 из блока проверки ограничений 3. На функциональный вход 12 блока 3 с выхода блока 1 поступает сигнал исчисленного значения функции y=ƒ(x1, x2, … xn), а с аналоговых входов 9 устройства на аналоговые входы 8 поступают входные аналоговые сигналы. В блоке 3 проверяются ограничения на значения функции y=ƒ(x1, x2, … xn). В качестве элементов сравнения в блоке 3 применяются компараторы, ограничивающие параметры которых задают входные сигналы x1, x2, … xn.

На выходе блока 3 функция ϕ принимает одно из двух значений:

Если логическая функция проверки ограничений ϕ(y, x1, x2, … xn)=1 и второй ключ 6 замкнут, то первый ключ 6 замыкается и результат вычисления функции y=ƒ(x1, x2, … xn) в блоке 1 попадает на выход 14 КП. Если логическая функция проверки ограничений ϕ(y, x1, x2, … xn)=0 и второй ключ 6 замкнут, то первый ключ 6 остается в разомкнутом состоянии и результат вычисления функции y=ƒ(x1, x2, … xn) в блоке 1 не попадает на выход 14 КП. При разомкнутом втором ключе 6 на втором выводе второго резистора 7 и на управляющем входе первого ключа 6 будет нулевой потенциал, первый ключ 6 остается в разомкнутом состоянии и результат вычисления функции y=ƒ(x1, x2, … xn) в блоке 1 не попадает на выход 14 КП.

Замыкание второго ключа 6 происходит при подаче на его управляющий вход логического уровня «1» с выхода логической схемы 3-И 5. Логическая схема 3-И 5 выполняет конъюнкцию логических сигналов: готовности входных параметров qГ, отрицания блокировки  и выполнения условий расчета.

и выполнения условий расчета.

Сигнал блокировки (qбл=1) передается с инвертирующего логического входа 10 устройства через первый инвертор 4 на первый вход логической схемы 3-И 5.

Сигнал готовности входных параметров qГ поступает на второй вход логической схемы 3-И 5 с логического входа 11 КП. Он получает значение логической «1», если на аналоговые входы 8 КП поданы значения всех параметров x1, x2, … xn. Если хотя бы один параметр из множества {x1, x2, … xn } не был получен, то qГ=0.

Сигнал логической функции θ(x1, x2, … xn) выполнения условий расчета исчисляется в блоке 2. Функция 9 принимает одно из двух значений:

Резисторы 7 в логических цепях устройства включены для обнуления входных уровней при отсутствии сигналов.

При замыкании второго ключа 6, и при выполнении ограничений (1) одновременно с передачей на аналоговый выход 14 КП значения параметра у на логический выход 13 КП с первого вывода второго резистора 7 передается сигнал готовности q=1. Сигнал q также, как и значение параметра у является составной частью результата расчета. При размыкании второго ключа 6 или при невыполненных ограничениях (1) сигнал готовности q=0. На инверсный логический выход 15 через второй инвертор 4 передается сигнал q, обратный сигналу q.

Значения логических функций ϕ(y, x1, x2, … xn) и θ(x1, x2, … xn) исчисляется на основе сравнения аналоговых сигналов во временном континууме. Таким образом, управление ключами 6 происходит непрерывно, и все выходные сигналы КП непрерывно изменяют в темпе изменения сигналов на входах КП.

Патентуемый КП эффективен в задачах управления быстродействующими техническими и технологическими процессами. Такие системы требуют параметрического анализа состояния объекта и среды в реальном масштабе времени для подключения тех или иных процедур и функций управления. Рассмотрим простой пример применения устройства.

Предположим, что требуется сформировать сигнал управления

Функция ƒ1(x1, x2) в задаче имеет максимальный приоритет. Она применяется в случае, если оба сигнала x1 и х2 поданы на вход устройства, условия выбора функции ƒ1 не нарушены и выполнены ограничения на значение Z=ƒ1(x1, x2). Функция ƒ2(x1) применяется, когда нарушено хотя бы одно требование на применение функции ƒ1, на вход подан сигнал x1, условия выбора функции ƒ2 не нарушены и выполнены ограничения на значение Z=ƒ2(x1). Функция ƒ3(х3) применяется, когда нарушено хотя бы одно требование на применение функций ƒ1 и ƒ2, на вход подан сигнал x2, условия выбора функции ƒ3 не нарушены и выполнены ограничения на значение Z=ƒ3(x2).

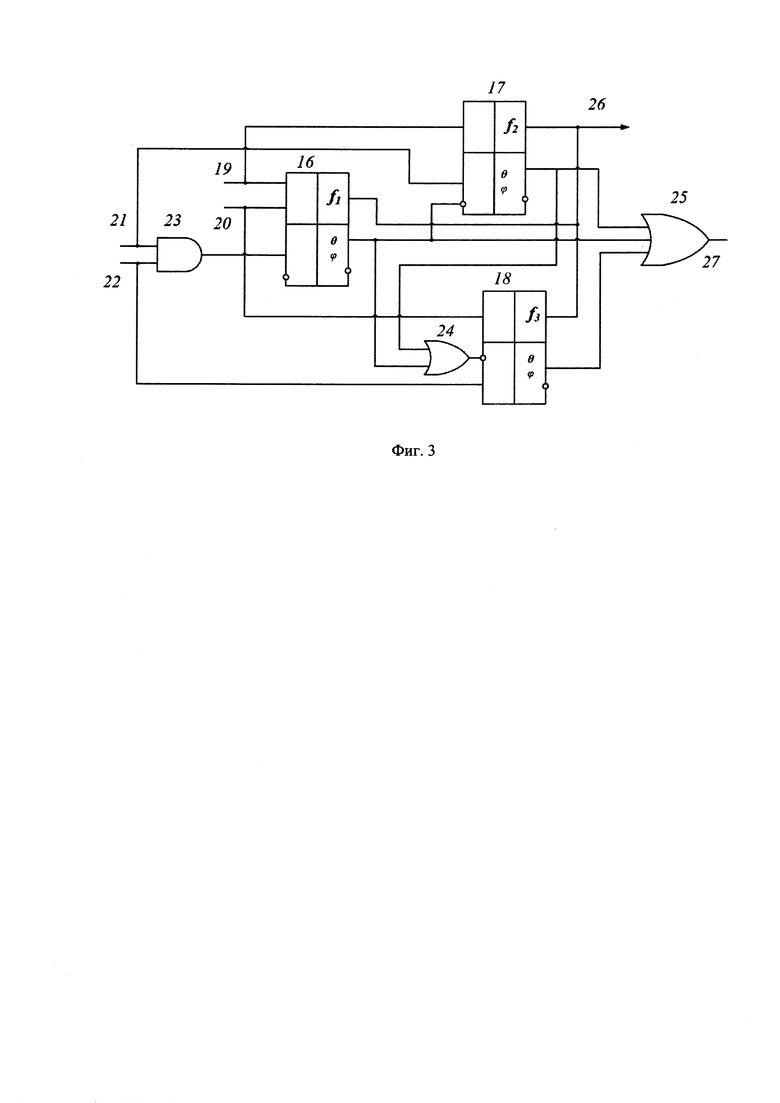

Задача реализована в виде селектора функций (СФ) соединением трех КП: 16, 17, 18 (Фиг. 3). СФ обрабатывает аналоговые сигналы х1 и х2, которые поступают на входы 19 и 20. На входы 21 и 22 подаются логические уровни признаков подачи сигналов (готовность) q1 и q2. Для управления работой в СФ включены логические схемы 2И 23, 2ИЛИ 24 и 3ИЛИ 25. КП 16 реализует функцию ƒ1(x1, x2). КП 17 реализует функцию ƒ2(x1). КП 18 реализует функцию ƒ3(x2).

В селекторе вычисления организованы так, что функции, имеющие больший приоритет, автоматически блокируют расчетные функции с меньшим приоритетом. Блокировка выполняется передачей сигналов на инверсные логические выходы устройства с меньшим приоритетом с логических выходов устройств с большим приоритетом. Поскольку по условиям задачи функции ƒ1, ƒ2, ƒ3 не могут выполнятся одновременно, функциональные выходы трех КП закорочены 26, а логические выходы КП дизъюнктивно объединены 27.

Включение в цепи управления аналоговыми вычислениями логических функций позволяют по сравнению с существующими техническими решениями аналоговых процессоров:

• расширить функциональные возможности аналоговых процессоров в направлении введения дополнительных функций управления вычислениями,

• за счет унификации структуры КП реализовать универсальный подход к созданию аналоговых процессоров, снизить трудоемкость и сложность разработки аналоговых процессоров, решающих разнообразные вычислительные задачи,

• за счет унификации представления сигналов на входах и выходах применять КП в качестве составных частей сложных аналоговых процессоров, работа которых основывается на логике обработки сигналов,

• за счет исключения цифровой обработки повысить быстродействие функционально-логических операций над аналоговыми сигналами.

Вышеизложенные сведения позволяют сделать вывод, что предлагаемый КП обеспечивает по сравнению с прототипом заявленные преимущества.

Проведенный заявителем анализ уровня техники позволил установить, что аналоги, характеризующиеся совокупностями существенных признаков, тождественными всем признакам заявленного КП, отсутствуют, что указывает на соответствие заявленного изобретения условию патентоспособности "новизна".

Предложенное устройство являются промышленно применимыми к существующим техническим средствам и соответствуют критерию «изобретательский уровень», так как они явным образом не следуют из уровня техники.

Таким образом, предложенное техническое решение соответствует установленным условиям патентоспособности изобретения.

1. Патент RU №2173879 МПК G06G 7/25 опубликован 20.09.2001 г.

2. Патент RU №2281551 МПК G06G 7/52 опубликован 10.08.2006 г.

3. Патент RU №2446462 МПК G06G 7/52 опубликован 27.03.2012 г.

4. Патент RU №2474875 МПК G06G 7/52 опубликован 10.02.2013 г.

5. Патент RU №2514784 МПК G06G 7/25 опубликован 10.05.2014 г.

6. R.G. Sanfelice. Analysis and Design of Cyber-Physical Systems. A Hybrid Control Systems Approach // Cyber-Physical Systems: From Theory to Practice / D. Rawat, J. Rodrigues, I. Stojmenovic. - CRC Press, 2016. - ISBN 978-1-4822-6333-6.

7. Патент RU №2541850, МПК G06G 7/25 опубликован 20.02.2015 г.

| название | год | авторы | номер документа |

|---|---|---|---|

| СПОСОБ УПРАВЛЕНИЯ АНАЛОГОВЫМИ ВЫЧИСЛЕНИЯМИ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2013 |

|

RU2541850C2 |

| АНАЛОГОВЫЙ МУЛЬТИПЛЕКСОР | 2012 |

|

RU2504900C1 |

| АНАЛОГОВЫЙ ПРОЦЕССОР | 2017 |

|

RU2676422C1 |

| Способ хранения и считывания аналоговых значений функций многих переменных | 2017 |

|

RU2656704C1 |

| РАНГОВЫЙ ФИЛЬТР | 2013 |

|

RU2543307C2 |

| РАНГОВЫЙ СОРТИРОВЩИК | 2006 |

|

RU2324222C1 |

| РАНГОВЫЙ ФИЛЬТР | 2015 |

|

RU2620199C1 |

| РАНГОВЫЙ СОРТИРОВЩИК | 2006 |

|

RU2324223C1 |

| РАНГОВЫЙ СОРТИРОВЩИК | 2007 |

|

RU2338249C1 |

| Способ управления реакцией нейропроцессора на входные сигналы | 2018 |

|

RU2724784C2 |

Изобретение относится к континуальному процессору. Технический результат заключается в повышении эффективности управления аналоговыми вычислениями. Процессор содержит соединенные между собой аналоговый блок вычисления выходной функции y=ƒ(x1, x2, … xn), блок вычисления логической функции условия θ(x1, x2, … xn), блок вычисления логической функции ограничения ϕ(y, x1, x2, … xn), два инвертора, логическую схему 3-И, два управляемых замыкающих ключа, два резистора. 3 ил.

Континуальный процессор (КП), в состав которого входят аналоговый блок вычисления выходной функции y=ƒ(x1, x2, … xn), блок вычисления логической функции условия θ(x1, x2, … xn), блок вычисления логической функции ограничения ϕ(y, x1, x2, … xn), два инвертора, логическая схема 3-И, два управляемых замыкающих ключа, два резистора, аналоговые входы блоков вычисления выходной функции y=ƒ(x1, x2, … xn), вычисления логической функции условия θ(x1, x2, … xn), вычисления логической функции ограничения подключены к аналоговым входам КП, вход первого инвертора подключен к инвертирующему логическому входу подачи на КП блокирующего сигнала и к первому выводу первого резистора, выход первого инвертора подключен к первому входу логической схемы 3-И, второй вывод первого резистора заземлен, второй вход логической схемы 3-И подключен к логическому входу подачи сигнала готовности входных сигналов КП, третий вход логической схемы 3-И подключен к выходу блока вычисления логической функции условия, выход аналогового блока вычисления выходной функции подключен к входному контакту первого ключа и к функциональному входу блока вычисления логической функции ограничения, выход логической схемы 3-И подключен к управляющему входу второго замыкающего ключа, выход блока вычисления логической функции ограничения подключен к входному контакту второго ключа, выходной контакт второго ключа подключен к входу второго инвертора, к первому выводу второго резистора, к управляющему входу первого замыкающего ключа и к логическому выходу КП, второй вывод второго резистора заземлен, выходной контакт первого ключа подключен к аналоговому выходу КП, выход второго инвертора подключен к инверсному логическому выходу КП.

| СПОСОБ УПРАВЛЕНИЯ АНАЛОГОВЫМИ ВЫЧИСЛЕНИЯМИ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2013 |

|

RU2541850C2 |

| АНАЛОГОВЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ | 2013 |

|

RU2514784C1 |

| АНАЛОГОВЫЙ ПРОЦЕССОР | 2012 |

|

RU2474875C1 |

| АНАЛОГОВЫЙ ПРОЦЕССОР | 2011 |

|

RU2446462C1 |

| АНАЛОГОВЫЙ ПРОЦЕССОР | 2005 |

|

RU2281551C1 |

| АНАЛОГО-РАНГОВЫЙ ПРОЦЕССОР | 2000 |

|

RU2173879C1 |

| Способ восстановления спиралей из вольфрамовой проволоки для электрических ламп накаливания, наполненных газом | 1924 |

|

SU2020A1 |

Авторы

Даты

2020-12-28—Публикация

2020-09-25—Подача