Область техники, к которой относится изобретение

Настоящее изобретение относится к устройству обработки данных и к способу обработки данных, и, более конкретно, например, к устройству обработки данных и способу обработки данных, которые выполнены с возможностью повышения устойчивости к ошибке данных.

Уровень техники

Код LDPC (проверки на четность низкой плотности) имеет высокую способность коррекции ошибок и, в последнее время, например, началось его широкое использования для системы передачи, которая включает в себя спутниковую цифровую широковещательную передачу данных, такую как DVB (Цифровая широковещательная передача видеоданных)-S.2 (например, см. Непатентный документ 1), которая используется в Европе. Кроме того, пересматривается возможность использования кода LDPC для наземной цифровой широковещательной передачи следующего поколения.

В соответствии с последними исследованиями, можно понять, что при использовании кода LDPC, аналогично турбокоду и т.п., могут быть достигнуты возможности, близкие к пределу Шеннона, по мере увеличения длины кода. Кроме того, поскольку код LDPC имеет такое свойство, что минимальное расстояние представляет собой пропорцию длины кода, LDPC имеет хорошую характеристику относительно вероятности ошибки блоков и имеет преимущество, состоящее в том, что так называемое, явление нижнего уровня ошибки, которое наблюдается в характеристиках декодирования Турбо кода и т.п., в основном, не возникает.

Далее код LDPC будет описан более конкретно. Код LDPC представляет собой линейный код и здесь будет описан, как имеющий две размерности, что не является необходимым.

Код LDPC имеет отличительную характеристику, состоящую в том, что матрица проверки на четность, которая определяет код LDPC, является разреженной. Здесь разреженная матрица представляет собой матрицу, в которой число элементов "1" матрицы очень мало (матрица, в которой большая часть элементов представляют собой "0").

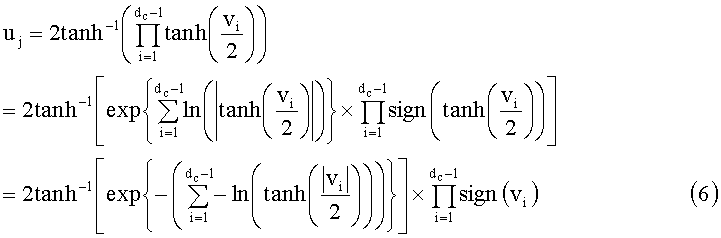

На фиг.1 иллюстрируется пример матрицы Н проверки на четность кода LDPC.

В матрице Н проверки на четность, показанной на фиг.1, вес (количество "1") (вес столбца) каждого столбца составляет "3", и вес (вес строки) каждой строки составляет "6".

При кодировании (кодировании LDPC) в соответствии с кодом LDPC, например, матрицу G генерирования генерируют на основе матрицы Н проверки на четность, и кодовое слово (код LDPC) генерируют путем умножения битов информации в двух размерностях на матрицу G генерирования.

Более конкретно, устройство кодирования, которое выполняет кодирование LDPC, вначале вычисляет матрицу G генерирования, которая удовлетворяет уравнению GHT=0 при HT, представляющей собой транспонированную матрицу для матрицы Н проверки на четность. Здесь, в случае, когда матрица G генерирования представляет собой матрицу К×N, устройство кодирования генерирует кодовое слово с (=uG), формируемое N битами, путем умножения матрицы G генерирования на строку битов (вектор u) битов информации, сформированных К битами. Кодовое слово (код LDPC), которое генерируется с помощью устройства кодирования, принимают на стороне приема через заданный канал связи.

Декодирование кода LDPC представляет собой алгоритм, предложенный Галлагером, который назвал его вероятностным декодированием, и может быть выполнено в соответствии с алгоритмом передачи сообщений, который основан на распространении доверия, о так называемом, графе Таннера, который сформирован переменным узлом (также называется узлом сообщения) и проверочным узлом. Ниже переменный узел и проверочный узел будут просто называться узлами, в соответствующих местах.

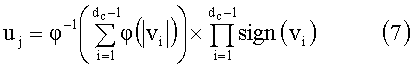

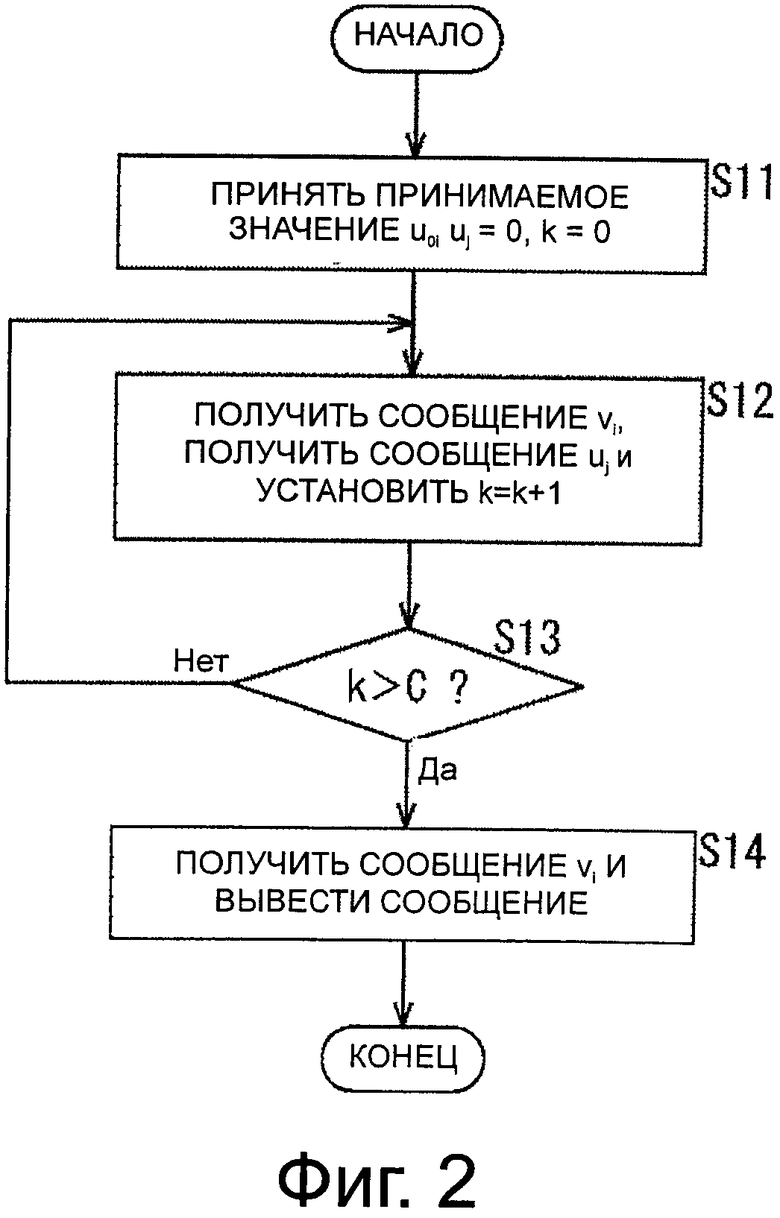

На фиг.2 иллюстрируется последовательность декодирования кода LDPC.

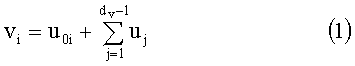

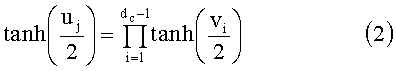

Ниже реальное значение (принятый LLR), который получают путем представления вероятности "0" для значения i-ого кодового бита для кода LDPC (одно кодовое слово), который принимают на стороне приема, как логарифмическое отношение правдоподобия, также будет называться принятым значением u0i, насколько это соответствует. Кроме того, сообщение, которое выводят из узла проверки, обозначено, как uj, и сообщение, которое выводят от переменного узла, обозначено, как vi.

Вначале, при декодировании кода LDPC, как показано на фиг.2, на этапе S11, код LDPC инициализирует сообщение (сообщение узла проверки) uj, переводя его в "0", переменную k, которая принимает целое число, как счетчик процесса повторения, инициализируют, сбрасывая ее в "0", и обработка переходит на этап S12. На этапе S12, на основе принятого значения u0i, которое получают путем приема кода LDPC, получают сообщение (сообщение переменного узла) vi, выполняя вычисление (вычисление переменного узла), представленное в Уравнении (1), и сообщение uj получают, выполняя вычисление (вычисление проверочного узла), представленное в Уравнении (2), на основе сообщения vi.

Уравнение 1

Уравнение 2

Здесь dv и dc, представленные в Уравнениях (1) и (2), представляют собой параметры, которые представляют количество "1" матрицы Н проверки на четность в вертикальном направлении (столбец) и в горизонтальном направлении (строка), которые могут быть выбраны произвольно, и, например, в случае кода (3, 6), dv=3 и dc=6.

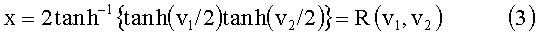

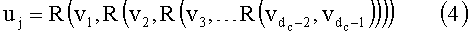

Кроме того, при вычислении переменного узла в соответствии с Уравнением (1) и при вычислении проверочного узла в соответствии с Уравнением (2), каждое сообщение, вводимое из ответвления (ребра) (линия, соединяющая переменный узел и проверочный узел), в который должно быть выведено сообщение, не установлено, как цель вычисления, и, соответственно, диапазоны вычисления составляют от 1 до dv-1 и от 1 до dc-1. Вычисление проверочного узла, представленное в Уравнении (2), фактически выполняют путем комбинирования таблицы функции R (v1, v2), представленной в Уравнении (3), которая определена, как выход двух входов v1 и v2, заранее и последовательно (рекурсивно), используя таблицу, представленную в Уравнении (4).

Уравнение 3

Уравнение 4

Кроме того, на этапе S12, переменную k последовательно увеличивают на единицу, и обработка переходит на этап S13. На этапе S13 определяют, больше или нет переменная k заданного количества С повторений декодирования. На этапе S13, в случае, когда переменную k определяют, как не большую, чем С, обработка возвращается на этап S12, и ту же обработку повторяют.

С другой стороны, в случае, когда переменную k определяют, как превышающую С, на этапе S13, обработка переходит на этап S14, сообщение vi, как результат декодирования, который выводят в конечном итоге, получают, выполняя вычисление, представленное в Уравнении (5), и выводят, на чем обработка декодирования кода LDPC заканчивается.

Уравнение 5

Здесь вычисление, представленное в Уравнении (5), в отличие от вычисления переменного узла, представленного в Уравнении (1), выполняют, используя сообщение uj, подаваемое из всех ответвлений, которые соединены с переменным узлом.

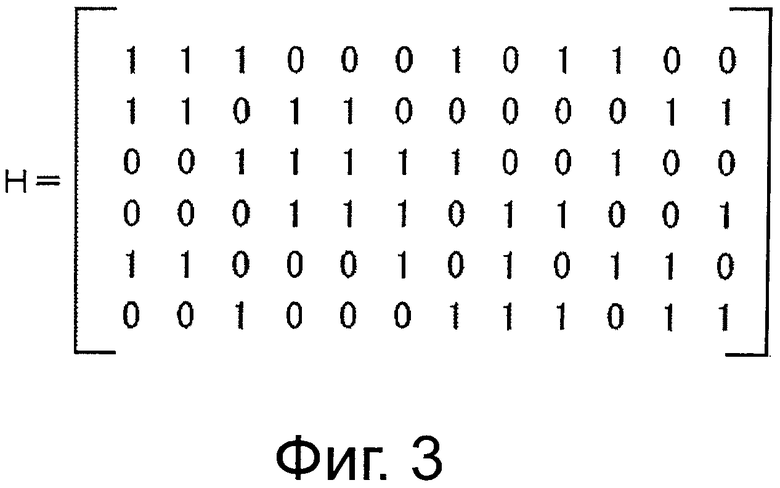

На фиг.3 иллюстрируется пример матрицы Н проверки на четность для кода LDPC (3, 6) (скорость кодирования 1/2, длина кода 12).

В матрице Н проверки на четность, представленной на фиг.3, аналогично тому, что показано на фиг.1, вес столбца равен 3, и вес строки равен 6.

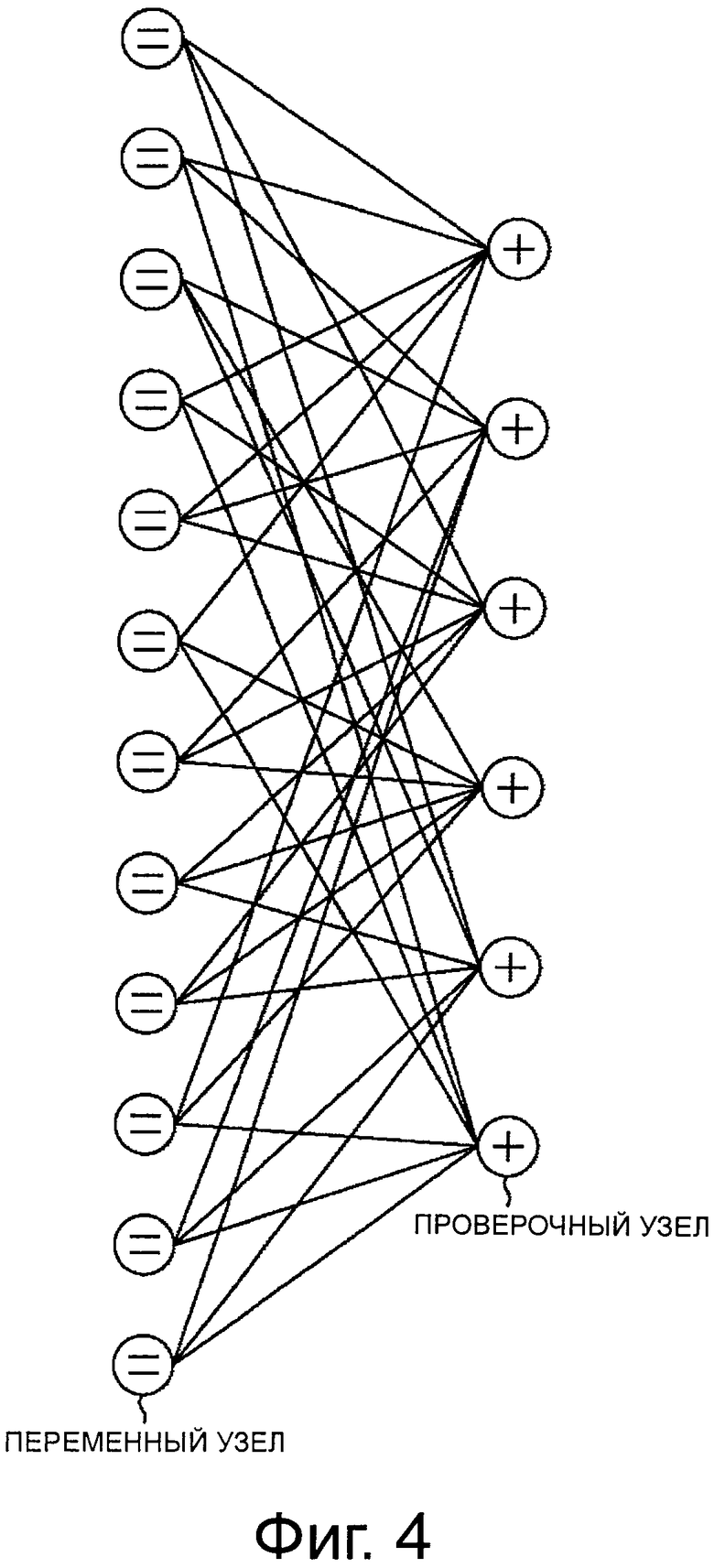

На фиг.4 иллюстрируется граф Таннера матрицы Н проверки на четность, представленной на фиг.3.

Здесь, на фиг.4, узел, который обозначен знаком "плюс" "+", представляет собой проверочный узел, и узел, который обозначен знаком "равенства" "=", представляет собой переменный узел. Проверочный узел и переменный узел соответствуют строке и столбцу матрицы Н проверки на четность. Линия, проведенная между проверочным узлом и переменным узлом, представляет собой ответвление (ребро) и соответствует "1" элемента матрицы проверки на четность.

Другими словами, в случае, когда элемент j-ой строки и i-ого столбца матрицы проверки на четность равен "1", на фиг.4, i-ый переменный узел (узел "=") сверху и j-ый проверочный узел (узел "+") сверху соединены ответвлением. Ответвление представляет, что кодовый бит, соответствующий переменному узлу, имеет ограниченное условие, соответствующее проверочному узлу.

Алгоритм суммы - произведения, представляет собой способ декодирования кода LDPC, в котором вычисление переменного узла и вычисление проверочного узла выполняются многократно.

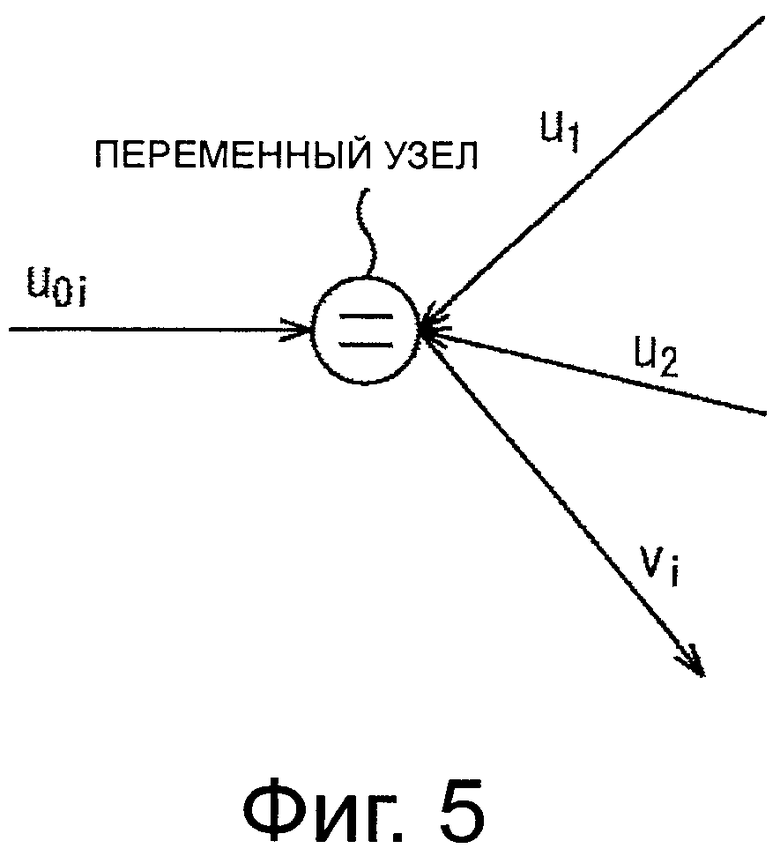

На фиг.5 иллюстрируется вычисление переменного узла, которое выполняют на переменном узле.

В переменном узле сообщение vi, которое соответствует ответвлению, которое представляет собой цель вычисления, получают с помощью вычисления переменного узла, который представлен в Уравнении (1), используя сообщения u1 и u2, подаваемые из остальных ответвлений, соединенных с переменным узлом, и принятое значение u0i. Сообщения, которые соответствуют другим ответвлениям, получают таким же образом.

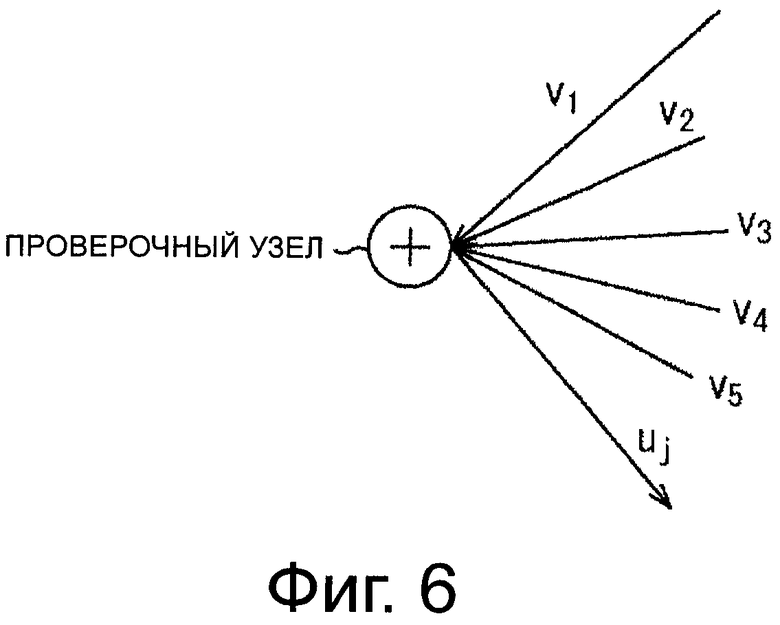

На фиг.6 иллюстрируется вычисление проверочного узла, которое выполняют в проверочном узле.

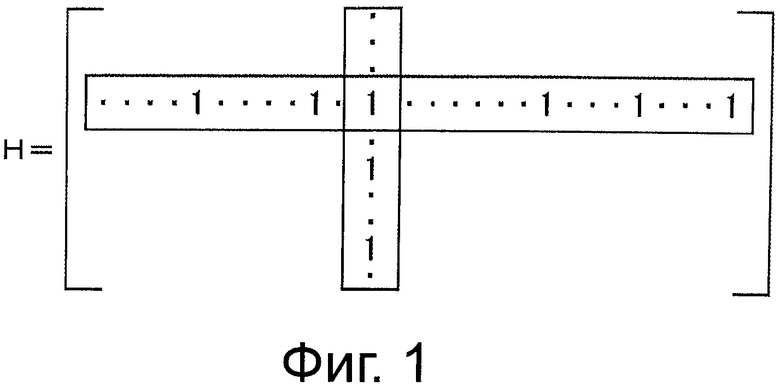

Здесь вычисление проверочного узла, представленное в Уравнении (2), может быть перезаписано в Уравнение (6), используя уравнения а×b=exp{ln(|а|)+ln(|b|)}×sign(a)×sign(b). Здесь, sign (х) представляет собой 1, когда х≥0, и представляет собой -1, когда х<0.

Уравнение 6

В случае, когда х≥0, когда функция φ(х) определена, как уравнение φ(х)=ln(tanh(х/2)), уравнение φ-1(х)=2tanh-1(e-x), удовлетворяется, и, соответственно. Уравнение (6) может быть преобразовано в Уравнение (7).

Уравнение 7

В проверочном узле вычисление проверочного узла, представленное в Уравнении (2), выполняют на основе Уравнения (7).

Другими словами, в проверочном узле, как представлено на фиг.6, сообщение uj, которое соответствует ответвлению, которое представляет собой цель вычисления, может быть получено путем вычисления проверочного узла, представленного в Уравнении (7), используя сообщения v1, v2, v3, v4 и v5, подаваемые из остальных ответвлений, соединенных с проверочным узлом. Сообщения, соответствующие другим ответвлениям, получают таким же образом.

Кроме того, функция ϕ(х), представленная в Уравнении (7), может быть представлена, как уравнение of ϕ(х)=ln((ex+1)/(ex-1)), и ϕ(х)=ϕ-1(х) for х>0. При выполнении функции ϕ(х) и ϕ-1(х) в аппаратных средствах, возникают случаи, когда функции воплощают, используя LUT (справочные таблицы), и LUT являются одинаковыми для обеих функций.

Список литературы

Непатентный документ

Непатентный документ 1: DVB-S.2: ETSI EN 302 307 VI. 1.2 (2006-06)

Раскрытие изобретения

Задачи, решаемые изобретением

Код LDPC используется в DVB-S.2, который представляет собой стандарт спутниковой цифровой широковещательной передачи, или DVB-T.2, который представляет собой стандарт наземной цифровой широковещательной передачи следующего поколения. Кроме того, код LDPC, как планируется, должен использоваться в DVB-C.2, который представляет собой стандарт цифровой широковещательной передачи CATV следующего поколения (кабельное телевидение).

В цифровой широковещательной передаче, которая соответствует стандарту DVB, такому, как DVB-S.2, код LDPC установлен (символизирован), как символ ортогональной модуляции (цифровой модуляции), такой как QPSK (квадратурная манипуляция с фазовым сдвигом), и символ преобразуют на сигнальную точку и передают.

При символизации кода LDP обмен кодовыми битами кода LDPC выполняют в единицах по два или больше кодовых битов, и кодовые биты после обмена рассматриваются, как символьные биты.

Для обмена кодовыми битами для символизации кода LDPC, предложены различные системы, и, например, такие системы определены также в DVB-T.2.

Однако, DVB-T.2 представляет собой стандарт цифровой широковещательной передачи, который специализированно используют для фиксированных оконечных устройств, таких как телевизионные приемники, установленные в домах и т.п., и, может не соответствовать цифровой широковещательной передаче, которая специально используется для мобильных оконечных устройств.

Другими словами, размеры схемы мобильных оконечных устройств должны быть меньшими, чем у фиксированных оконечных устройств, и должно быть достигнуто меньшее потребление энергии мобильным оконечным устройством. В соответствии с этим, при цифровой широковещательной передаче, которая специально используется для мобильных оконечных устройств, для уменьшения нагрузки, необходимой для обработки, такой как декодирование кода LDPC и т.п. в мобильном оконечном устройстве, например, возникают случаи, когда количество повторений при декодировании кода LDPC (количество С повторений) или длина кода LDPC ограничены в большей степени, чем при цифровой широковещательной передачи, которая специально используется для фиксированных оконечных устройств.

Однако, даже при таких ограничениях, устойчивость к ошибкам должна поддерживаться в определенной степени.

Настоящее изобретение было разработано с учетом такой ситуации и предназначено для улучшения устойчивости к ошибке данных, таких как код LDPC.

Решения задач

В соответствии с первым аспектом настоящего изобретения, предложено устройство обработки данных или способ обработки данных, включающие в себя средство кодирования, которое выполняет кодирование с использованием кода LDPC, имеющего длину кода 4320 битов и скорость кодирования 1/2, или выполняет кодирование с использованием кода LDPC, имеющего длину кода 4320 битов и скорость кодирования 1/2, при этом матрица проверки на четность кода LDPC составлена путем размещения элементов 1 информационной матрицы, определенных на основе таблицы исходного значения матрицы проверки на четность для матрицы проверки на четность, представляющей положения элементов 1 информационной матрицы, соответствующих длине информации в соответствии с длиной кода и скоростью кодирования для каждых 72 столбцов, в направлении столбцов, с периодом 72 столбца, и таблицу исходного значения матрицы проверки на четность формируют следующим образом:

142 150 213 247 507 538 578 828 969 1042 1781 1612 1584 1509 1315 1107 1934 2106 2117

3 17 20 31 97 466 571 580 842 983 1480 1465 1413 1392 1261 1226 1152 2047 2125

49 169 258 548 582 839 873 881 931 995 1906 1865 1826 1776 1654 1639 1209 1145 1956

148 393 396 486 568 806 909 965 1947 1844 1736 1664 1534 1402 1371 1306 1256 1203 2055

185 191 263 290 384 769 981 1071 1926 1910 1880 1842 1815 1769 1723 1554 1357 1202 1991

424 444 923 1679

91 436 535 978

362 677 821 1695

1454 1392 1117 2030

35 840 1477 2152

1061 1836 1202 1879

242 286 1140 1538

111 240 481 760

59 1268 1899 2144

737 1395 1299 2072

34 288 810 1903

232 1013 1365 1729

410 783 1066 1187

113 885 1423 1560

760 909 1475 2048

68 254 420 1867

283 325 334 970

168 321 479 554

378 836 1913 1928

101 238 964 1393

304 460 1497 1588

151 192 1075 1614

297 313 677 1303

329 447 1348 1832

582 831 984 1900.

В соответствии со вторым аспектом настоящего изобретения, предложено устройство или способ обработки данных, состоящий в обработке данных, включающее в себя средство кодирования, которое выполняет кодирование с использованием кода LDPC, имеющего длину кода 4320 битов и скорость кодирования 7/12, или выполняет кодирование с использованием кода LDPC, имеющего длину кода 4320 битов и скорость кодирования 7/12, при этом матрица проверки на четность кода LDPC выполнена путем размещения элементов 1 информационной матрицы, которые определяют на основе таблицы исходного значения матрицы проверки на четность для матрицы проверки на четность, представляющей положения элементов 1 информационной матрицы, соответствующей длине информации в соответствии с длиной кода и скоростью кодирования для каждых 72 столбцов, в направлении столбца, в период 72 столбца, и таблицу исходного значения матрицы проверки на четность формируют следующим образом:

96 246 326 621 668 748 874 965 1022 1627 1481 1469 1300 1142 1117 1108 1702

22 79 122 127 339 359 516 587 1025 1681 1651 1594 1484 1478 1294 1143 1794

80 426 429 506 599 810 892 1016 1729 1713 1384 1316 1281 1277 1246 1117 1753

15 145 182 305 451 563 570 635 781 827 983 1317 1311 1244 1204 1123 1348

11 157 164 292 301 360 636 859 871 895 1613 1454 1268 1206 1164 1138 1783

455 610 1123 1603

631 914 1424 1461

149 507 1275 1468

5 1078 1415 1735

169 772 775 1516

1683 1315 1207 1688

19 1053 1221 1260

933 1095 1597 1628

893 1360 1209 1740

1675 1486 1222 1737

897 1074 1651 1728

115 730 1363 1752

1734 1672 1552 1795

75 1087 1371 1712

123 438 839 1074

4 203 1407 1798

441 476 658 1400

380 1741 1341 1774

974 1664 1487 1756

7 273 834 1658

798 1653 1475 1686

12 1539 1237 1709

211 1618 1494 1624

367 1036 1390 1587

18 166 1645 1679

530 1092 1571 1707

588 1689 1593 1707

980 1522 1104 1701

1025 1552 1510 1683

270 340 1326 1770.

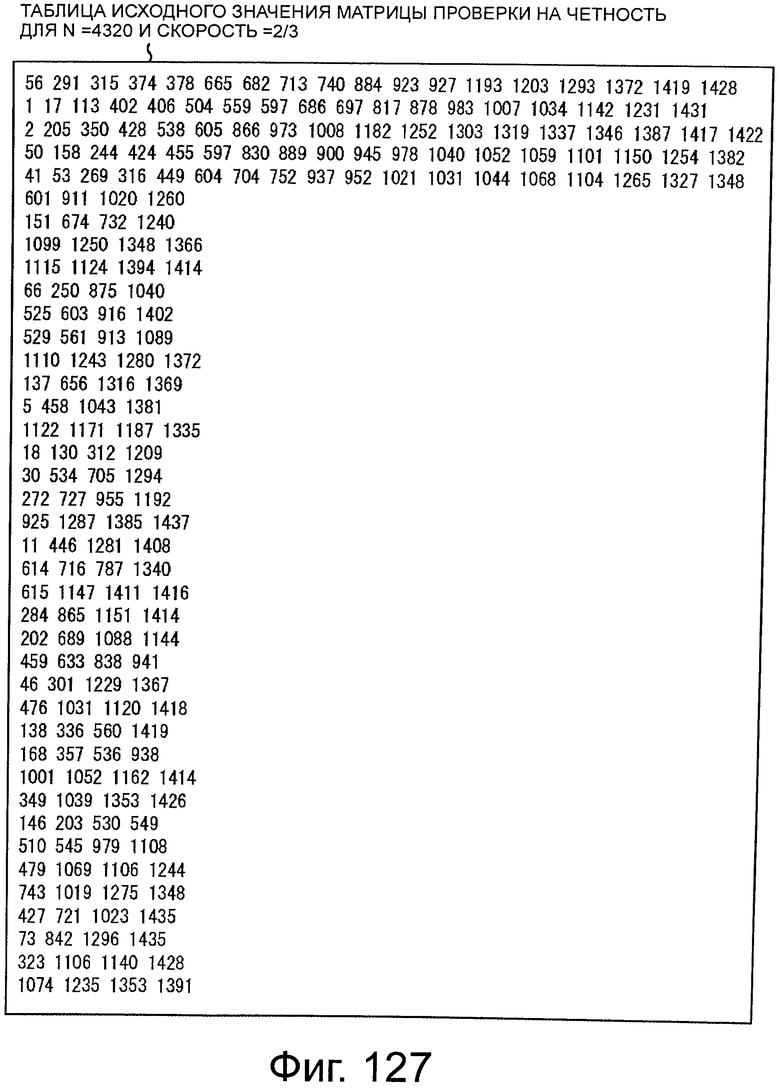

В соответствии с третьим аспектом настоящего изобретения предложено устройство или способ обработки данных, состоящий в обработке данных, включающее в себя средство кодирования, которое выполняет кодирование с использованием кода LDPC, имеющего длину кода 4320 битов и скорость кодирования 2/3, или выполняет кодирование с использованием кода LDPC, имеющего длину кода 4320 битов и скорость кодирования 2/3, при этом матрица проверки на четность кода LDPC выполнена путем размещения элементов 1 информационной матрицы, которые определяют на основе таблицы исходного значения матрицы проверки на четность для матрицы проверки на четность, представляющей положения элементов 1 информационной матрицы, соответствующей длине информации в соответствии с длиной кода и скоростью кодирования для каждых 72 столбцов, в направлении столбца, в период 72 столбца, и таблицу исходного значения матрицы проверки на четность формируют следующим образом:

56 291 315 374 378 665 682 713 740 884 923 927 1419 1372 1293 1203 1193 1428

1 17 113 402 406 504 559 597 686 697 817 878 983 1007 1034 1231 1142 1431

2 205 350 428 538 605 866 973 1008 1417 1387 1346 1337 1319 1303 1252 1182 1422

50 158 244 424 455 597 830 889 900 945 978 1040 1052 1059 1254 1150 1101 1382

41 53 269 316 449 604 704 752 937 952 1021 1031 1044 1068 1327 1265 1104 1348

601 911 1020 1260

151 674 732 1240

1099 1348 1250 1366

1394 1124 1115 1414

66 250 875 1040

525 603 916 1402

529 561 913 1089

1280 1243 1110 1372

137 656 1316 1369

5 458 1043 1381

1187 1171 1122 1335

18 130 312 1209

30 534 705 1294

272 727 955 1192

925 1385 1287 1437

11 446 1281 1408

614 716 787 1340

615 1411 1147 1416

284 865 1151 1414

202 689 1088 1144

459 633 838 941

46 301 1229 1367

476 1031 1120 1418

138 336 560 1419

168 357 536 938

1001 1052 1162 1414

349 1039 1353 1426

146 203 530 549

510 545 979 1108

479 1069 1106 1244

743 1019 1275 1348

427 721 1023 1435

73 842 1296 1435

323 1140 1106 1428

1074 1353 1235 1391.

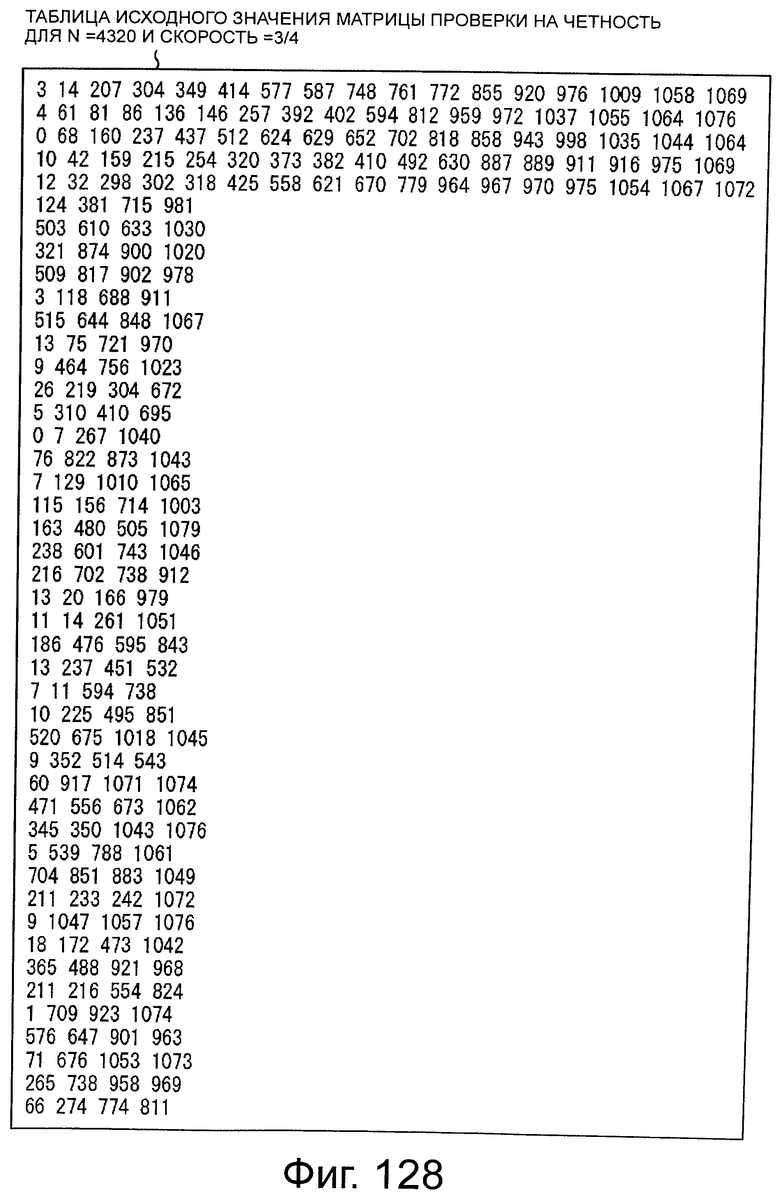

В соответствии с четвертым аспектом настоящего изобретения предложено устройство или способ обработки данных, состоящий в обработке данных, включающее в себя средство кодирования, которое выполняет кодирование с использованием кода LDPC, имеющего длину кода 4320 битов и скорость кодирования 3/4, или выполняет кодирование с использованием кода LDPC, имеющего длину кода 4320 битов и скорость кодирования 3/4, при этом матрица проверки на четность кода LDPC выполнена путем размещения элементов 1 информационной матрицы, которые определяют на основе таблицы исходного значения матрицы проверки на четность для матрицы проверки на четность, представляющей положения элементов 1 информационной матрицы, соответствующей длине информации в соответствии с длиной кода и скоростью кодирования для каждых 72 столбцов, в направлении столбца, в период 72 столбца, и таблицу исходного значения матрицы проверки на четность формируют следующим образом:

3 14 207 304 349 414 577 587 748 761 772 855 920 976 1009 1058 1069

4 61 81 86 136 146 257 392 402 594 812 959 972 1037 1055 1064 1076

0 68 160 237 437 512 624 629 652 702 818 858 943 998 1035 1044 1064

10 42 159 215 254 320 373 382 410 492 630 887 889 911 916 975 1069

12 32 298 302 318 425 558 621 670 779 964 967 970 975 1054 1067 1072

124 381 715 981

503 610 633 1030

321 874 900 1020

509 817 902 978

3 118 688 911

515 644 848 1067

13 75 721 970

9 464 756 1023

26 219 304 672

5 310 410 695

0 7 267 1040

76 822 873 1043

7 129 1010 1065

115 156 714 1003

163 480 505 1079

238 601 743 1046

216 702 738 912

13 20 166 979

11 14 261 1051

186 476 595 843

13 237 451 532

7 11 594 738

10 225 495 851

520 675 1018 1045

9 352 514 543

60 917 1071 1074

471 556 673 1062

345 350 1043 1076

5 539 788 1061

704 851 883 1049

211 233 242 1072

9 1047 1057 1076

18 172473 1042

365 488 921 968

211 216 554 824

1 709 923 1074

576 647 901 963

71 676 1053 1073

265 738 958 969

66 274 774 811.

В соответствии с пятым аспектом настоящего изобретения предложено устройство обработки данных, которое выполняет декодирование кода LDPC (проверка на четность низкой плотности), устройство обработки данных, включающее в себя средство декодирования, которое выполняет декодирование кода LDPC, имеющего длину кода 4320 битов и скорость кодирования 1/2, при этом матрица проверки на четность кода LDPC выполнена путем размещения элементов 1 информационной матрицы, которые определяют на основе таблицы исходного значения матрицы проверки на четность для матрицы проверки на четность, представляющей положения элементов 1 информационной матрицы, соответствующей длине информации в соответствии с длиной кода и скоростью кодирования для каждых 72 столбцов, в направлении столбца, в период 72 столбца, и в котором таблицу исходного значения матрицы проверки на четность формируют следующим образом:

142 150 213 247 507 538 578 828 969 1042 1781 1612 1584 1509 1315 1107 1934 2106 2117

3 17 20 31 97 466 571 580 842 983 1480 1465 1413 1392 1261 1226 1152 2047 2125

49 169 258 548 582 839 873 881 931 995 1906 1865 1826 1776 1654 1639 1209 1145 1956

148 393 396 486 568 806 909 965 1947 1844 1736 1664 1534 1402 1371 1306 1256 1203 2055

185 191 263 290 384 769 981 1071 1926 1910 1880 1842 1815 1769 1723 1554 1357 1202 1991

424 444 923 1679

91 436 535 978

362 677 821 1695

1454 1392 1117 2030

35 840 1477 2152

1061 1836 1202 1879

242 286 1140 1538

111 240 481 760

59 1268 1899 2144

737 1395 1299 2072

34 288 810 1903

232 1013 1365 1729

410 783 1066 1187

113 885 1423 1560

760 909 1475 2048

68 254 420 1867

283 325 334 970

168 321 479 554

378 836 1913 1928

101 238 964 1393

304 460 1497 1588

151 192 1075 1614

297 313 677 1303

329 447 1348 1832

582 831 984 1900.

В соответствии с шестым аспектом настоящего изобретения предложено устройство обработки данных, которое выполняет декодирование кода LDPC (проверка на четность низкой плотности), устройство обработки данных, включающее в себя средство декодирования, которое выполняет декодирование кода LDPC, имеющего длину кода 4320 битов и скорость кодирования 7/12, при этом матрица проверки на четность кода LDPC выполнена путем размещения элементов 1 информационной матрицы, которые определяют на основе таблицы исходного значения матрицы проверки на четность для матрицы проверки на четность, представляющей положения элементов 1 информационной матрицы, соответствующей длине информации в соответствии с длиной кода и скоростью кодирования для каждых 72 столбцов, в направлении столбца, в период 72 столбца, и в котором таблицу исходного значения матрицы проверки на четность формируют следующим образом:

96 246 326 621 668 748 874 965 1022 1627 1481 1469 1300 1142 1117 1108 1702

22 79 122 127 339 359 516 587 1025 1681 1651 1594 1484 1478 1294 1143 1794

80 426 429 506 599 810 892 1016 1729 1713 1384 1316 1281 1277 1246 1117 1753

15 145 182 305 451 563 570 635 781 827 983 1317 1311 1244 1204 1123 1348

11 157 164 292 301 360 636 859 871 895 1613 1454 1268 1206 1164 1138 1783

455 610 1123 1603

631 914 1424 1461

149 507 1275 1468

5 1078 1415 1735

169 772 775 1516

1683 1315 1207 1688

19 1053 1221 1260

933 1095 1597 1628

893 1360 1209 1740

1675 1486 1222 1737

897 1074 1651 1728

115 730 1363 1752

1734 1672 1552 1795

75 1087 1371 1712

123 438 839 1074

4203 1407 1798

441 476 658 1400

380 1741 1341 1774

974 1664 1487 1756

7 273 834 1658

798 1653 1475 1686

12 1539 1237 1709

211 1618 1494 1624

367 1036 1390 1587

18 166 1645 1679

530 1092 1571 1707

588 1689 1593 1707

980 1522 1104 1701

1025 1552 1510 1683

270 340 1326 1770.

В соответствии с седьмым аспектом настоящего изобретения, предложено устройство обработки данных, которое выполняет декодирование кода LDPC (проверка на четность низкой плотности), устройство обработки данных, включающее в себя средство декодирования, которое выполняет декодирование кода LDPC, имеющего длину кода 4320 битов и скорость кодирования 2/3, при этом матрица проверки на четность кода LDPC выполнена путем размещения элементов 1 информационной матрицы, которые определяют на основе таблицы исходного значения матрицы проверки на четность для матрицы проверки на четность, представляющей положения элементов 1 информационной матрицы, соответствующей длине информации в соответствии с длиной кода и скоростью кодирования для каждых 72 столбцов, в направлении столбца, в период 72 столбца, и в котором таблицу исходного значения матрицы проверки на четность формируют следующим образом:

56 291 315 374 378 665 682 713 740 884 923 927 1419 1372 1293 1203 1193 1428

1 17 113 402 406 504 559 597 686 697 817 878 983 1007 1034 1231 1142 1431

2 205 350 428 538 605 866 973 1008 1417 1387 1346 1337 1319 1303 1252 1182 1422

50 158 244 424 455 597 830 889 900 945 978 1040 1052 1059 1254 1150 1101 1382

41 53 269 316 449 604 704 752 937 952 1021 1031 1044 1068 1327 1265 1104 1348

601 911 1020 1260

151 674 732 1240

1099 1348 1250 1366

1394 1124 1115 1414

66 250 875 1040

525 603 916 1402

529 561 913 1089

1280 1243 1110 1372

137 656 1316 1369

5458 1043 1381

1187 1171 1122 1335

18 130 312 1209

30 534 705 1294

272 727 955 1192

925 1385 1287 1437

11 446 1281 1408

614 716 787 1340

615 1411 1147 1416

284 865 1151 1414

202 689 1088 1144

459 633 838 941

46 301 1229 1367

476 1031 1120 1418

138 336 560 1419

168 357 536 938

1001 1052 1162 1414

349 1039 1353 1426

146 203 530 549

510 545 979 1108

479 1069 1106 1244

743 1019 1275 1348

427 721 1023 1435

73 842 1296 1435

323 1140 1106 1428

1074 1353 1235 1391.

В соответствии с восьмым аспектом настоящего изобретения предложено устройство обработки данных, которое выполняет декодирование кода LDPC (проверка на четность низкой плотности), устройство обработки данных, включающее в себя средство декодирования, которое выполняет декодирование кода LDPC, имеющего длину кода 4320 битов и скорость кодирования 3/4, при этом матрица проверки на четность кода LDPC выполнена путем размещения элементов 1 информационной матрицы, которые определяют на основе таблицы исходного значения матрицы проверки на четность для матрицы проверки на четность, представляющей положения элементов 1 информационной матрицы, соответствующей длине информации в соответствии с длиной кода и скоростью кодирования для каждых 72 столбцов, в направлении столбца, в период 72 столбца, и в котором таблицу исходного значения матрицы проверки на четность формируют следующим образом:

3 14 207 304 349 414 577 587 748 761 772 855 920 976 1009 1058 1069

4 61 81 86 13 исходного значения 6 146 257 392 402 594 812 959 972 1037 1055 1064 1076

0 68 160 237 437 512 624 629 652 702 818 858 943 998 1035 1044 1064

10 42 159 215 254 320 373 382 410 492 630 887 889 911 916 975 1069

12 32 298 302 318 425 558 621 670 779 964 967 970 975 1054 1067 1072

124 381 715 981

503 610 633 1030

321 874 900 1020

509 817 902 978

3 118 688 911

515 644 848 1067

13 75 721 970

9 464 756 1023

26 219 304 672

5 310 410 695

0 7 267 1040

76 822 873 1043

7 129 1010 1065

115 156 714 1003

163 480 505 1079

238 601 743 1046

216 702 738 912

13 20 166 979

11 14 261 1051

186 476 595 843

13 237 451 532

7 11 594 738

10 225 495 851

520 675 1018 1045

9 352 514 543

60 917 1071 1074

471 556 673 1062

345 350 1043 1076

5 539 788 1061

704 851 883 1049

211 233 242 1072

9 1047 1057 1076

18 172 473 1042

365 488 921 968

211 216 554 824

1 709 923 1074

576 647 901 963

71 676 1053 1073

265 738 958 969

66 274 774 811.

В соответствии с первым - четвертым аспектами настоящего изобретения, кодирование выполняют, используя код LDPC, имеющий длину кода 4320 битов и скорость кодирования 1/2, 7/12, 2/3 или 3/4.

В соответствии с пятым - восьмым аспектами настоящего изобретения, выполняют декодирование кода LDPC, имеющего длину кода 4320 битов и скорость кодирования 1/2, 7/12, 2/3 или 3/4.

Матрицу проверки на четность кода LDPC выполняют путем размещения элементов 1 информационной матрицы, которые определены на основе таблицы исходного значения матрицы проверки на четность для матрицы проверки на четность, представляющей положения элементов 1 информационной матрицы, соответствующей длине информации, в соответствии с длиной кода и скоростью кодирования для каждых из 72 столбцов, в направлении столбцов за период 72 столбца, и таблицу исходного значения матрицы проверки на четность кода LDPC, имеющую скорость кодирования 1/2 формируют следующим образом:

142 150 213 247 507 538 578 828 969 1042 1781 1612 1584 1509 1315 1107 1934 2106 2117

3 17 20 31 97 466 571 580 842 983 1480 1465 1413 1392 1261 1226 1152 2047 2125

49 169 258 548 582 839 873 881 931 995 1906 1865 1826 1776 1654 1639 1209 1145 1956

148 393 396 486 568 806 909 965 1947 1844 1736 1664 1534 1402 1371 1306 1256 1203 2055

185 191 263 290 384 769 981 1071 1926 1910 1880 1842 1815 1769 1723 1554 1357 1202 1991

424 444 923 1679

91 436 535 978

362 677 821 1695

1454 1392 1117 2030

35 840 1477 2152

1061 1836 1202 1879

242 286 1140 1538

111 240 481 760

59 1268 1899 2144

737 1395 1299 2072

34 288 810 1903

232 1013 1365 1729

410 783 1066 1187

113 885 1423 1560

760 909 1475 2048

68 254 420 1867

283 325 334 970

168 321 479 554

378 836 1913 1928

101 238 964 1393

304 460 1497 1588

151 192 1075 1614

297 313 677 1303

329 447 1348 1832

582 831 984 1900.

Кроме того, таблицу исходного значения матрицы проверки на четность кода LDPC, имеющего скорость кодирования 7/12, формируют следующим образом:

96 246 326 621 668 748 874 965 1022 1627 1481 1469 1300 1142 1117 1108 1702

22 79 122 127 339 359 516 587 1025 1681 1651 1594 1484 1478 1294 1143 1794

80 426 429 506 599 810 892 1016 1729 1713 1384 1316 1281 1277 1246 1117 1753

15 145 182 305 451 563 570 635 781 827 983 1317 1311 1244 1204 1123 1348

11 157 164 292 301 360 636 859 871 895 1613 1454 1268 1206 1164 1138 1783

455 610 1123 1603

631 914 1424 1461

149 507 1275 1468

5 1078 1415 1735

169 772 775 1516

1683 1315 1207 1688

19 1053 1221 1260

933 1095 1597 1628

893 1360 1209 1740

1675 1486 1222 1737

897 1074 1651 1728

115 730 1363 1752

1734 1672 1552 1795

75 1087 1371 1712

123 438 839 1074

4 203 1407 1798

441 476 658 1400

380 1741 1341 1774

974 1664 1487 1756

7 273 834 1658

798 1653 1475 1686

12 1539 1237 1709

211 1618 1494 1624

367 1036 1390 1587

18 166 1645 1679

530 1092 1571 1707

588 1689 1593 1707

980 1522 1104 1701

1025 1552 1510 1683

270 340 1326 1770.

Также, таблицу исходного значения матрицы проверки на четность кода LDPC, имеющего скорость кодирования 2/3, формируют следующим образом:

56 291 315 374 378 665 682 713 740 884 923 927 1419 1372 1293 1203 1193 1428

1 17 113 402 406 504 559 597 686 697 817 878 983 1007 1034 1231 1142 1431

2 205 350 428 538 605 866 973 1008 1417 1387 1346 1337 1319 1303 1252 1182 1422

50 158 244 424 455 597 830 889 900 945 978 1040 1052 1059 1254 1150 1101 1382

41 53 269 316 449 604 704 752 937 952 1021 1031 1044 1068 1327 1265 1104 1348

601 911 1020 1260

151 674 732 1240

1099 1348 1250 1366

1394 1124 1115 1414

66 250 875 1040

525 603 916 1402

529 561 913 1089

1280 1243 1110 1372

137 656 1316 1369

5458 1043 1381

1187 1171 1122 1335

18 130 312 1209

30 534 705 1294

272 727 955 1192

925 1385 1287 1437

11 446 1281 1408

614 716 787 1340

615 1411 1147 1416

284 865 1151 1414

202 689 1088 1144

459 633 838 941

46 301 1229 1367

476 1031 1120 1418

138 336 560 1419

168 357 536 938

1001 1052 1162 1414

349 1039 1353 1426

146 203 530 549

510 545 979 1108

479 1069 1106 1244

743 1019 1275 1348

427 721 1023 1435

73 842 1296 1435

323 1140 1106 1428

107 41353 1235 1391.

Кроме того, таблицу исходного значения матрицы проверки на четность кода LDPC, имеющего скорость кодирования 3/4, формируют следующим образом:

3 14 207 304 349 414 577 587 748 761 772 855 920 976 1009 1058 1069

4 61 81 86 136 146 257 392 402 594 812 959 972 1037 1055 1064 1076

0 68 160 237 437 512 624 629 652 702 818 858 943 998 1035 1044 1064

10 42 159 215 254 320 373 382 410 492 630 887 889 911 916 975 1069

12 32 298 302 318 425 558 621 670 779 964 967 970 975 1054 1067 1072

124 381 715 981

503 610 633 1030

321 874 900 1020

509 817 902 978

3 118 688 911

515 644 848 1067

13 75 721 970

9 464 756 1023

26 219 304 672

5 310 410 695

0 7 267 1040

76 822 873 1043

7 129 1010 1065

115 156 714 1003

163 480 505 1079

238 601 743 1046

216 702 738 912

13 20 166 979

11 14 261 1051

186 476 595 843

13 237 451 532

7 11 594 738

10 225 495 851

520 675 1018 1045

9 352 514 543

60 917 1071 1074

471 556 673 1062

345 350 1043 1076

5 539 788 1061

704 851 883 1049

211 233 242 1072

9 1047 1057 1076

18 172 473 1042

365 488 921 968

211 216 554 824

1 709 923 1074

576 647 901 963

71 676 1053 1073

265 738 958 969

66 274 774 811.

Здесь устройство обработки данных может представлять собой независимое устройство или внутренний блок, составляющий устройство.

Эффекты изобретения

В соответствии с первым - восьмым аспектами может быть повышена устойчивость к ошибкам.

Краткое описание чертежей

На фиг.1 показана схема, которая иллюстрирует матрицу Н проверки на четность кода LDPC.

На фиг.2 показана блок-схема последовательности операций, представляющая последовательность декодирования кода LDPC.

На фиг.3 показана схема, которая иллюстрирует пример матрицы проверки на четность кода LDPC.

На фиг.4 показана схема, которая иллюстрирует граф Таннера матрицы проверки на четность.

На фиг.5 показана схема, иллюстрирующая узел колебаний.

На фиг.6 показана схема, иллюстрирующая проверочный узел.

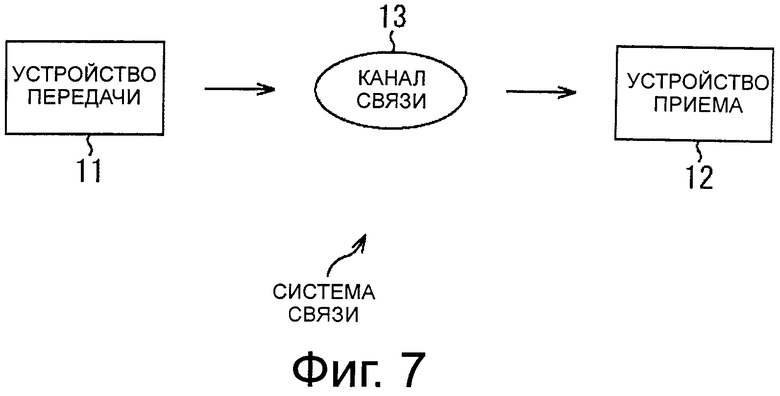

На фиг.7 показана схема, которая иллюстрирует пример конфигурации системы передачи в соответствии с вариантом осуществления настоящего изобретения.

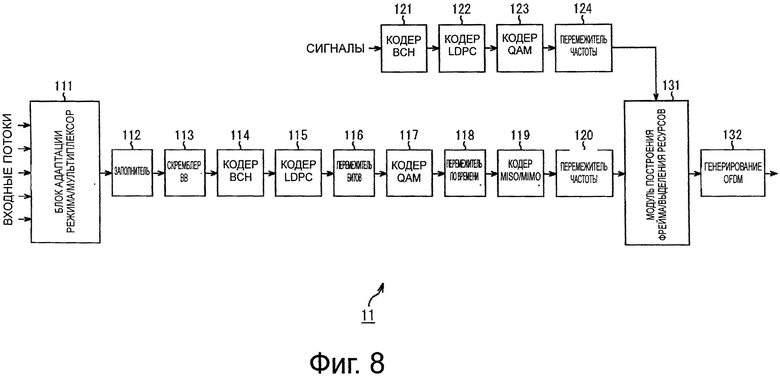

На фиг.8 показана блок-схема, представляющая пример конфигурации устройства передачи 11.

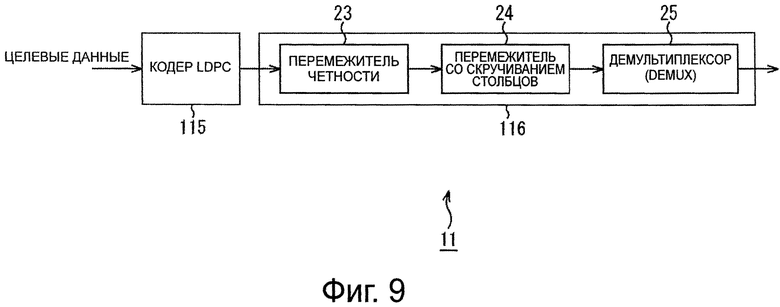

На фиг.9 показана блок-схема, представляющая пример конфигурации перемежителя битов 116.

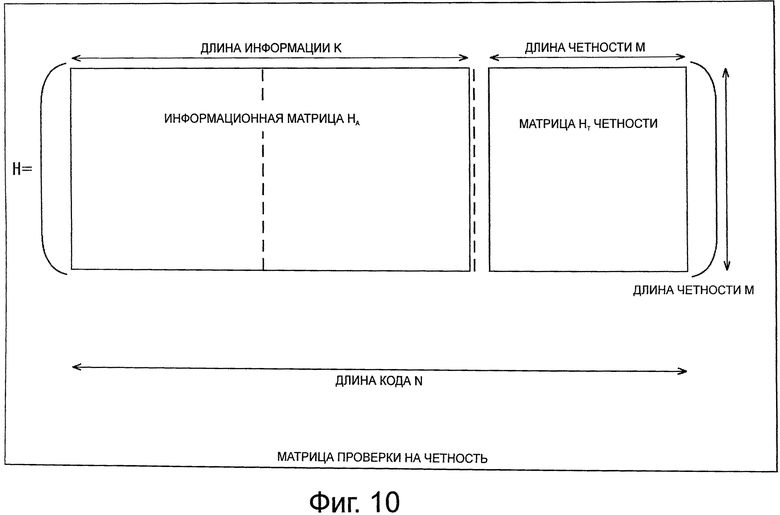

На фиг.10 показана схема, которая иллюстрирует матрицу проверки на четность.

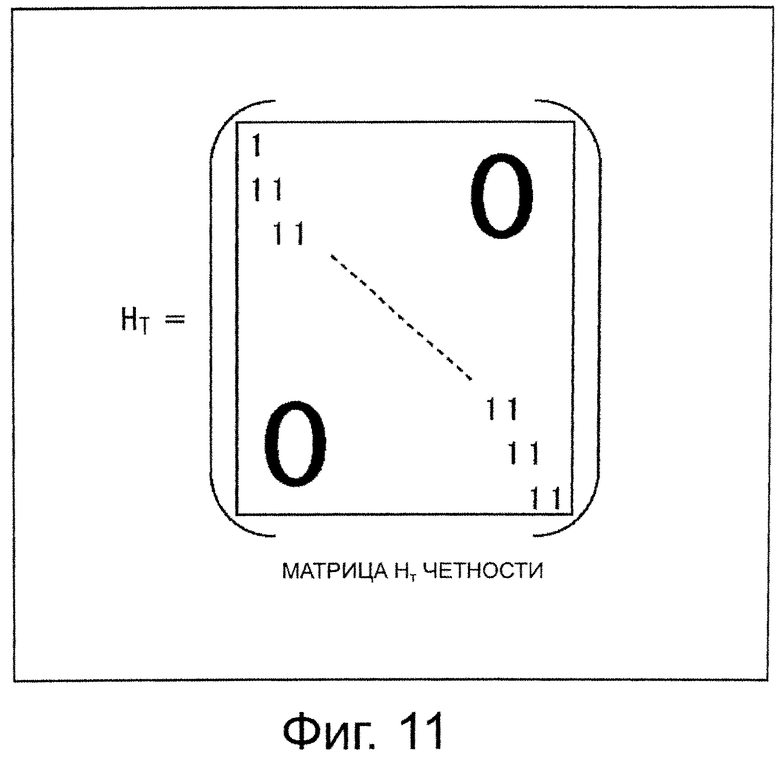

На фиг.11 показана схема, иллюстрирующая матрицу четности.

На фиг.12 показана схема, которая иллюстрирует матрицу проверки на четность кода LDPC, который определен в стандарте DVB-S.2.

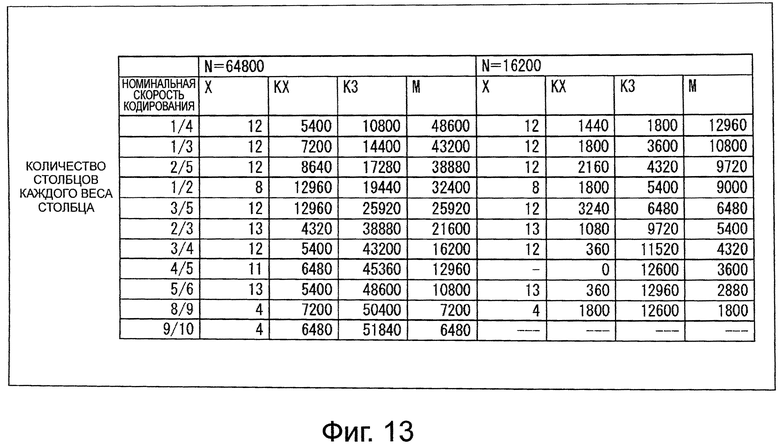

На фиг.13 показана схема, которая иллюстрирует матрицу проверки на четность кода LDPC, который определен в стандарте DVB-S.2.

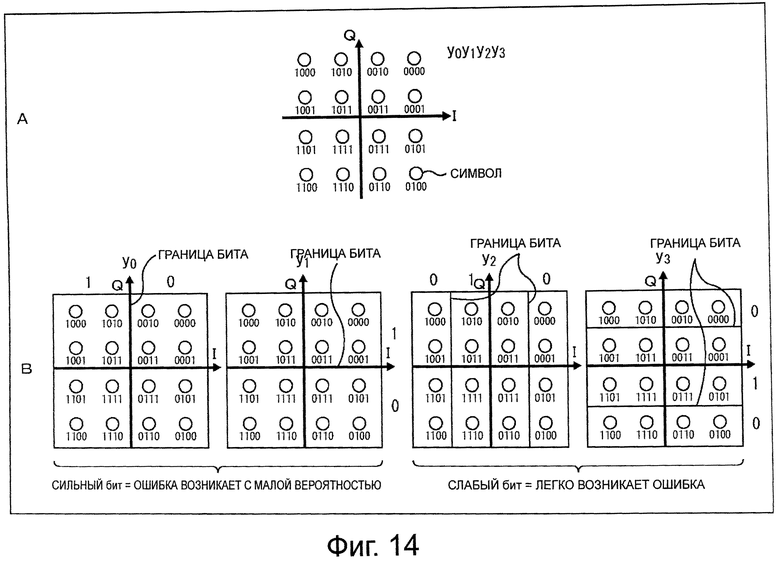

На фиг.14 показана схема, которая иллюстрирует компоновку точек сигнала 16 QAM.

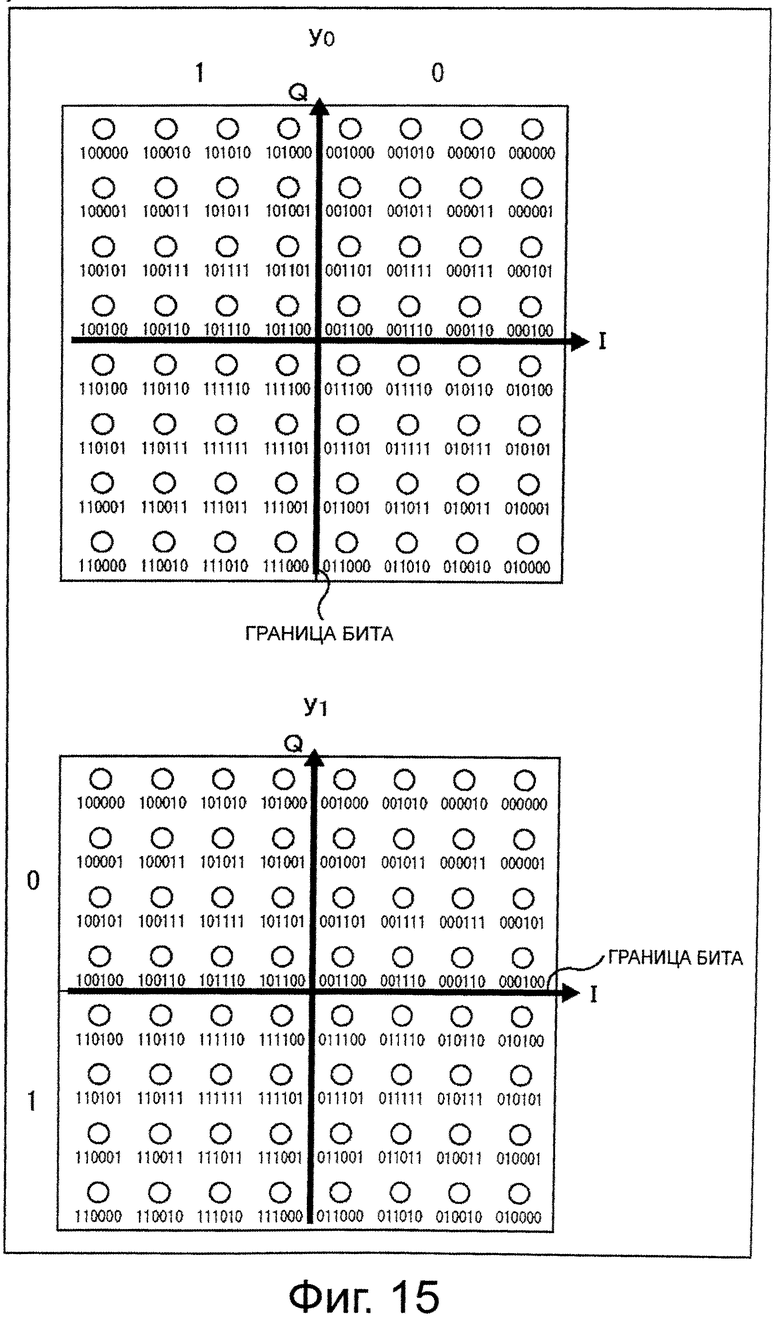

На фиг.15 показана схема, которая иллюстрирует компоновку точек сигнала 64 QAM.

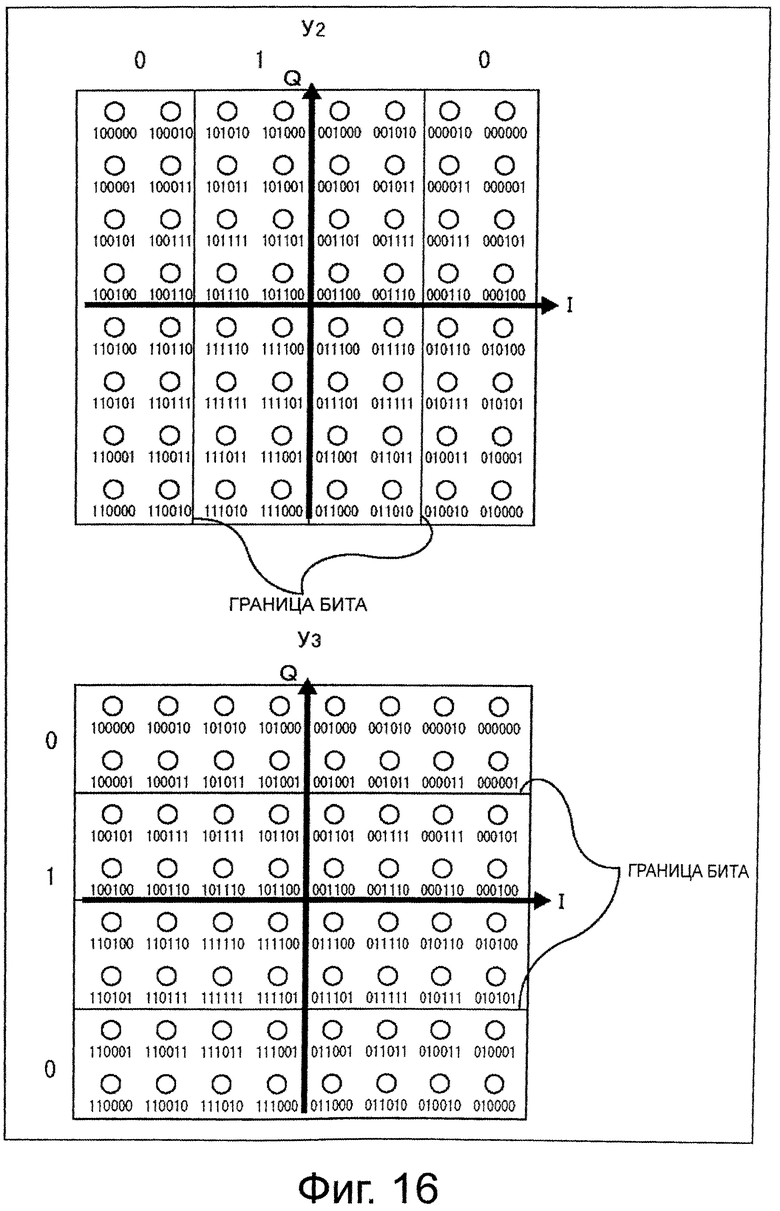

На фиг.16 показана схема, которая иллюстрирует компоновку точек сигнала 64 QAM.

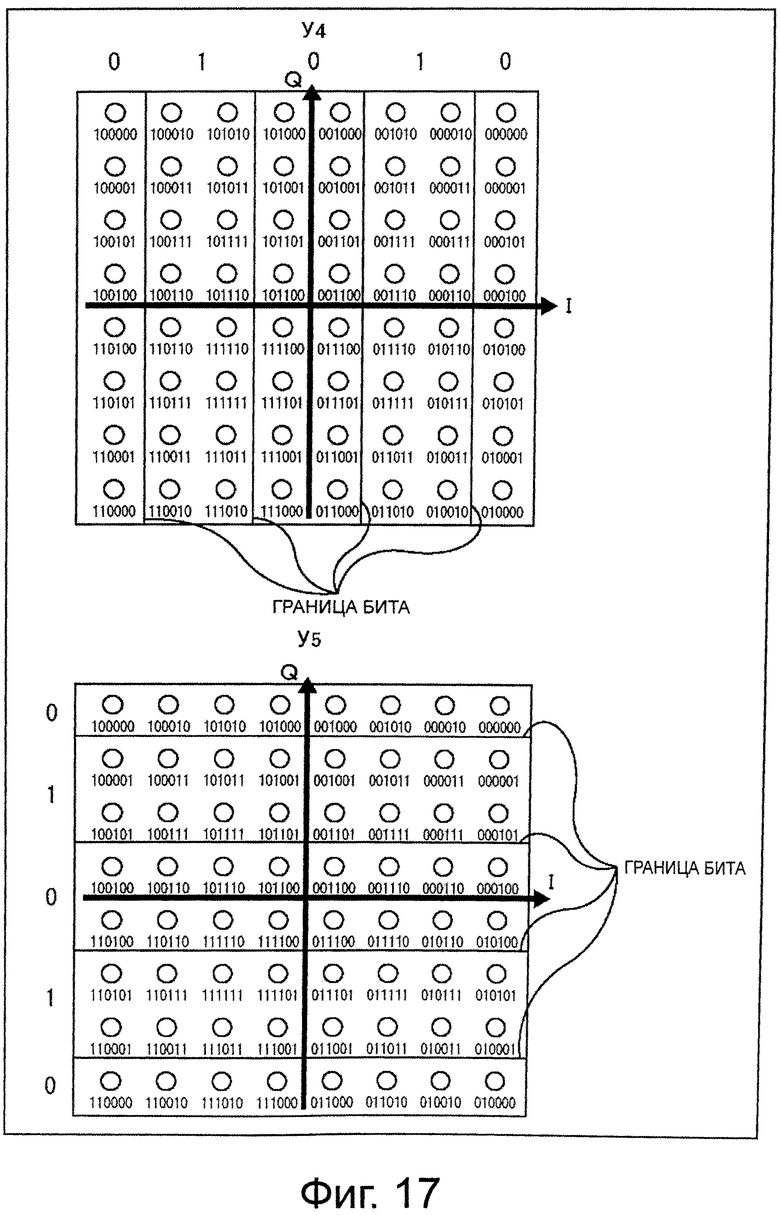

На фиг.17 показана схема, которая иллюстрирует компоновку точек сигнала 64 QAM.

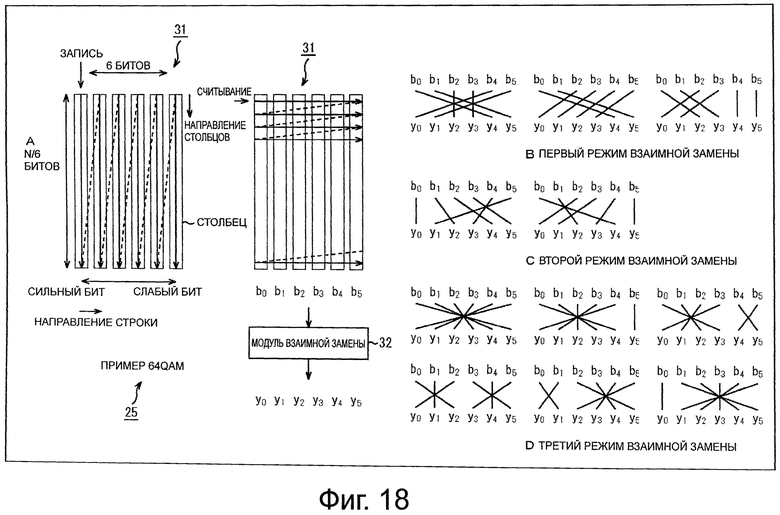

На фиг.18 показана схема, которая иллюстрирует обработку демультиплексора 25.

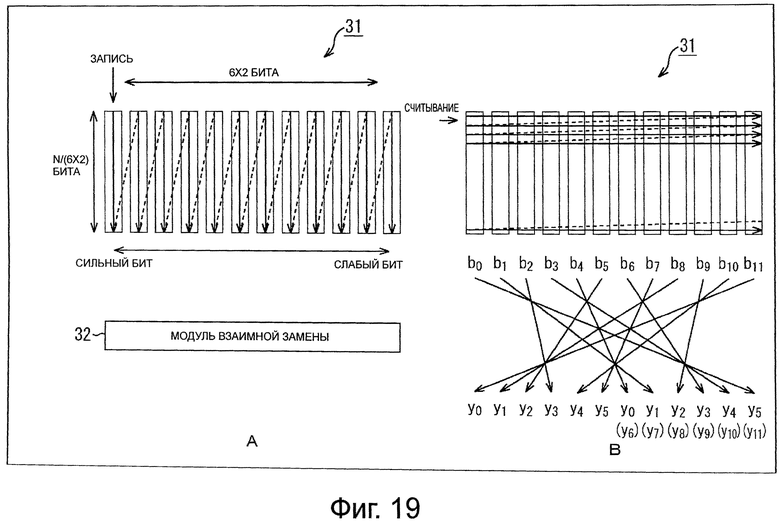

На фиг.19 показана схема, которая иллюстрирует обработку демультиплексора 25.

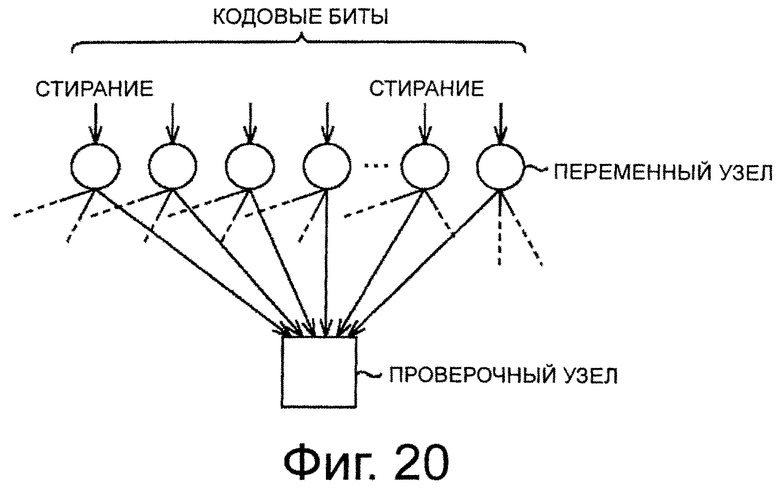

На фиг.20 показана схема, которая иллюстрирует граф Таннера для декодирования кода LDPC.

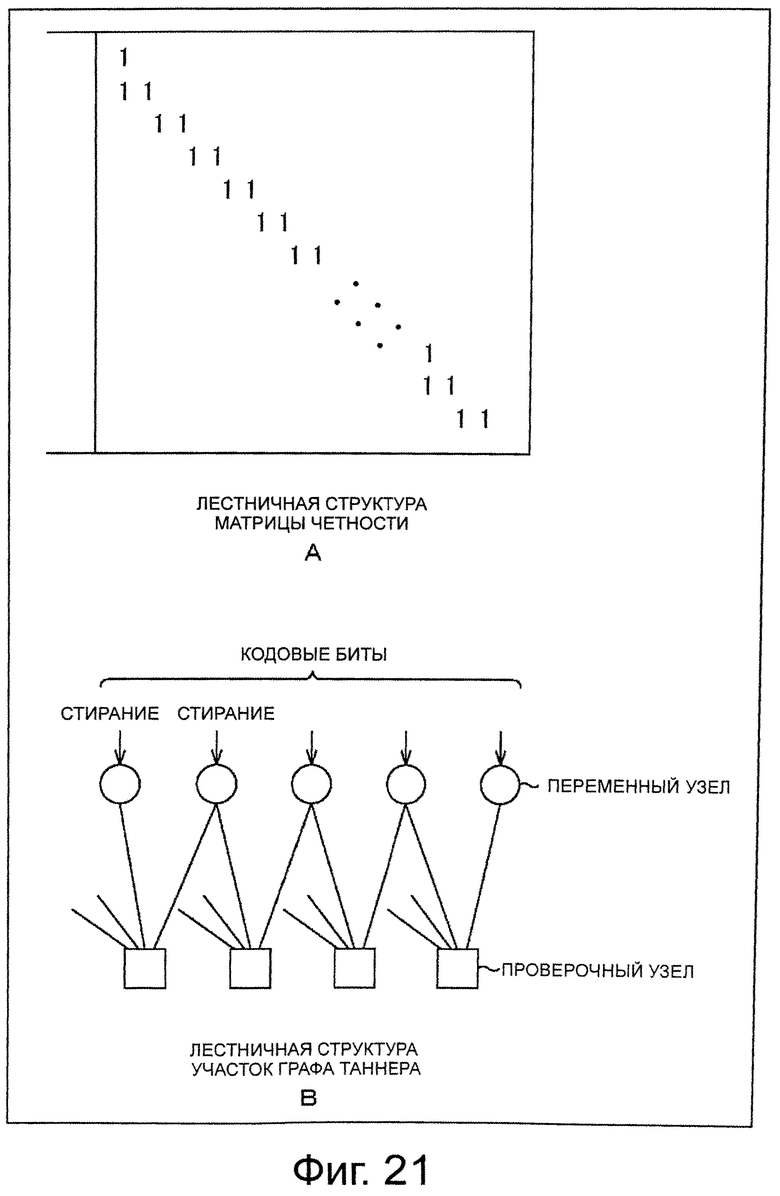

На фиг.21 представлены схемы, которые поясняют матрицу HT четности, имеющую ступенчатую структуру, и граф Таннера, соответствующий матрице HT четности.

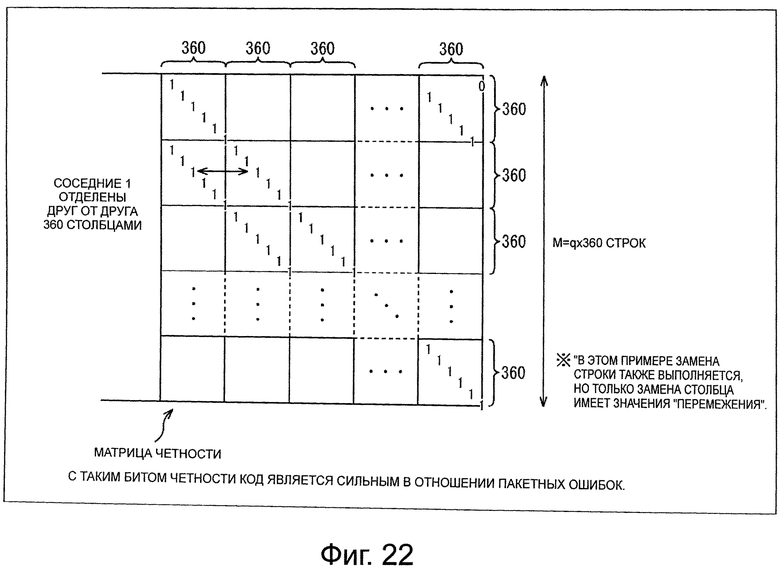

На фиг.22 показана схема, которая иллюстрирует матрицу HT четности матрицы Н проверки на четность, которая соответствует коду LDPC, после перемежения четности.

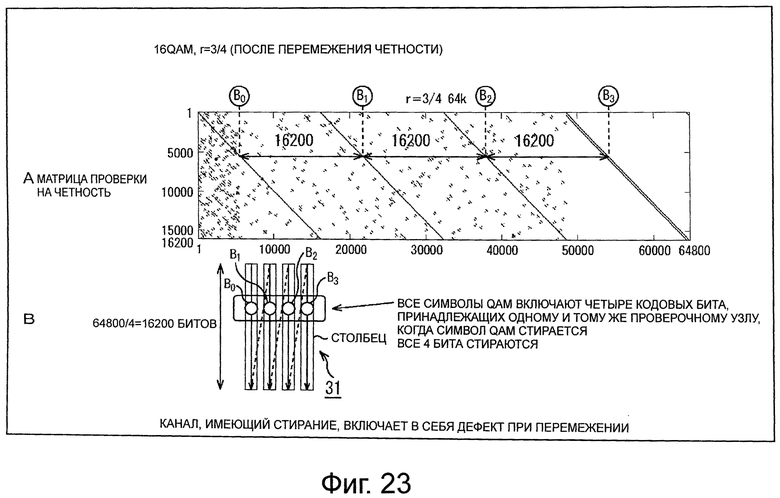

На фиг.23 показана схема, которая иллюстрирует преобразованную матрицу проверки на четность.

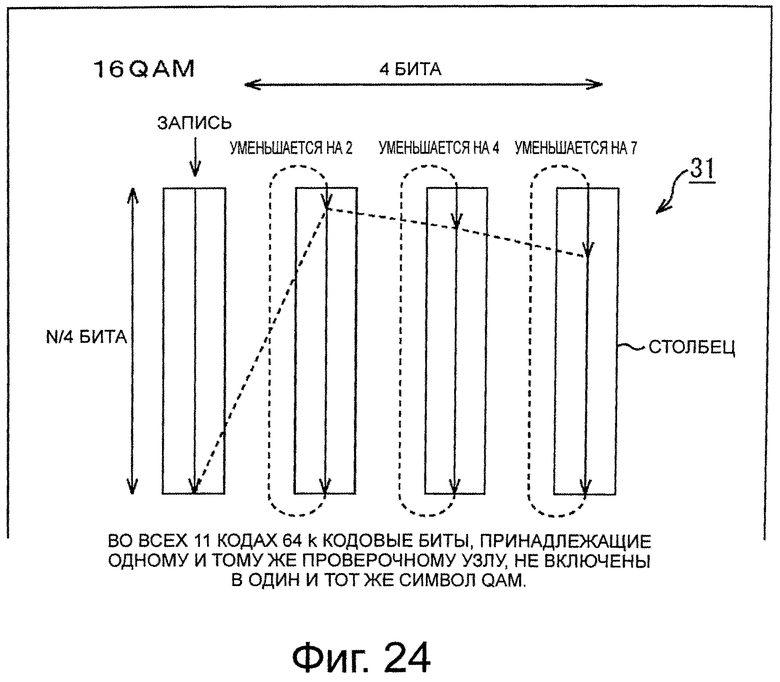

На фиг.24 показана схема, которая иллюстрирует процесс перемежителя 24 со скручиванием столбцов.

На фиг.25 показана схема, которая иллюстрирует запоминающее устройство 31 количества столбцов, которое требуется для перемежения со скручиванием столбцов, и адресов его начальных положений записи.

На фиг.26 показана схема, которая иллюстрирует запоминающее устройство 31 количества столбцов, которое требуется для перемежения со скручиванием столбцов, и адресов его начальных положений записи.

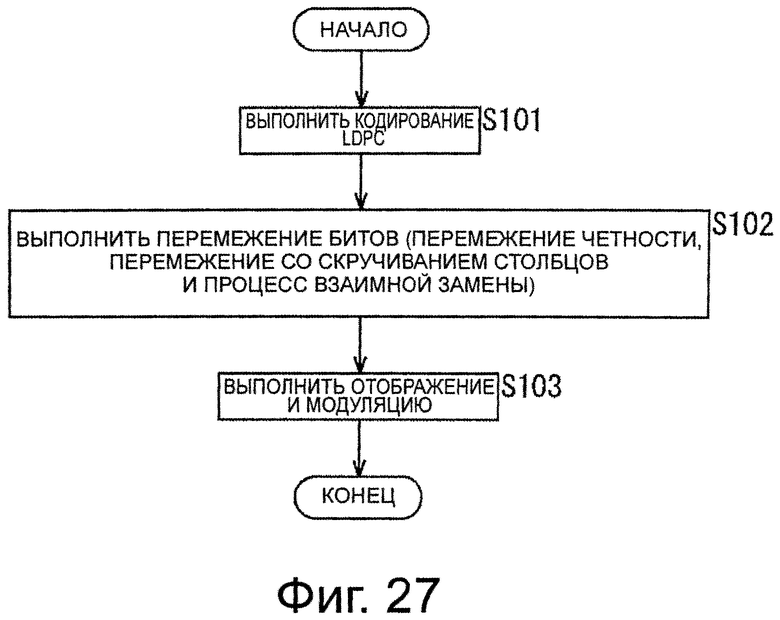

На фиг.27 показана блок-схема последовательности операций, представляющая обработку, выполняемую перемежителем 116 битов и кодером QAM 117.

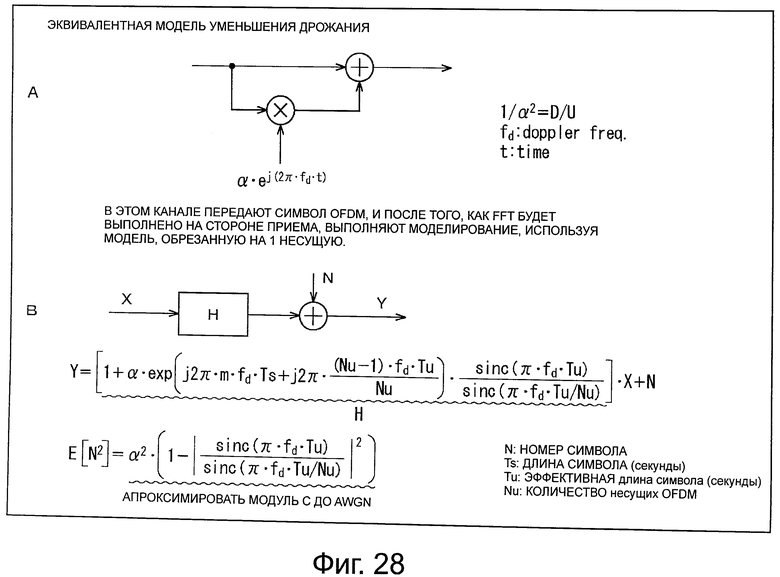

На фиг.28 показана схема, которая иллюстрирует модель канала связи, используемую при моделировании.

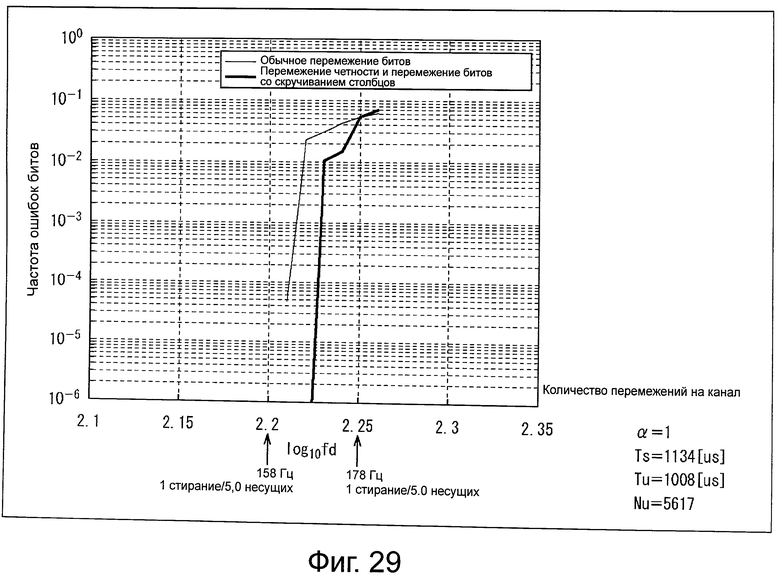

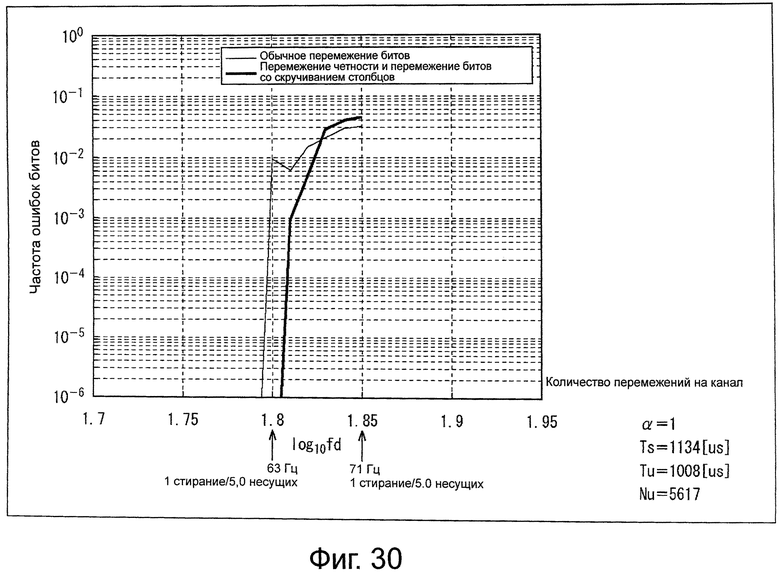

На фиг.29 показана схема, которая иллюстрирует соотношение между коэффициентом ошибок и частотой fd Допплера дрожаний, полученное путем моделирования.

На фиг.30 показана схема, которая иллюстрирует соотношение между коэффициентом ошибок и частотой fd Допплера дрожаний, полученное путем моделирования.

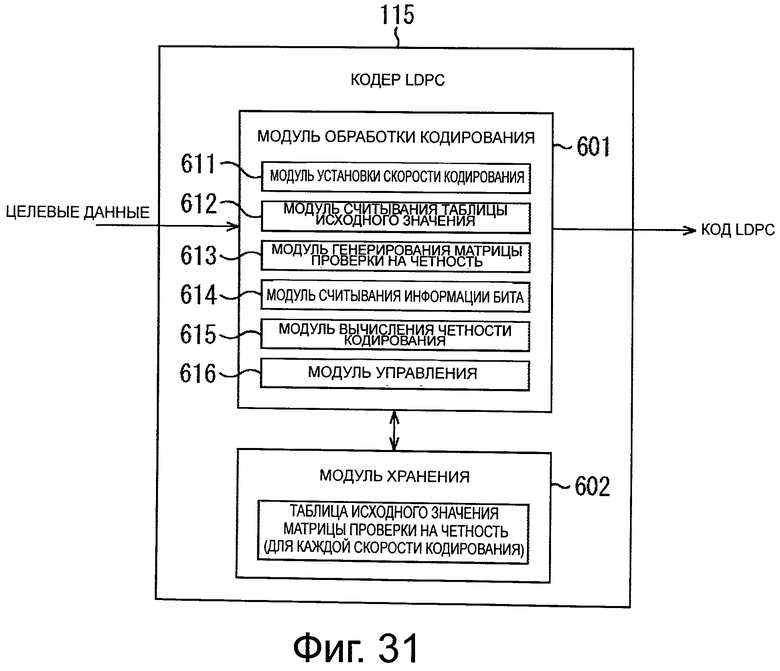

На фиг.31 показана блок-схема, представляющая пример конфигурации кодера LDPC115.

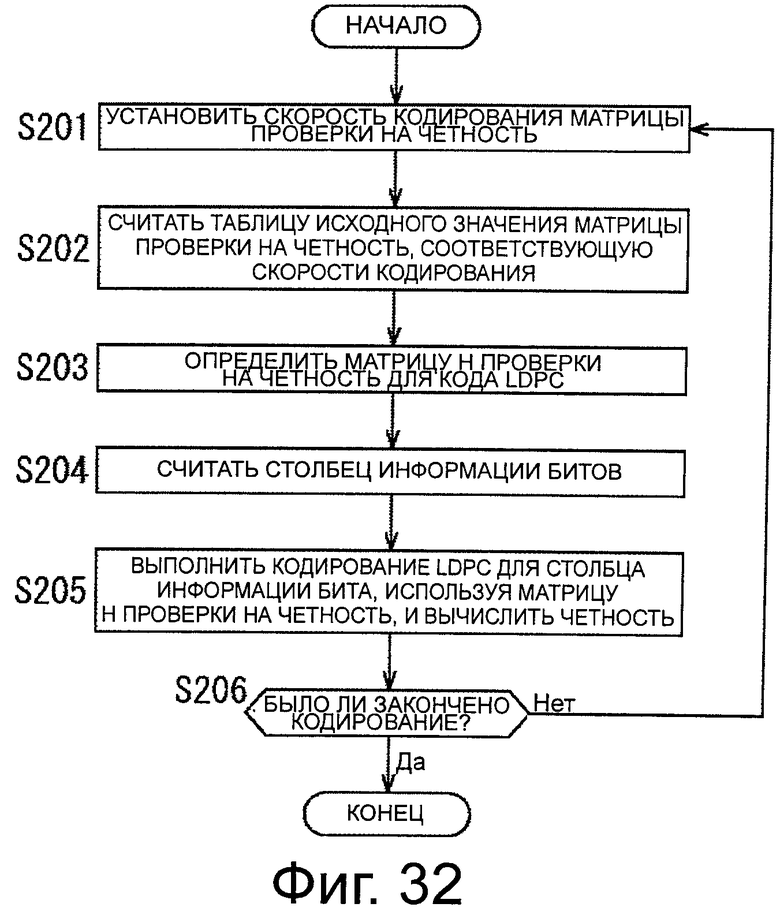

На фиг.32 показана блок-схема последовательности операций, представляющая обработку кодера LDPC 115.

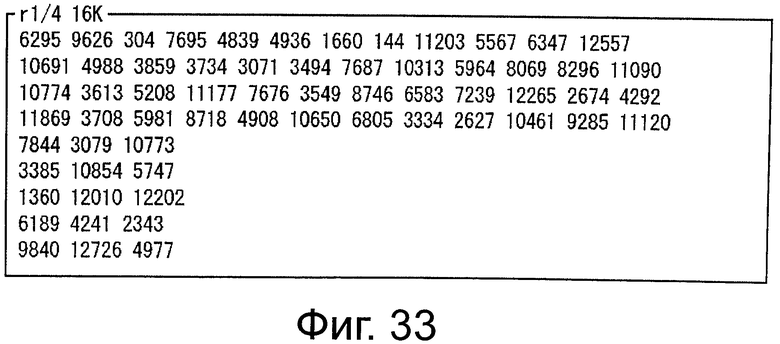

На фиг.33 показана схема, которая иллюстрирует пример таблицы исходного значения матрицы проверки на четность, имеющей скорость кодирования 1/4 и длину кода 16200.

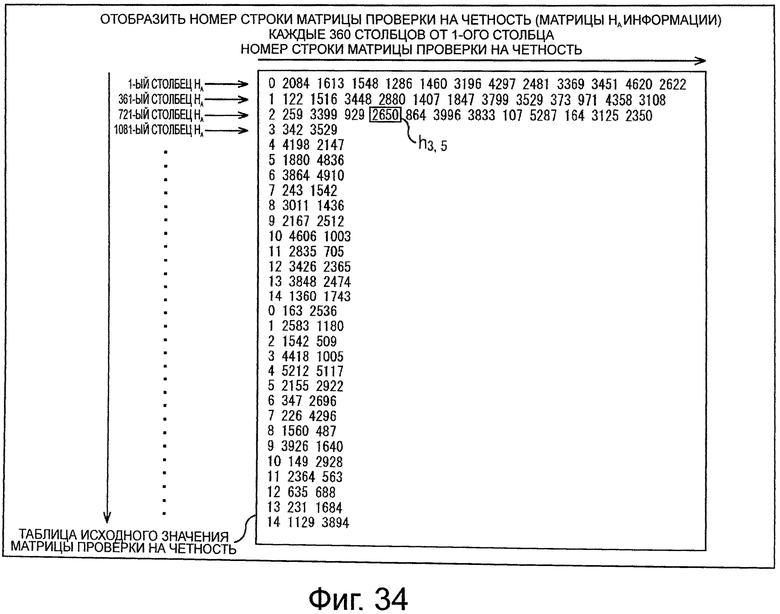

На фиг.34 показана схема, которая иллюстрирует способ получения матрицы Н проверки на четность из таблицы исходного значения матрицы проверки на четность.

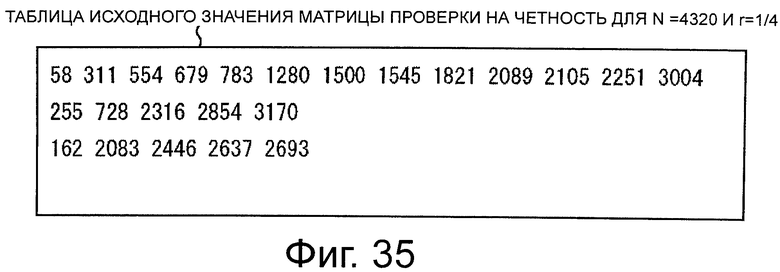

На фиг.35 показана схема, которая иллюстрирует пример таблицы исходного значения матрицы проверки на четность, имеющей скорость кодирования 1/4 и длину кода 4320.

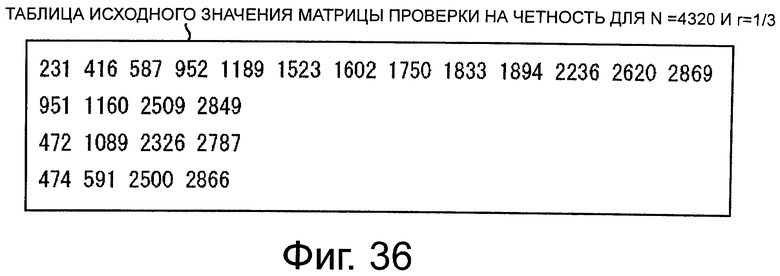

На фиг.36 показана схема, которая иллюстрирует пример таблицы исходного значения матрицы проверки на четность, имеющей скорость кодирования 1/3 и длину кода 4320.

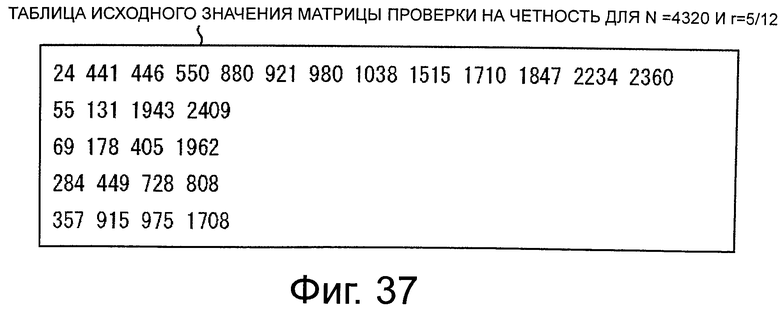

На фиг.37 показана схема, которая иллюстрирует пример таблицы исходного значения матрицы проверки на четность, имеющей скорость кодирования 5/12 и длину кода 4320.

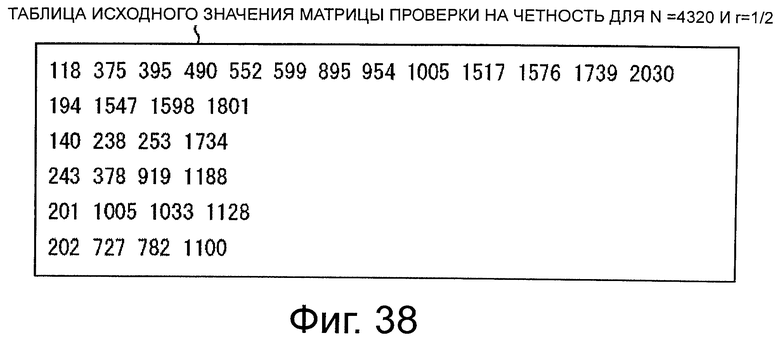

На фиг.38 показана схема, которая иллюстрирует пример таблицы исходного значения матрицы проверки на четность, имеющей скорость кодирования 1/2 и длину кода 4320.

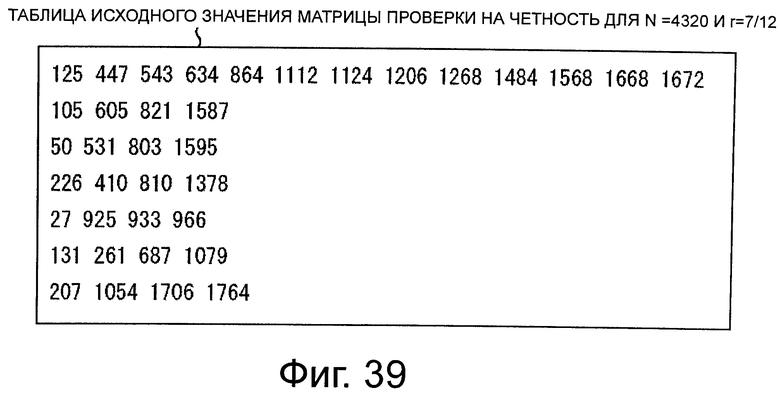

На фиг.39 показана схема, которая иллюстрирует пример таблицы исходного значения матрицы проверки на четность, имеющей скорость кодирования 7/12 и длину кода 4320.

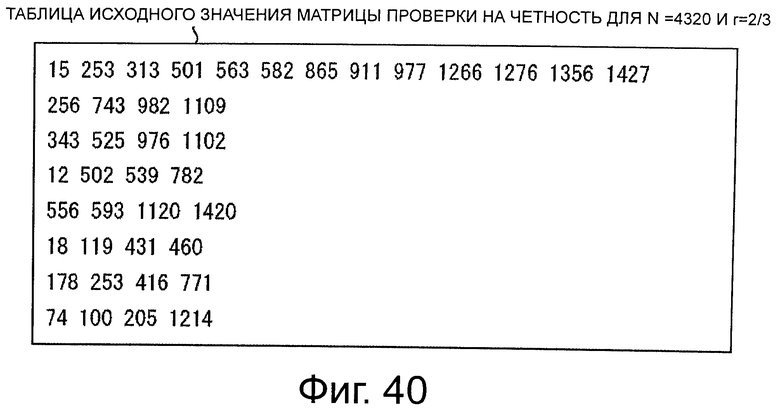

На фиг.40 показана схема, которая иллюстрирует пример таблицы исходного значения матрицы проверки на четность, имеющей скорость кодирования 2/3 и длину кода 4320.

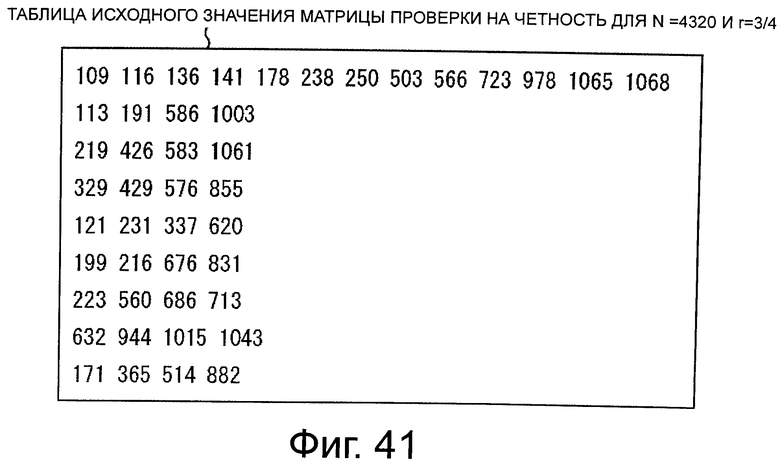

На фиг.41 показана схема, которая иллюстрирует пример таблицы исходного значения матрицы проверки на четность, имеющей скорость кодирования 3/4 и длину кода 4320.

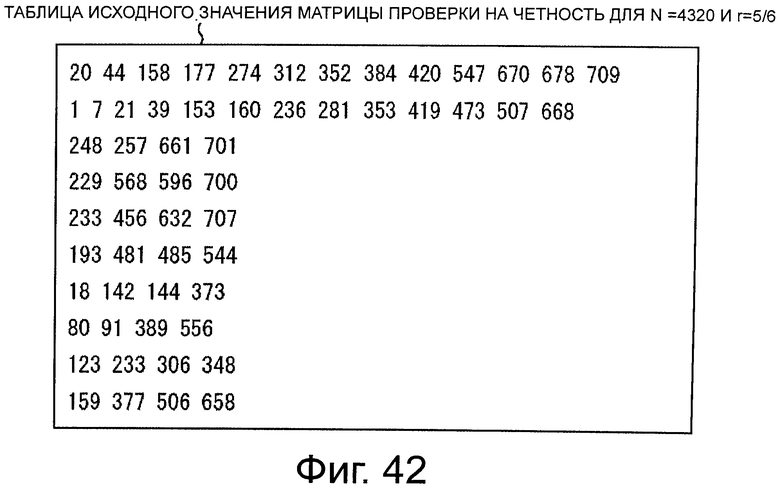

На фиг.42 показана схема, которая иллюстрирует пример таблицы исходного значения матрицы проверки на четность, имеющей скорость кодирования 5/6 и длину кода 4320.

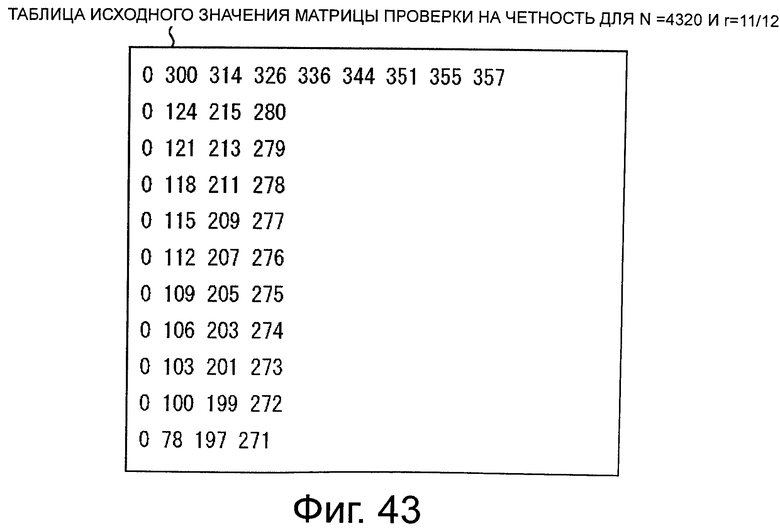

На фиг.43 показана схема, которая иллюстрирует пример таблицы исходного значения матрицы проверки на четность, имеющей скорость кодирования 11/12 и длину кода 4320.

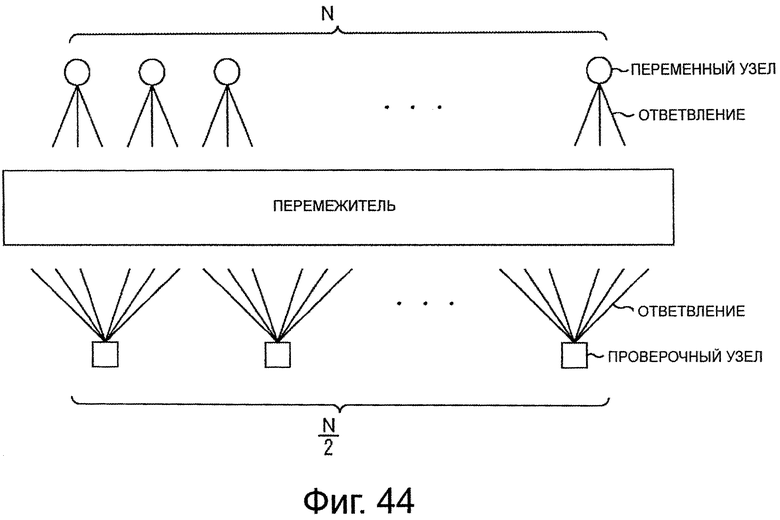

На фиг.44 показана схема, которая иллюстрирует пример графа Таннера совокупности последовательности степени, имеющей вес столбца 3 и вес строки 6.

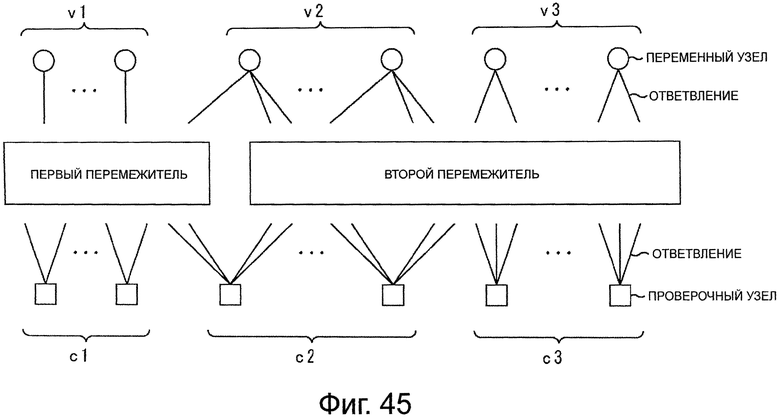

На фиг.45 показана схема, которая иллюстрирует пример графа Таннера совокупности с множеством ребер.

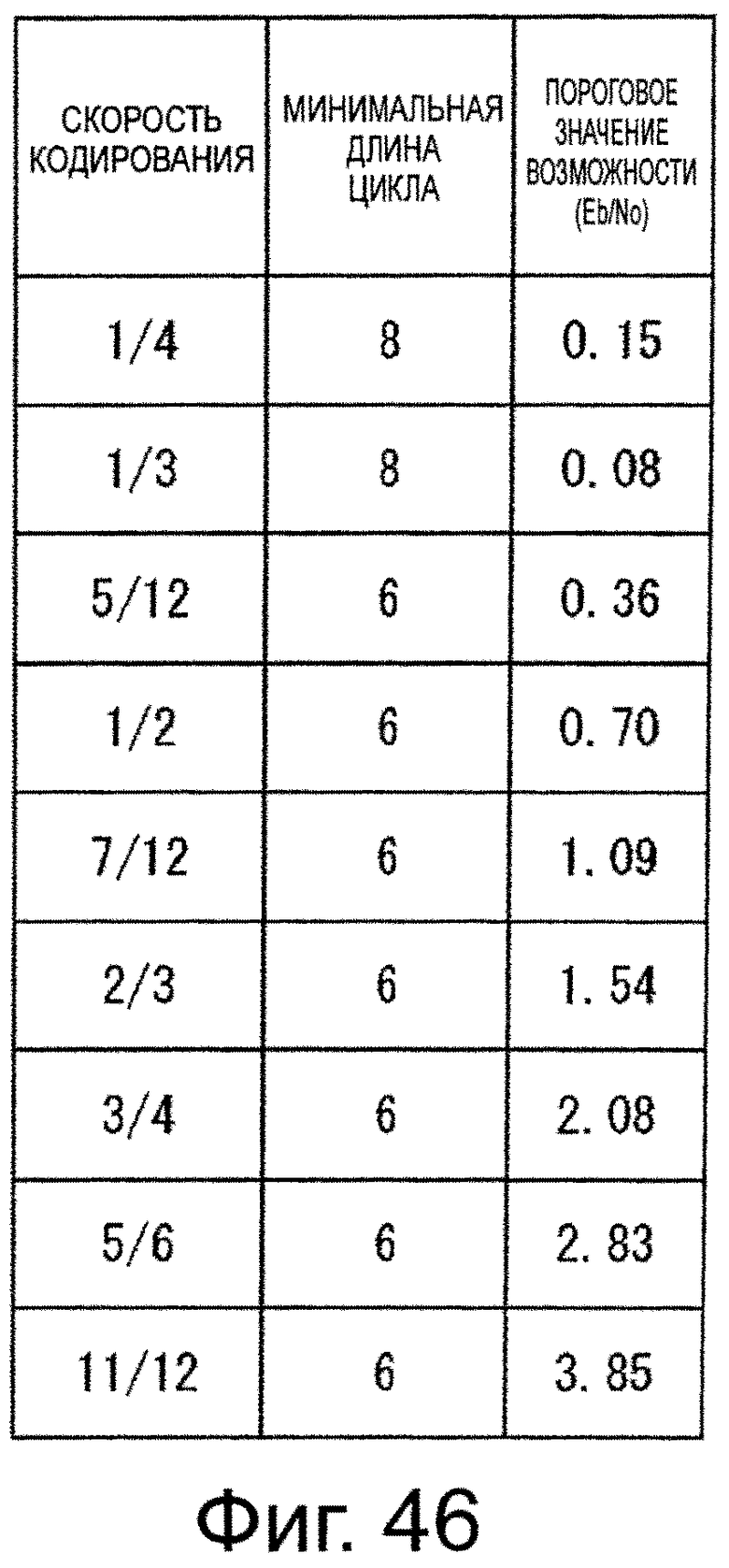

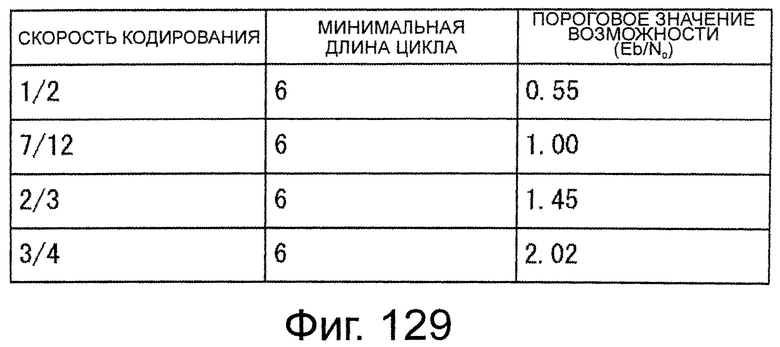

На фиг.46 показана схема, которая иллюстрирует минимальную длину цикла и порог возможностей матрицы проверки на четность кода LDPC, имеющего длину кода 4320.

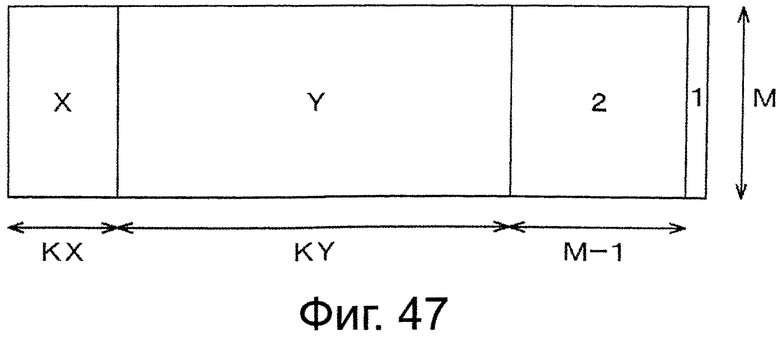

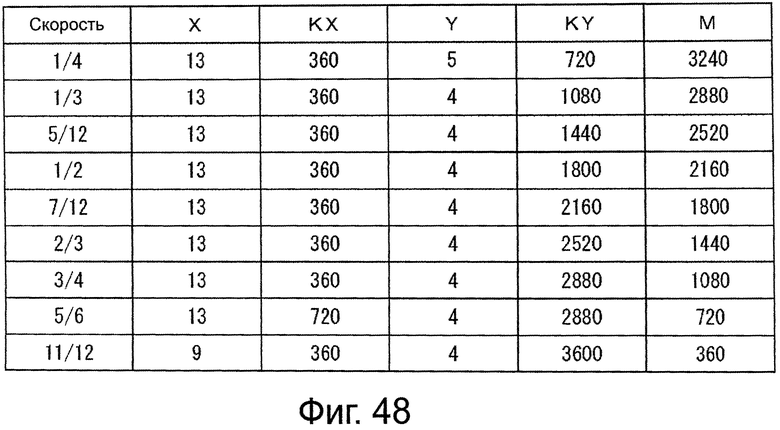

На фиг.47 показана схема, которая иллюстрирует матрицу проверки на четность кода LDPC, имеющего длину кода 4320.

На фиг.48 показана схема, которая иллюстрирует матрицу проверки на четность кода LDPC, имеющего длину кода 4320.

На фиг.49 показана схема, которая иллюстрирует запоминающее устройства 31 количества столбцов, которое требуется для перемежения со скручиванием столбцов, и адресов его начальных положений записи.

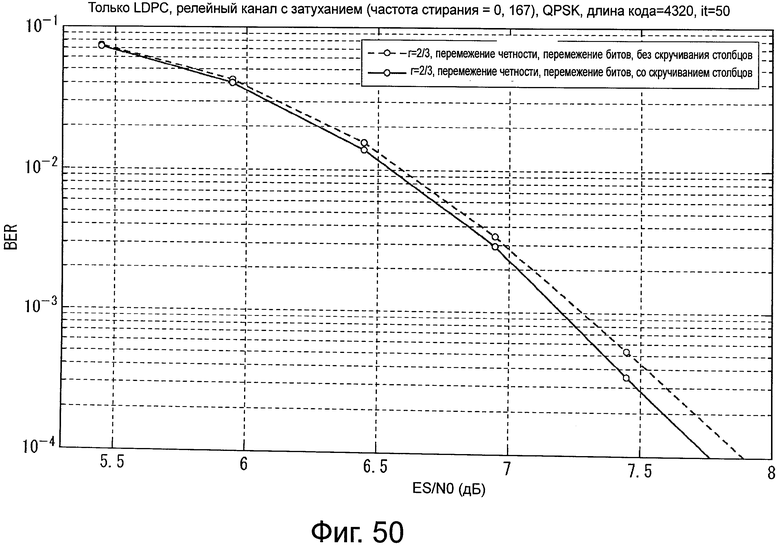

На фиг.50 показана схема, которая иллюстрирует результат моделирования BER в случае, когда выполнено перемежение со скручиванием столбцов.

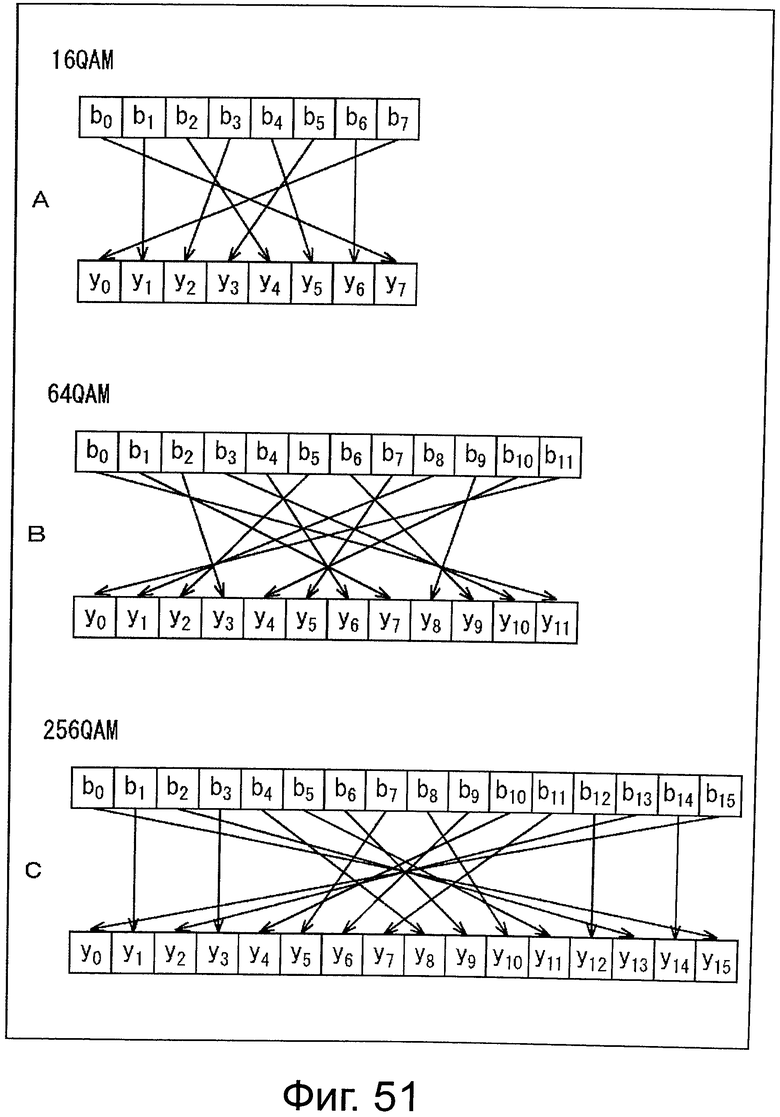

На фиг.51 показана схема, которая иллюстрирует процесс взаимной замены в соответствии с текущим режимом.

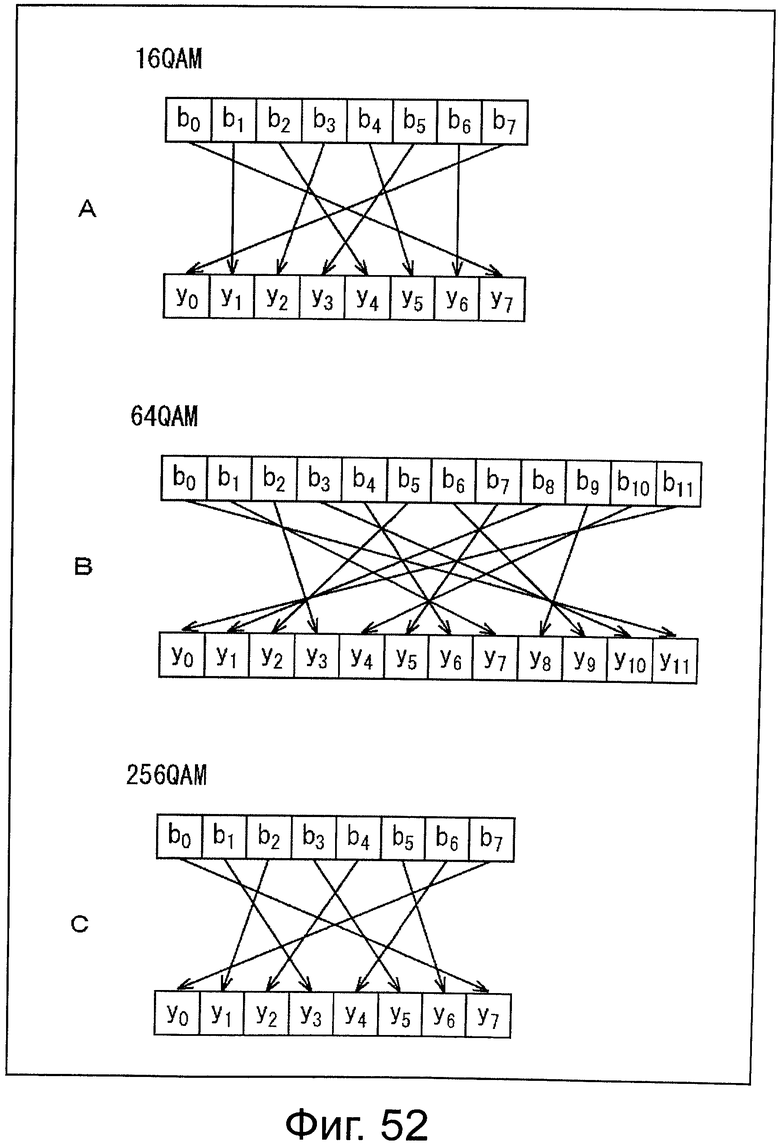

На фиг.52 показана схема, которая иллюстрирует процесс взаимной замены в соответствии с текущим режимом.

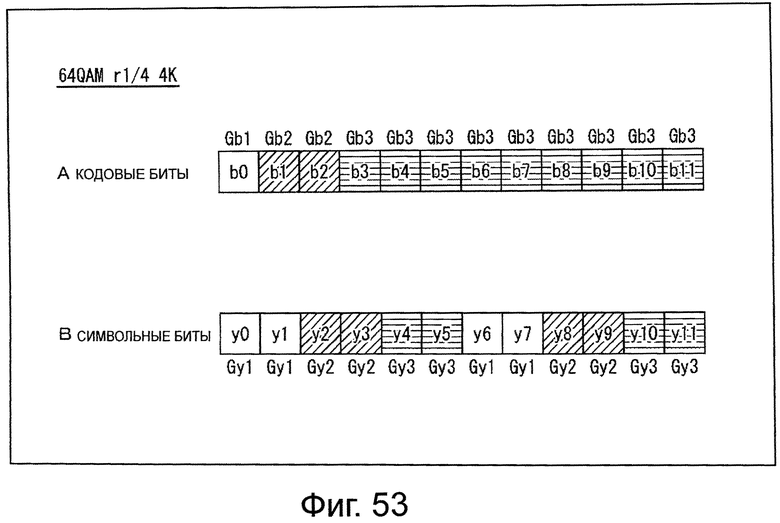

На фиг.53 показана схема, которая иллюстрирует группы кодовых битов и группы символьных битов в случае, когда код LDPC, имеющий длину кода 4 k и скорость кодирования 1/4 модулированы в соответствии с 64 QAM, и множитель b равен двум.

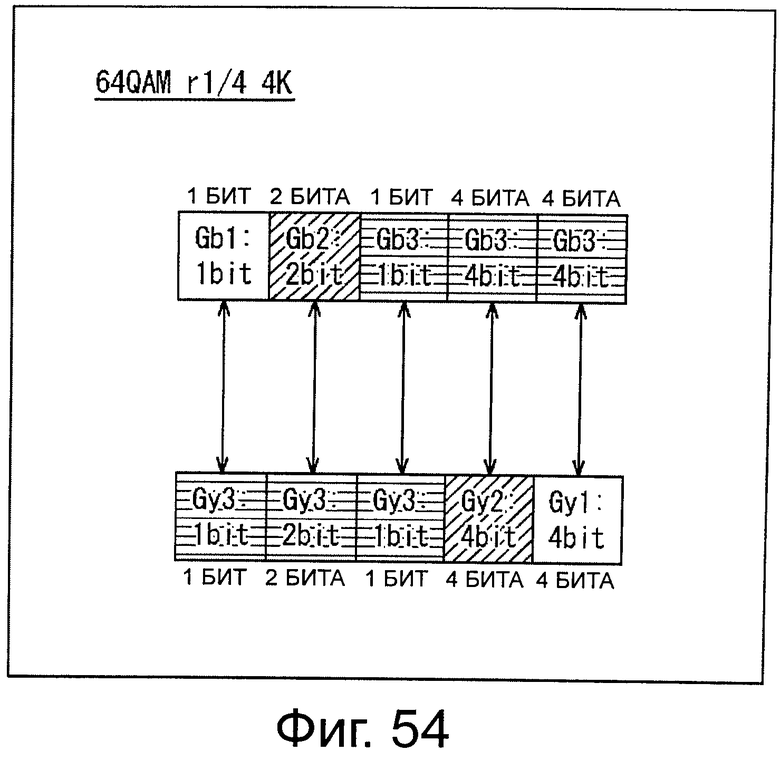

На фиг.54 показана схема, которая иллюстрирует правило выделения в случае, когда код LDPC, имеющий длину кода 4 k и скорость кодирования 1/4, модулирован в соответствии с 64 QAM, и множитель b равен двум.

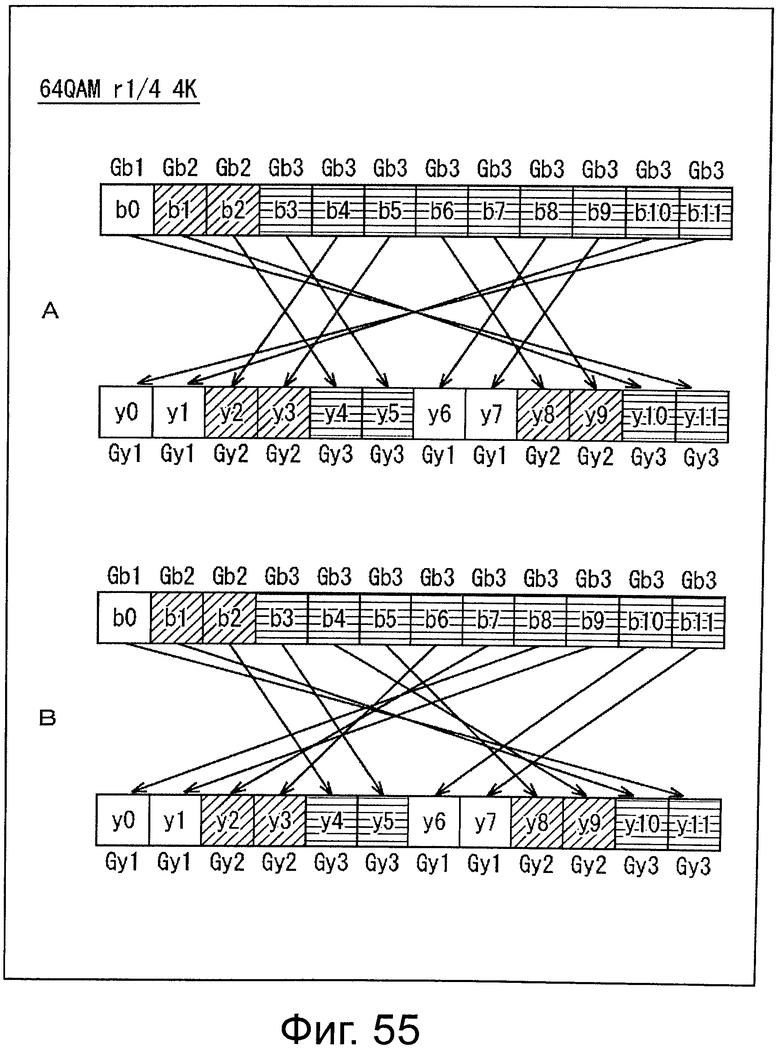

На фиг.55 показана схема, которая иллюстрирует взаимную замену кодовых битов в соответствии с правилом выделения в случае, когда код LDPC, имеющий длину кода 4 k и скорость кодирования 1/4, модулирован в соответствии с 64 QAM, и множитель b равен двум.

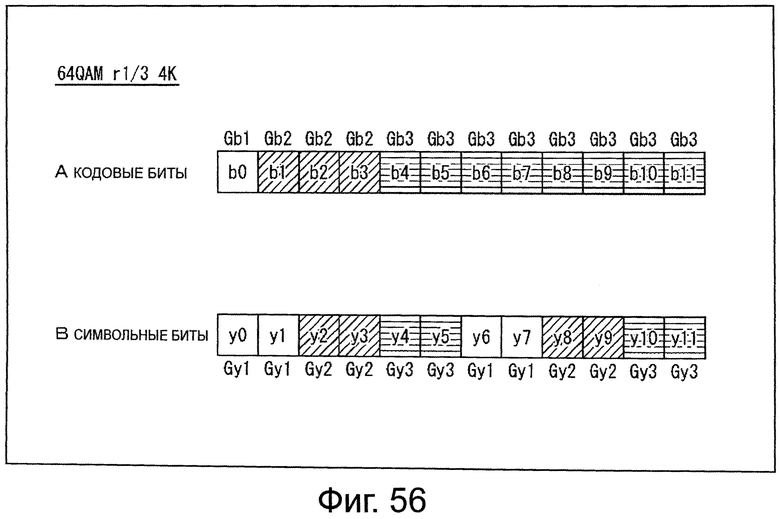

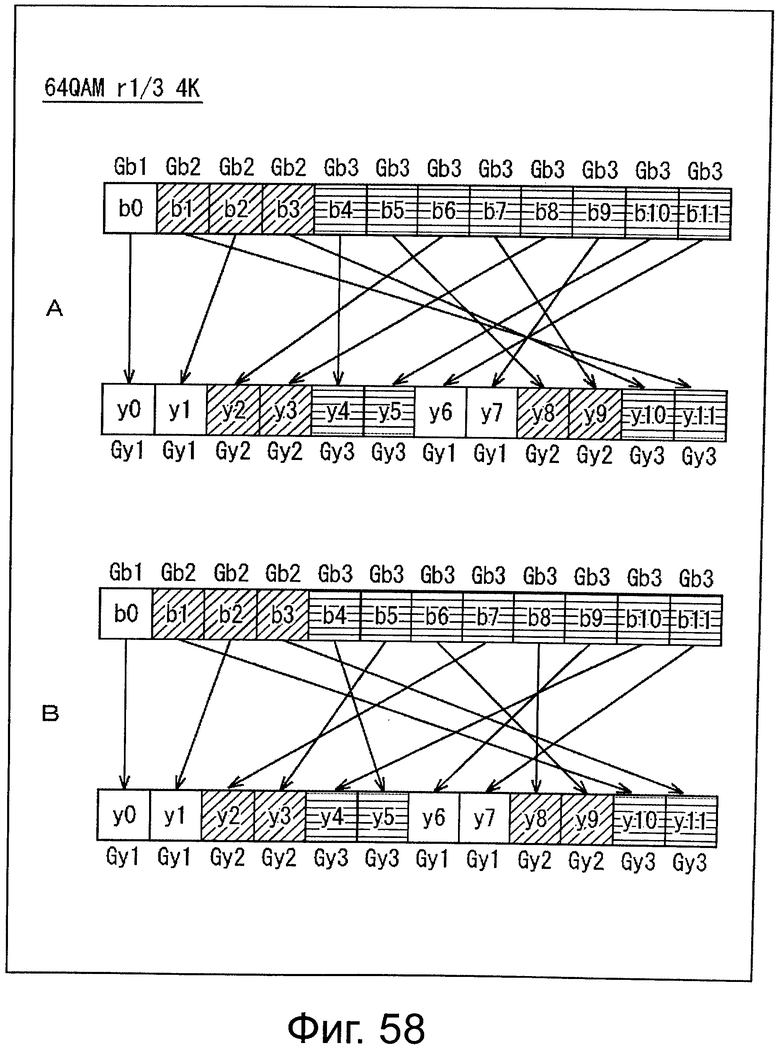

На фиг.56 показана схема, которая иллюстрирует группу кодовых битов и группу символьных битов в случае, когда код LDPC, имеющий длину кода 4 k и скорость кодирования 1/3, модулирован в соответствии с 64 QAM, и множитель b равен двум.

На фиг.57 показана схема, которая иллюстрирует правило выделения в случае, когда код LDPC, имеющий длину кода 4 k и скорость кодирования 1/3, модулирован в соответствии с 64 QAM, и множитель b равен двум.

На фиг.58 показана схема, которая иллюстрирует взаимную замену кодовых битов в соответствии с правилом выделения в случае, когда код LDPC, имеющий длину кода 4 k и скорость кодирования 1/3, модулирован в соответствии с 64 QAM, и множитель b равен двум.

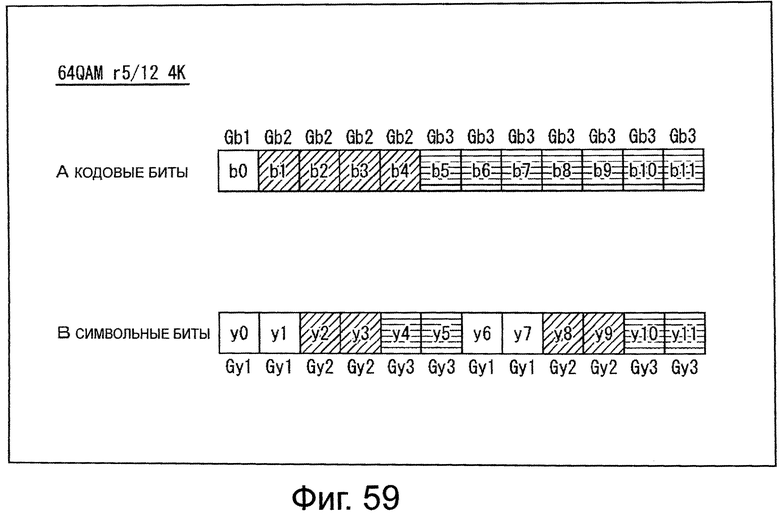

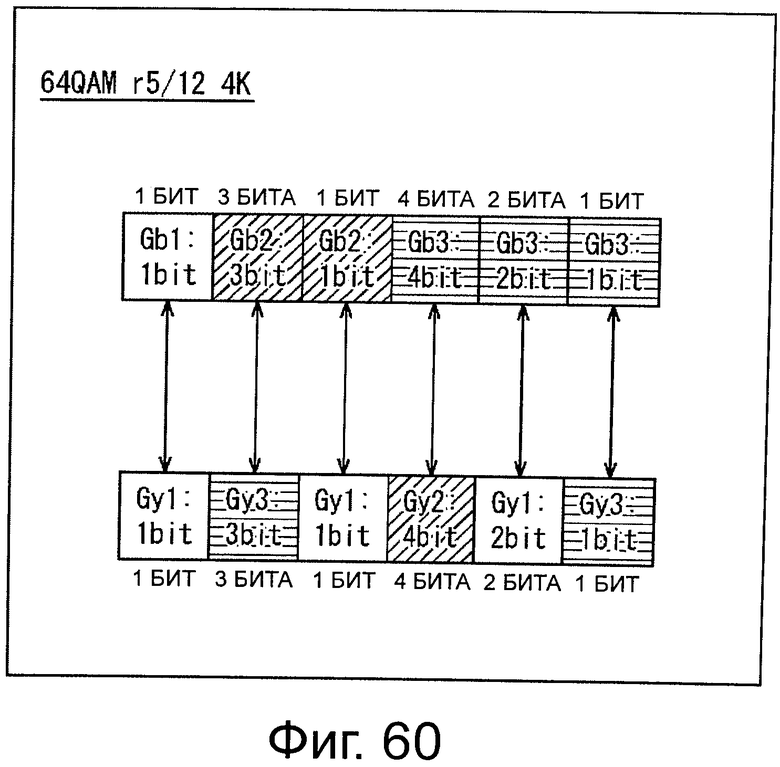

На фиг.59 показана схема, которая иллюстрирует группу кодовых битов и группу символьных битов в случае, когда код LDPC, имеющий длину кода 4 k и скорость кодирования 5/12, модулирован в соответствии с 64 QAM, и множитель b равен двум.

На фиг.60 показана схема, которая иллюстрирует правило выделения в случае, когда код LDPC, имеющий длину кода 4 k и скорость кодирования 5/12, модулирован в соответствии с 64 QAM, и множитель b равен двум.

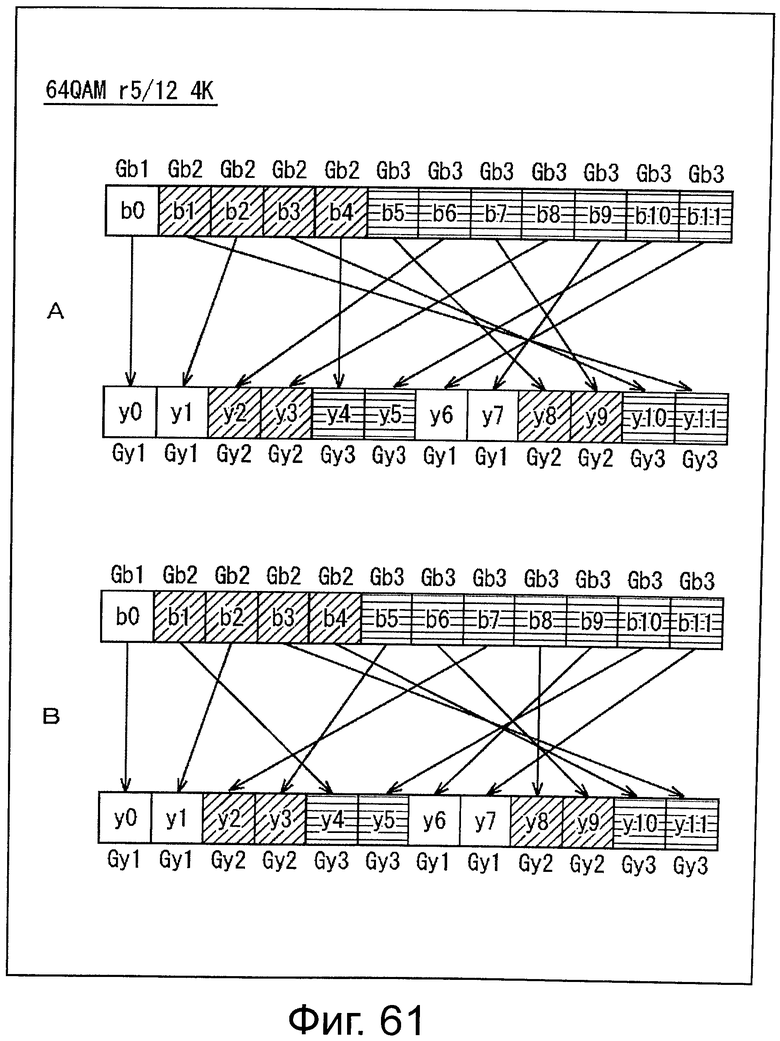

На фиг.61 показана схема, которая иллюстрирует взаимную замену кодовых битов в соответствии с правилом выделения в случае, когда код LDPC, имеющий длину кода 4 k и скорость кодирования 5/12, модулирован в соответствии с 64 QAM, и множитель b равен двум.

На фиг.62 показана схема, которая иллюстрирует группу кодовых битов и группу символьных битов в случае, когда код LDPC, имеющий длину кода 4 k и скорость кодирования 1/2, модулирован в соответствии с 64 QAM, и множитель b равен двум.

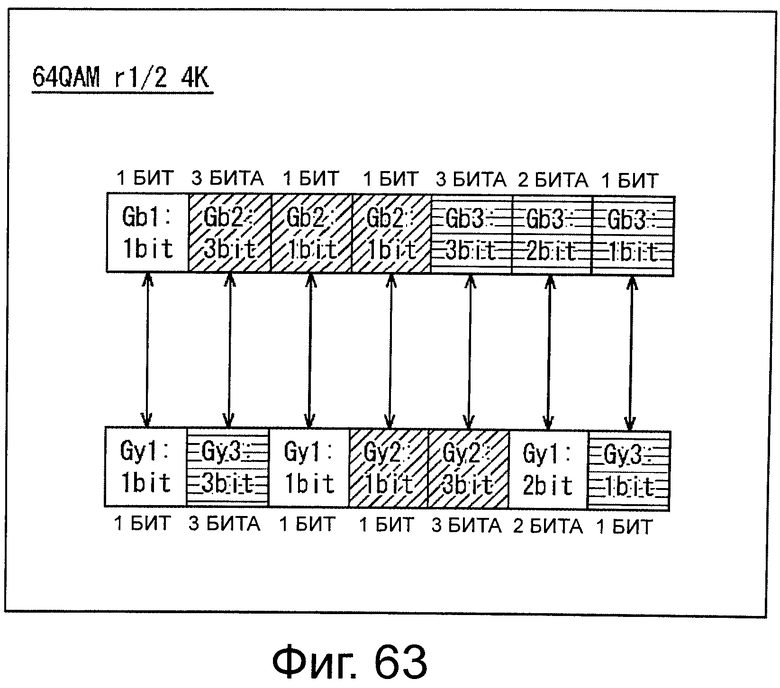

На фиг.63 показана схема, которая иллюстрирует правило выделения в случае, когда код LDPC, имеющий длину кода 4 k и скорость кодирования 1/2, модулирован в соответствии с 64 QAM, и множитель b равен двум.

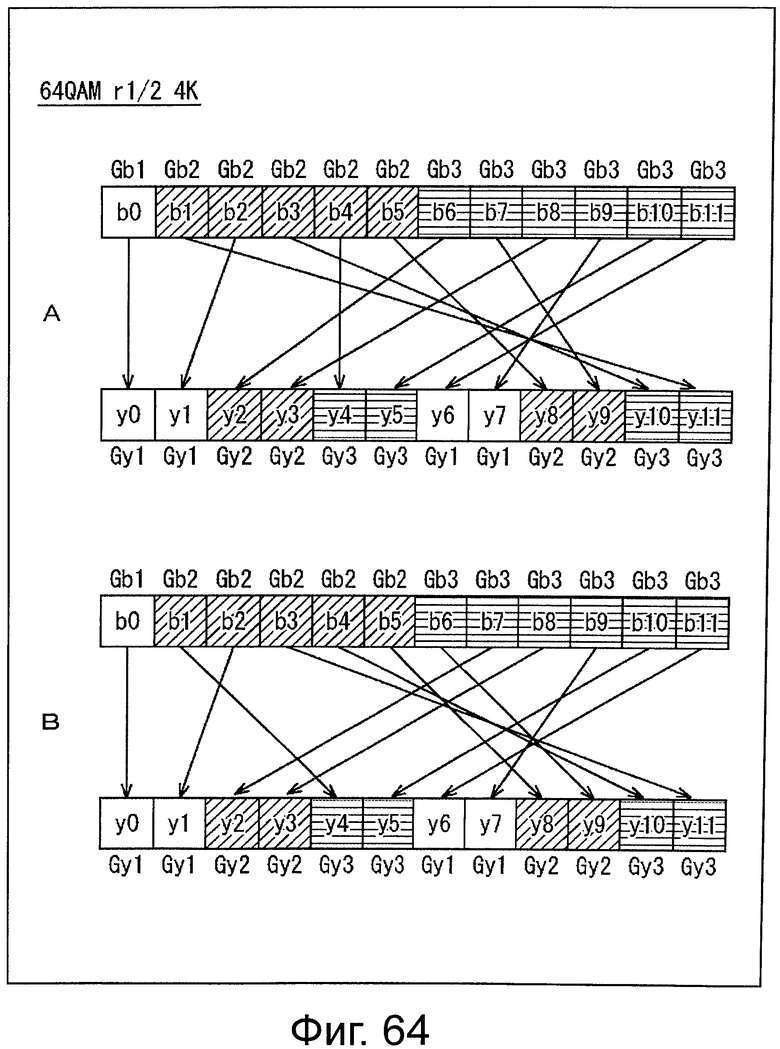

На фиг.64 показана схема, которая иллюстрирует взаимную замену кодовых битов в соответствии с правилом выделения в случае, когда код LDPC, имеющий длину кода 4 k и скорость кодирования 1/2, модулирован в соответствии с 64 QAM, и множитель b равен двум.

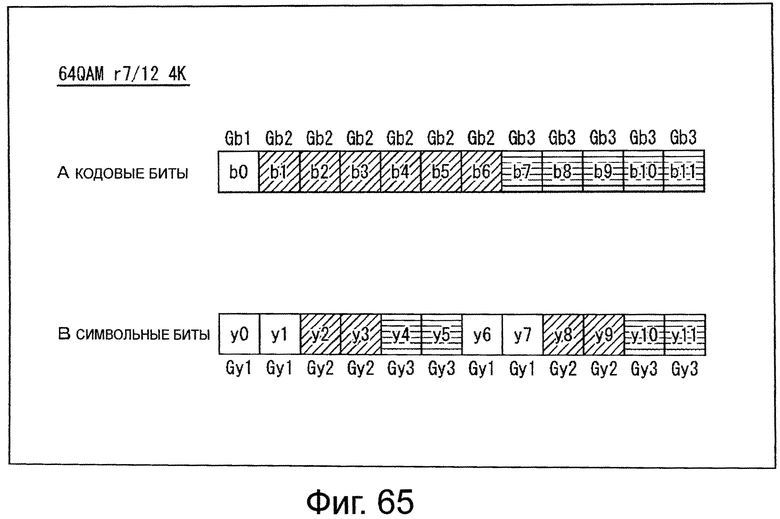

На фиг.65 показана схема, которая иллюстрирует группу кодовых битов и группу символьных битов в случае, когда код LDPC, имеющий длину кода 4 k и скорость кодирования 7/12, модулирован в соответствии с 64 QAM, и множитель b равен двум.

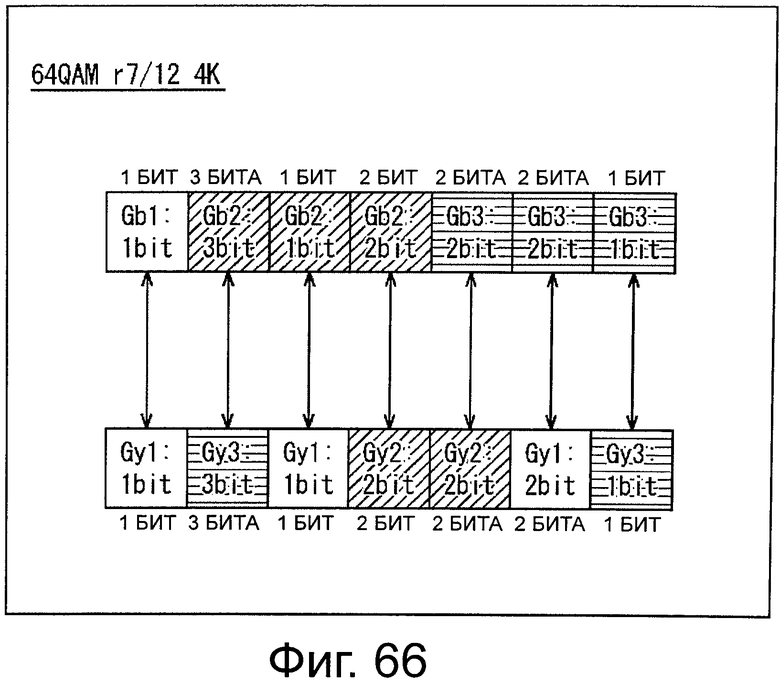

На фиг.66 показана схема, которая иллюстрирует правило выделения в случае, когда код LDPC, имеющий длину кода 4 k и скорость кодирования 7/12, модулирован в соответствии с 64 QAM, и множитель b равен двум.

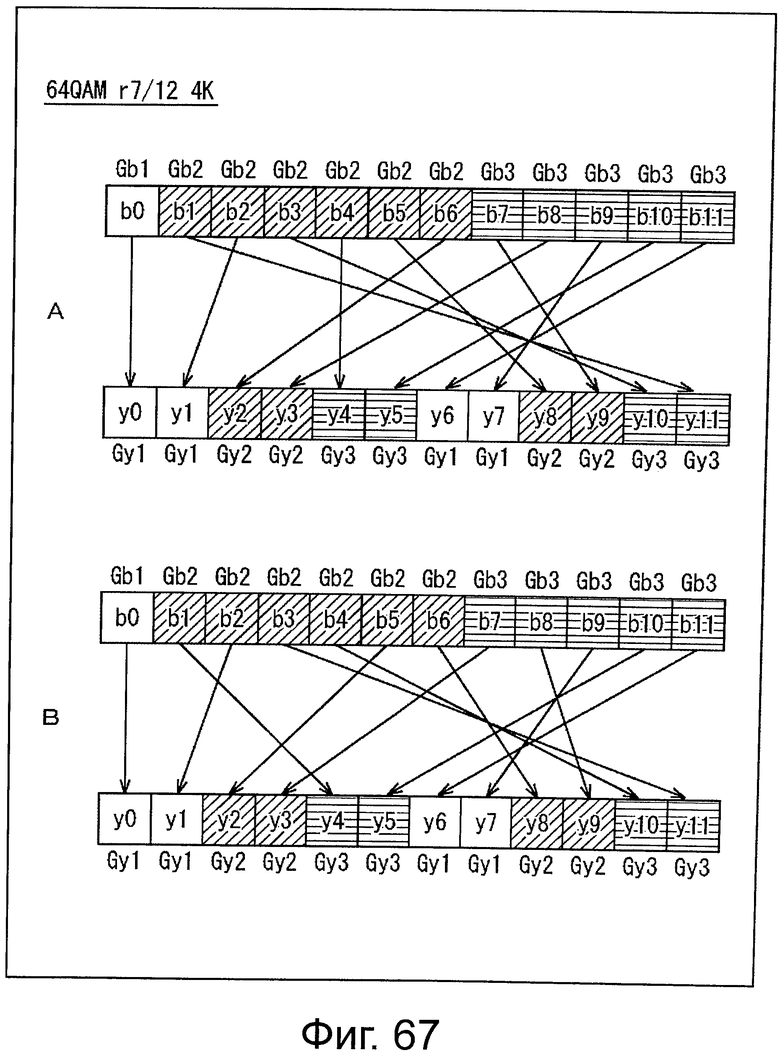

На фиг.67 показана схема, которая иллюстрирует взаимную замену кодовых битов в соответствии с правилом выделения в случае, когда код LDPC, имеющий длину кода 4 k и скорость кодирования 7/12, модулирован в соответствии с 64 QAM, и множитель b равен двум.

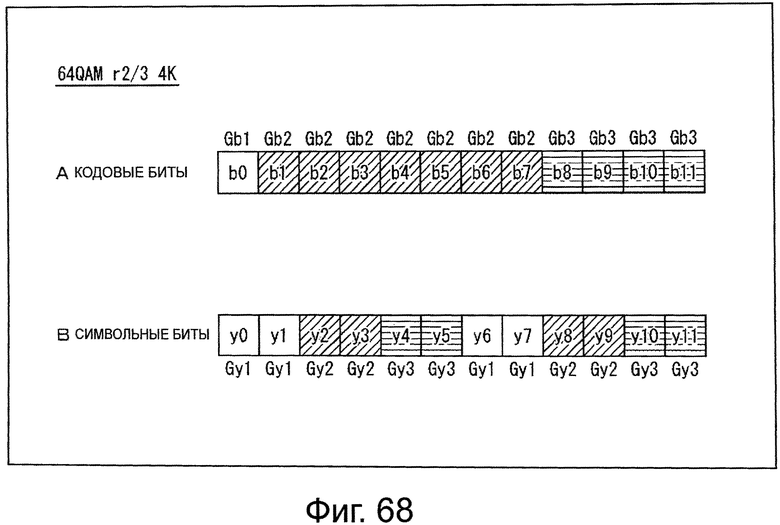

На фиг.68 показана схема, которая иллюстрирует группу кодовых битов и группу символьных битов в случае, когда код LDPC, имеющий длину кода 4 k и скорость кодирования 2/3, модулирован в соответствии с 64 QAM, и множитель b равен двум.

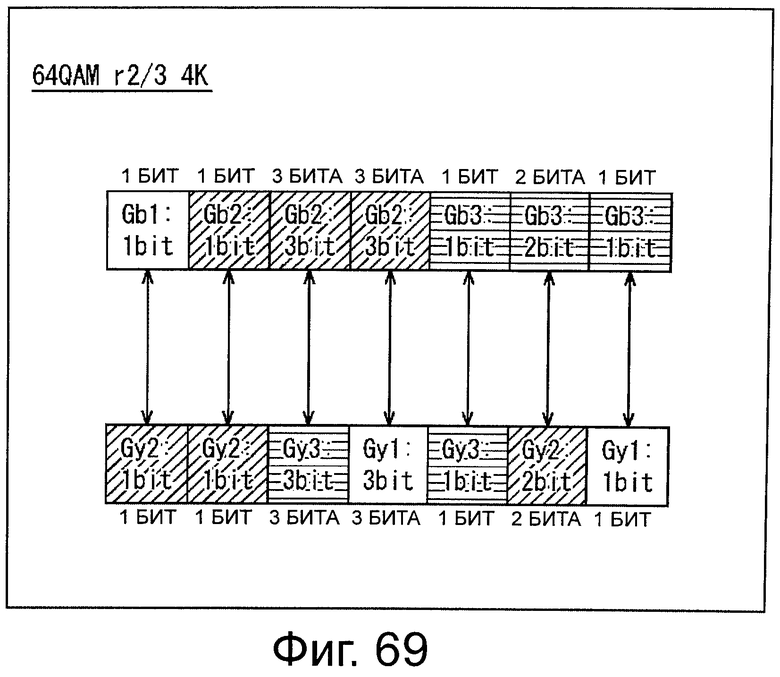

На фиг.69 показана схема, которая иллюстрирует правило выделения в случае, когда код LDPC, имеющий длину кода 4 k и скорость кодирования 2/3, модулирован в соответствии с 64 QAM, и множитель b равен двум.

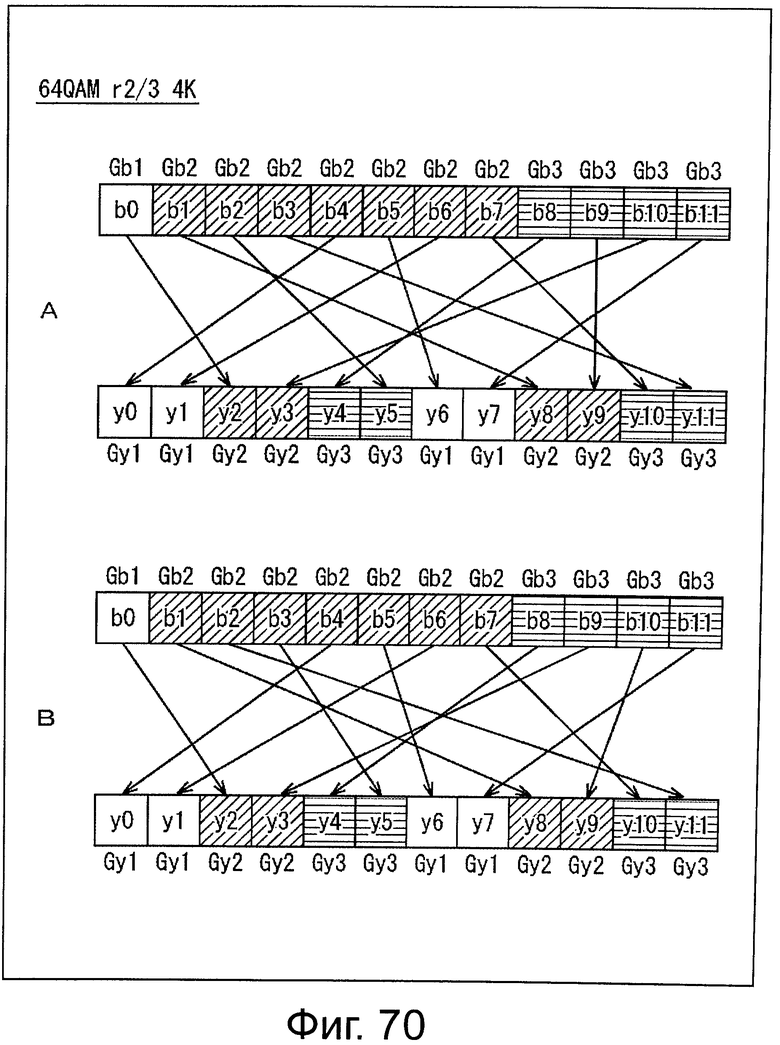

На фиг.70 показана схема, которая иллюстрирует взаимную замену кодовых битов в соответствии с правилом выделения в случае, когда код LDPC, имеющий длину кода 4 k и скорость кодирования 2/3, модулирован в соответствии с 64 QAM, и множитель b равен двум.

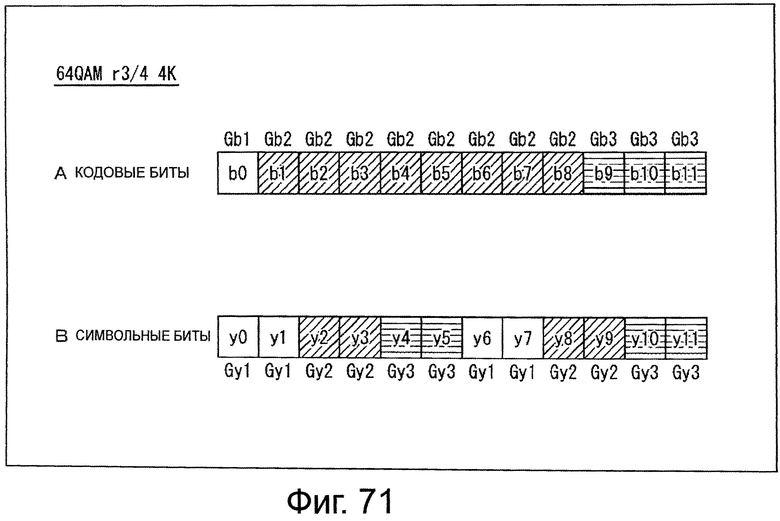

На фиг.71 показана схема, которая иллюстрирует группу кодовых битов и группу символьных битов в случае, когда код LDPC, имеющий длину кода 4 k и скорость кодирования 3/4, модулирован в соответствии с 64 QAM, и множитель b равен двум.

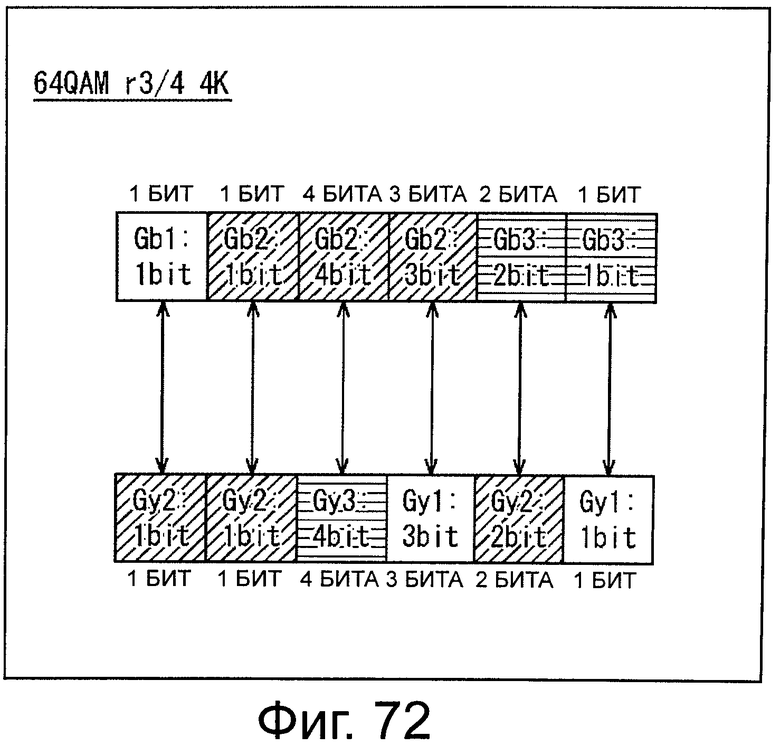

На фиг.72 показана схема, которая иллюстрирует правило выделения в случае, когда код LDPC, имеющий длину кода 4 k и скорость кодирования 3/4, модулирован в соответствии с 64 QAM, и множитель b равен двум.

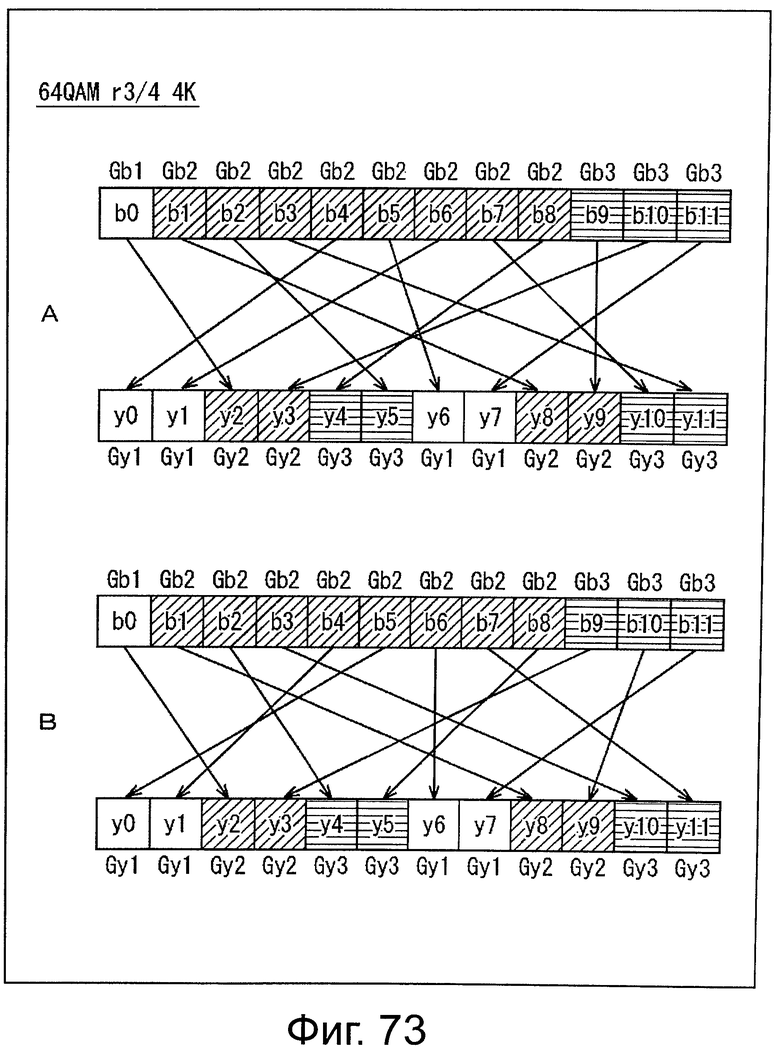

На фиг.73 показана схема, которая иллюстрирует взаимную замену кодовых битов, в соответствии с правилом выделения, в случае, когда код LDPC, имеющий длину кода 4 k и скорость кодирования 3/4, модулирован в соответствии с 64 QAM, и множитель b равен двум.

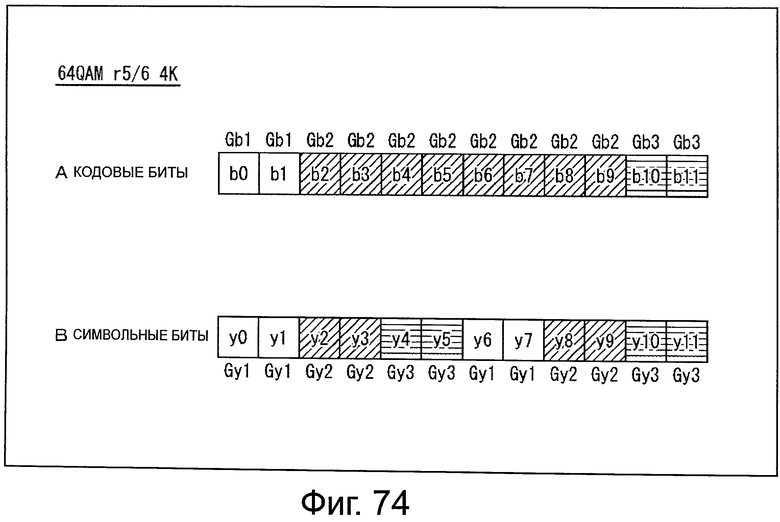

На фиг.74 показана схема, которая иллюстрирует группу кодовых битов и группу символьных битов в случае, когда код LDPC, имеющий длину кода 4 k и скорость кодирования 5/6, модулирован в соответствии с 64 QAM, и множитель b равен двум.

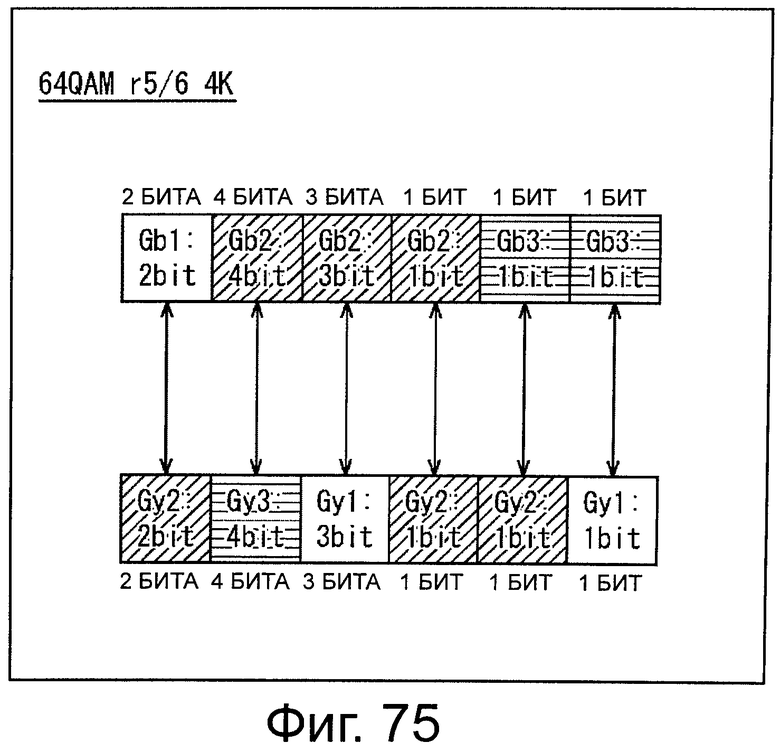

На фиг.75 показана схема, которая иллюстрирует правило выделения в случае, когда код LDPC, имеющий длину кода 4 k и скорость кодирования 5/6, модулирован в соответствии с 64 QAM, и множитель b равен двум.

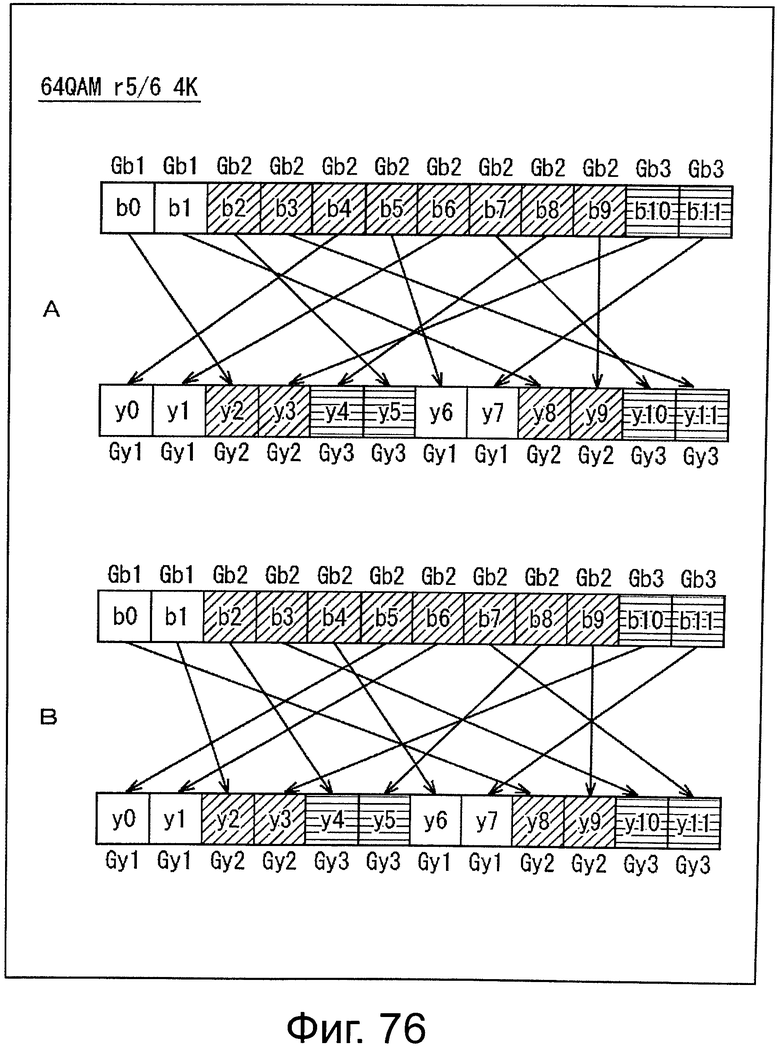

На фиг.76 показана схема, которая иллюстрирует взаимную замену кодовых битов в соответствии с правилом выделения в случае, когда код LDPC, имеющий длину кода 4 k и скорость кодирования 5/6, модулирован в соответствии с 64 QAM, и множитель b равен двум.

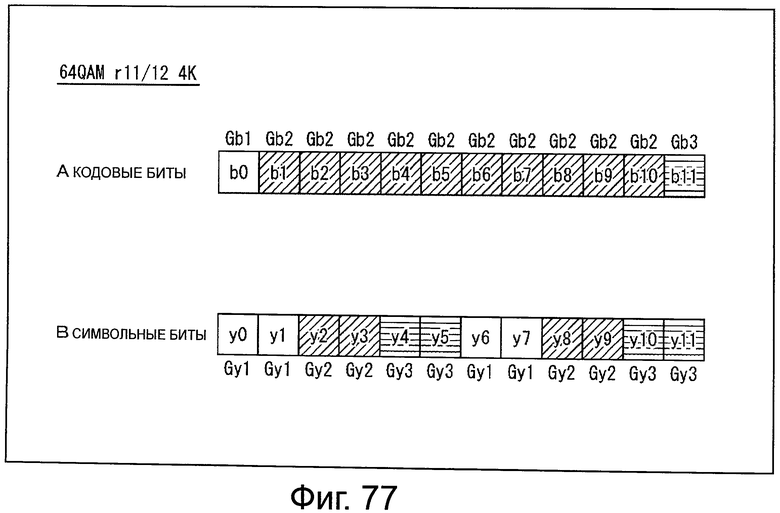

На фиг.77 показана схема, которая иллюстрирует группу кодовых битов и группу символьных битов в случае, когда код LDPC, имеющий длину кода 4 k и скорость кодирования 11/12, модулирован в соответствии с 64 QAM, и множитель b равен двум.

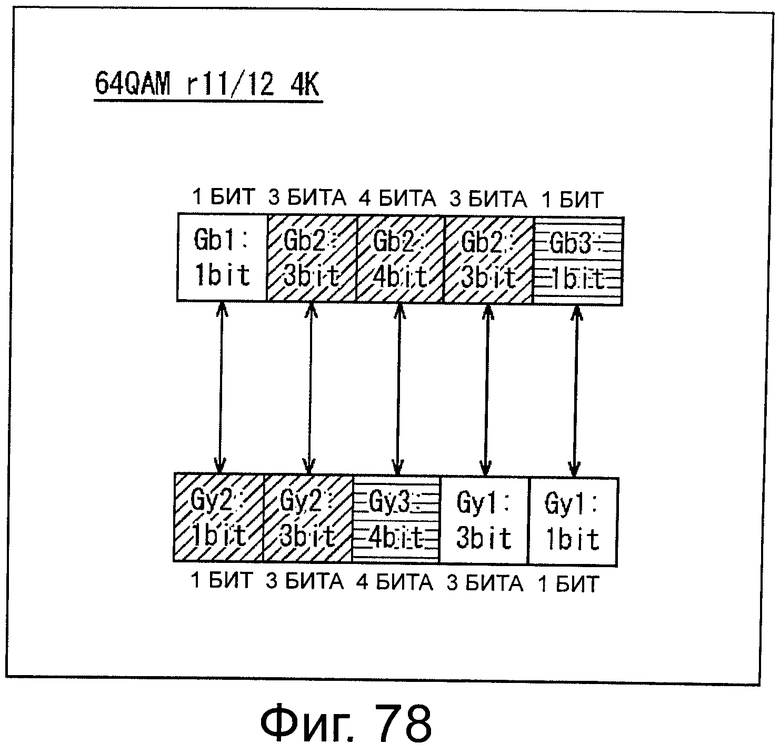

На фиг.78 показана схема, которая иллюстрирует правило выделения в случае, когда код LDPC, имеющий длину кода 4 k и скорость кодирования 11/12, модулирован в соответствии с 64 QAM, и множитель b равен двум.

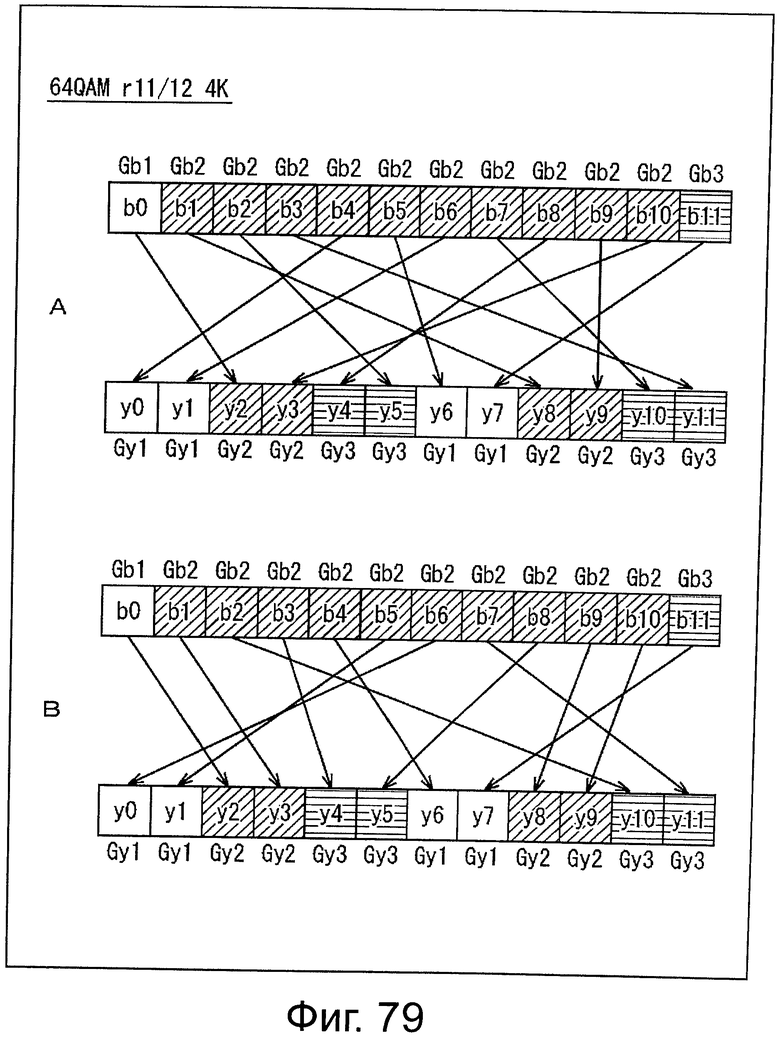

На фиг.79 показана схема, которая иллюстрирует взаимную замену кодовых битов в соответствии с правилом выделения в случае, когда код LDPC, имеющий длину кода 4 k и скорость кодирования 11/12, модулирован в соответствии с 64 QAM, и множитель b равен двум.

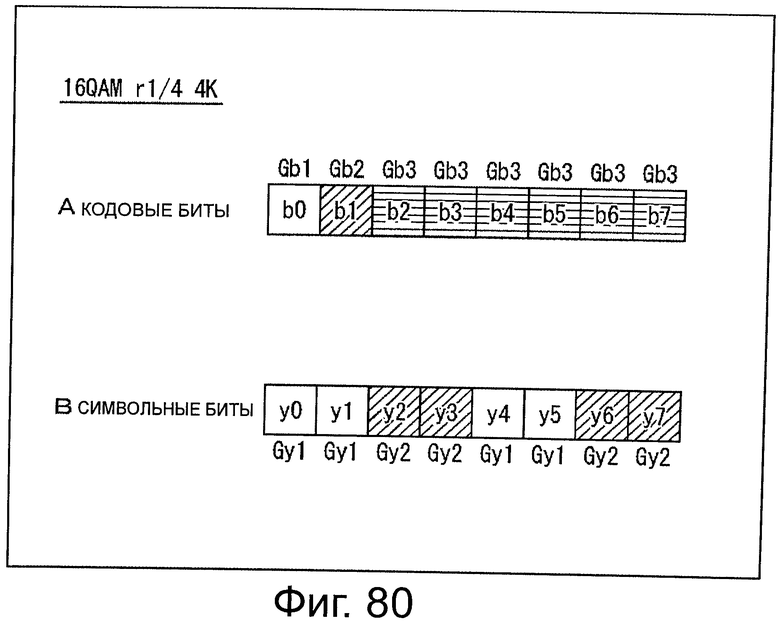

На фиг.80 показана схема, которая иллюстрирует группу кодовых битов и группу символьных битов в случае, когда код LDPC, имеющий длину кода 4 k и скорость кодирования 1/4, модулирован в соответствии с 16 QAM, и множитель b равен двум.

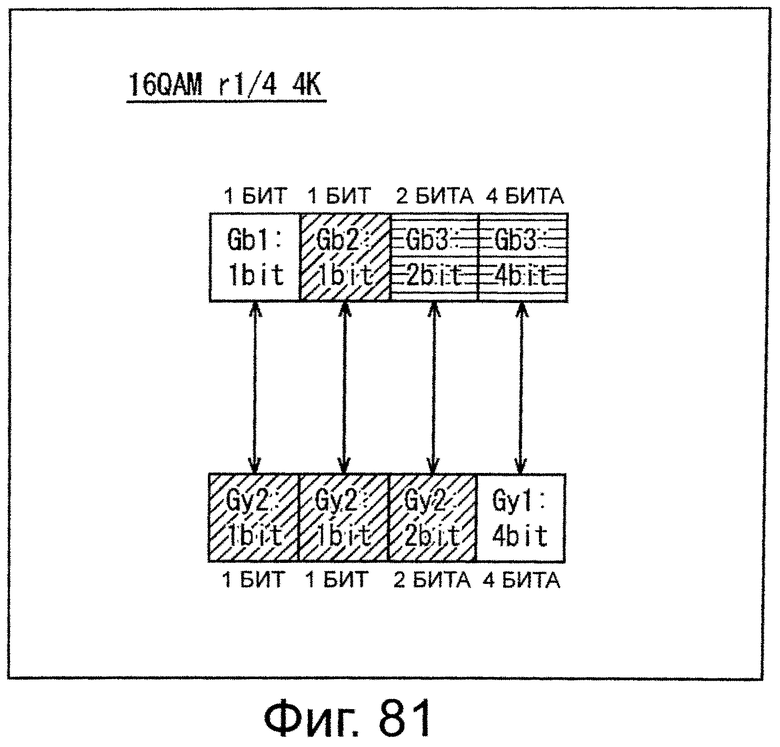

На фиг.81 показана схема, которая иллюстрирует правило выделения в случае, когда код LDPC, имеющий длину кода 4 k и скорость кодирования 1/4, модулирован в соответствии с 16 QAM, и множитель b равен двум.

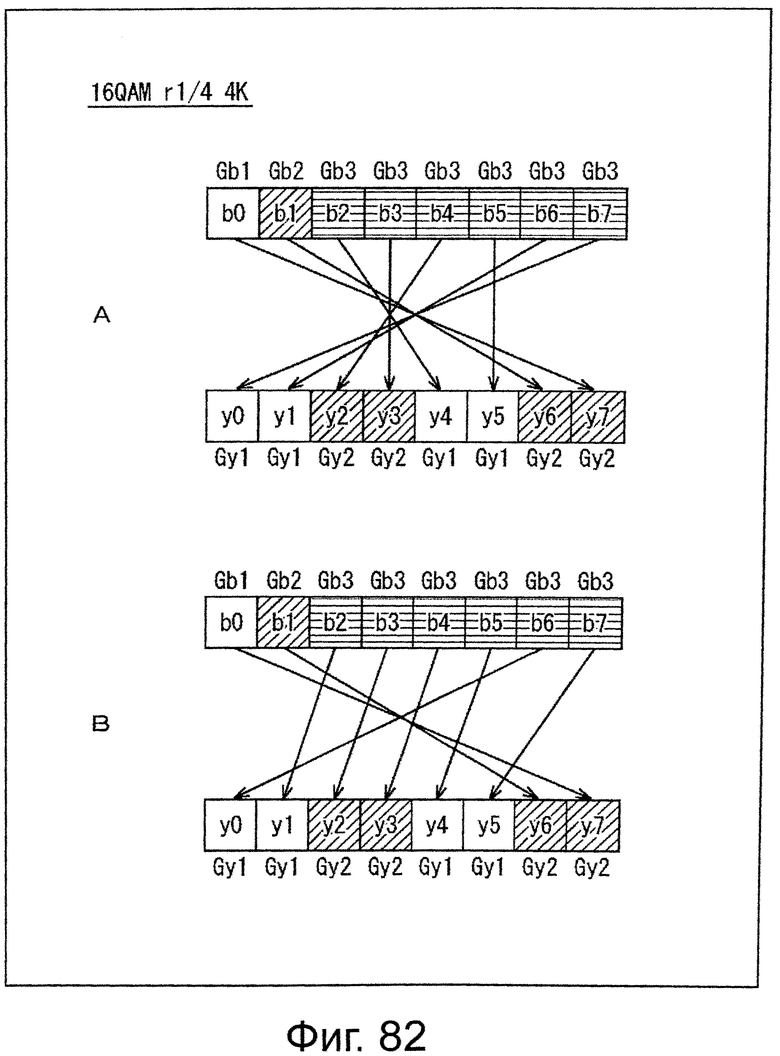

На фиг.82 показана схема, которая иллюстрирует взаимную замену кодовых битов в соответствии с правилом выделения в случае, когда код LDPC, имеющий длину кода 4 k и скорость кодирования 1/4, модулирован в соответствии с 16 QAM, и множитель b равен двум.

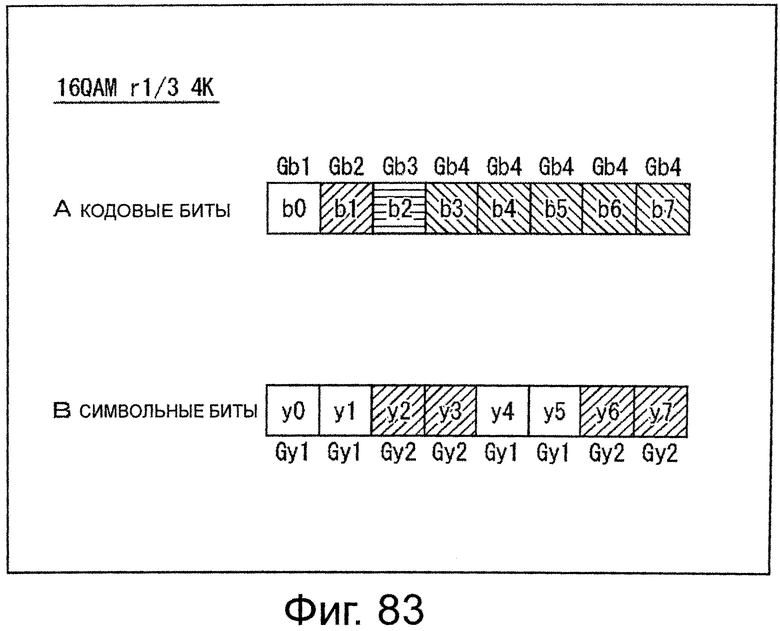

На фиг.83 показана схема, которая иллюстрирует группу кодовых битов и группу символьных битов в случае, когда код LDPC, имеющий длину кода 4 k и скорость кодирования 1/3, модулирован в соответствии с 16 QAM, и множитель b равен двум.

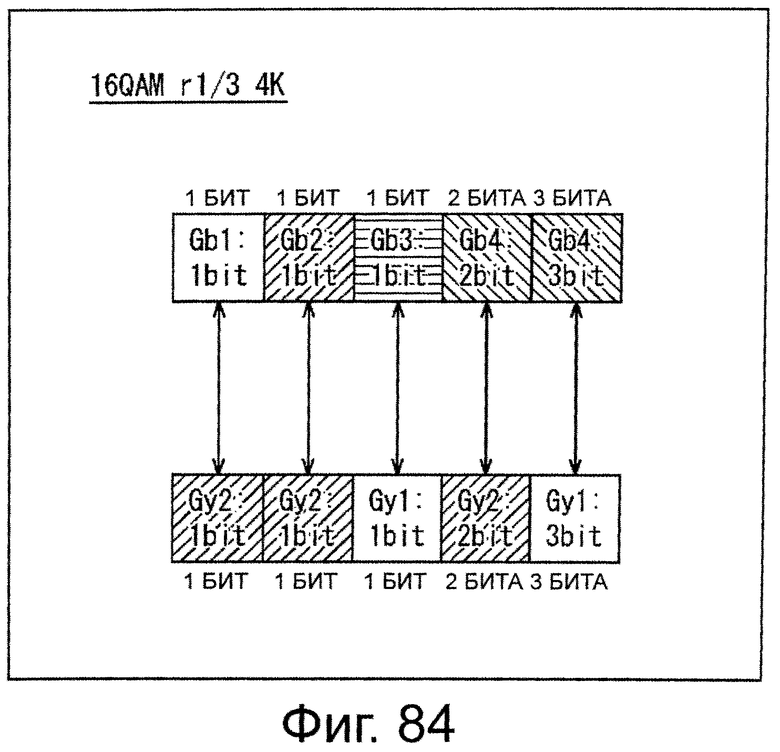

На фиг.84 показана схема, которая иллюстрирует правило выделения в случае, когда код LDPC, имеющий длину кода 4 k и скорость кодирования 1/3, модулирован в соответствии с 16 QAM, и множитель b равен двум.

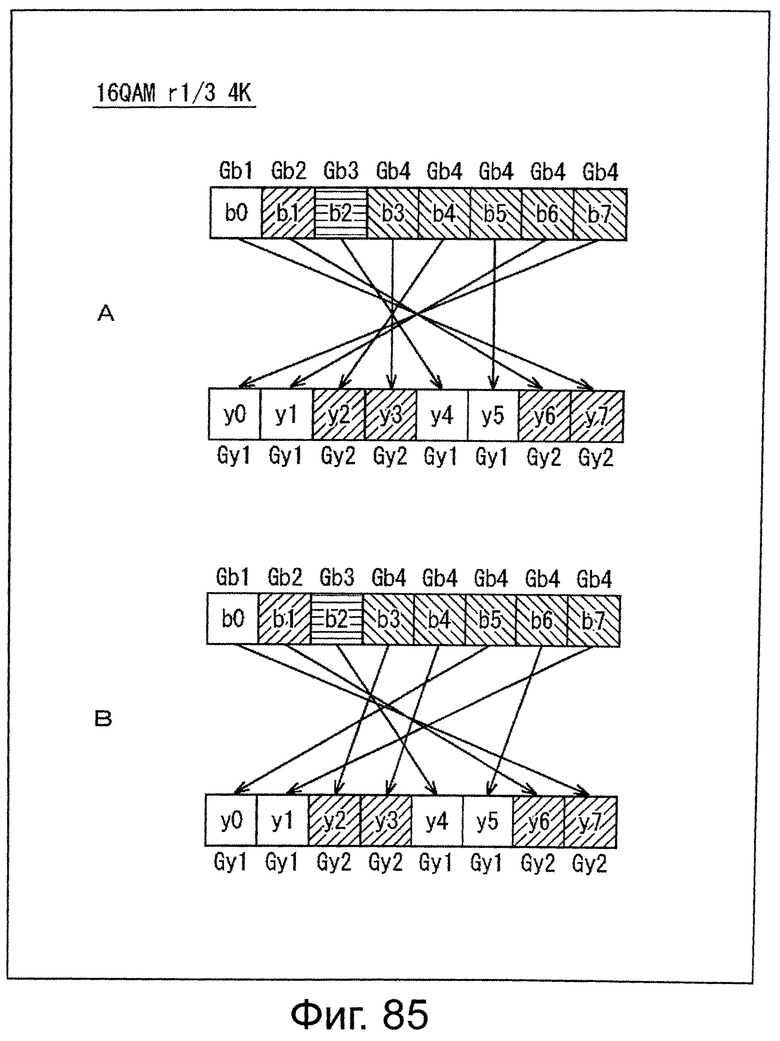

На фиг.85 показана схема, которая иллюстрирует взаимную замену кодовых битов в соответствии с правилом выделения в случае, когда код LDPC, имеющий длину кода 4 k и скорость кодирования 1/3, модулирован в соответствии с 16 QAM, и множитель b равен двум.

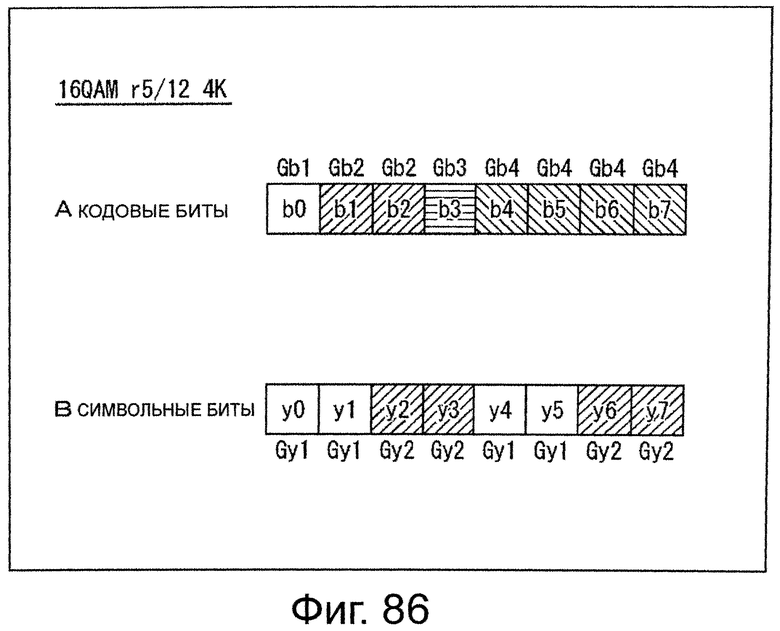

На фиг.86 показана схема, которая иллюстрирует группу кодовых битов и группу символьных битов в случае, когда код LDPC, имеющий длину кода 4 k и скорость кодирования 5/12, модулирован в соответствии с 16 QAM, и множитель b равен двум.

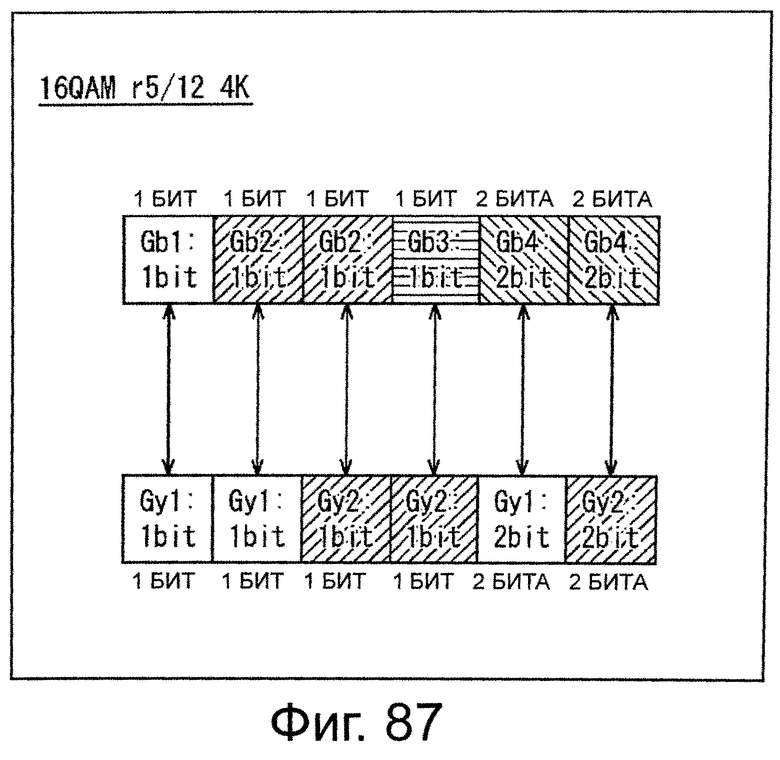

На фиг.87 показана схема, которая иллюстрирует правило выделения в случае, когда код LDPC, имеющий длину кода 4 k и скорость кодирования 5/12, модулирован в соответствии с 16 QAM, и множитель b равен двум.

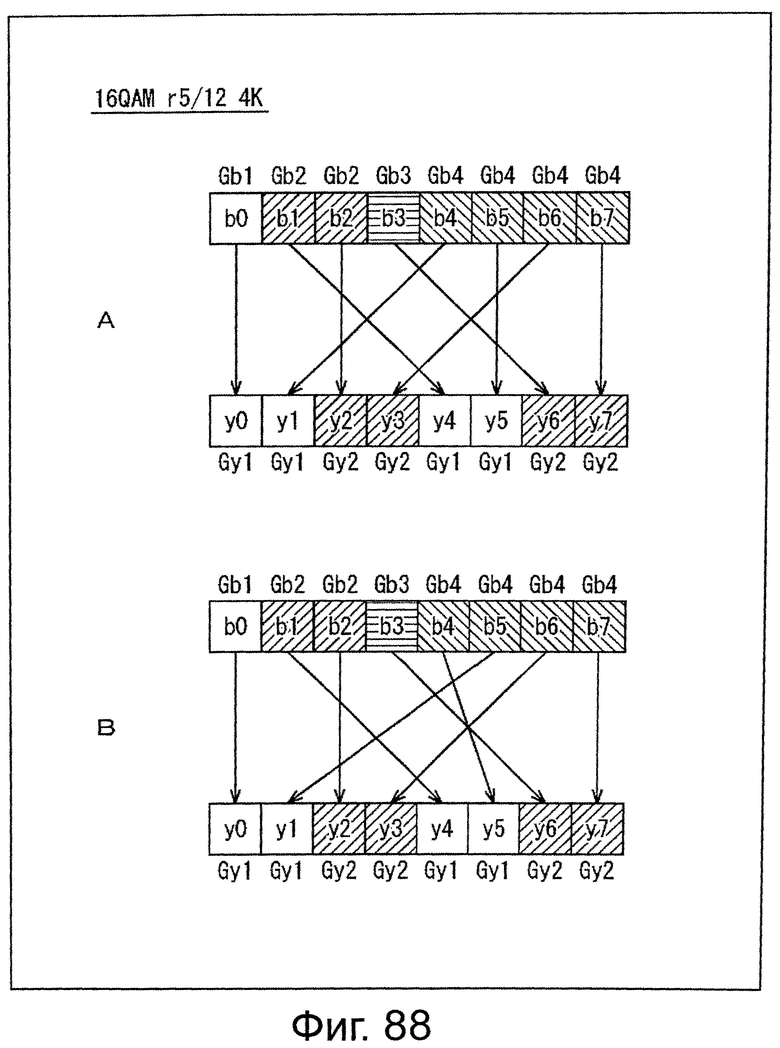

На фиг.88 показана схема, которая иллюстрирует взаимную замену кодовых битов в соответствии с правилом выделения в случае, когда код LDPC, имеющий длину кода 4 k и скорость кодирования 5/12, модулирован в соответствии с 16 QAM, и множитель b равен двум.

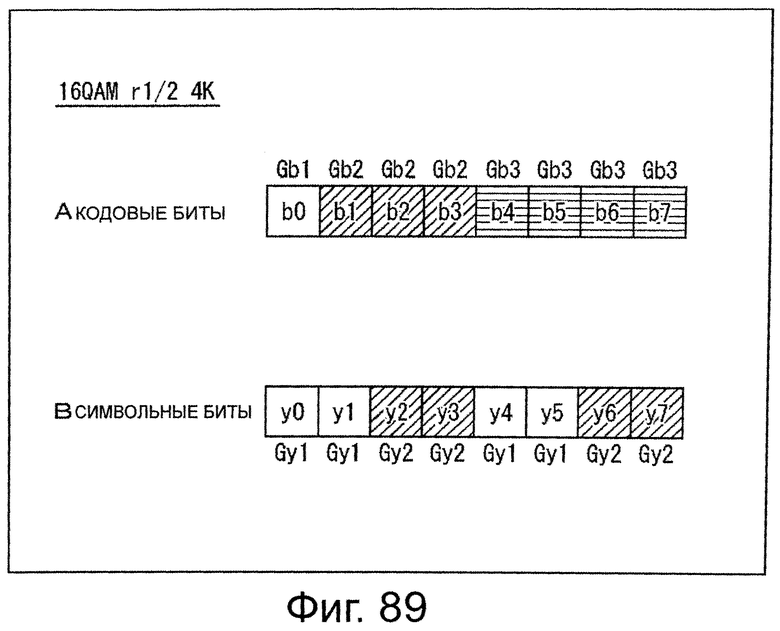

На фиг.89 показана схема, которая иллюстрирует группу кодовых битов и группу символьных битов в случае, когда код LDPC, имеющий длину кода 4 k и скорость кодирования 1/2, модулирован в соответствии с 16 QAM, и множитель b равен двум.

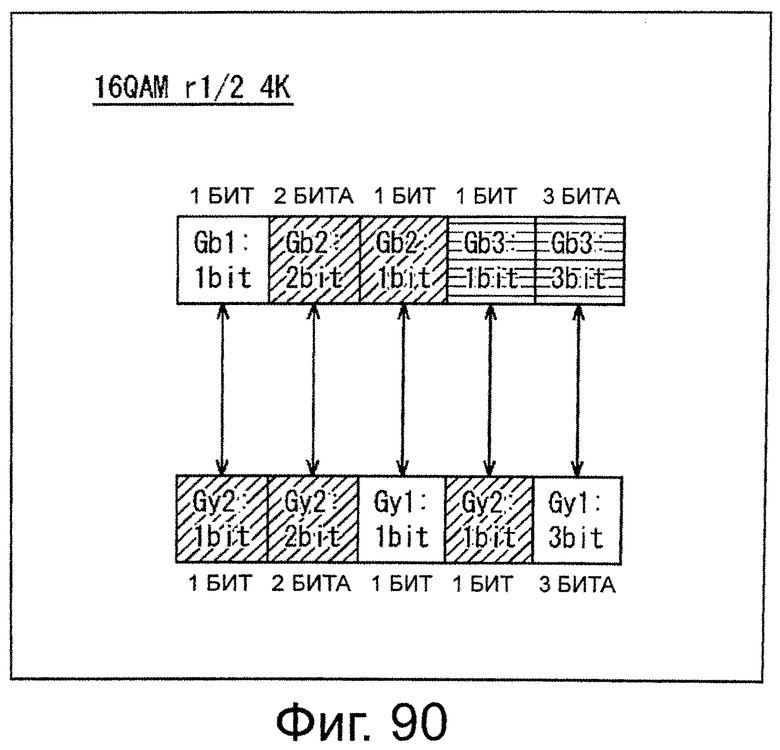

На фиг.90 показана схема, которая иллюстрирует правило выделения в случае, когда код LDPC, имеющий длину кода 4 k и скорость кодирования 1/2, модулирован в соответствии с 16 QAM, и множитель b равен двум.

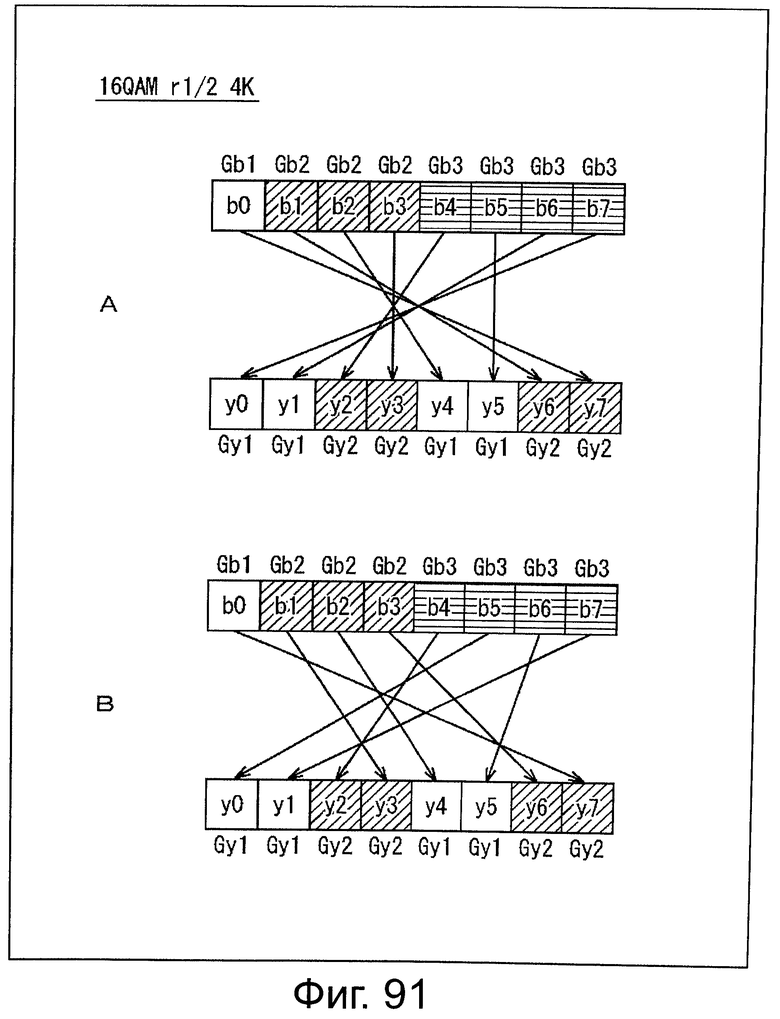

На фиг.91 показана схема, которая иллюстрирует взаимную замену кодовых битов в соответствии с правилом выделения в случае, когда код LDPC, имеющий длину кода 4 k и скорость кодирования 1/2, модулирован в соответствии с 16 QAM, и множитель b равен двум.

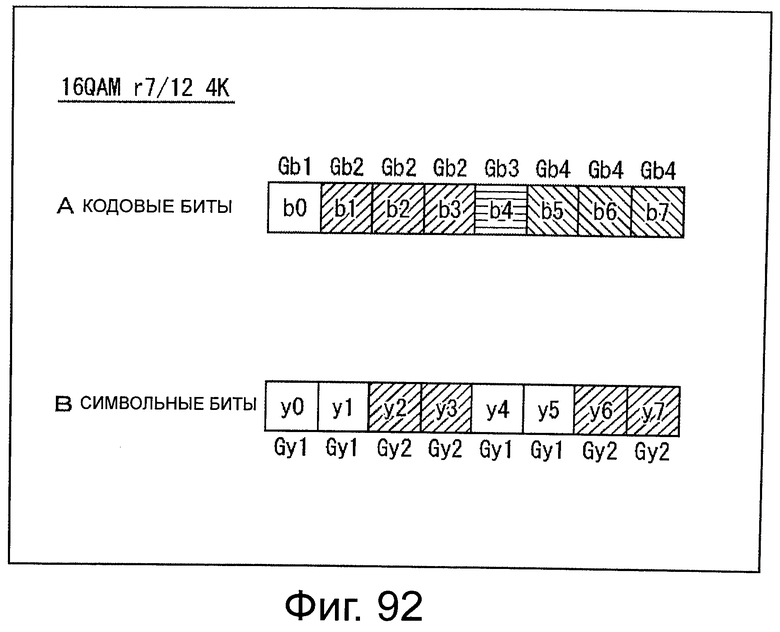

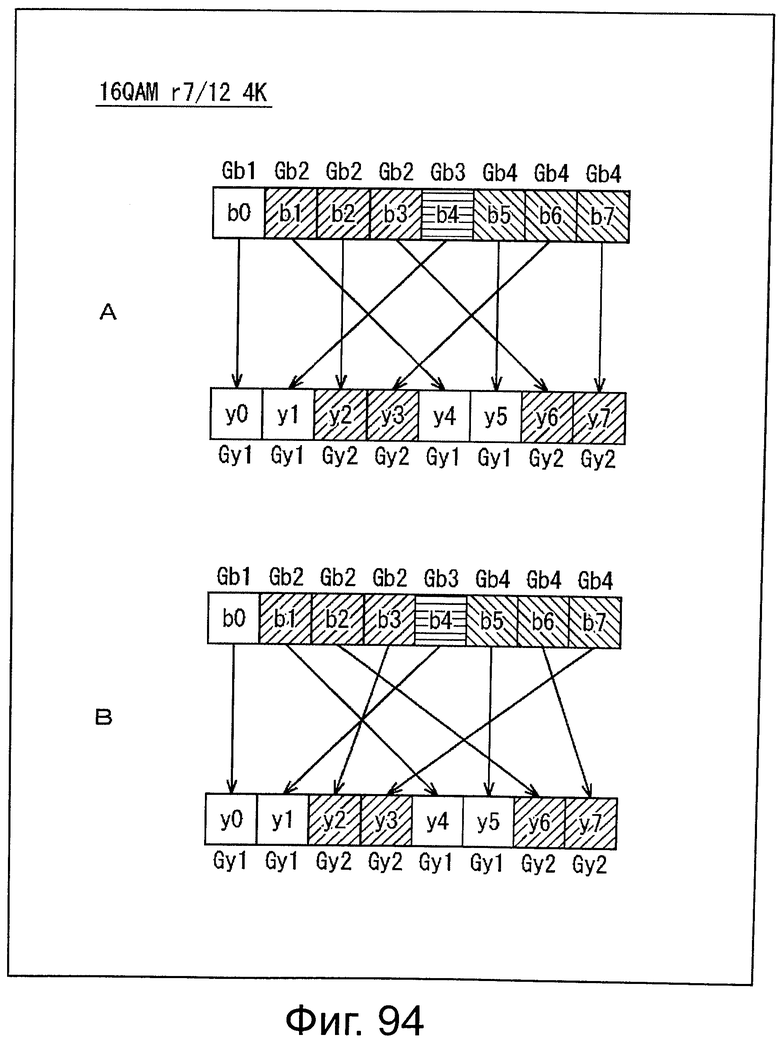

На фиг.92 показана схема, которая иллюстрирует группу кодовых битов и группу символьных битов в случае, когда код LDPC, имеющий длину кода 4 k и скорость кодирования 7/12, модулирован в соответствии с 16 QAM, и множитель b равен двум.

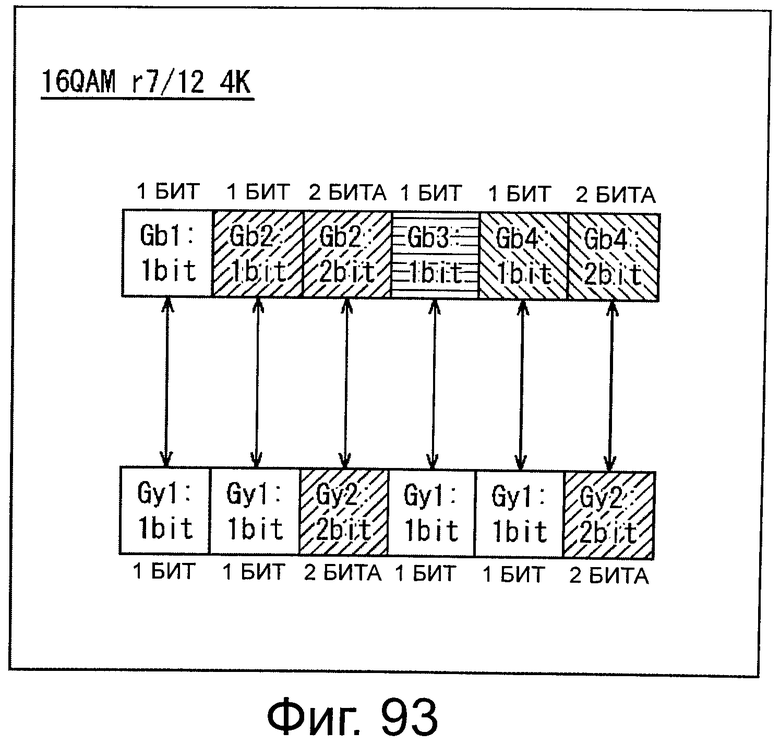

На фиг.93 показана схема, которая иллюстрирует правило выделения в случае, когда код LDPC, имеющий длину кода 4 k и скорость кодирования 7/12, модулирован в соответствии с 16 QAM, и множитель b равен двум.

На фиг.94 показана схема, которая иллюстрирует взаимную замену кодовых битов в соответствии с правилом выделения в случае, когда код LDPC, имеющий длину кода 4 k и скорость кодирования 7/12, модулирован в соответствии с 16 QAM, и множитель b равен двум.

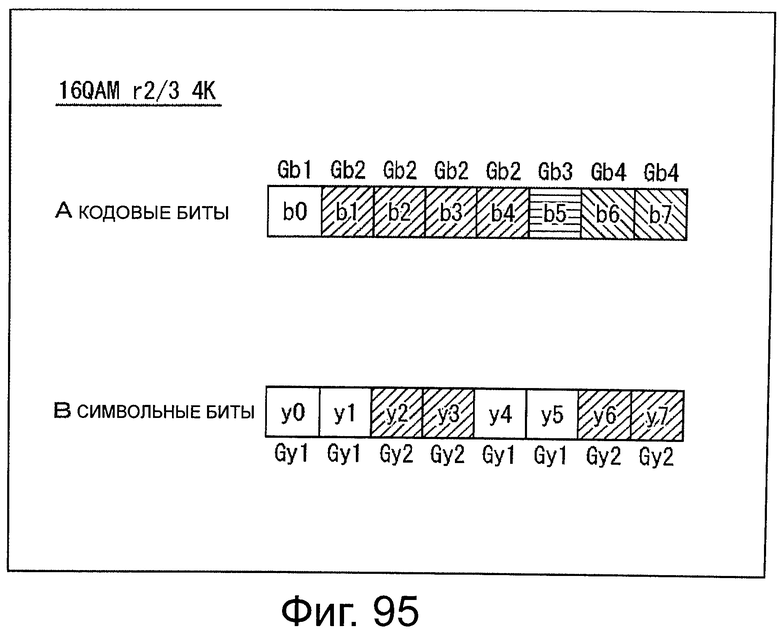

На фиг.95 показана схема, которая иллюстрирует группу кодовых битов и группу символьных битов в случае, когда код LDPC, имеющий длину кода 4 k и скорость кодирования 2/3, модулирован в соответствии с 16 QAM, и множитель b равен двум.

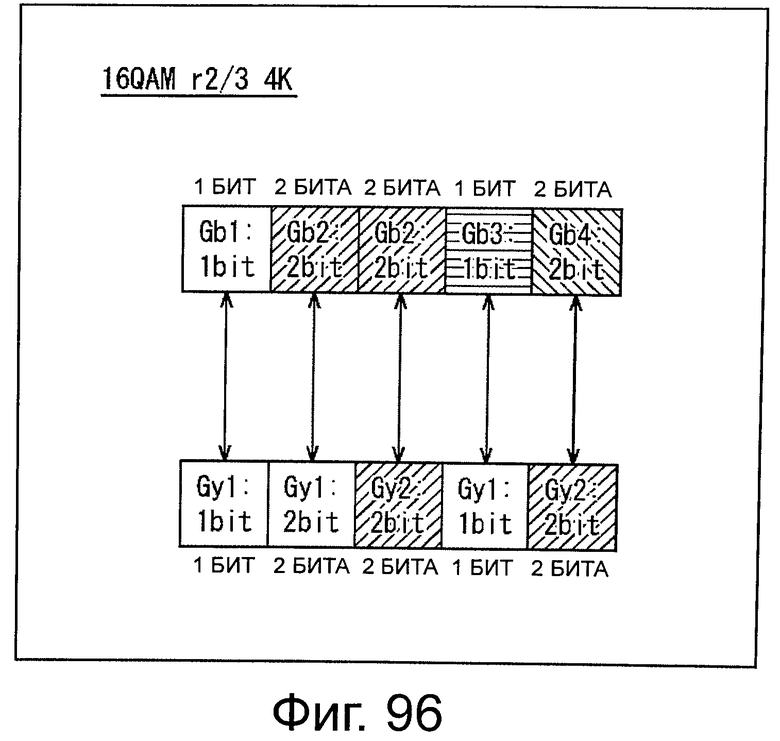

На фиг.96 показана схема, которая иллюстрирует правило выделения в случае, когда код LDPC, имеющий длину кода 4 k и скорость кодирования 2/3, модулирован в соответствии с 16 QAM, и множитель b равен двум.

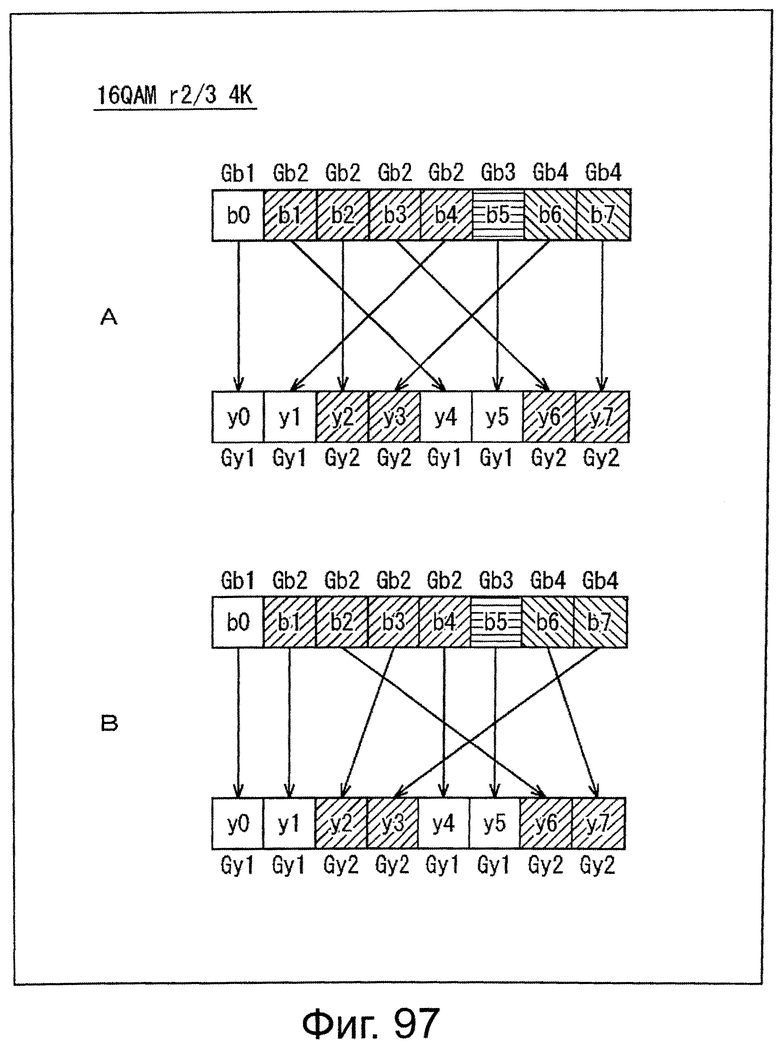

На фиг.97 показана схема, которая иллюстрирует взаимную замену в случае, когда код LDPC, имеющий длину кода 4 k и скорость кодирования 2/3, модулирован в соответствии с 16 QAM, и множитель b равен двум.

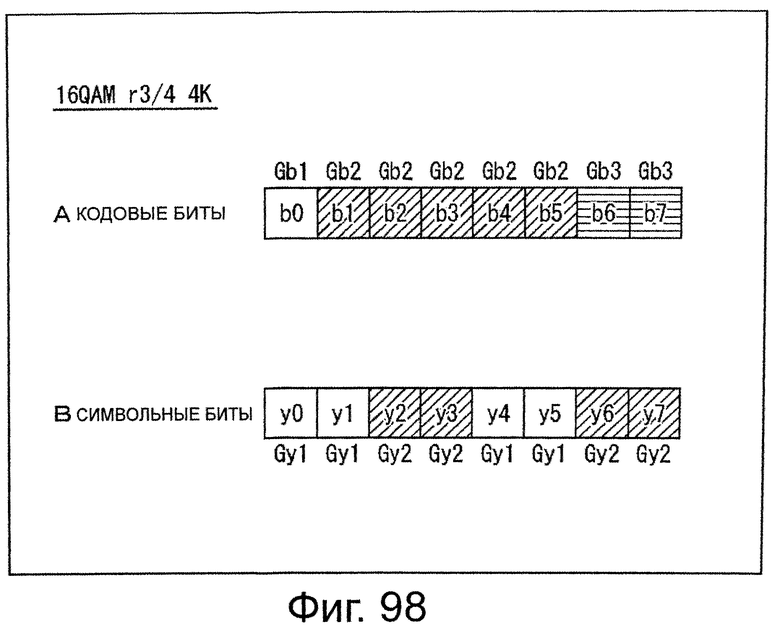

На фиг.98 показана схема, которая иллюстрирует группу кодовых битов и группу символьных битов в случае, когда код LDPC, имеющий длину кода 4 k и скорость кодирования 3/4, модулирован в соответствии с 16 QAM, и множитель b равен двум.

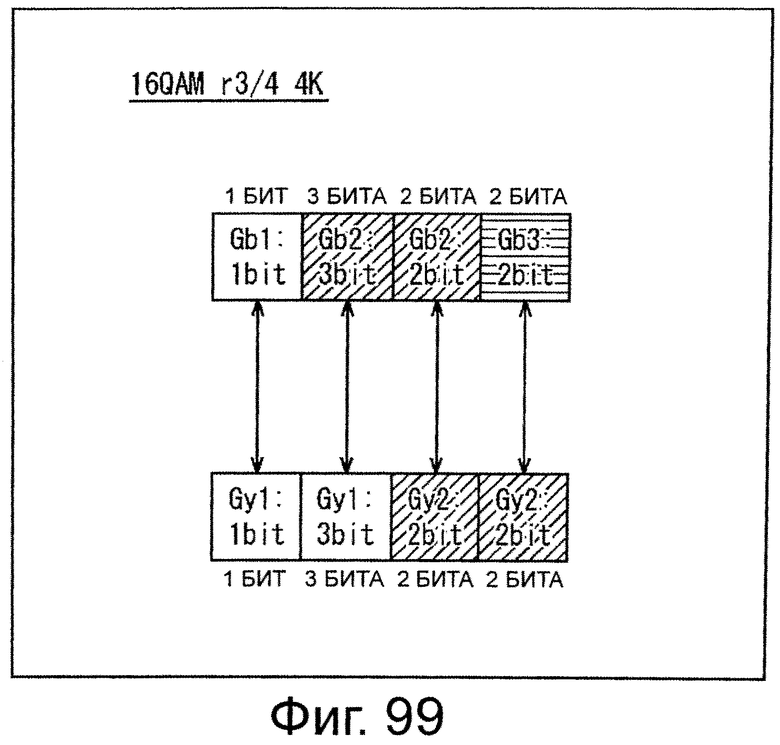

На фиг.99 показана схема, которая иллюстрирует правило выделения в случае, когда код LDPC, имеющий длину кода 4 k и скорость кодирования 3/4, модулирован в соответствии с 16 QAM, и множитель b равен двум.

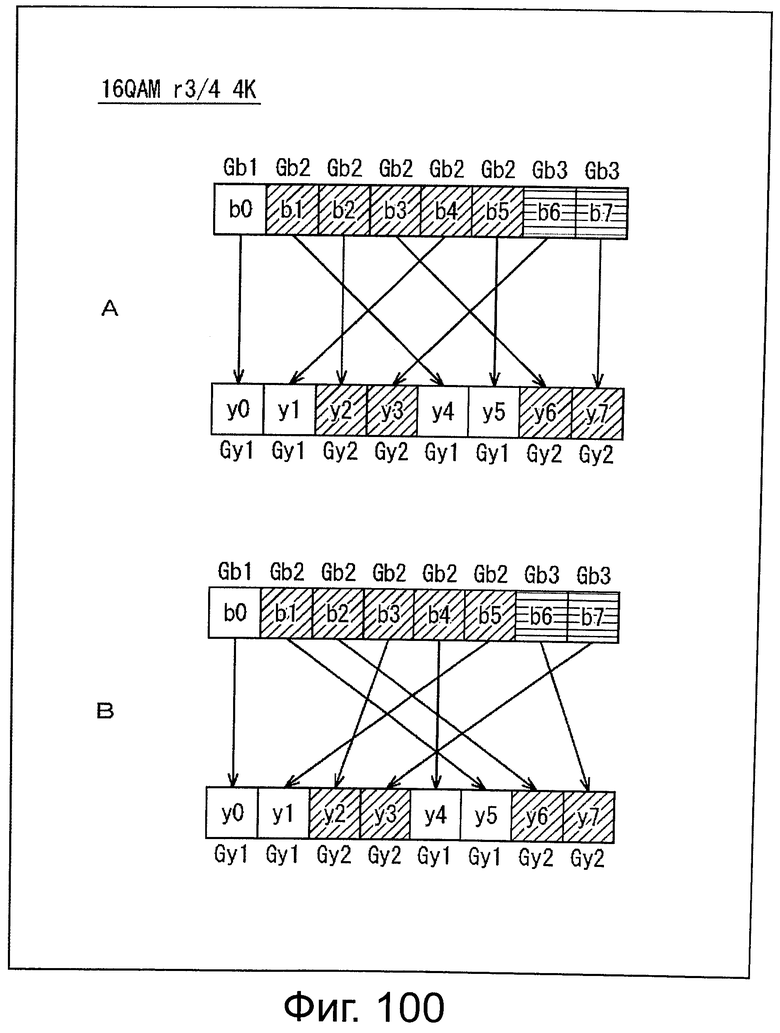

На фиг.100 показана схема, которая иллюстрирует взаимную замену кодовых битов в соответствии с правилом выделения в случае, когда код LDPC, имеющий длину кода 4 k и скорость кодирования 3/4, модулирован в соответствии с 16 QAM, и множитель b равен двум.

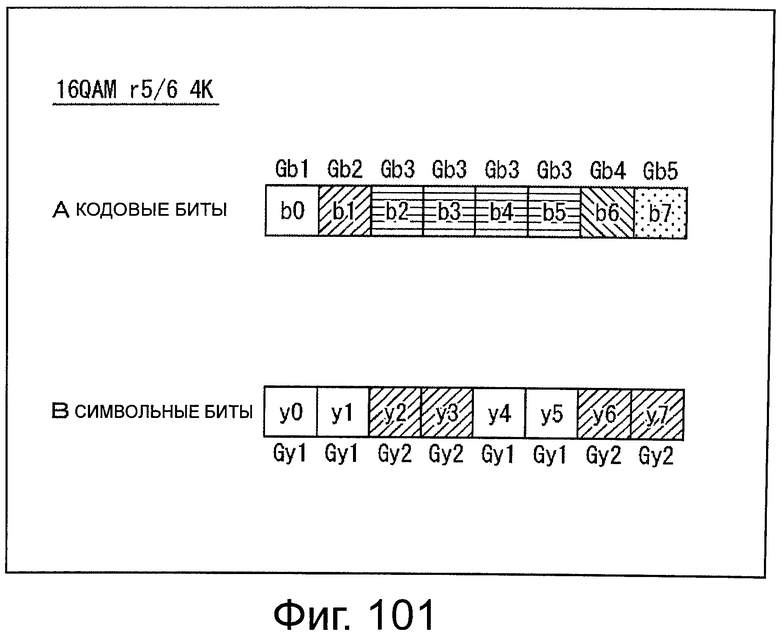

На фиг.101 показана схема, которая иллюстрирует группу кодовых битов и группу символьных битов в случае, когда код LDPC, имеющий длину кода 4 k и скорость кодирования 5/6, модулирован в соответствии с 16 QAM, и множитель b равен двум.

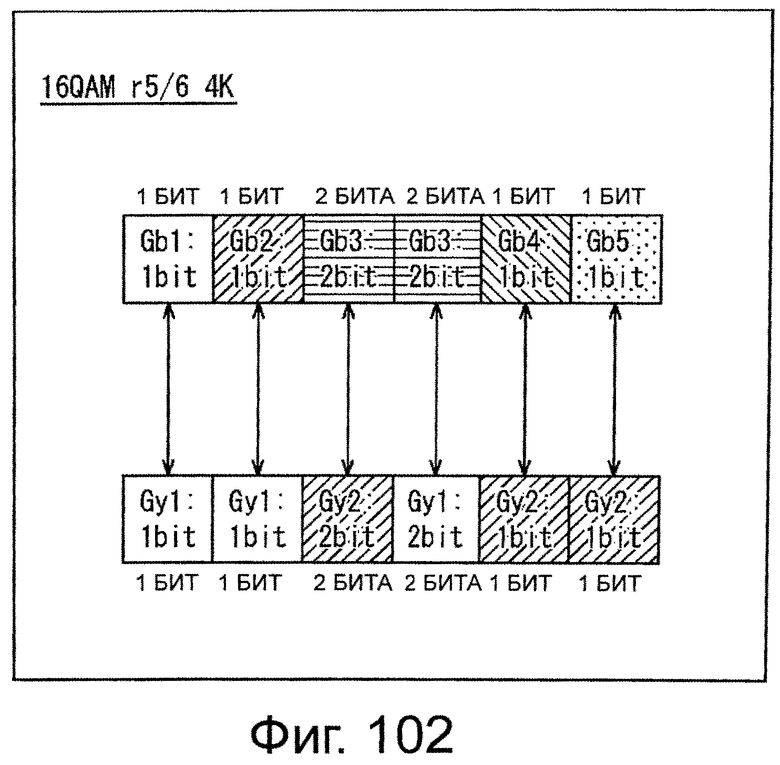

На фиг.102 показана схема, которая иллюстрирует правило выделения в случае, когда код LDPC, имеющий длину кода 4 k и скорость кодирования 5/6, модулирован в соответствии с 16 QAM, и множитель b равен двум.

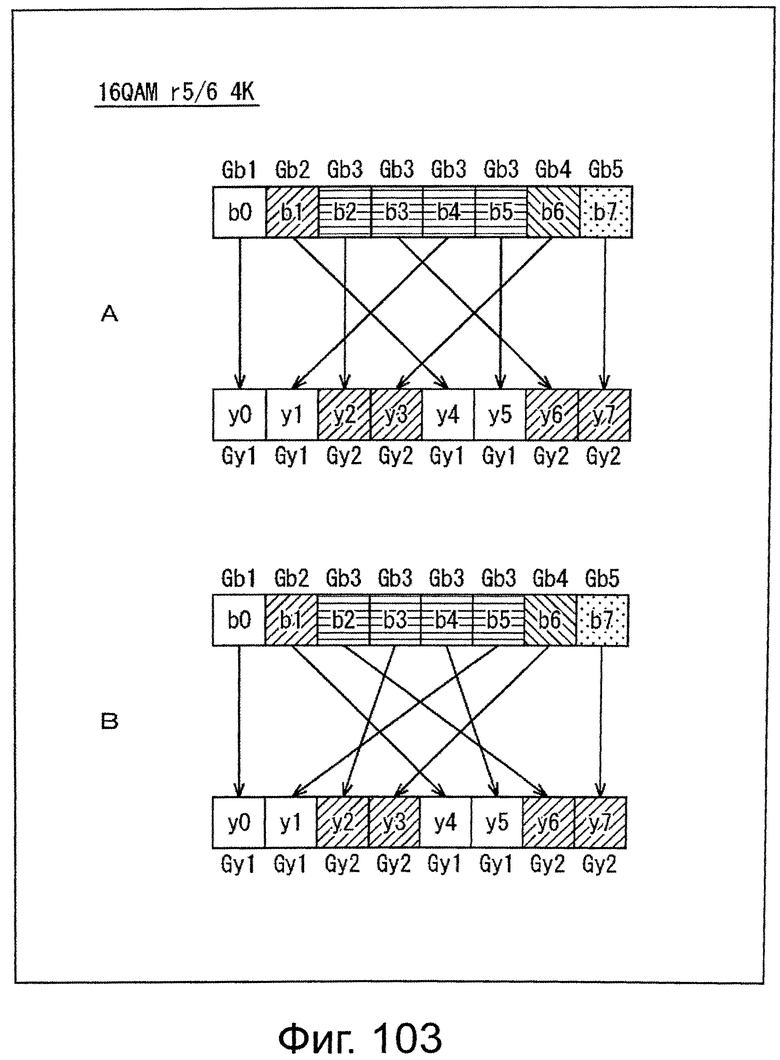

На фиг.103 показана схема, которая иллюстрирует взаимную замену кодовых битов в соответствии с правилом выделения в случае, когда код LDPC, имеющий длину кода 4 k и скорость кодирования 5/6, модулирован в соответствии с 16 QAM, и множитель b равен двум.

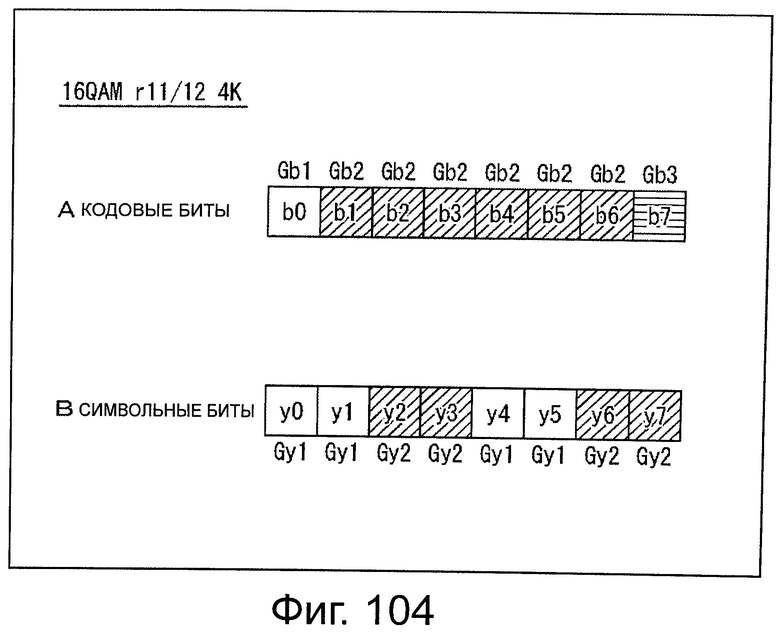

На фиг.104 показана схема, которая иллюстрирует группу кодовых битов и группу символьных битов в случае, когда код LDPC, имеющий длину кода 4 k и скорость кодирования 11/12, модулирован в соответствии с 16 QAM, и множитель b равен двум.

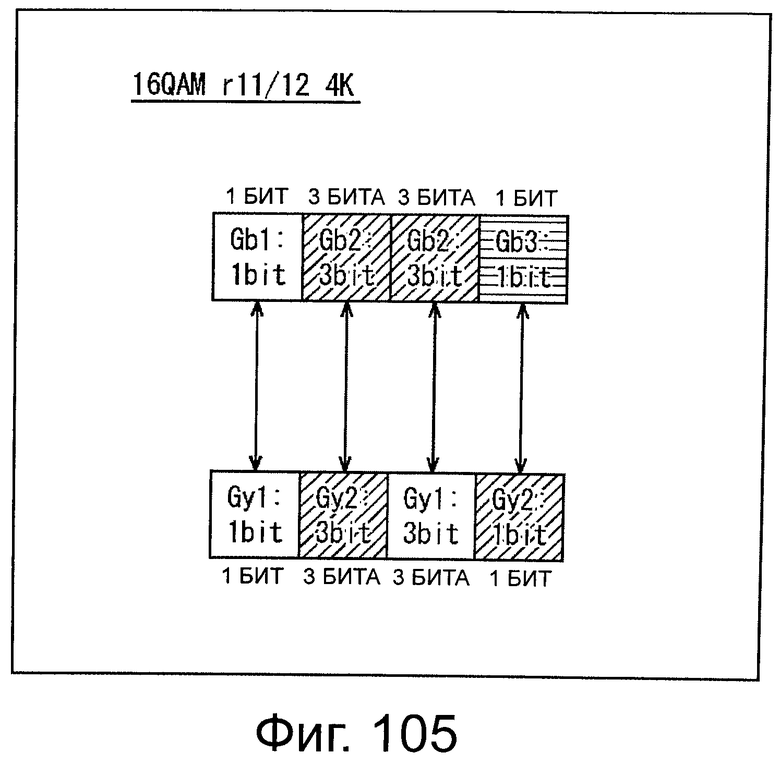

На фиг.105 показана схема, которая иллюстрирует правило выделения в случае, когда код LDPC, имеющий длину кода 4 k и скорость кодирования 11/12, модулирован в соответствии с 16 QAM, и множитель b равен двум.

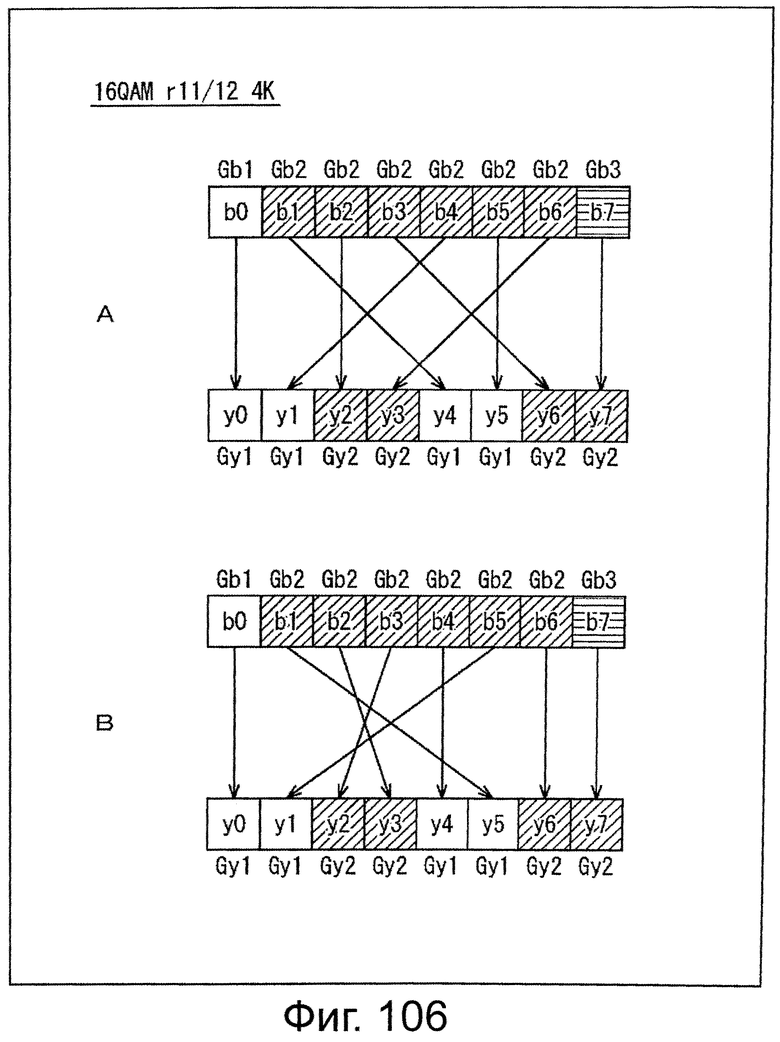

На фиг.106 показана схема, которая иллюстрирует взаимную замену кодовых битов в соответствии с правилом выделения в случае, когда код LDPC, имеющий длину кода 4 k и скорость кодирования 11/12, модулирован в соответствии с 16 QAM, и множитель b равен двум.

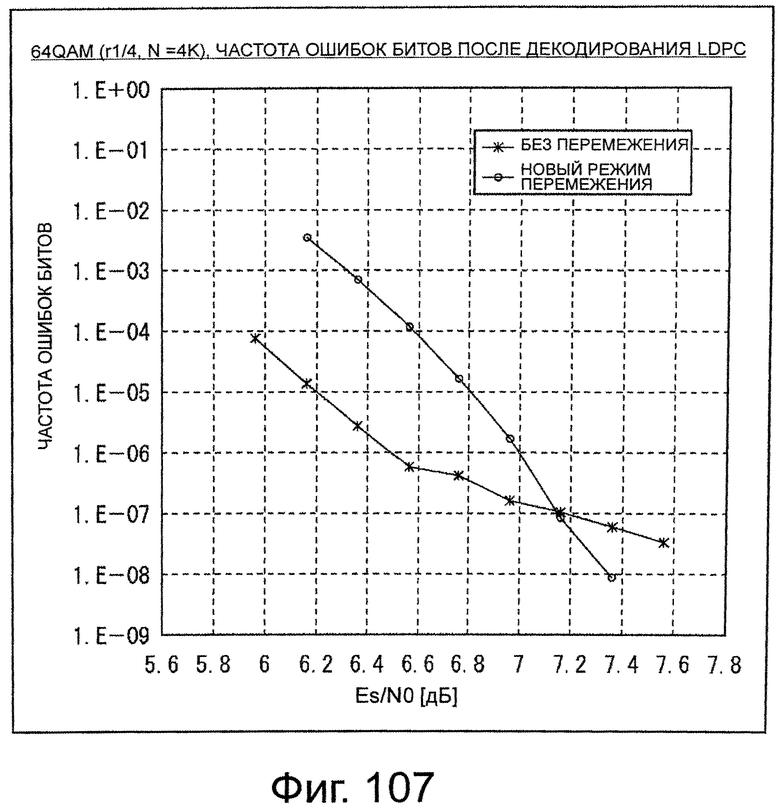

На фиг.107 показана схема, которая иллюстрирует результат моделирования BER в случае, когда код LDPC, имеющий длину кода 4 k и скорость кодирования 1/4, модулирован в соответствии с 64 QAM, и множитель b равен двум.

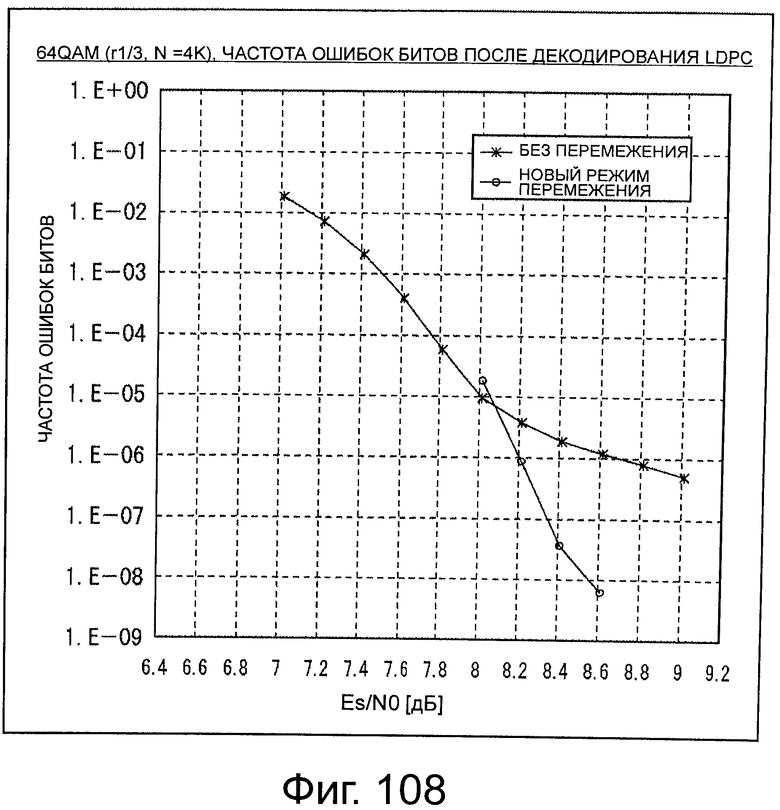

На фиг.108 показана схема, которая иллюстрирует результат моделирования BER в случае, когда код LDPC, имеющий длину кода 4 k и скорость кодирования 1/3, модулирован в соответствии с 64 QAM, и множитель b равен двум.

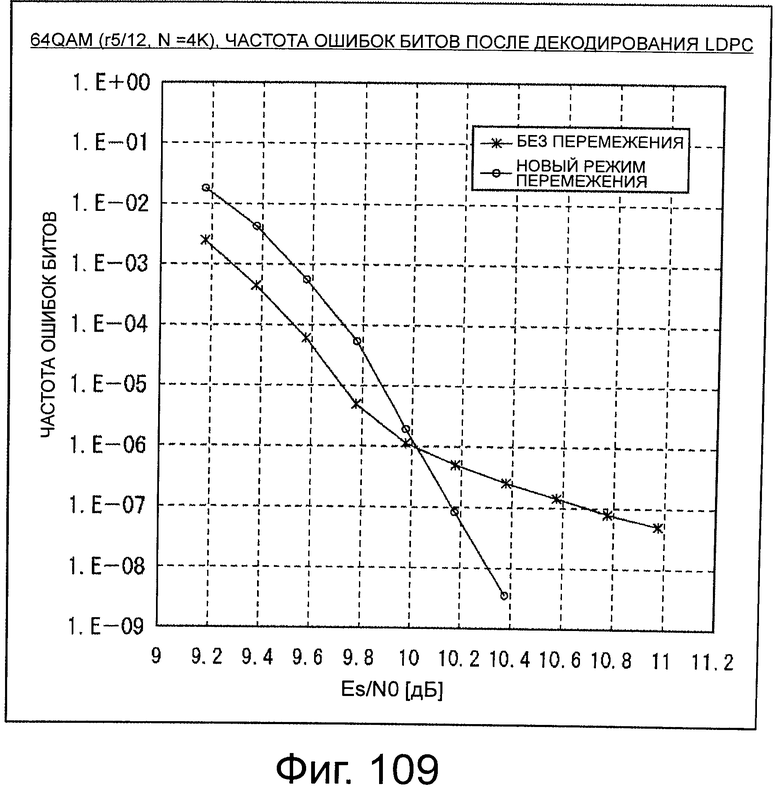

На фиг.109 показана схема, которая иллюстрирует результат моделирования BER в случае, когда код LDPC, имеющий длину кода 4 k и скорость кодирования 5/12, модулирован в соответствии с 64 QAM, и множитель b равен двум.

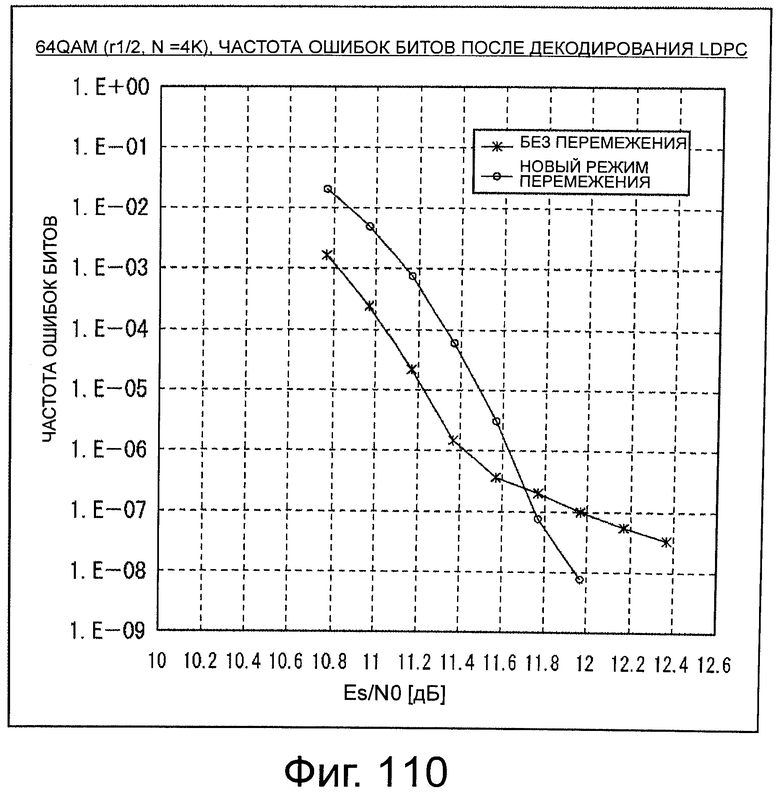

На фиг.110 показана схема, которая иллюстрирует результат моделирования BER в случае, когда код LDPC, имеющий длину кода 4 k и скорость кодирования 1/2, модулирован в соответствии с 64 QAM, и множитель b равен двум.

На фиг.111 показана схема, которая иллюстрирует результат моделирования BER в случае, когда код LDPC, имеющий длину кода 4 k и скорость кодирования 7/12, модулирован в соответствии с 64 QAM, и множитель b равен двум.

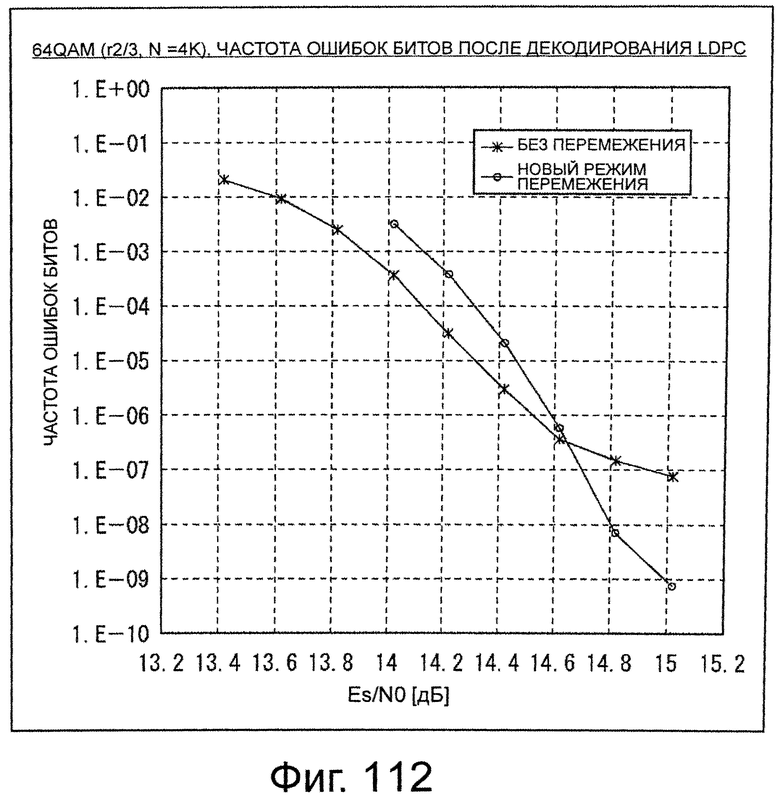

На фиг.112 показана схема, которая иллюстрирует результат моделирования BER в случае, когда код LDPC, имеющий длину кода 4 k и скорость кодирования 2/3, модулирован в соответствии с 64 QAM, и множитель b равен двум.

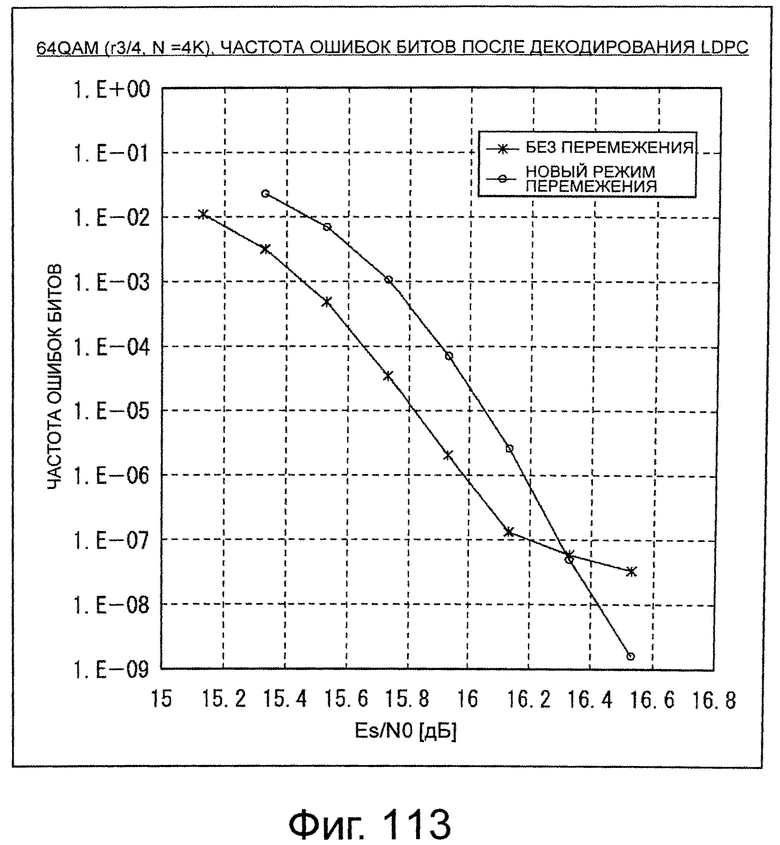

На фиг.113 показана схема, которая иллюстрирует результат моделирования BER в случае, когда код LDPC, имеющий длину кода 4 k и скорость кодирования 3/4, модулирован в соответствии с 64 QAM, и множитель b равен двум.

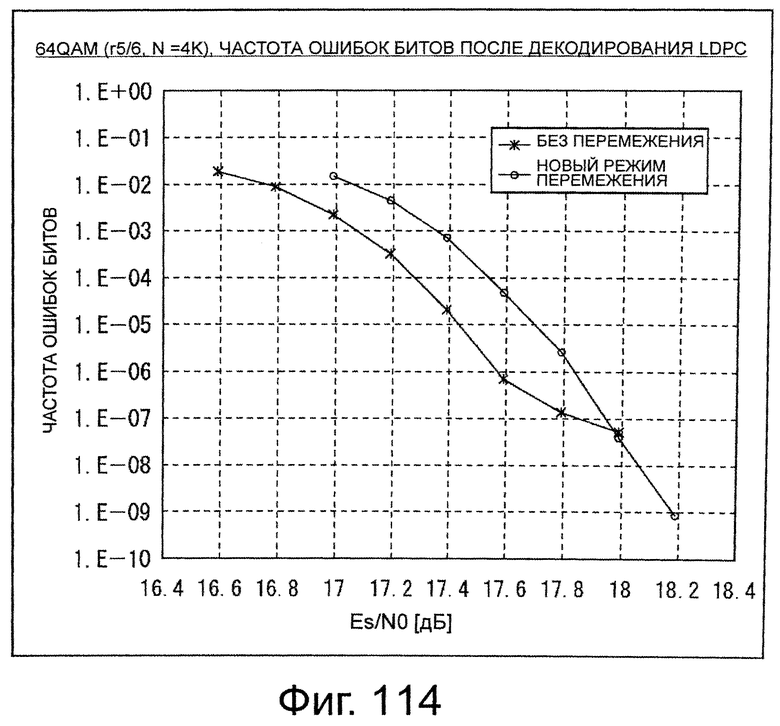

На фиг.114 показана схема, которая иллюстрирует результат моделирования BER в случае, когда код LDPC, имеющий длину кода 4 k и скорость кодирования 5/6, модулирован в соответствии с 64 QAM, и множитель b равен двум.

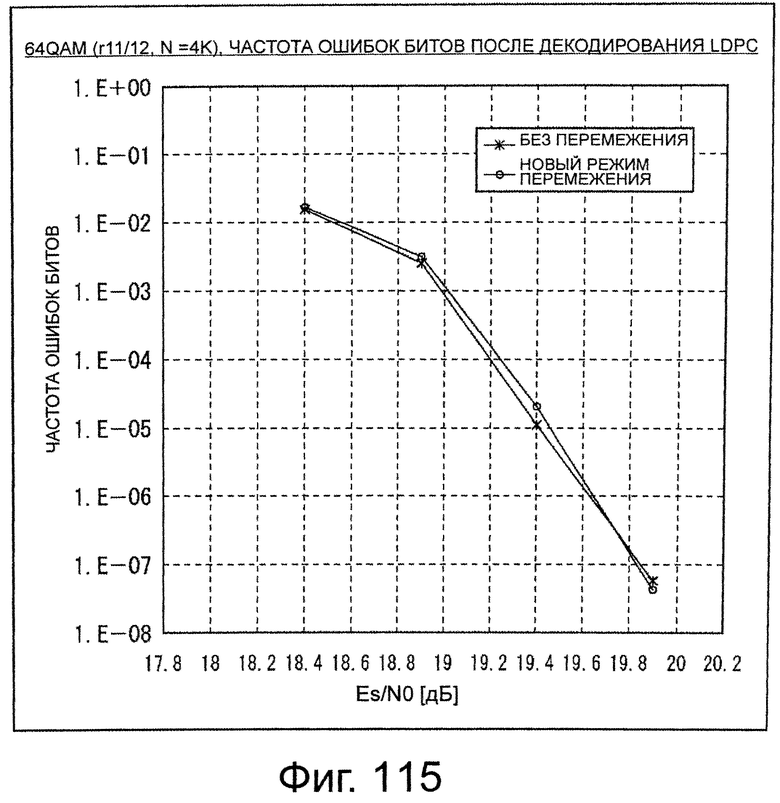

На фиг.115 показана схема, которая иллюстрирует результат моделирования BER в случае, когда код LDPC, имеющий длину кода 4 k и скорость кодирования 11/12, модулирован в соответствии с 64 QAM, и множитель b равен двум.

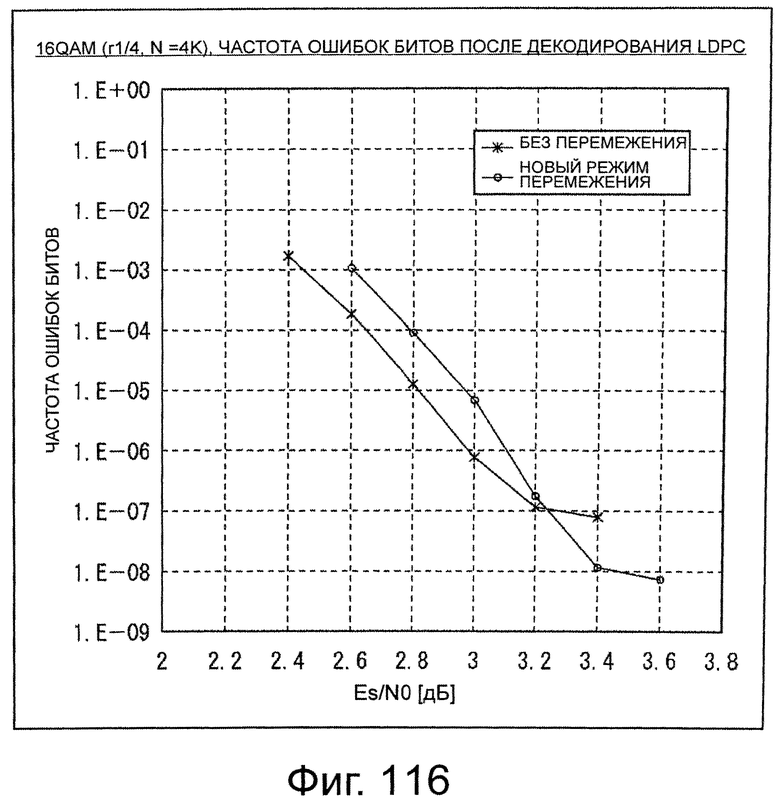

На фиг.116 показана схема, которая иллюстрирует результат моделирования BER в случае, когда код LDPC, имеющий длину кода 4 k и скорость кодирования 1/4, модулирован в соответствии с 16 QAM, и множитель b равен двум.

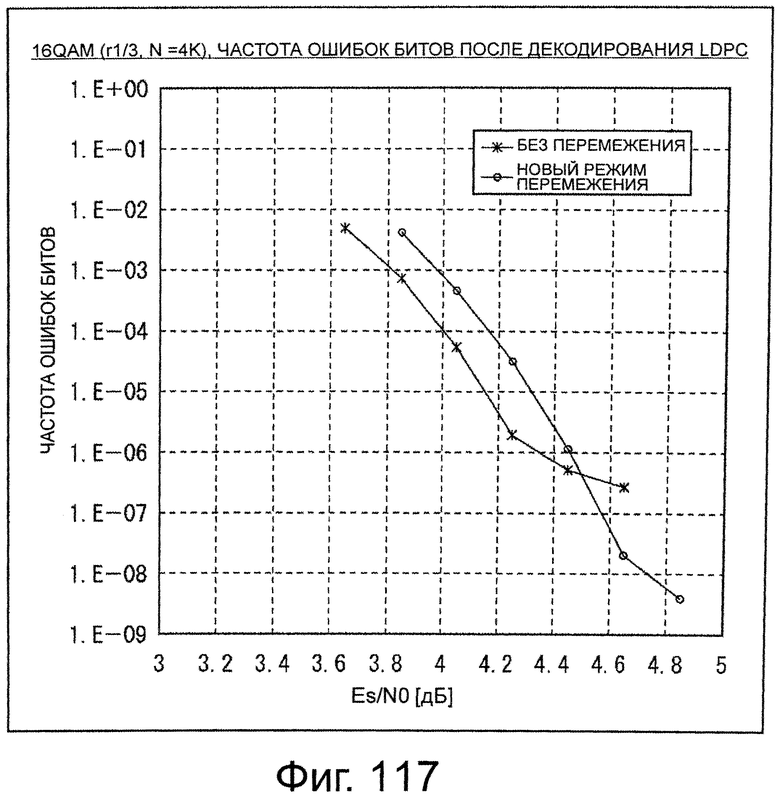

На фиг.117 показана схема, которая иллюстрирует результат моделирования BER в случае, когда код LDPC, имеющий длину кода 4 k и скорость кодирования 1/3, модулирован в соответствии с 16 QAM, и множитель b равен двум.

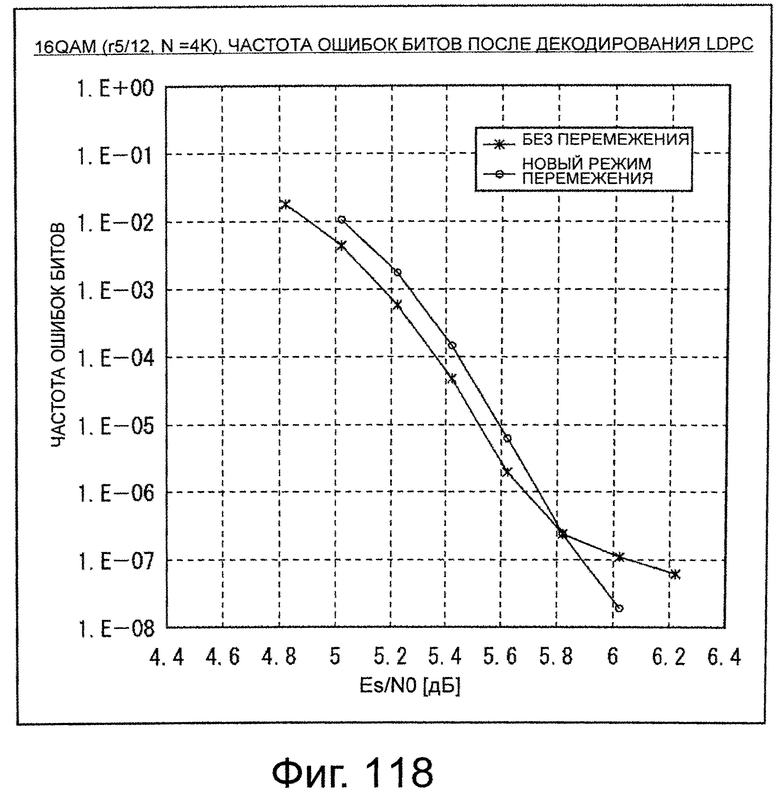

На фиг.118 показана схема, которая иллюстрирует результат моделирования BER в случае, когда код LDPC, имеющий длину кода 4 k и скорость кодирования 5/12, модулирован в соответствии с 16 QAM, и множитель b равен двум.

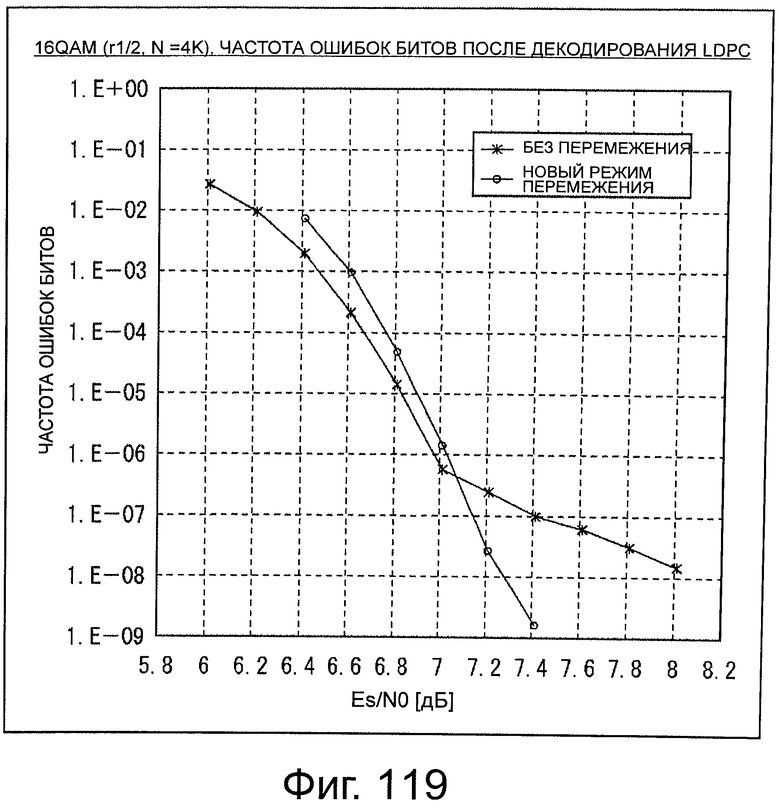

На фиг.119 показана схема, которая иллюстрирует результат моделирования BER в случае, когда код LDPC, имеющий длину кода 4 k и скорость кодирования 1/2, модулирован в соответствии с 16 QAM, и множитель b равен двум.

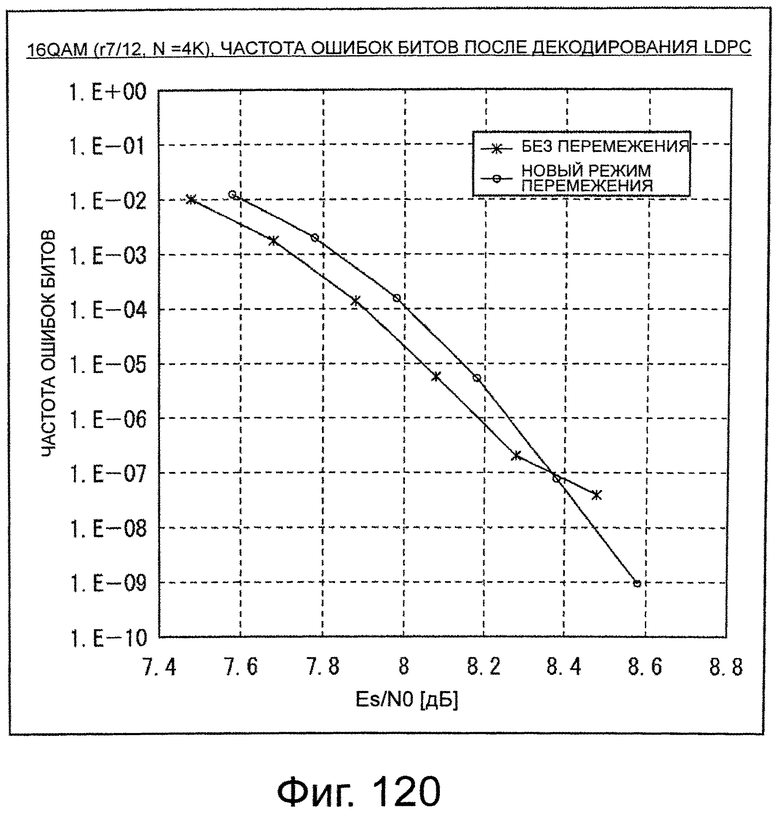

На фиг.120 показана схема, которая иллюстрирует результат моделирования BER в случае, когда код LDPC, имеющий длину кода 4 k и скорость кодирования 7/12, модулирован в соответствии с 16 QAM, и множитель b равен двум.

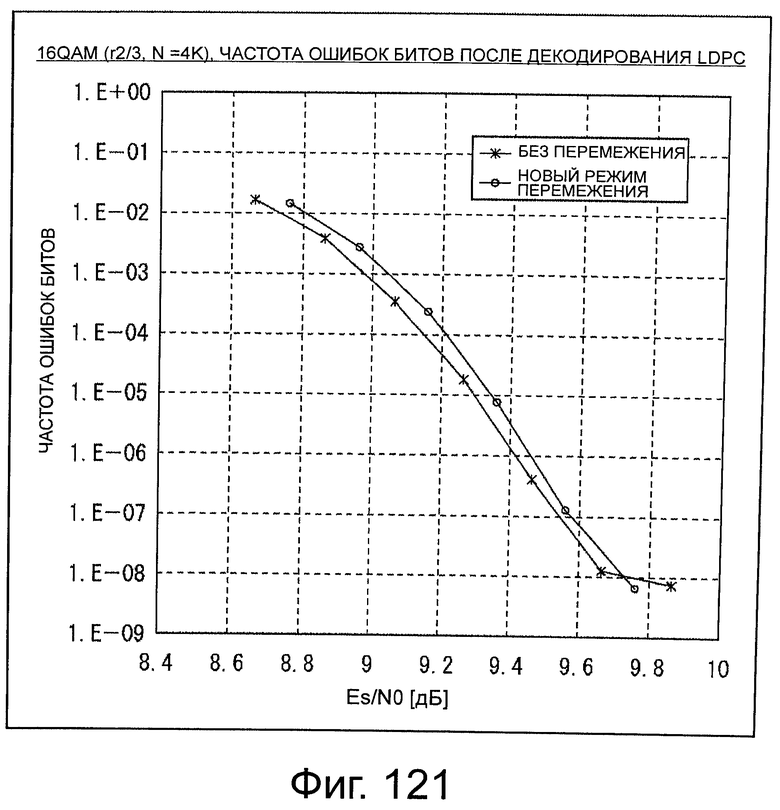

На фиг.121 показана схема, которая иллюстрирует результат моделирования BER в случае, когда код LDPC, имеющий длину кода 4 k и скорость кодирования 2/3, модулирован в соответствии с 16 QAM, и множитель b равен двум.

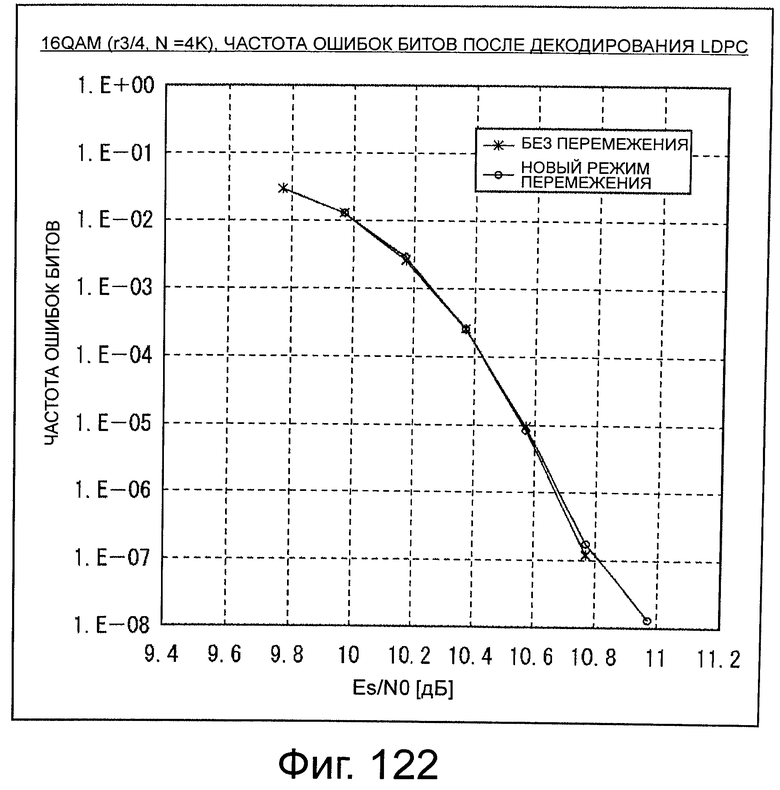

На фиг.122 показана схема, которая иллюстрирует результат моделирования BER в случае, когда код LDPC, имеющий длину кода 4 k и скорость кодирования 3/4, модулирован в соответствии с 16 QAM, и множитель b равен двум.

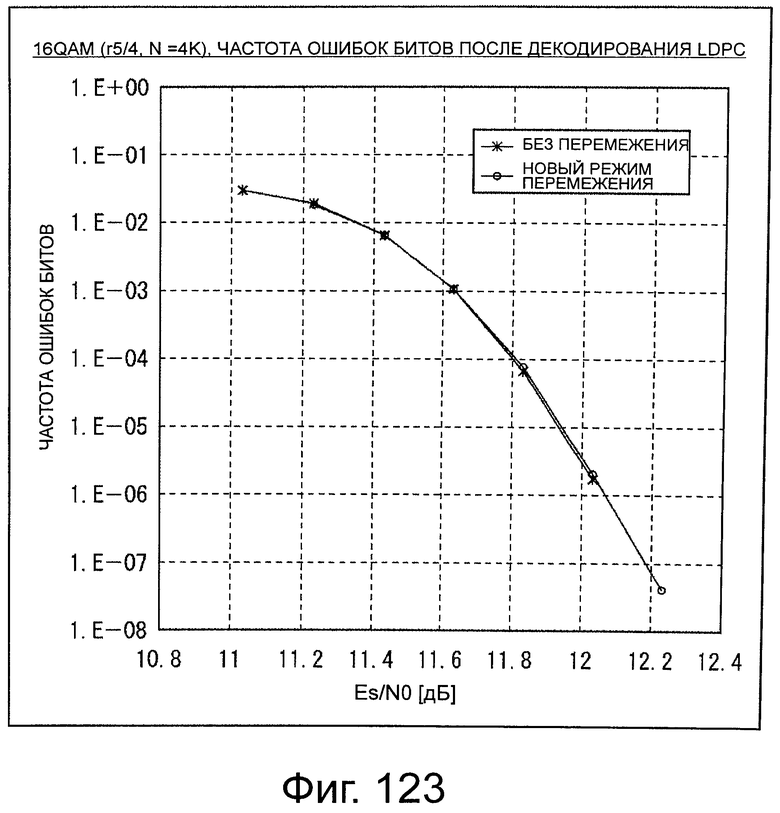

На фиг.123 показана схема, которая иллюстрирует результат моделирования BER в случае, когда код LDPC, имеющий длину кода 4 k и скорость кодирования 5/6, модулирован в соответствии с 16 QAM, и множитель b равен двум.

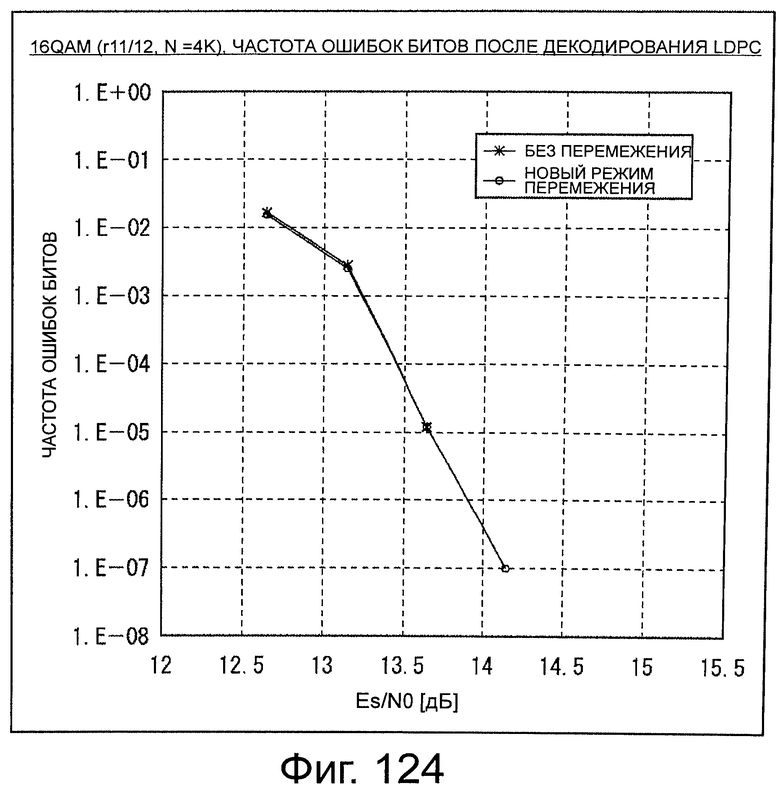

На фиг.124 показана схема, которая иллюстрирует результат моделирования BER в случае, когда код LDPC, имеющий длину кода 4 k и скорость кодирования 11/12, модулирован в соответствии с 16 QAM, и множитель b равен двум.

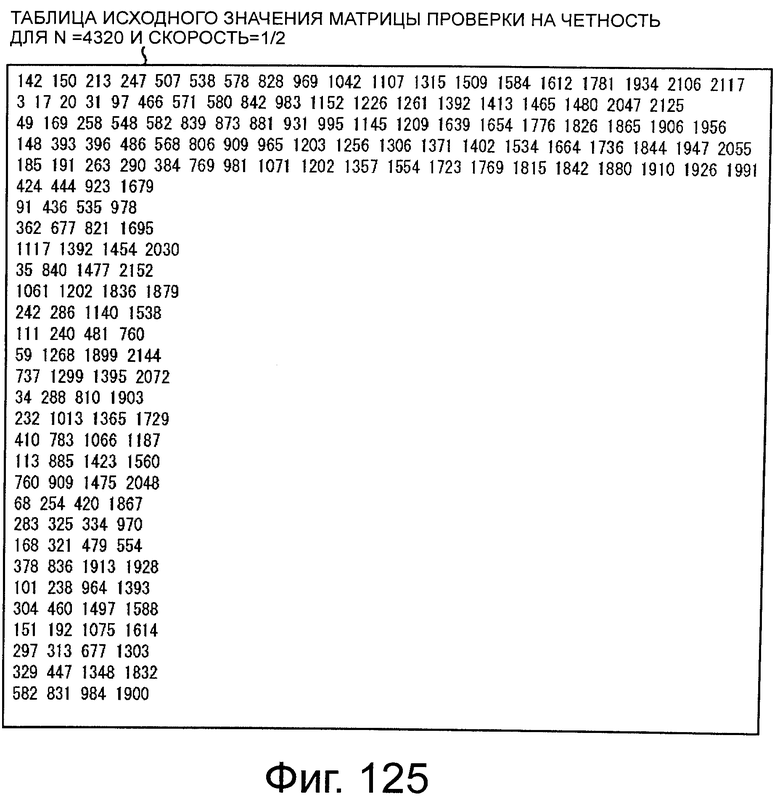

На фиг.125 показана схема, которая иллюстрирует пример таблицы исходного значения матрицы проверки на четность, имеющей скорость кодирования 1/2 и длину кода 4320.

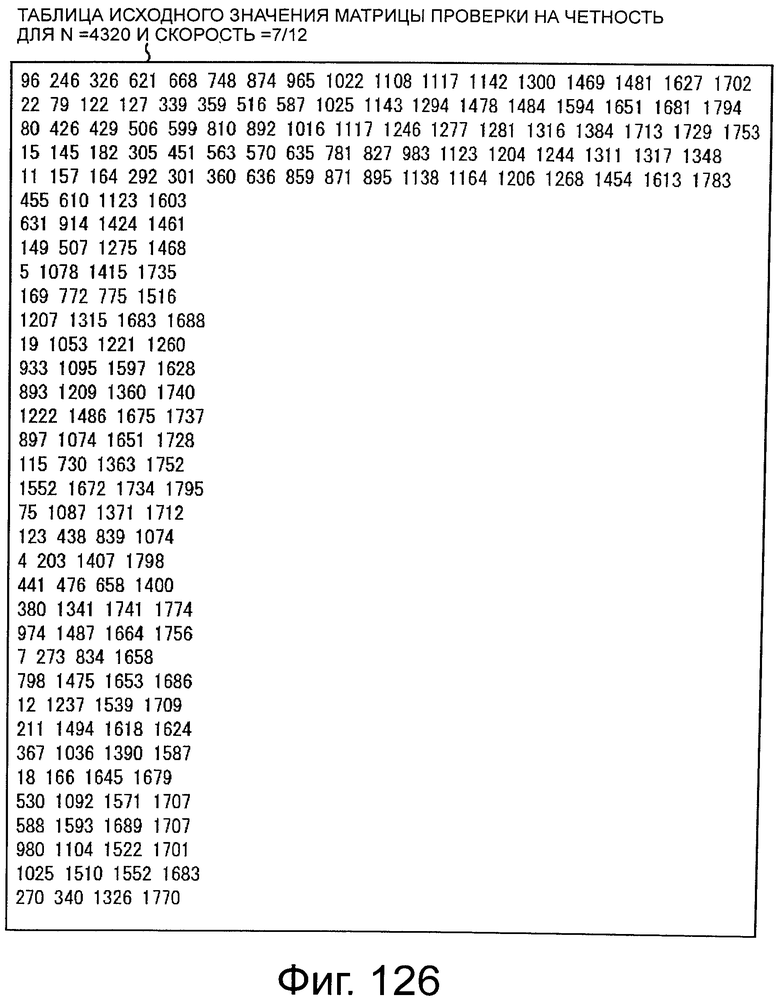

На фиг.126 показана схема, которая иллюстрирует пример таблицы исходного значения матрицы проверки на четность, имеющей скорость кодирования 7/12 и длину кода 4320.

На фиг.127 показана схема, которая иллюстрирует пример таблицы исходного значения матрицы проверки на четность, имеющей скорость кодирования 2/3 и длину кода 4320.

На фиг.128 показана схема, которая иллюстрирует пример таблицы исходного значения матрицы проверки на четность, имеющей скорость кодирования 3/4 и длину кода 4320.

На фиг.129 показана схема, которая иллюстрирует минимальную длину цикла и порог возможностей матрицы проверки на четность кода LDPC, имеющего длину кода 4320.

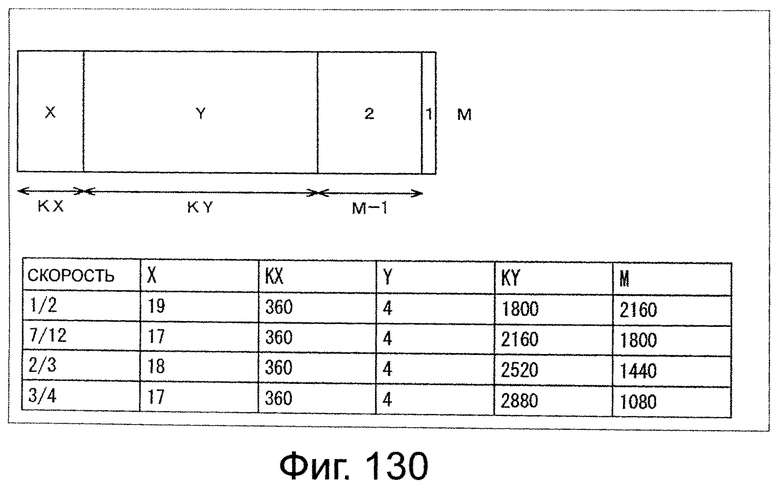

На фиг.130 показана схема, которая иллюстрирует матрицу проверки на четность кода LDPC, имеющего длину кода 4320.

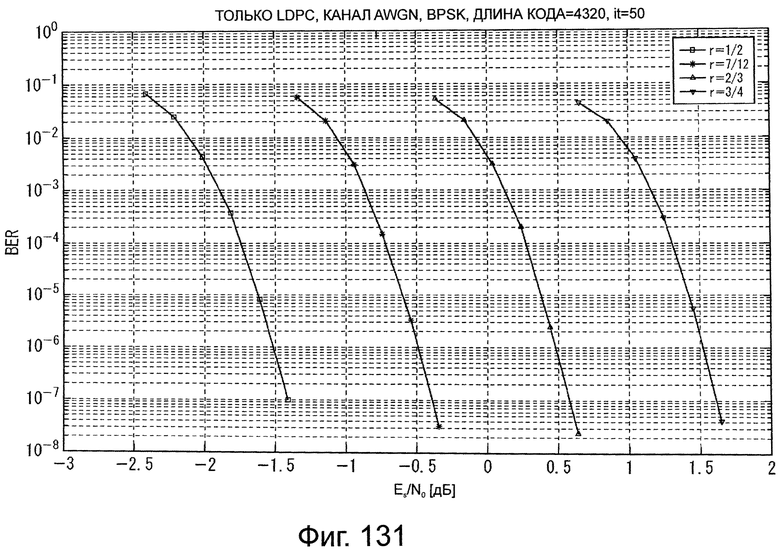

На фиг.131 показана схема, которая иллюстрирует результат моделирования BER.

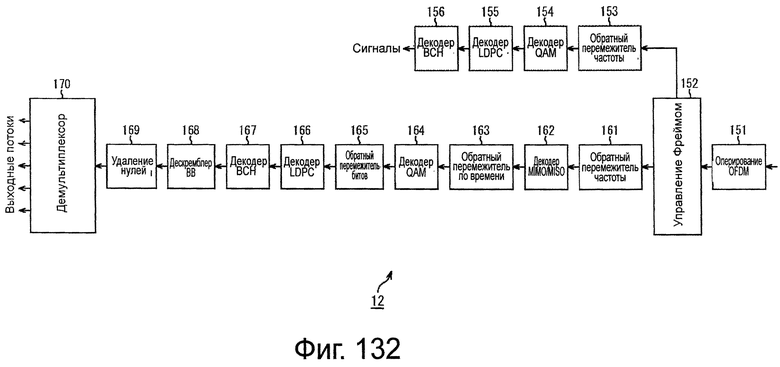

На фиг.132 показана блок-схема, представляющая пример конфигурации приемного устройства 12.

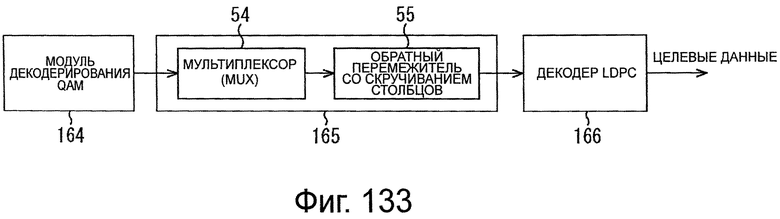

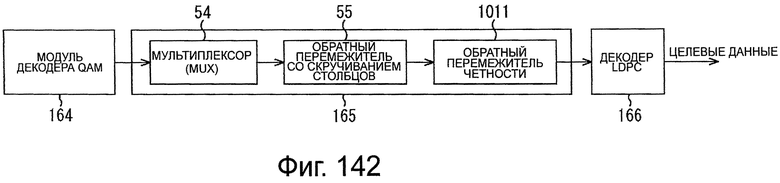

На фиг.133 показана блок-схема, представляющая пример конфигурации обратного перемежителя 165 битов.

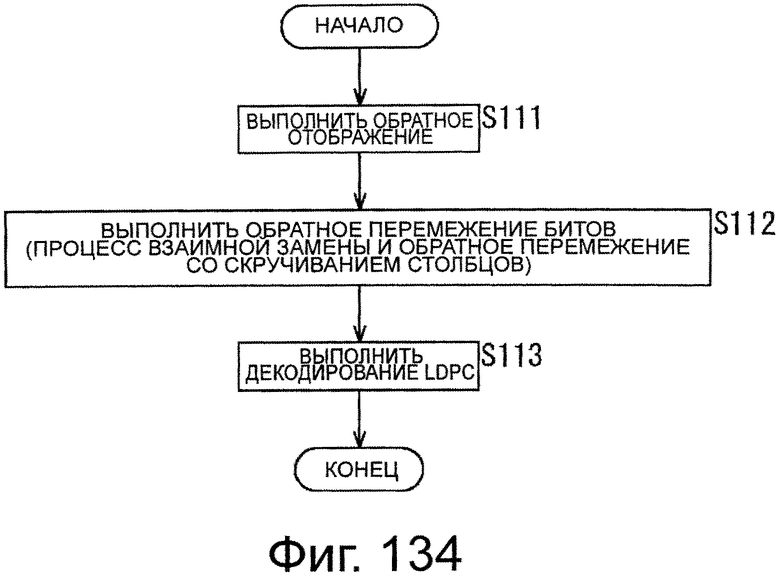

На фиг.134 показана блок-схема последовательности операций процесса, который выполняет декодер QAM 164, обратный перемежитель 165 битов и декодер LDPC 166.

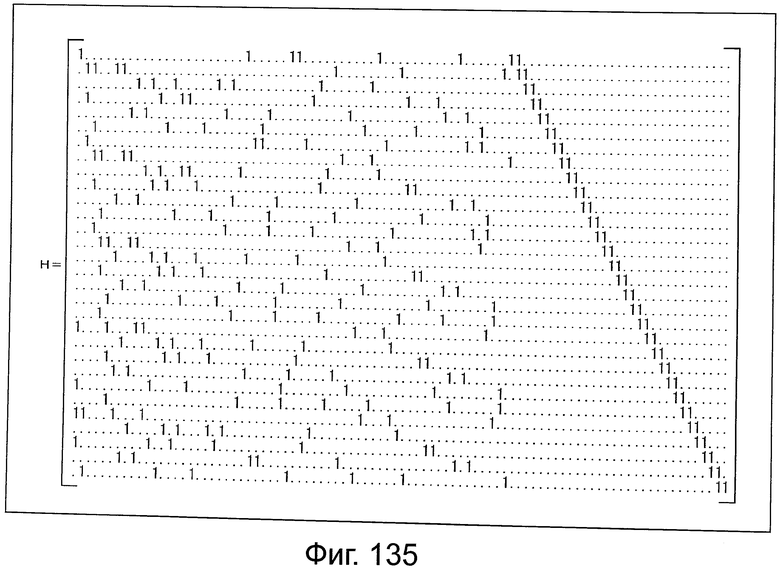

На фиг.135 показана схема, которая иллюстрирует пример матрицы проверки на четность кода LDPC.

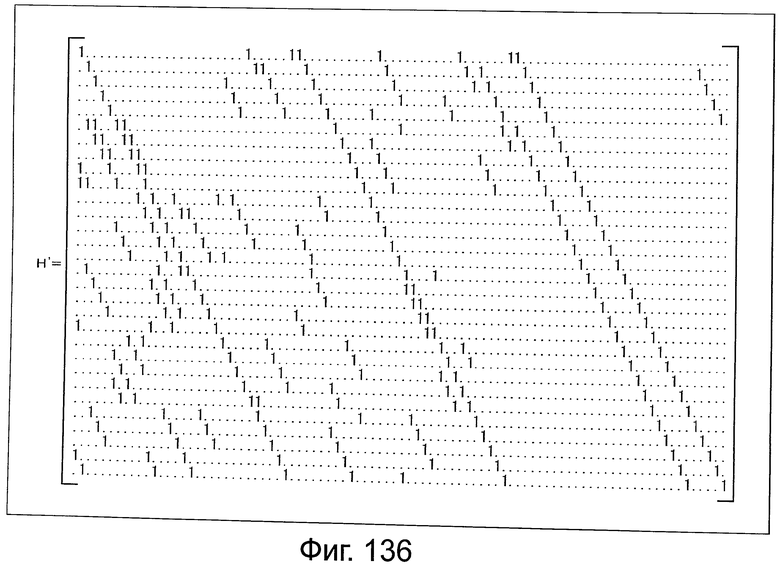

На фиг.136 показана схема, которая иллюстрирует матрицу (преобразованную матрицу проверки на четность), полученную в результате замены строки и замены столбца матрицы проверки на четность.

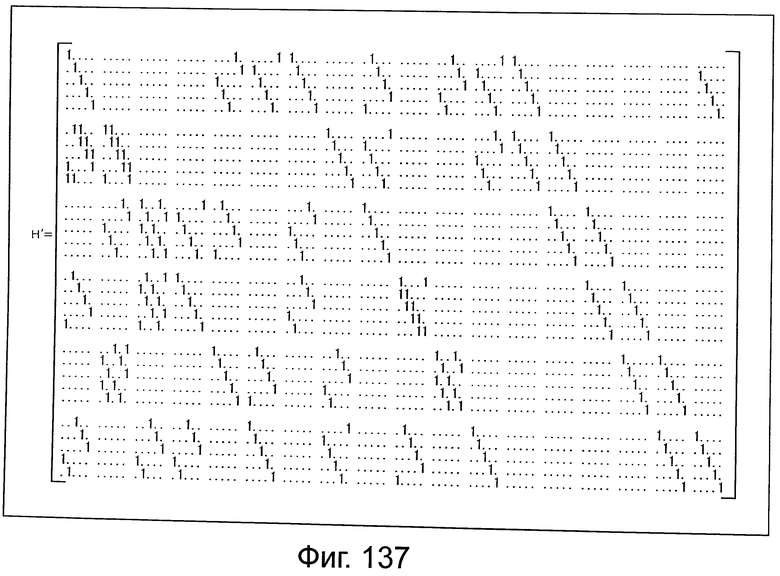

На фиг.137 показана схема, которая иллюстрирует преобразованную матрицу проверки на четность, которая разделена на модули 5х5.

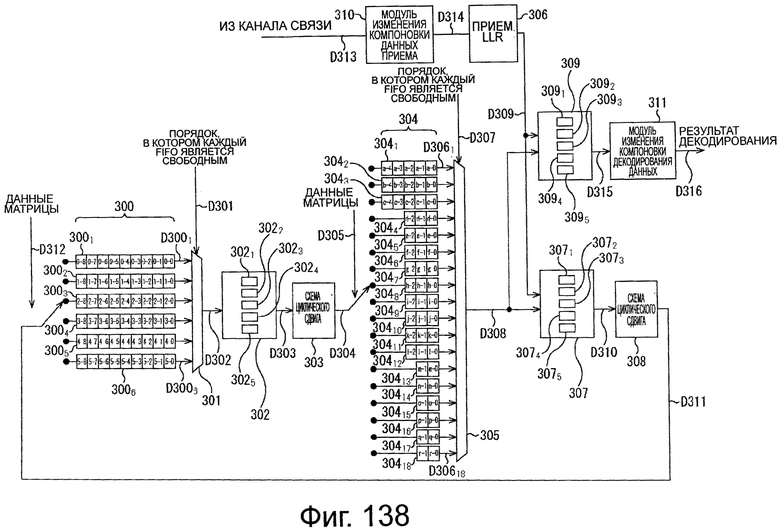

На фиг.138 показана блок-схемой, которая иллюстрирует пример конфигурации декодера, который выполняет все вычисления узла Р полностью.

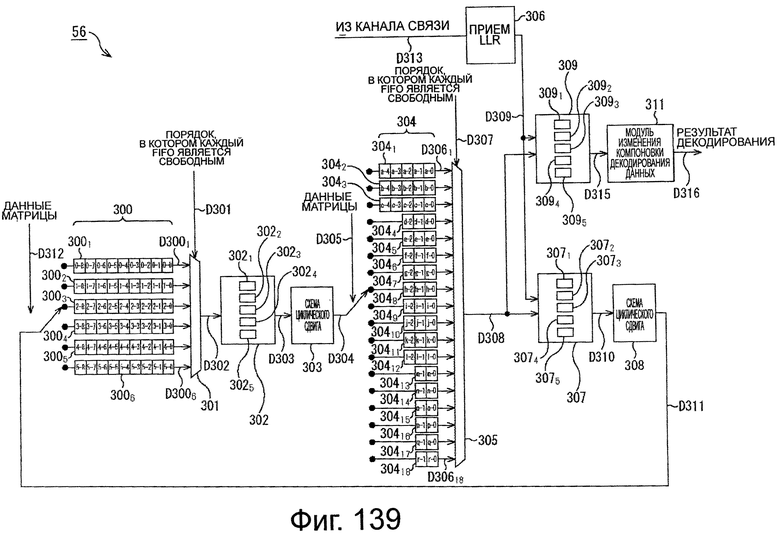

На фиг.139 показана блок-схема, представляющая пример конфигурации декодера LDPC 166.

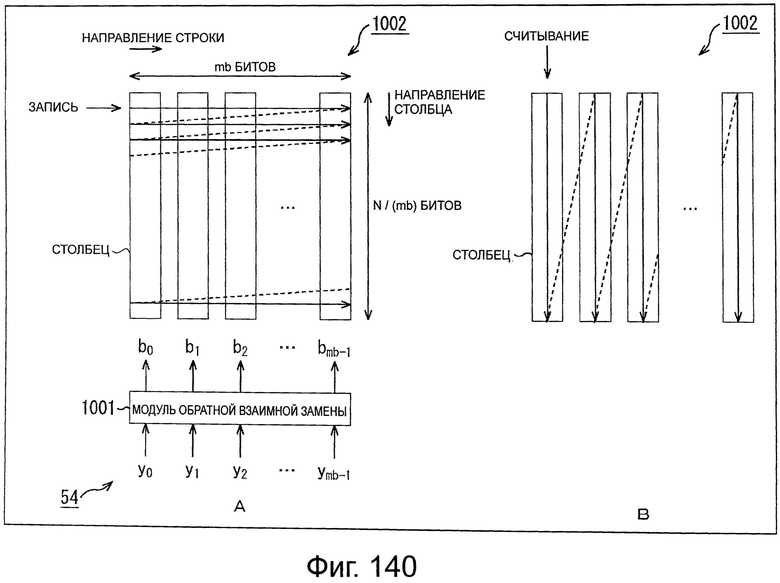

На фиг.140 показана схема, которая иллюстрирует процесс мультиплексора 54, который составляет обратный перемежитель 165 битов.

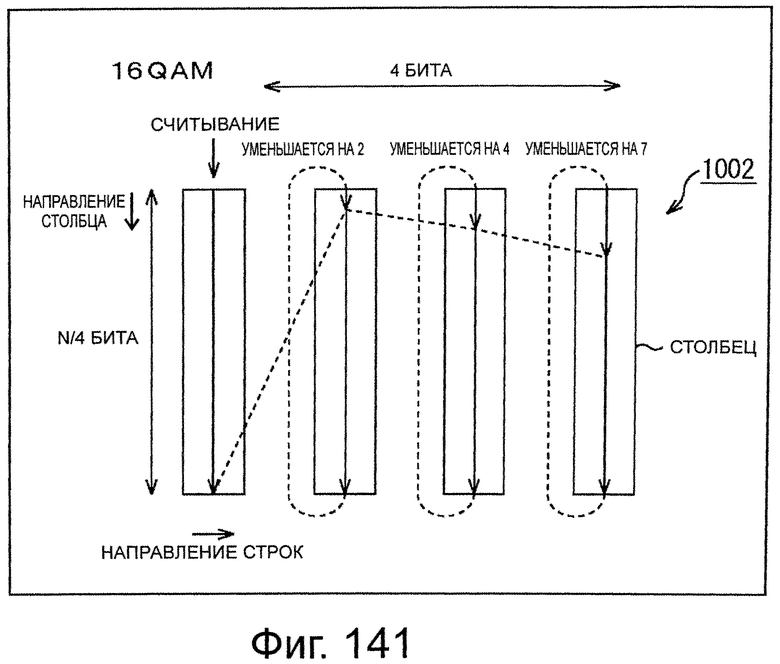

На фиг.141 показана схема, которая иллюстрирует процесс обратного перемежителя 55 со скручиванием столбцов.

На фиг.142 показана блок-схема, представляющая другой пример конфигурации обратного перемежителя 165 битов.

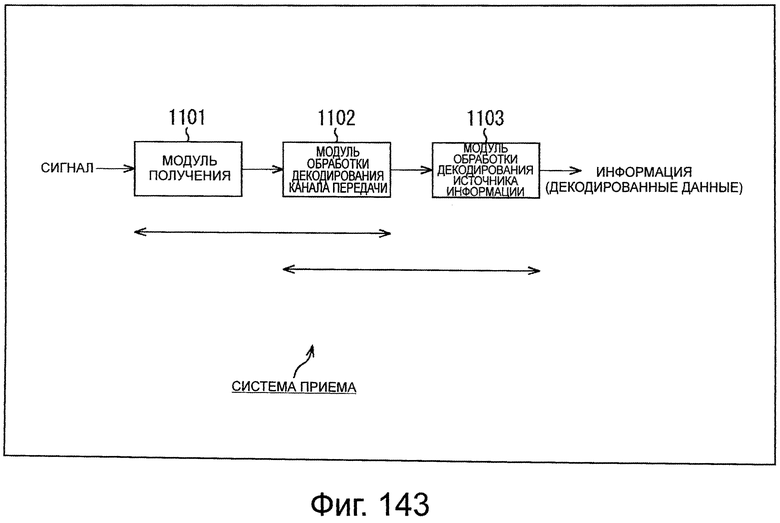

На фиг.143 показана блок-схема, представляющая первый пример конфигурации системы приема, в которой может быть применено приемное устройство 12.

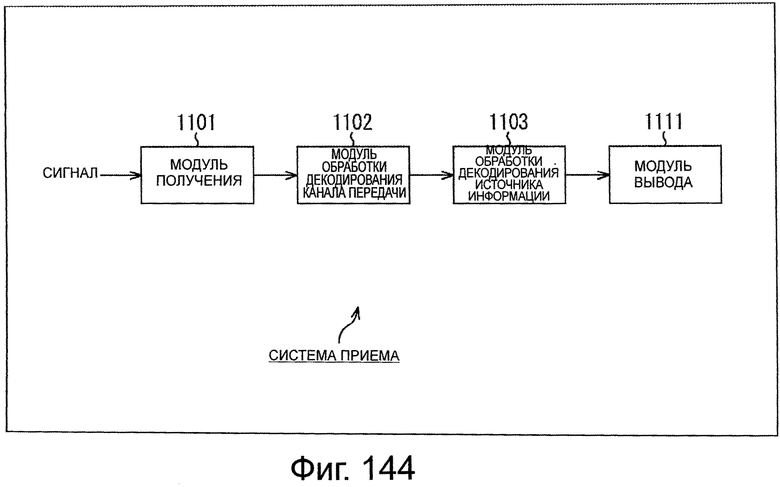

На фиг.144 показана блок-схема, представляющая второй пример конфигурации системы приема, в которой может быть применено приемное устройство 12.

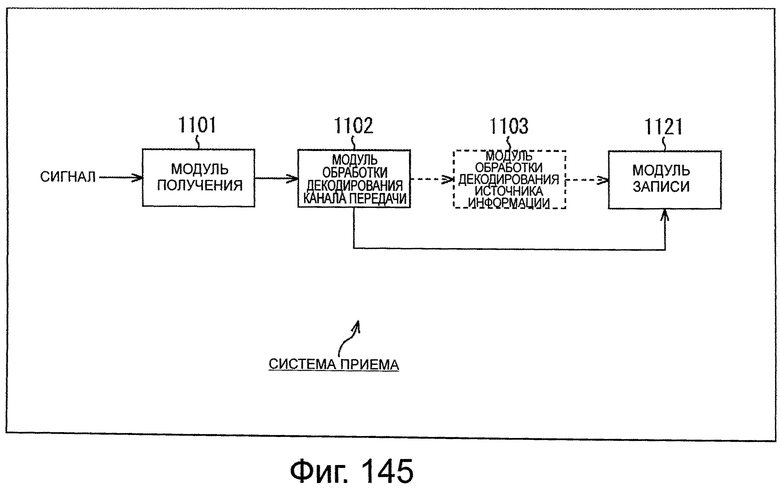

На фиг.145 показана блок-схема, представляющая третий пример конфигурации системы приема, в которой может быть применено приемное устройство 12.

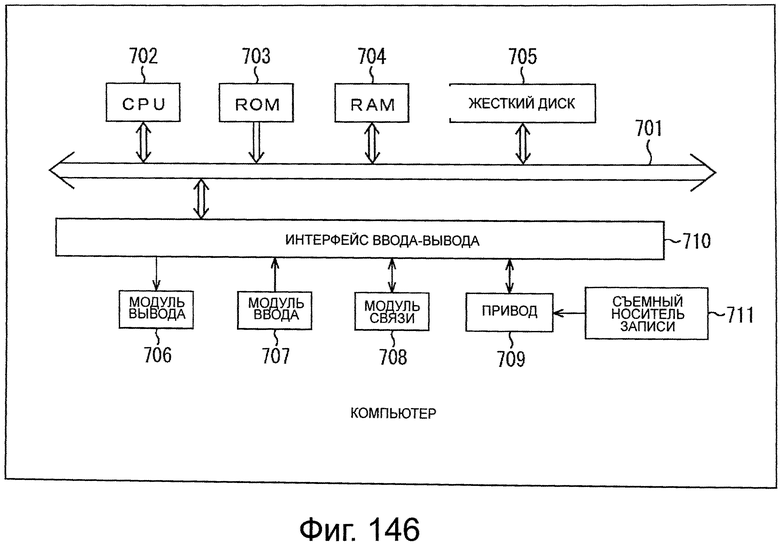

На фиг.146 показана блок-схема, представляющая пример конфигурации компьютера в соответствии с вариантом осуществления настоящего изобретения.

Осуществление изобретения

Пример конфигурации системы передачи в соответствии с настоящим изобретением

На фиг.7 иллюстрируется пример конфигурации системы передачи (здесь система представляет собой логическое объединение множества устройств, независимо от того, расположены или нет устройства в соответствии с этими конфигурациями в одном и том же корпусе), в соответствии с вариантом осуществления настоящего изобретения.

На фиг.7 система передачи выполнена, как устройство 11 передачи и устройство 12 приема.

[0066] Устройство 11 передачи посылает (выполняет широковещательную передачу) (передает) программу, которая специально используется для фиксированного оконечного устройства или мобильного оконечного устройства. Другими словами, устройство 11 передачи, например, кодирует целевые данные, которые представляют собой цель передачи, такие как видеоданные или аудиоданные, как программу, которая специально используется для фиксированного оконечного устройства или мобильного оконечного устройства, в коде LDPC и передает код LDPC, например, через канал 13 передачи данных, который представляет собой наземную волну.

Устройство 12 приема, например, представляет собой мобильное оконечное устройство, принимает код LDPC, который передают от устройства 11 передачи через канал 13 связи, декодирует код LDPC в целевые данные и выводит целевые данные.

Здесь код LDPC, который используется в системе передачи, показанной на фиг.7, известен, как канал связи с чрезвычайно высокими возможностями в отношении AWGN (аддитивный белый гауссов шум).

Однако, в канале 13 связи наземной волны и т.п., возникает случай, когда появляется пакет ошибок или удаление данных. Например, в системе OFDM (система разделения с ортогональным частотным мультиплексированием), в среде с многолучевым распространением, в которой D/U (отношение желательного к нежелательному) составляет 0 дБ (мощность нежелательного = эхо-сигналу, который имеет такую же мощность, как и мощность желательного = основному каналу), возникает случай, когда мощность конкретного символа равна нулю (удаление) в соответствии с задержкой эхо-сигнала (другой канал распространения, кроме основного канала).

Кроме того, также при дрожании сигнала (канал связи, к которому добавляется эхо-сигнал или допплеровская частота с задержкой, равной нулю), в случае, когда D/U равно 0 дБ, возникает случай, когда мощность всех символов OFDM в определенные моменты времени равна нулю (удаление), из-за допплеровской частоты.

Кроме того, возникает случай, когда возникает пакет ошибок из-за состояния разводки проводов, сформированной в модуле приема (не показан на чертеже) на стороне устройства 12 приема, например в антенне, которая принимает сигнал, переданный устройством 11 передачи на устройство 12 приема, или нестабильности мощности устройства 12 приема.

В то же время, при декодировании кода LDPC, в столбце матрицы Н проверки на четность и, кроме того, в переменном узле, который соответствует кодовому биту для кода LDPC, как показано на фиг.5, описанной выше, выполняется вычисление переменного узла, представленного в Уравнении (1), который сопровождается добавлением кодового бита (принятое значение u0i) кода LDPC, и, соответственно, когда возникает ошибка в кодовом бите, который используется для вычисления переменного узла, точность запрашиваемого сообщения уменьшается.

Кроме того, при декодировании кода LDPC, в проверочном узле, вычисление проверочного узла, представленное в Уравнении (7), выполняют, используя сообщения, полученные в переменных узлах, соединенных с проверочным узлом, и, соответственно, когда количество проверочных узлов, имеющих ошибки (включая в себя удаление), которые возникают одновременно во множестве переменных узлов (кодовые биты кода LDPC, которые соответствуют им), соединенных с ним, увеличивается, возможность декодирования ухудшается.

Другими словами, например, когда два или больше переменных узла, соединенных с проверочным узлом, удаляют одновременно, проверочный узел возвращает сообщение равной вероятности для вероятности значения, равного нулю, и вероятности значения единица во все переменные узлы. В таком случае проверочный узел, который возвращает сообщение равной вероятности, не вносит свой вклад в процесс декодирования единицы (набор единиц при вычислении переменного узла и вычислении проверочного узла), и, в результате, количество повторений процесса декодирования должно быть велико, в результате чего способность декодирования ухудшается, и потребление энергии в устройстве 12 приема, которое декодирует код LDPC, увеличивается.

Поэтому, в системе передачи, показанной на фиг.7, улучшается сопротивление пакетам ошибок или удалению, в то время как возможности в канале передачи данных AWGN поддерживаются.

Пример конфигурации устройства 11 передачи

На фиг.8 показана блок-схема, которая иллюстрирует пример конфигурации устройства 11 передачи, показанного на фиг.7.

В устройстве 11 передачи, один или больше входных потоков, в виде целевых данных, подают на блок адаптации режима/мультиплексор 111.

Блок адаптации режима/мультиплексор 111 выполняет выбор режима и мультиплексирование одного или больше входных потоков, подаваемых на него, и подает данные, полученные в результате, на заполнитель 112.

Заполнитель 112 выполняет заполнение нулями (вставку нулей), которое необходимо для данных, подаваемых блоком адаптации режима/мультиплексором 111, и подает данные, полученные в результате этого, на скремблер 113 ВВ.

Скремблер 113 ВВ выполняет процесс диффузии энергии для данных, подаваемых заполнителем 112, и подает полученные в результате данные, на кодер 114 ВСН.

Кодер 114 ВСН выполняет кодирование ВСН для данных, поданных скремблером 113 ВВ, и подает данные, полученные в результате этого, на кодер 115 LDPC, как данные цели LDPC, которые представляют собой цель для кодирования LDPC.

Кодер 115 LDPC выполняет кодирование LDPC для целевых данных LDPC, подаваемых кодером 114 ВСН, в соответствии с матрицей проверки на четность, в которой матрица четности, которая представляет собой часть кода LDPC, соответствующую битам четности, имеет структуру лестницы и выводит код LDPC, в котором целевые данные LDPC установлены, как биты информации.

Другими словами, кодер 115 LDPC выполняет кодирование LDPC для кодирования целевых данных LDPC в коде LDPC, таком как код LDPC, например, определенном в стандарте DVB-T.2, и выводит полученный код LDPC, в качестве результата кодирования.

Здесь, в стандарте DVB-T.2 используется код LDPC, определенный в стандарте DVB-S.2, за исключением случая, когда длина кода составляет 16200 битов, и скорость кодирования составляет 3/5. Код LDPC, определенный в стандарте DVB-T.2, представляет собой код IRA (накопление с нерегулярным повтором), и матрица четности для матрицы проверки на четность кода LDPC имеет структуру лестницы. Матрица четности и структура лестницы будут описаны ниже. Код IRA, например, описан в "Irregular Repeat-Accumulate Codes," H. Jin, A. Khandekar, and R.J. McEliece, in Proceedings of second International Symposium on Turbo codes and Related Topics, pp.1-8, Sept. 2000.

Код LDPC, который выводят из кодера 115 LDPC, подают в перемежитель 116 битов.

Перемежитель 116 битов выполняет перемежение битов, которое будет описано ниже, для кода LDPC, подаваемого из кодера 115 LDPC, и подает код LDPC после перемежения битов в кодер 117 QAM.

Кодер 117 QAM выполняет ортогональную модуляцию (многозначную модуляцию), путем преобразования кода LDPC, подаваемого из перемежителя 116 битов, в точку сигнала ортогональной модуляции, которая представляет один символ в единицах (единичный символ) кодовых битов для кода LDPC одного бита или больше.

Другими словами, кодер 117 QAM выполняет ортогональную модуляцию, путем преобразования кода LDPC, подаваемого из перемежителя 116 битов, в точку сигнала, определенную в режиме модуляции, используемом для выполнения ортогональной модуляции кода LDPC на плоскости IQ (созвездие IQ) определенной осью i, представляющей компонент i, который является синфазным с несущей волной, и осью Q, представляющей компонент Q, ортогональный несущей волне.

Здесь в качестве режимов модуляции для ортогональной модуляции, выполняемой кодером 117 QAM, например, присутствуют режимы модуляции, которые включают в себя режимы модуляции, определенные в стандарте DVB-T, другими словами, например, существует QPSK. (квадратурная манипуляция с фазовым сдвигом фаз), 16 QAM (квадратурная амплитудная модуляция), 64 QAM, 256 QAM, 1024 QAM и 4096 QAM. В кодере 117 QAM, режим модуляции, например, для ортогональной модуляции установлен заранее, например, в соответствии с оперированием оператора устройства 11 передачи. Кроме того, в кодере 117 QAM, может быть выполнена, например, 4 РАМ (импульсная амплитудная модуляция) и любой другой тип ортогональной модуляции.

Данные (символы, преобразованные в точку сигнала), полученные при обработке, выполняемой в кодере 117 QAM, подают на перемежитель 118 по времени.

Перемежитель 118 по времени выполняет перемежение по времени (перемежение в направлении времени) в единицах символов для данных (символов), подаваемых от кодера 117 QAM, и подает данные, полученные в результате, на кодер 119 MISO/MIMO.

Кодер 119 MISO/MIMO выполняет временно-пространственное кодирование данных (символов), подаваемых перемежителем 118 по времени и подает полученные в результате данные на перемежитель 120 частоты.

Перемежитель 120 частоты выполняет перемежение частоты (перемежение в направлении частоты) в единицах символов для данных (символов), подаваемых из кодера 119 MISO/MIMO, и подает полученные в результате данные на модуль 131 построения фрейма/выделения ресурсов.

В то же время, например, данные управления (сигналы), используемые для управления передачей, такие как преамбула, называемая L1 и т.п., подают на кодер 121 ВСН.

Кодер 121 ВСН выполняет кодирование ВСН для данных управления, подаваемых на него, аналогично кодеру 114 ВСН, и подает данные, полученные в результате этого, на кодер 122 LDPC.

Кодер 122 LDPC выполняет кодирование LDPC для данных, подаваемых от кодера 121 ВСН, как для целевых данных LDPC, аналогично кодеру 115 LDPC, и подает код LDPC, полученный в результате этого, на кодер 123 QAM.

Кодер 123 QAM, аналогично кодеру 117 QAM, преобразуют код LDPC, поданный от кодера 122 LDPC, в единицах (в единицах символов) кодовых битов одного или больше битов кода LDPC в точку сигнала ортогональной модуляции, представляющую один символ, выполняет ортогональную модуляцию для полученных в результате данных, и подает данные (символы), полученные в результате этого, на перемежитель 124 частоты.

Перемежитель 124 частоты, аналогично перемежителю 120 частоты, выполняет перемежение частоты для данных (символов), подаваемых кодером 123 QAM в единицах символов, и подает полученные в результате данные на модуль 131 построения фрейма/выделения ресурсов.

Модуль 131 построения фрейма/выделения ресурсов вставляет пилотные символы в необходимых положениях данных (символов), подаваемых перемежителями 120 и 124 частоты, конфигурирует фрейм, сконфигурированный по символам с заданным количеством данных, используя полученные в результате данные (символы), и подает этот фрейм на модуль 132 генерирования OFDM.

Модуль 132 генерирования OFDM генерирует сигнал OFDM, соответствующий фрейму, подаваемому модулем 131 построения фрейма/выделения ресурсов на основе фрейма, и передает сигнал OFDM через канал 13 передачи данных (фиг.7).

На фиг.9 иллюстрируется пример конфигурации перемежителя 116 битов, показанного на фиг.8.

Перемежитель 116 битов представляет собой устройство обработки данных, которое выполняет перемежение данных и выполнено на основе перемежителя 23 четности, перемежителя 24 со скручиванием столбцов и демультиплексора (DEMUX) 25.

Перемежитель 23 четности выполняет перемежение четности, в котором биты четности кода LDPC, подаваемые из кодера 115, LDPC перемежают в положения других битов четности, и подает код LDPC после перемежения четности на перемежитель 24 со скручиванием столбцов.

Перемежитель 24 со скручиванием столбцов выполняет перемежение со скручиванием столбцов для кода LDPC, подаваемого от перемежителя 23 четности, и подает код LDPC после перемежения со скручиванием столбцов на демультиплексор 25.

Другими словами, в кодере 117 QAM, показанном на фиг.8, код LDPC передают так, что кодовый бит одного или больше битов кода LDPC преобразуют в точку сигнала, представляющую один символ ортогональной модуляции.

В перемежителе 24 со скручиванием столбцов, например, выполняют скручивание столбцов, которое будет описано ниже, как процесс сортировки, в котором кодовые биты для кода LDPC, подаваемого из перемежителя 23 четности, сортируют так, что множество кодовых битов кода LDPC, которые соответствуют "1", которая присутствует в одной произвольной строке матрицы проверки на четность, используемой кодером 115 LDPC, не будут включены в один символ.

Демультиплексор 25 получает код LDPC, устойчивость к AWGN которого улучшают путем выполнения процесса взаимной замены, в ходе которой положения двух или больше кодовых битов кода LDPC, которые формируют символ, взаимно заменяют для кода LDPC, подаваемого из перемежителя 24 со скручиванием столбцов. Затем демультиплексор 25 подает два или больше кодовых бита кода LDPC, полученных в процессе взаимной замены, на кодер 117 QAM (фиг.8), как символ.

Далее, на фиг.10 иллюстрируется матрица Н проверки на четность, которая используется для кодирования LDPC кодером 115 LDPC, показанным на фиг.8.

Матрица Н проверки на четность имеет структуру LDGM (матрица генерирования низкой плотности) и может быть представлена в Уравнении Н=[НА|НТ] (матрица, в которой элементы информационной матрицы HA установлены, как элементы левой стороны, и элементы матрицы HT четности установлены, как элементы правой стороны) путем использования информационной матрицы HA части кодовых битов для кода LDPC, которая соответствует битам информации, и матрице HT четности, которая соответствует битам четности.

Здесь среди кодовых битов одного кода LDPC (одно кодовое слово), количество битов информации и количество битов четности обозначается, как длина К информации и длина М четности, соответственно, и количество кодовых битов одного кода LDPC называется длиной кода N (=К+М).

Длину К информации и длину М четности в отношении конкретного кода LDPC для длины кода N определяют на основе скорости кода. Кроме того, матрица Н проверки на четность представляет собой матрицу из М строк × N столбцов. Кроме того, информационная матрица HA представляет собой матрицу М×К, и матрица HT четности представляет собой матрицу М×М.

На фиг.11 иллюстрируется матрица HT четности для матрицы Н проверки на четность кода LDPC, определенного в стандарте DVB-T.2 (и DVB-S.2).

В матрице HT четности для матрицы Н проверки на четность кода LDPC, определенного в стандарте DVB-T.2, как показано на фиг.11, элементы 1 имеют структуру лестницы, в которой элементы, в известном смысле, выровнены в структуре лестницы. Вес строки матрицы HT четности равен 1 для первой строки и 2 для всех остальных строк. Кроме того, вес столбца равен 1 для последнего столбца и равен 2 для всех остальных столбцов.

Как показано выше, код LDPC матрицы Н проверки на четность, в которой матрица HT четности имеет структуру лестницы, может быть легко сгенерирован, используя матрицу Н проверки на четность.

Другими словами, код LDPC (одно кодовое слово), представленный, как вектор с строки и вектор s столбца, полученные в результате транспонирования вектора строки, представлен как cT. В векторе с строки, который представляет собой код LDPC, часть битов информации представлена, как вектор А строки, и часть битов четности представлена, как вектор Т строки.

В таком случае вектор с строки может быть представлен в Уравнении с=[А|Т] (вектор строки, в котором элементы вектора А строки установлены, как элементы левой стороны, и элементы вектора Т строки установлены, как элементы правой стороны), используя вектор строки, как биты информации, и вектор Т строки, как биты четности.

Матрица Н проверки на четность и вектор с=[А|Т] строки, как код LDPC, должны удовлетворять Уравнению HcT=0, и вектор Т строки, как биты четности, конфигурирующие вектор с=[А|Т] строки, удовлетворяющие Уравнению HcT=0, могут быть получены последовательно (по очереди), путем установки элементов каждой строки в 0 в порядке от элементов первой строки вектора HcT столбца, представленного в Уравнении HcT=0, в случае, когда матрица HT четности для матрицы Н=[HA|HT] проверки на четность имеет структуру лестницу, показанную на фиг.11.

На фиг.12 показана схема, которая иллюстрирует матрицу Н проверки на четность кода LDPC, который определен в стандарте DVB-T.2.

В матрице Н проверки на четность кода LDPC, определенного в стандарте DVB-T.2, вес столбца установлен равным Х для столбцов КХ от первого столбца, вес столбца установлен равным 3 для последующих К3 столбцов, вес столбца установлен равным 2 для последующих (М-1) столбцов, и вес столбца установлен равным 1 для последнего 1 столбца.

Здесь КХ+К3+М-1+1 является тем же самым, что и длина N кода.

На фиг.13 показана схема, которая иллюстрирует числа КХ, К3 и М столбцов, и вес Х столбца для каждой скорости r кода для кода LDPC, определенного в стандарте DVB-T.2.