Область техники, к которой относится изобретение

Настоящая технология относится к устройству обработки данных и способу обработки данных, и, например, в частности, относится к устройству обработки данных и способу обработки данных, которые позволяют обеспечить хорошее качество связи при передаче данных, используя код LDPC.

Уровень техники

Код LDPC (проверка на четность низкой плотности) обладает высокими возможностями коррекции ошибок и в настоящее время был широко принят для систем передачи, включающих в себя спутниковую цифровую широковещательную передачу данных, такую как DVB (цифровая широковещательная передача видеоданных) -S.2, используемую в Европе (например, см. Непатентную литературу 1). Кроме того, выполняется проверка использования кода LDPC для наземной цифровой широковещательной передачи данных следующего поколения, такой как DVB-T.2.

Исходя из последних исследований, известно, что рабочие характеристики, близкие к пределу Шеннона, получают с помощью кода LDPC при увеличении длины кода, аналогично турбокоду. Поскольку код LDPC обладает таким свойством, что кратчайшее расстояние пропорционально длине кода, код LDPC обладает преимуществами исключительной характеристики вероятности ошибки блока, и для него характерно, так называемое, явление минимального уровня ошибки, наблюдаемое в характеристиках декодирования редко генерируемого турбокода.

Список литературы

Непатентная литература

Непатентная литература 1: DVB-S.2: ETSI EN 302 307 V1.2.1 (2009-08)

Раскрытие изобретения

Техническая задача

В стандарте DVB, таком как DVB-S.2, DVB-T.2 и DVB-C.2, в котором используется код LDPC, из кода LDPC формируют символ (символизируют) ортогональной модуляции (цифровой модуляции), такой как QPSK (квадратурная фазовая модуляция), и этот символ отображают на точку сигнала ортогональной модуляции и передают.

При передаче данных, используя код LDPC, такой как DVB-S.2, описанный выше, необходимо обеспечить хорошее качество связи.

Учитывая такие обстоятельства, в соответствии с вариантом осуществления настоящей технологии, желательно обеспечить хорошее качество связи при передаче данных, используя код LDPC.

Решение задачи

Первое устройство обработки данных или способ обработки данных в соответствии с настоящей технологией представляет собой устройство обработки данных или способ обработки данных, включающий в себя: модуль/этап кодирования для выполнения кодирования LDPC на основе матрицы проверки на четность кода LDPC, в котором длина кода составляет 16200 битов, и скорость кодирования составляет 8/15; и модуль/этап взаимного обмена для обмена битом кода для кода LDPC, в котором длина кода составляет 16200 битов, и скорость кодирования составляет 8/15, с символьным битом символа, соответствующего любой из 8 точек сигнала, определенных 8PSK. Когда 3 бита битов кода, сохраненных в трех модулях сохранения, имеющих емкость сохранения 16200/3 битов, и считываемых поразрядно из модулей сохранения, выделяют для одного символа, (#i+1)-ый бит от старшего значащего бита из 3 битов из битов кода устанавливают в бит b#i, (#i+1)-ый бит от старшего значащего бита из 3 битов символьных битов одного символа устанавливают в бит y#i, и модуль/этап взаимного обмена выполняет обмен бита b0 на бит y1, бита b1 на бит y0 и бита b2 на бит y2. Код LDPC включает в себя информационный бит и бит четности. Матрица проверки на четность включает в себя информационную часть матрицы, соответствующую информационному биту, и часть матрицы четности, соответствующую биту четности. Информационная часть матрицы представлена таблицей исходного значения матрицы проверки на четность. Таблица исходного значения матрицы проверки на четность представляет собой таблицу, представляющую положения элементов 1 из информационной части матрицы для каждых 360 столбцов, и выражена следующим образом

32 384 430 591 1976 1296 1976 1999 2137 2175 3638 4214 4304 4486 4662 4999 5174 5700 6969 7115 7138 7189

1881 1788 1976 1910 2724 4504 4928 4973 5616 5686 5718 5846 6523 6893 6994 7074 7100 7277 7399 7476 7480 7537

2791 2824 2927 4196 4298 4800 4948 5361 5401 5688 5818 5862 5969 6029 6244 6645 6962 7203 7302 7454 7534

574 2056 1826 1976 1461 1976 2069 2387 2794 3349 3366 4951 5826 5834 5903 6640 6762 6786 6859 7043 7418 7431 7554

14 178 675 823 890 930 1209 1311 2898 4339 4600 5203 6485 6549 6970 7208 7218 7298 7454 7457 7462

4075 4188 7313 7553

5145 6018 7148 7507

3198 4858 6983 7033

3170 5126 5625 6901

2839 6093 7071 7450

11 3735 5413

2497 5400 7238

2067 5172 5714

1889 7173 7329

1795 2773 3499

2695 2944 6735

3221 4625 5897

1690 6122 6816

5013 6839 7358

1601 6849 7415

2180 7389 7543

2121 6838 7054

1948 3109 5046

272 1015 7464.

В первом устройстве обработки данных и способе обработки данных в соответствии с настоящей технологией, кодирование LDPC выполняют на основе матрицы проверки на четность кода LDPC, в котором длина кода составляет 16200 битов, и скорость кодирования составляет 8/15, и бит кода для кода LDPC, в котором длина кода составляет 16200 битов, и скорость кодирования составляет 8/15, обменивают с символьным битом символа, соответствующего любой из 8 точек сигнала, определенных 8PSK. При взаимном обмене, когда 3 бита битов кода, сохраненных в трех модулях сохранения, имеющих емкость сохранения 16200/3 битов, и считываемых поразрядно из модулей сохранения, выделяют для одного символа, (#i+1)-ый бит от старшего значащего бита из 3 битов из битов кода устанавливают в бит b#i, (#i+1)-ый бит от старшего значащего бита из 3 битов символьных битов одного символа устанавливают в бит y#i, бит b0 обменивают на бит y1, бит b1 обменивают на бит y0, и бит b2 обменивают на бит у2. Код LDPC включает в себя информационный бит и бит четности. Матрица проверки на четность включает в себя информационную часть матрицы, соответствующую информационному биту, и часть матрицы четности, соответствующую биту четности. Информационная часть матрицы представлена таблицей исходного значения матрицы проверки на четность. Таблица исходного значения матрицы проверки на четность представляет собой таблицу, представляющую положения элементов 1 из информационной части матрицы для каждых 360 столбцов, и выражена следующим образом

32 384 430 591 1976 1296 1976 1999 2137 2175 3638 4214 4304 4486 4662 4999 5174 5700 6969 7115 7138 7189

1881 1788 1976 1910 2724 4504 4928 4973 5616 5686 5718 5846 6523 6893 6994 7074 7100 7277 7399 7476 7480 7537

2791 2824 2927 4196 4298 4800 4948 5361 5401 5688 5818 5862 5969 6029 6244 6645 6962 7203 7302 7454 7534

574 2056 1826 1976 1461 1976 2069 2387 2794 3349 3366 4951 5826 5834 5903 6640 6762 6786 6859 7043 7418 7431 7554

14 178 675 823 890 930 1209 1311 2898 4339 4600 5203 6485 6549 6970 7208

7218 7298 7454 7457 7462

4075 4188 7313 7553

5145 6018 7148 7507

3198 4858 6983 7033

3170 5126 5625 6901

2839 6093 7071 7450

11 3735 5413

2497 5400 7238

2067 5172 5714

1889 7173 7329

1795 2773 3499

2695 2944 6735

3221 4625 5897

1690 6122 6816

5013 6839 7358

1601 6849 7415

2180 7389 7543

2121 6838 7054

1948 3109 5046

272 1015 7464.

Второе устройство обработки данных или способ обработки данных в соответствии с настоящей технологией представляет собой устройство обработки данных или способ обработки данных, включающий в себя: модуль/этап кодирования для выполнения кодирования LDPC на основе матрицы проверки на четность кода LDPC, в котором длина кода составляет 16200 битов, и скорость кодирования составляет 8/15; и модуль/этап взаимного обмена для обмена битом кода для кода LDPC, в котором длина кода составляет 16200 битов, и скорость кодирования составляет 8/15, с символьным битом символа, соответствующего любой из 16 точек сигнала, определенных 16APSK. Когда 4 бита битов кода, сохраненных в четырех модулях сохранения, имеющих емкость сохранения 16200/4 битов, и считываемых поразрядно из модулей сохранения, выделяют для одного символа, (#i+1)-ый бит от старшего значащего бита из 4 битов из битов кода устанавливают в бит b#i, (#i+1)-ый бит от старшего значащего бита из 4 битов символьных битов одного символа устанавливают в бит y#i, и модуль/этап взаимного обмена выполняет обмен бита b0 на бит у2, бита b1 на бит y1, бита b2 на бит y0 и бита b3 на бит у3. Код LDPC включает в себя информационный бит и бит четности. Матрица проверки на четность включает в себя информационную часть матрицы, соответствующую информационному биту, и часть матрицы четности, соответствующую биту четности. Информационная часть матрицы представлена таблицей исходного значения матрицы проверки на четность. Таблица исходного значения матрицы проверки на четность представляет собой таблицу, представляющую положения элементов 1 из информационной части матрицы для каждых 360 столбцов, и выражена следующим образом

32 384 430 591 1976 1296 1976 1999 2137 2175 3638 4214 4304 4486 4662 4999 5174 5700 6969 7115 7138 7189

1881 1788 1976 1910 2724 4504 4928 4973 5616 5686 5718 5846 6523 6893 6994 7074 7100 7277 7399 7476 7480 7537

2791 2824 2927 4196 4298 4800 4948 5361 5401 5688 5818 5862 5969 6029 6244 6645 6962 7203 7302 7454 7534

574 2056 1826 1976 1461 1976 2069 2387 2794 3349 3366 4951 5826 5834 5903 6640 6762 6786 6859 7043 7418 7431 7554

14 178 675 823 890 930 1209 1311 2898 4339 4600 5203 6485 6549 6970 7208 7218 7298 7454 7457 7462

4075 4188 7313 7553

5145 6018 7148 7507

3198 4858 6983 7033

3170 5126 5625 6901

2839 6093 7071 7450

11 3735 5413

2497 5400 7238

2067 5172 5714

1889 7173 7329

1795 2773 3499

2695 2944 6735

3221 4625 5897

1690 6122 6816

5013 6839 7358

1601 6849 7415

2180 7389 7543

2121 6838 7054

1948 3109 5046

272 1015 7464.

Во втором устройстве обработки данных и способе обработки данных в соответствии с настоящей технологией, кодирование LDPC выполняют на основе матрицы проверки на четность кода LDPC, в котором длина кода составляет 16200 битов, и скорость кодирования составляет 8/15, и бит кода для кода LDPC, в котором длина кода составляет 16200 битов, и скорость кодирования составляет 8/15, обменивают с символьным битом символа, соответствующего любой из 16 точек сигнала, определенных 16APSK. При взаимном обмене, когда 4 бита битов кода, сохраненных в четырех модулях сохранения, имеющих емкость сохранения 16200/4 битов, и считываемых поразрядно из модулей сохранения, выделяют для одного символа, (#i+1)-ый бит от старшего значащего бита из 4 битов из битов кода устанавливают в бит b#i, (#i+1)-ый бит от старшего значащего бита из 4 битов символьных битов одного символа устанавливают в бит y#i, бит b0 обменивают на бит у2, бит b1 обменивают на бит y1, бит b2 обменивают на бит y0, и бит b3 обменивают на бит у3. Код LDPC включает в себя информационный бит и бит четности. Матрица проверки на четность включает в себя информационную часть матрицы, соответствующую информационному биту, и часть матрицы четности, соответствующую биту четности. Информационная часть матрицы представлена таблицей исходного значения матрицы проверки на четность. Таблица исходного значения матрицы проверки на четность представляет собой таблицу, представляющую положения элементов 1 из информационной части матрицы для каждых 360 столбцов, и выражена следующим образом

32 384 430 591 1976 1296 1976 1999 2137 2175 3638 4214 4304 4486 4662 4999 5174 5700 6969 7115 7138 7189

1881 1788 1976 1910 2724 4504 4928 4973 5616 5686 5718 5846 6523 6893 6994 7074 7100 7277 7399 7476 7480 7537

2791 2824 2927 4196 4298 4800 4948 5361 5401 5688 5818 5862 5969 6029 6244 6645 6962 7203 7302 7454 7534

574 2056 1826 1976 1461 1976 2069 2387 2794 3349 3366 4951 5826 5834 5903 6640 6762 6786 6859 7043 7418 7431 7554

14 178 675 823 890 930 1209 1311 2898 4339 4600 5203 6485 6549 6970 7208 7218 7298 7454 7457 7462

4075 4188 7313 7553

5145 6018 7148 7507

3198 4858 6983 7033

3170 5126 5625 6901

2839 6093 7071 7450

11 3735 5413

2497 5400 7238

2067 5172 5714

1889 7173 7329

1795 2773 3499

2695 2944 6735

3221 4625 5897

1690 6122 6816

5013 6839 7358

1601 6849 7415

2180 7389 7543

2121 6838 7054

1948 3109 5046

272 1015 7464.

Устройство обработки данных может представлять собой независимое устройство и может представлять собой внутренний блок, составляющий одно устройство.

Полезные эффекты изобретения

В соответствии с вариантом осуществления настоящей технологии, можно обеспечить хорошее качество связи при передаче данных, используя код LDPC.

Предпочтительные эффекты, представленные в настоящем описании, являются просто примером, и полезные эффекты варианта осуществления настоящей технологии не ограничены предпочтительными эффектами, представленными в настоящем описании, и могут присутствовать дополнительные полезные эффекты.

Краткое описание чертежей

На фиг. 1 представлена иллюстрация матрицы H проверки на четность кода LDPC.

На фиг. 2 показана блок-схема последовательности операций, поясняющая последовательность декодирования кода LDPC.

На фиг. 3 представлена иллюстрация примера матрицы проверки на четность кода LDPC.

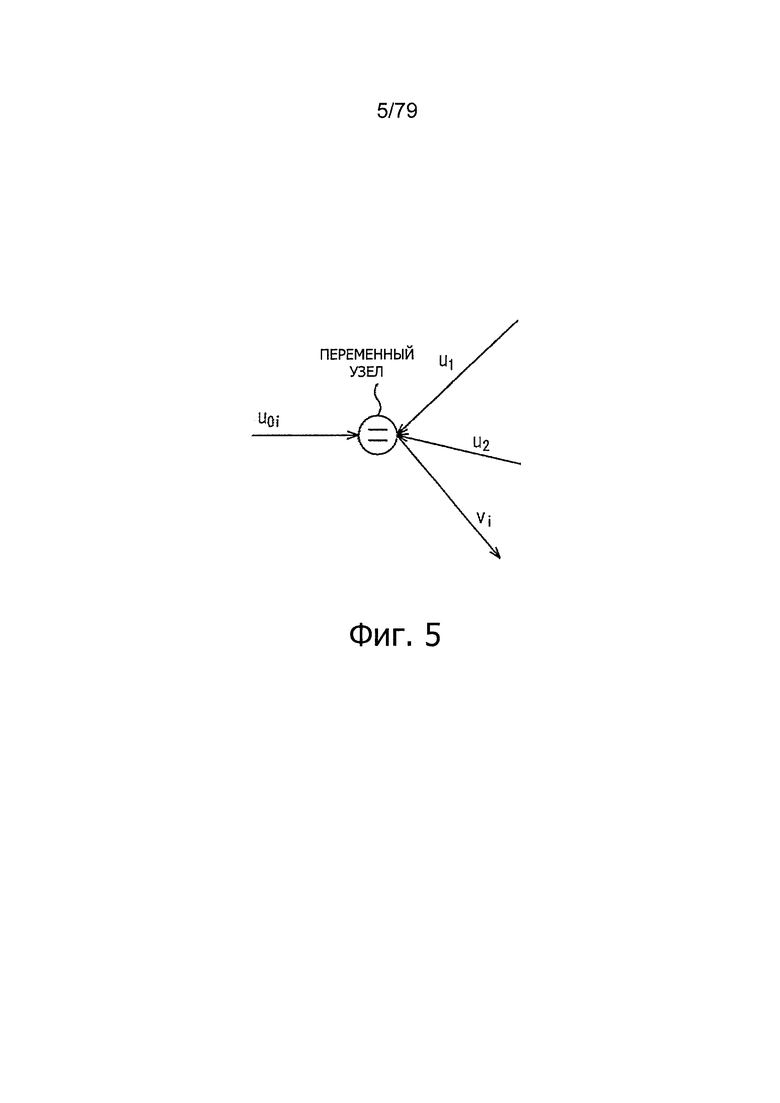

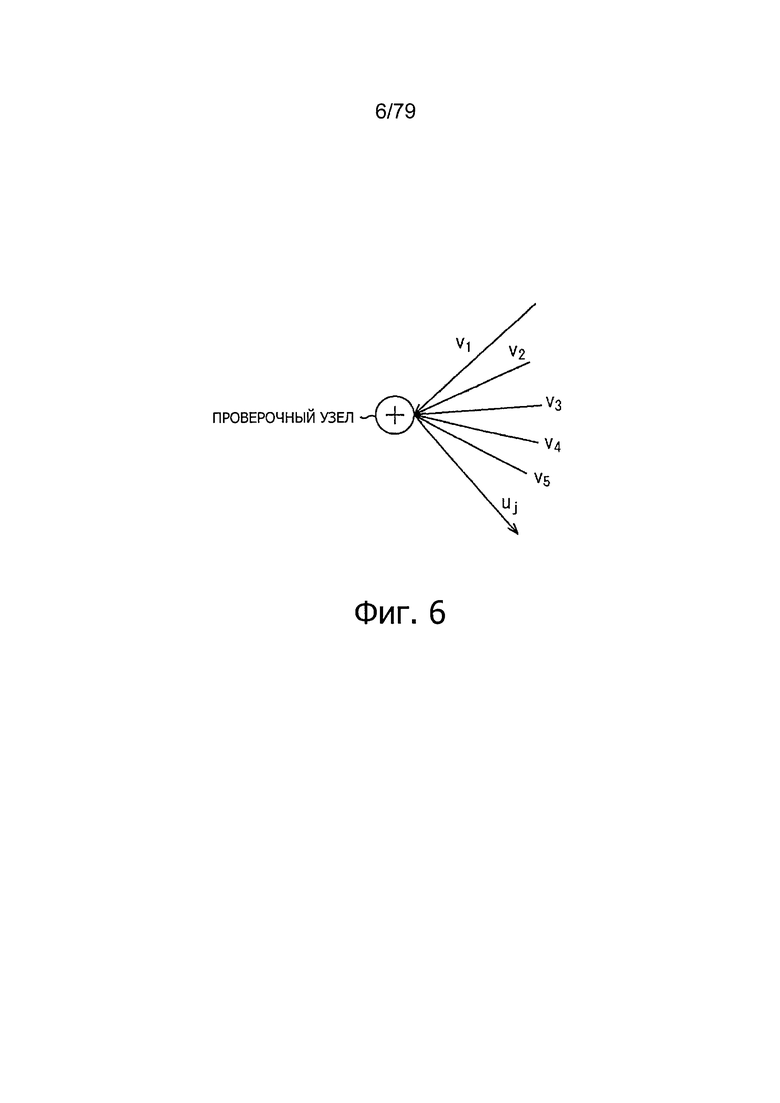

На фиг. 4 представлена иллюстрация графа Таннера матрицы проверки на четность. На фиг. 5 представлена иллюстрация переменного узла. На фиг. 6 представлена иллюстрация узла управления.

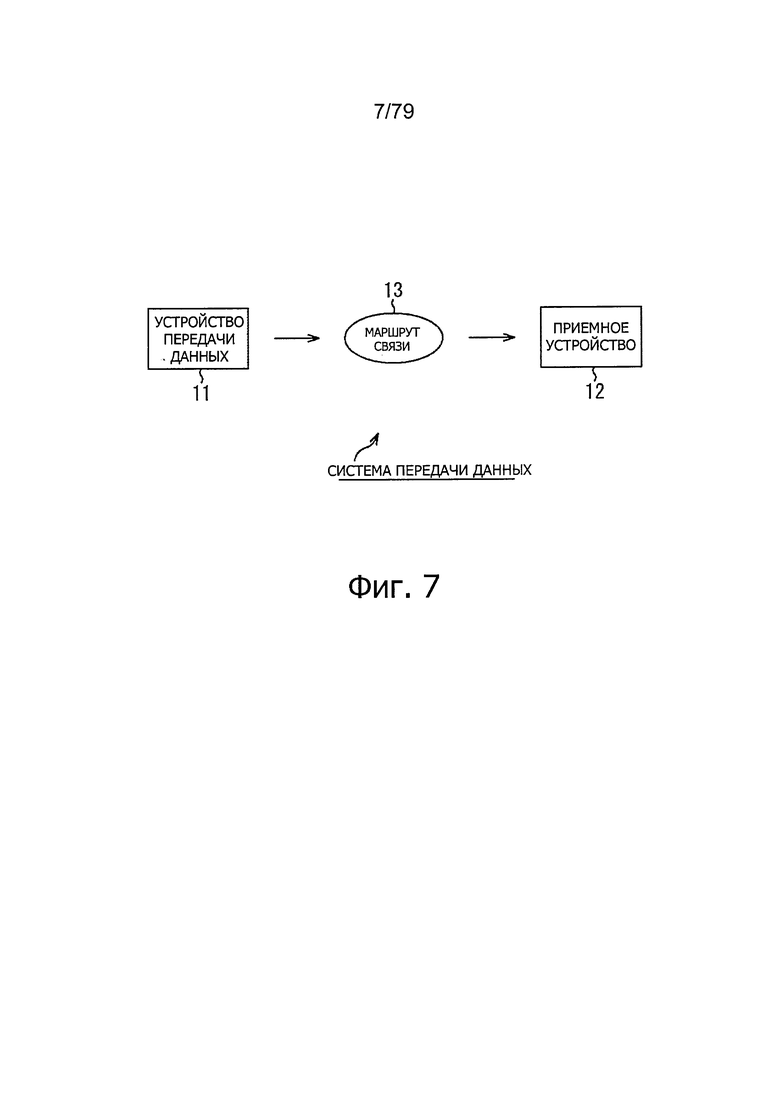

На фиг. 7 представлена иллюстрация примера конфигурации варианта осуществления системы передачи, в которой применяется настоящее изобретение.

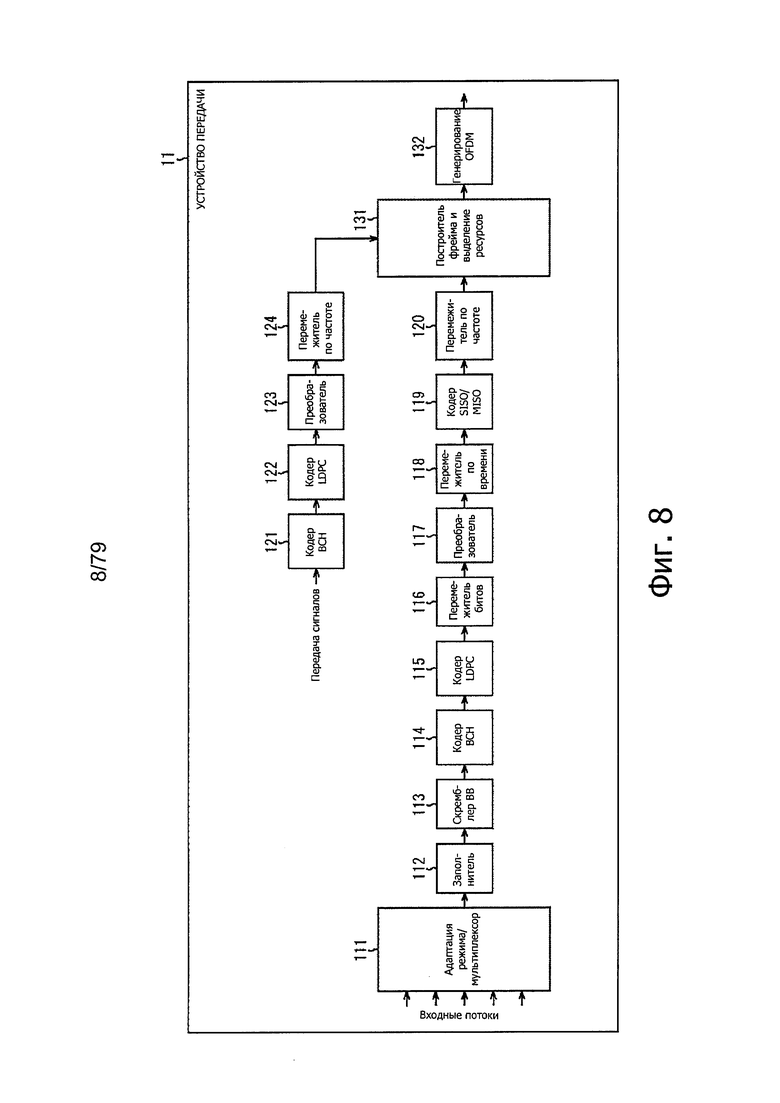

На фиг. 8 показана блок-схема, поясняющая пример конфигурации устройства 11 передачи.

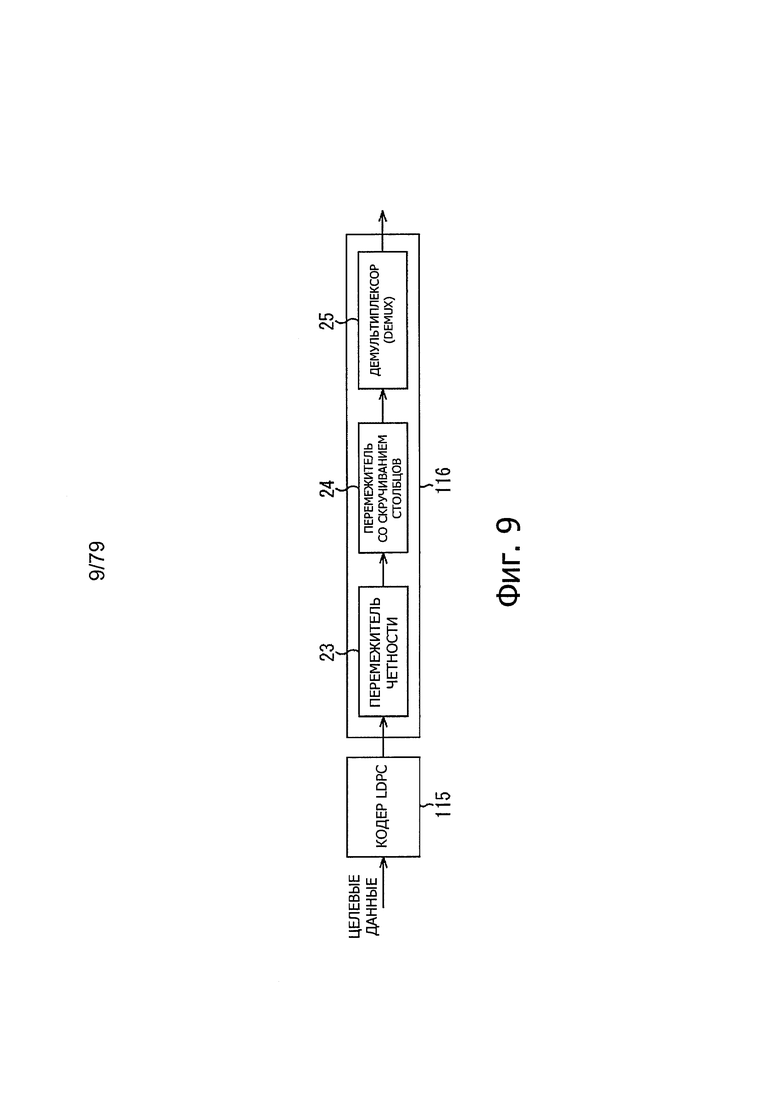

На фиг. 9 показана блок-схема, поясняющая пример конфигурации перемежителя 116 битов.

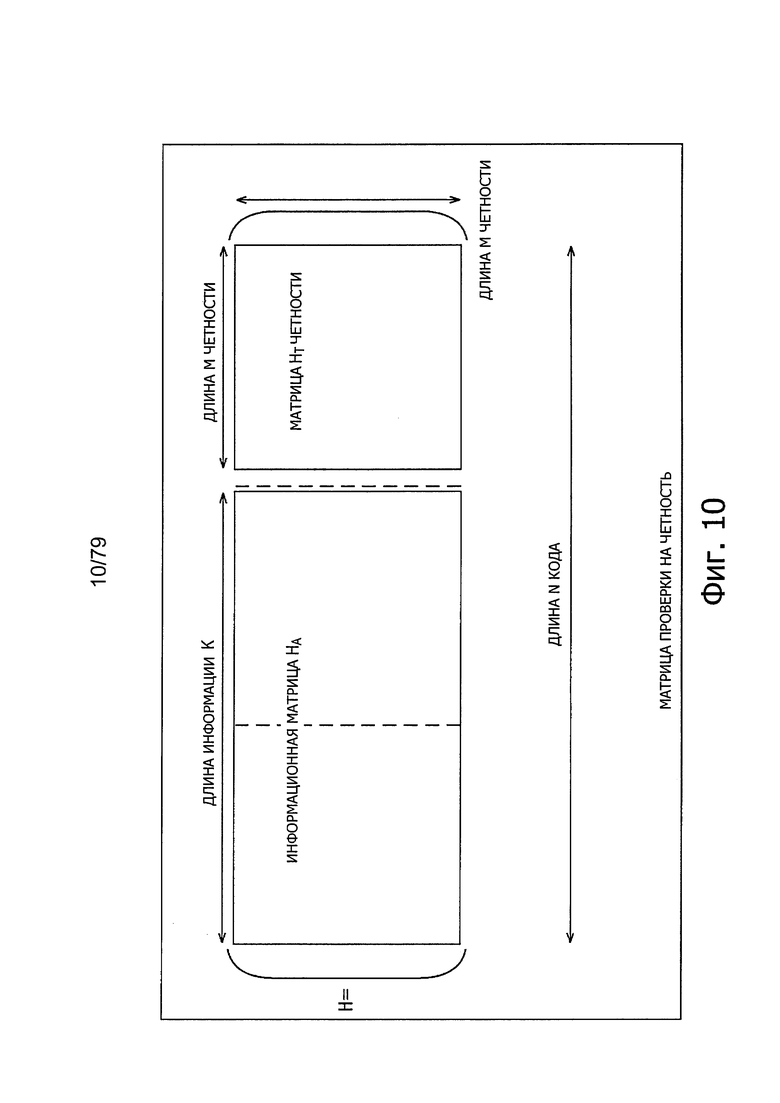

На фиг. 10 представлена иллюстрация матрицы проверки на четность.

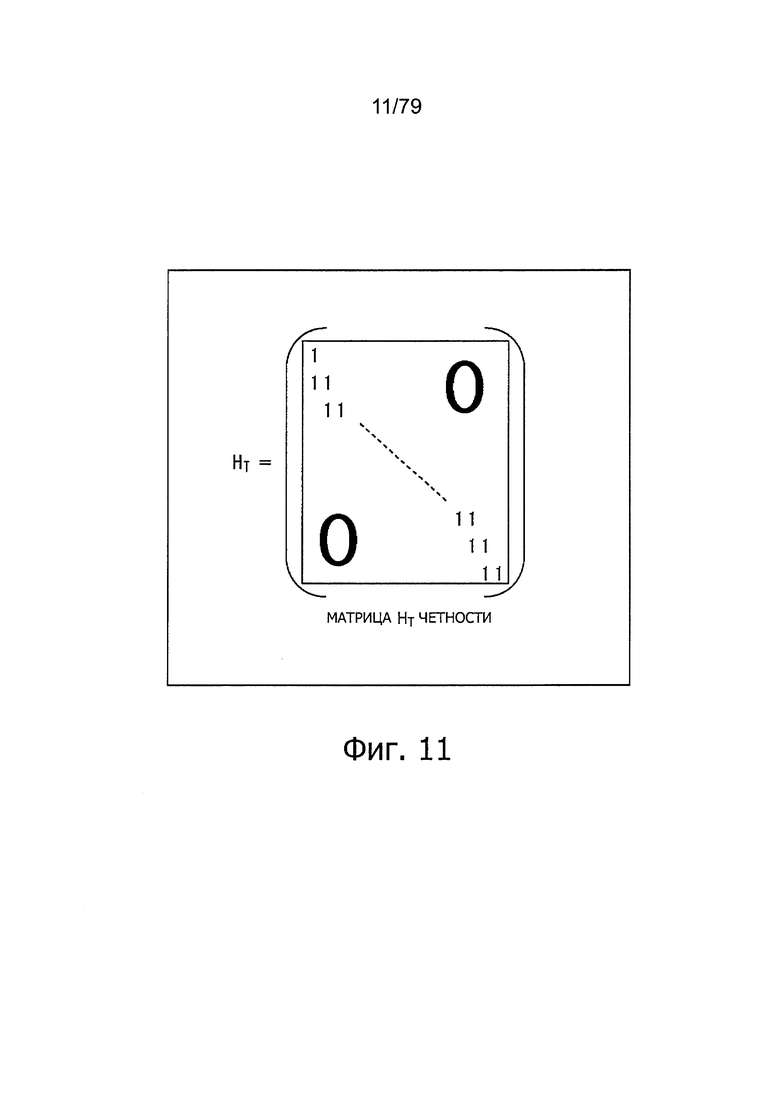

На фиг. 11 представлена иллюстрация матрицы четности.

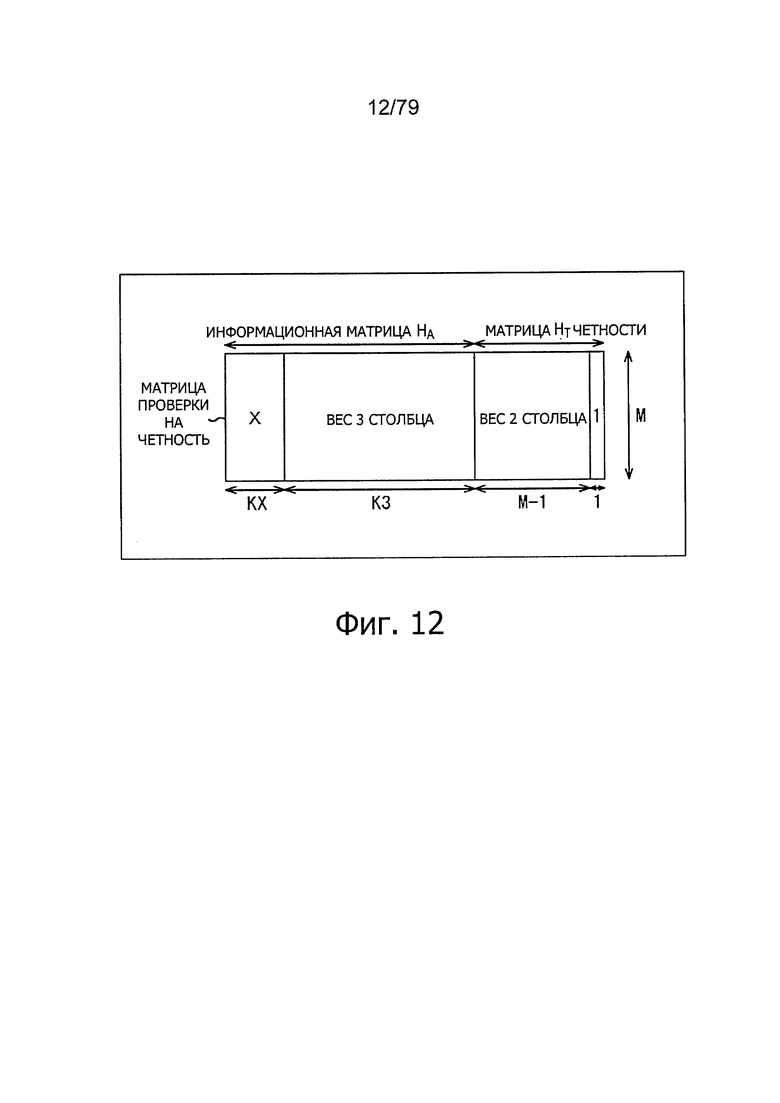

На фиг. 12 представлена иллюстрация матрицы проверки на четность кода LDPC, определенного в стандарте DVB-S.2.

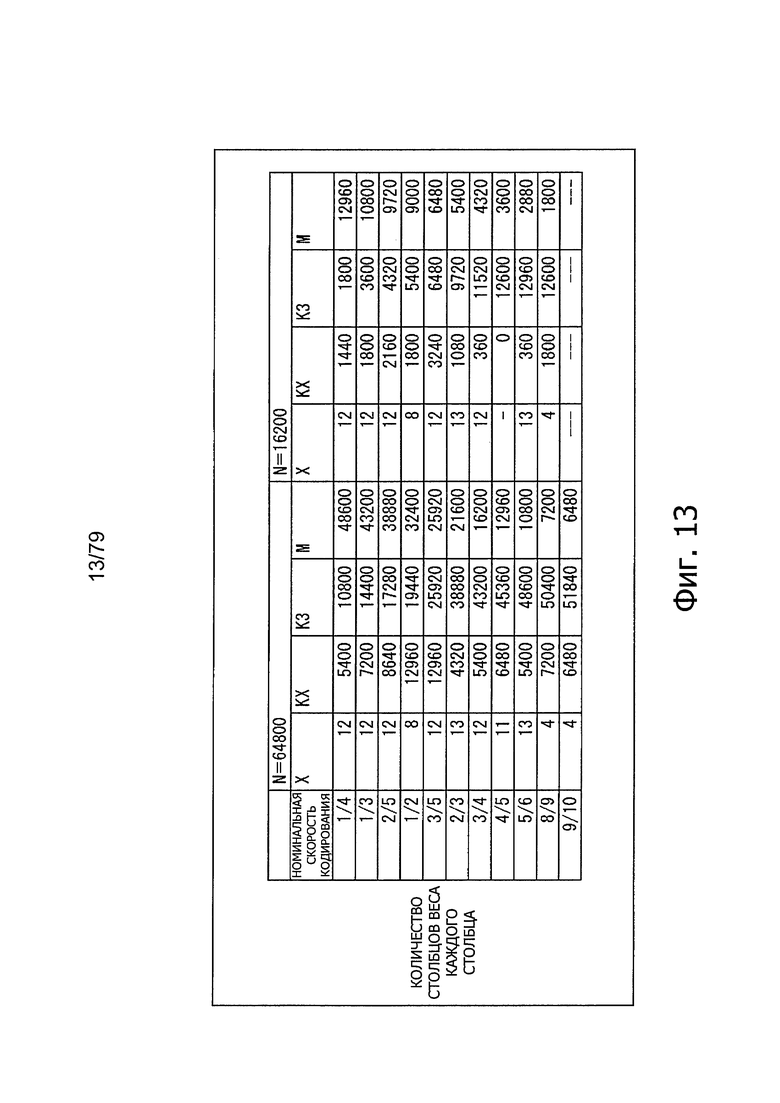

На фиг. 13 представлена иллюстрация матрицы проверки на четность кода LDPC, определенного в стандарте DVB-S.2.

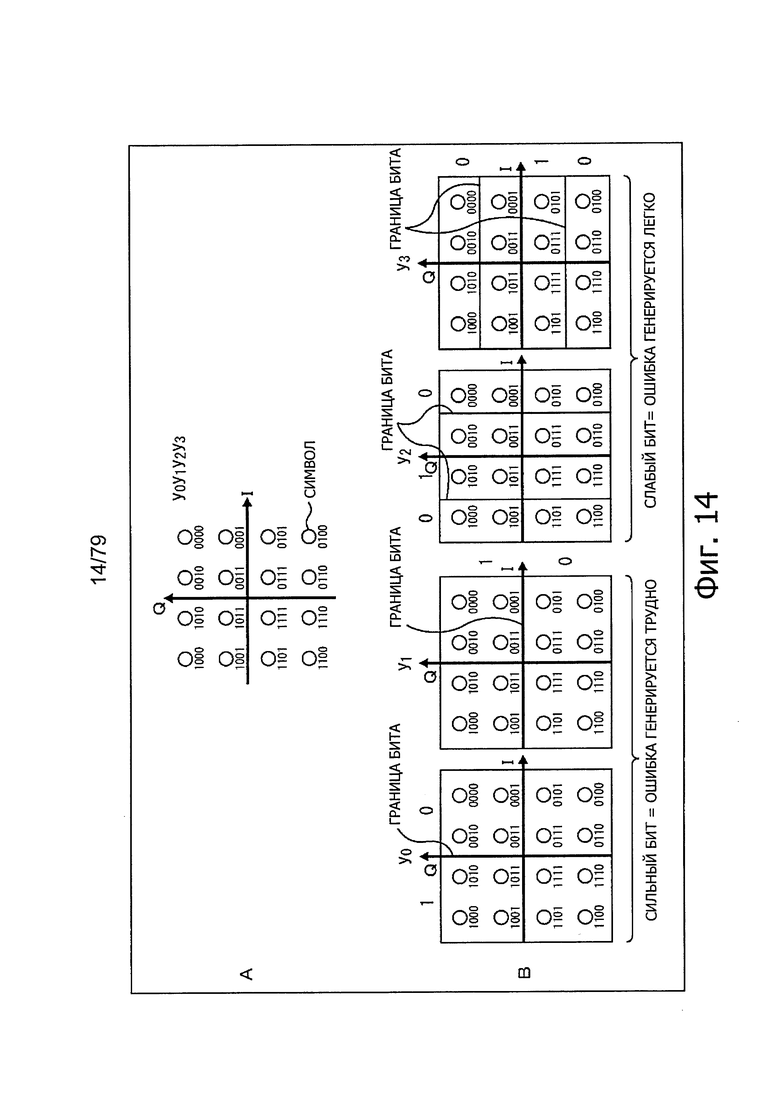

На фиг. 14 представлена иллюстрация компоновки точки сигнала 16QAM.

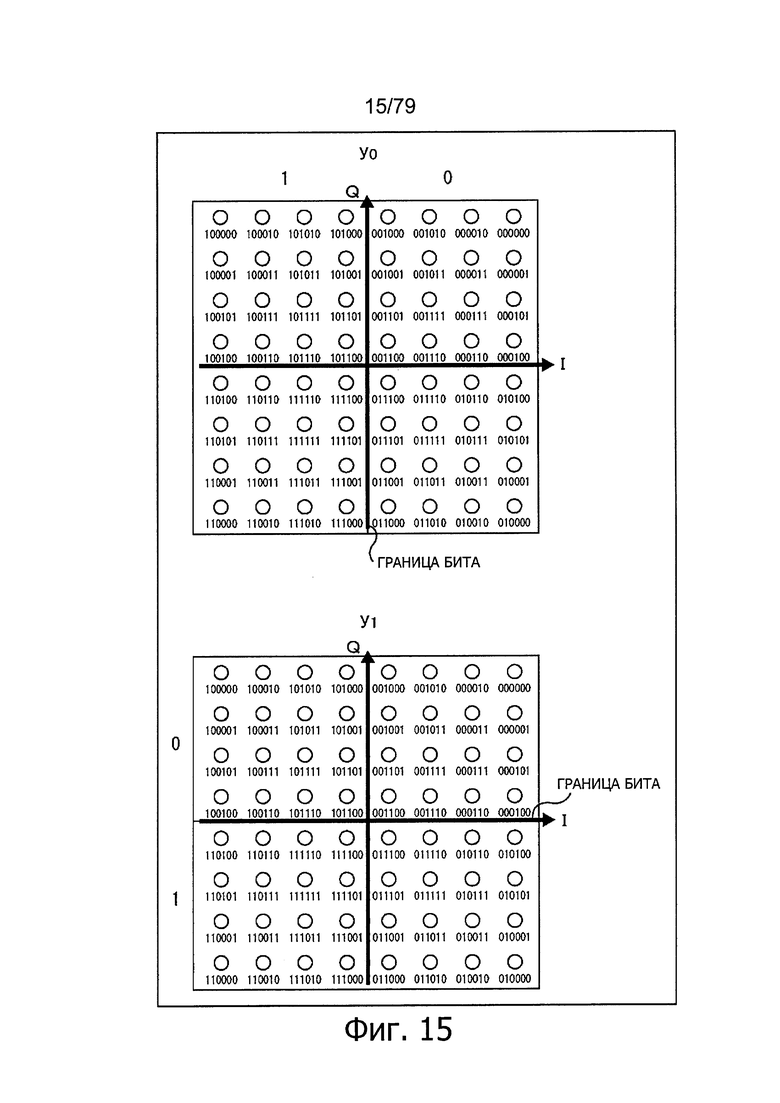

На фиг. 15 представлена иллюстрация компоновки точки сигнала 64QAM.

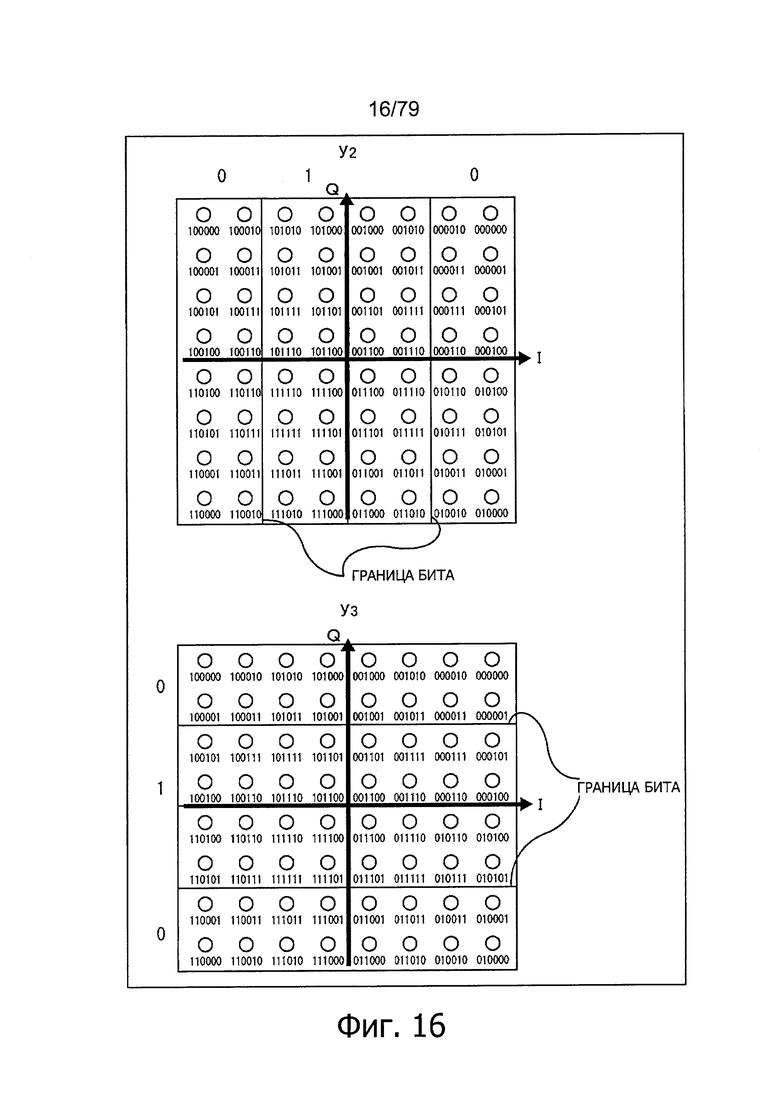

На фиг. 16 представлена иллюстрация компоновки точки сигнала 64QAM.

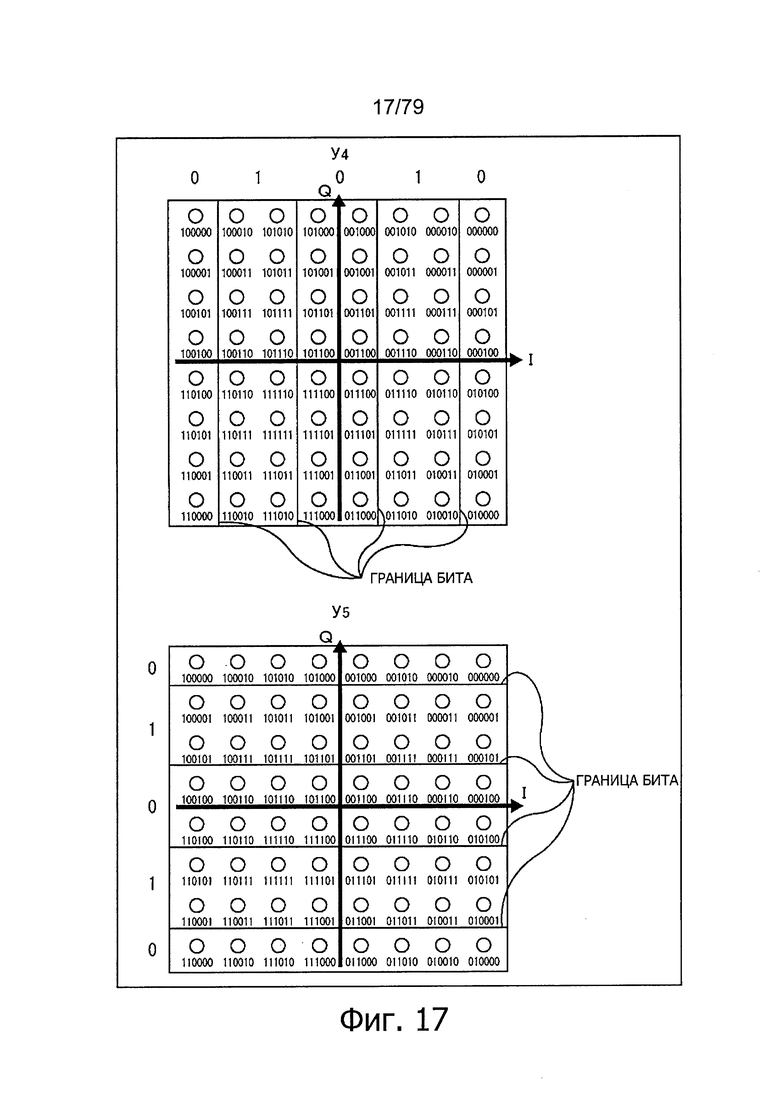

На фиг. 17 представлена иллюстрация компоновки точки сигнала 64QAM.

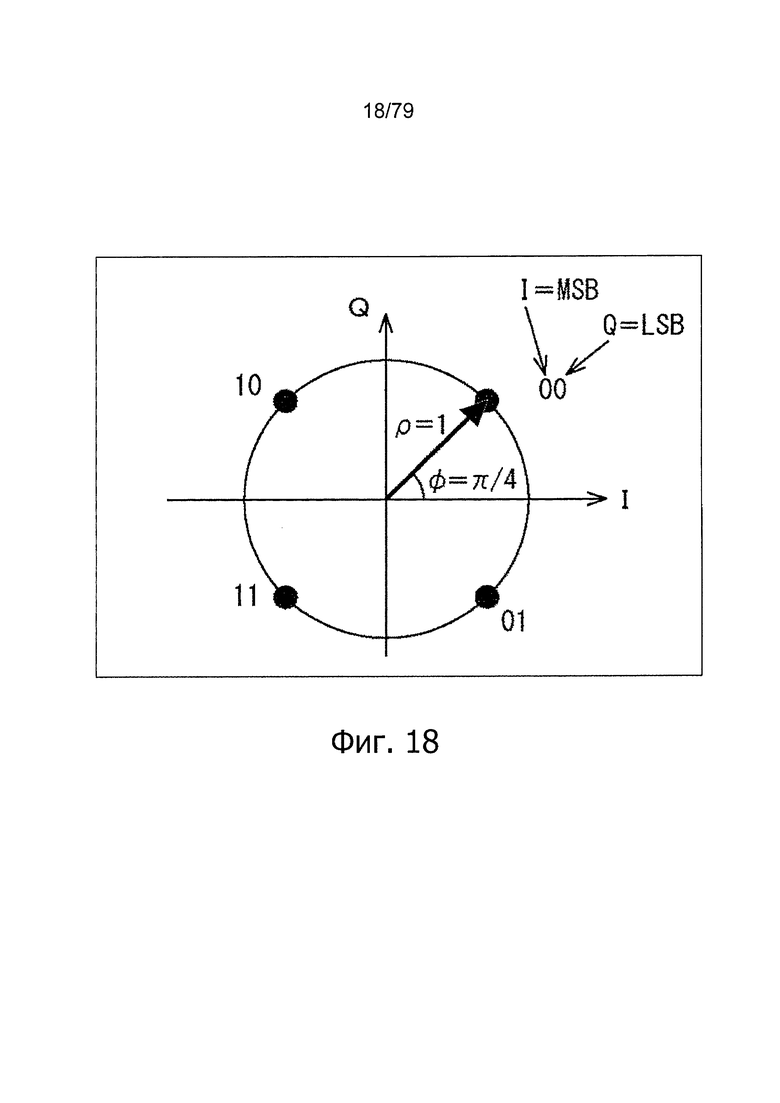

На фиг. 18 представлена иллюстрация компоновки точки сигнала, определенной в стандарте DVB-S.2.

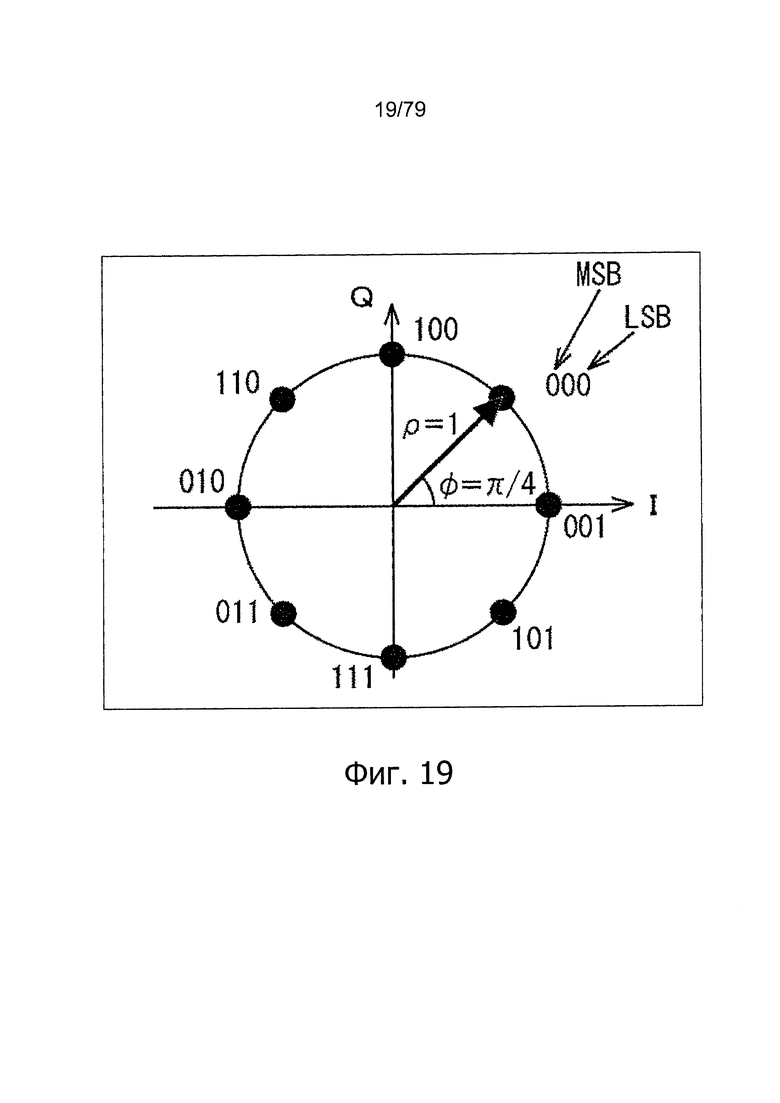

На фиг. 19 представлена иллюстрация компоновки точки сигнала, определенной в стандарте DVB-S.2.

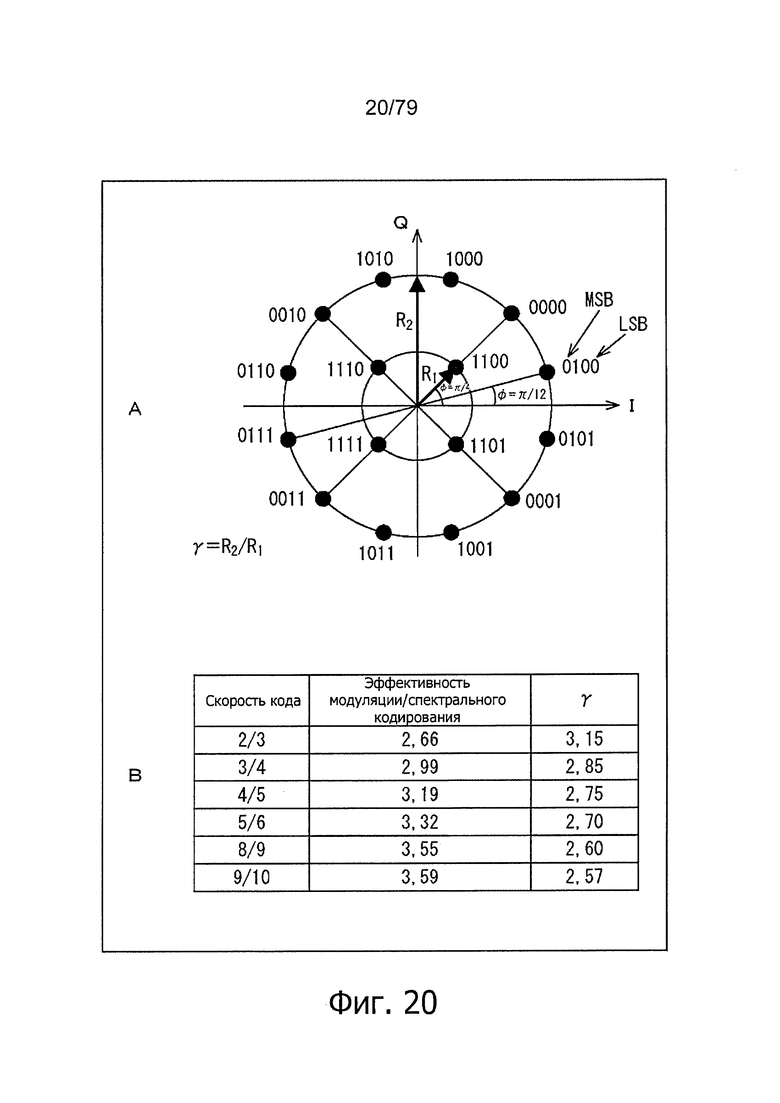

На фиг. 20 представлена иллюстрация компоновки точки сигнала, определенной в стандарте DVB-S.2.

На фиг. 21 представлена иллюстрация компоновки точки сигнала, определенной в стандарте DVB-S.2.

На фиг. 22 представлена иллюстрация обработки демультиплексора 25.

На фиг. 23 представлена иллюстрация обработки демультиплексора 25.

На фиг. 24 представлена иллюстрация графа Таннера для декодирования кода LDPC.

На фиг. 25 представлена иллюстрация матрицы ΗT четности, становящейся ступенчатой структурой, и графа Таннера, соответствующего матрице ΗT четности.

На фиг. 26 представлена иллюстрация матрицы ΗT четности матрицы Η проверки на четность, соответствующей коду LDPC после перемежения четности.

На фиг. 27 представлена иллюстрация преобразованной матрицы проверки на четность.

На фиг. 28 представлена иллюстрация обработки перемежителя 24 со скручиванием столбцов.

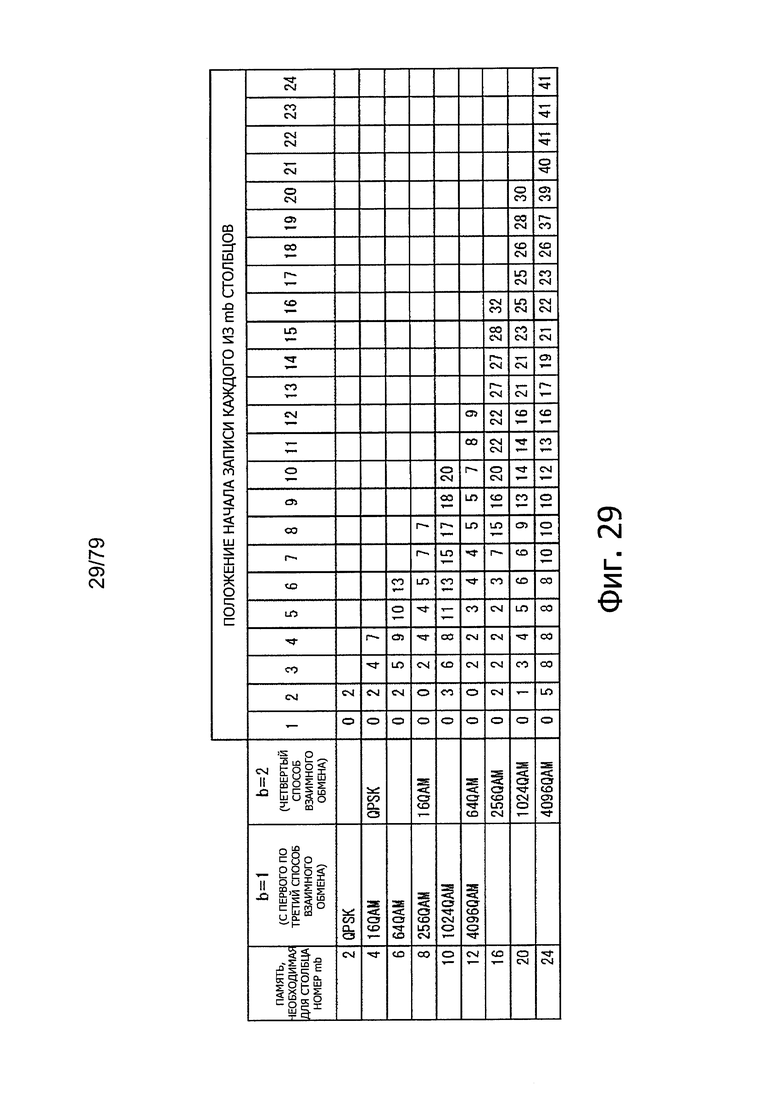

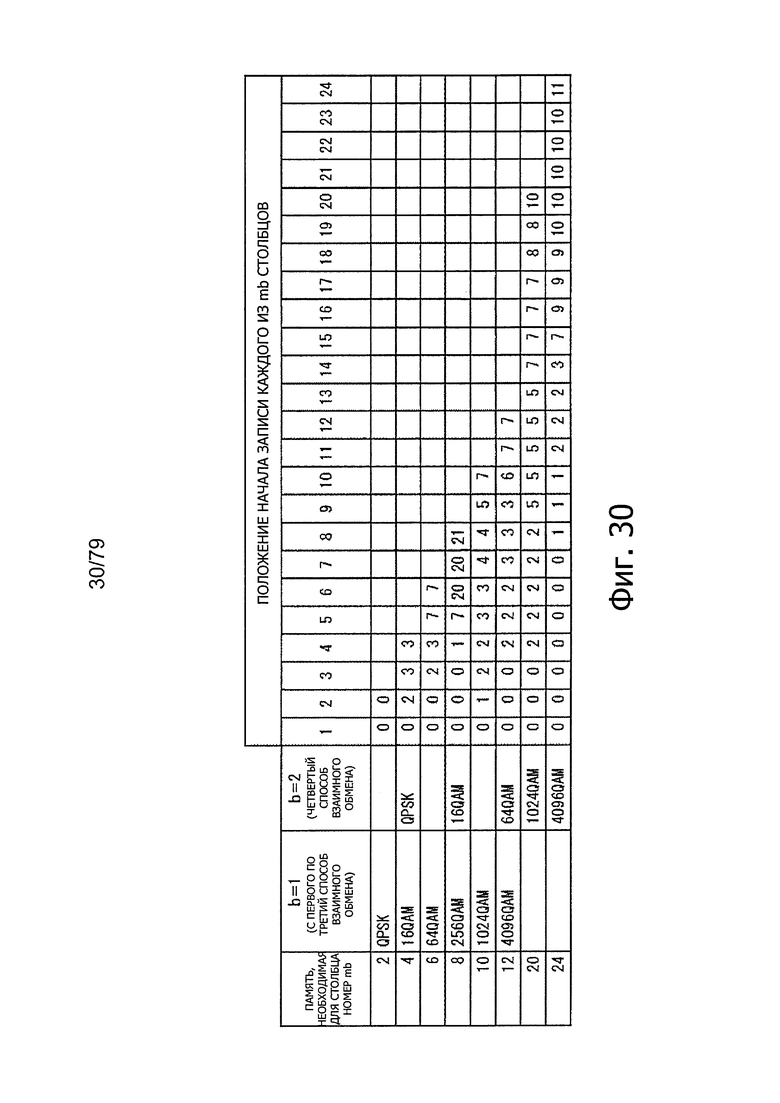

На фиг. 29 представлена иллюстрация номера столбца запоминающего устройства 31, необходимого для перемежения со скручиванием столбцов, и адреса положения начала записи.

На фиг. 30 представлена иллюстрация номера столбца запоминающего устройства 31, необходимого для перемежения со скручиванием столбцов, и адреса положения начала записи.

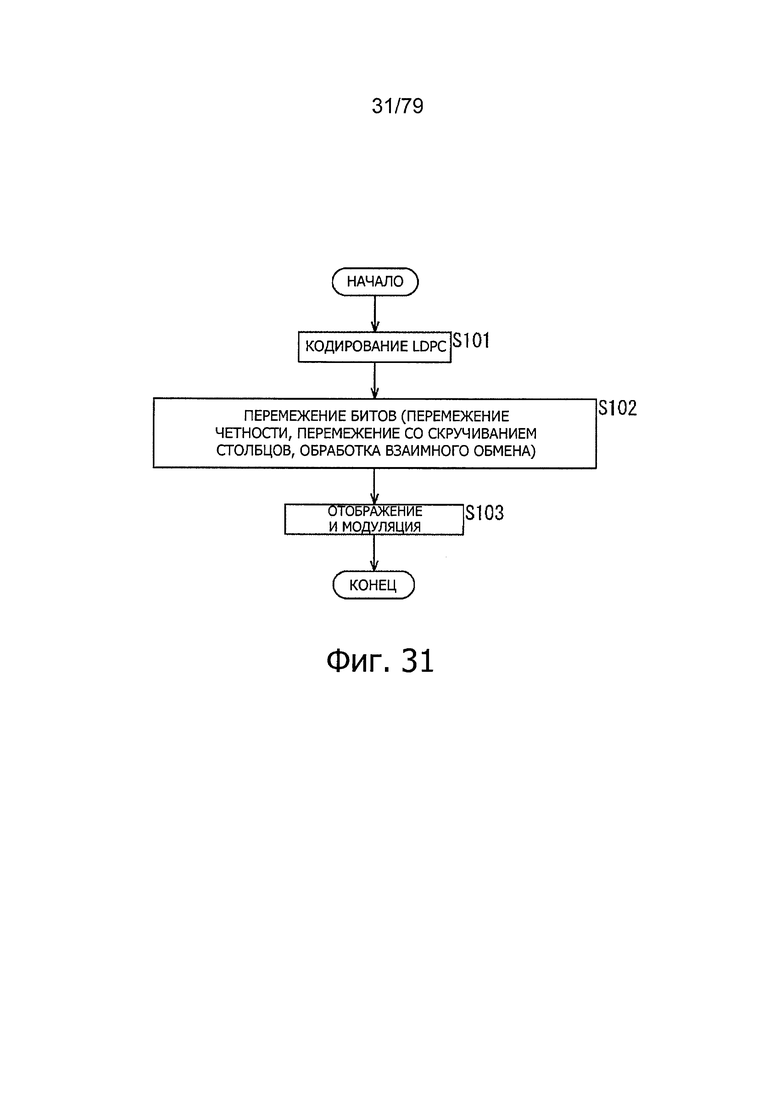

На фиг. 31 показана обработка, иллюстрирующая блок-схему последовательности операций, выполняемых перемежителем 116 битов и преобразователем 117.

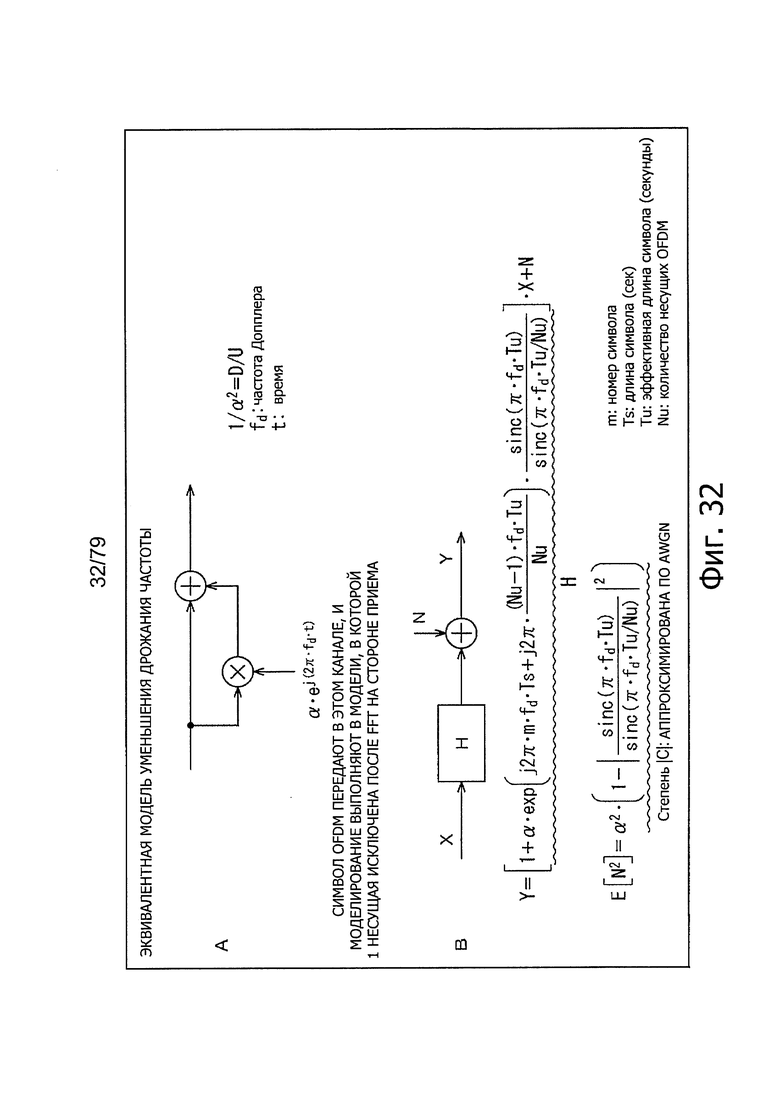

На фиг. 32 представлена иллюстрация модели канала связи, принятого в результате моделирования.

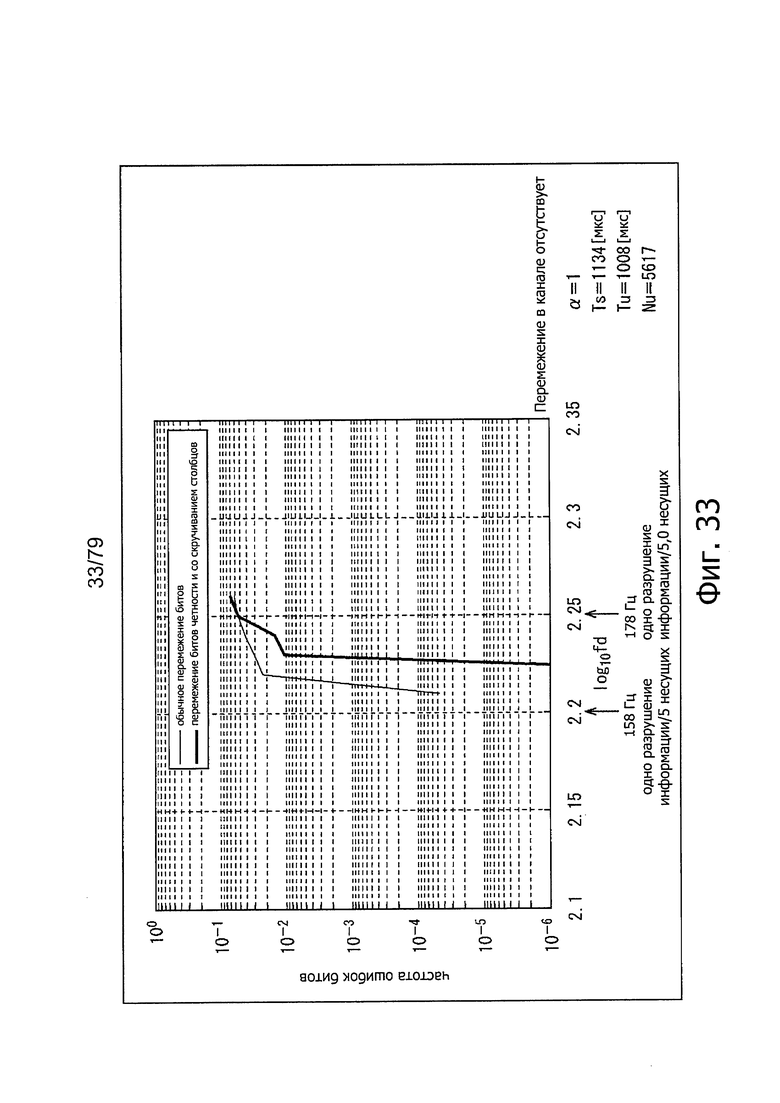

На фиг. 33 представлена иллюстрация соотношения частоты ошибок, полученного моделированием, и частоты fd Допплера, вызывавшей дрожание частоты.

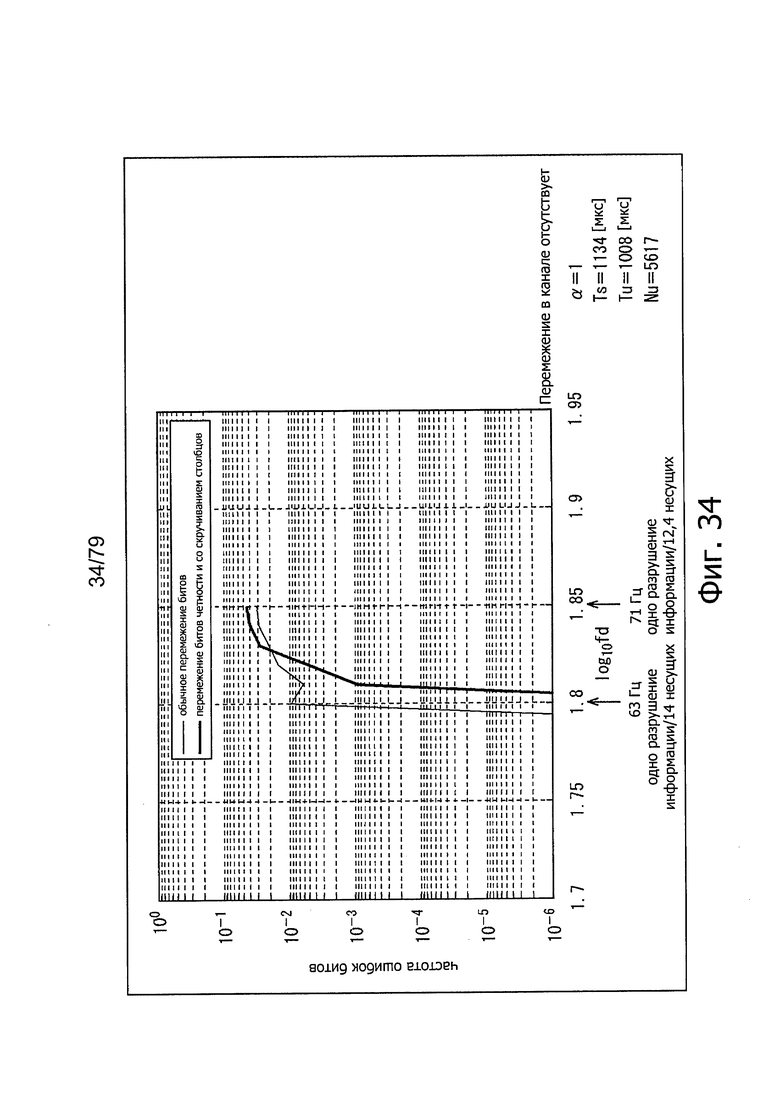

На фиг. 34 представлена иллюстрация соотношения частоты ошибок, полученного моделированием, и частоты fd Допплера, вызывавшей дрожание частоты.

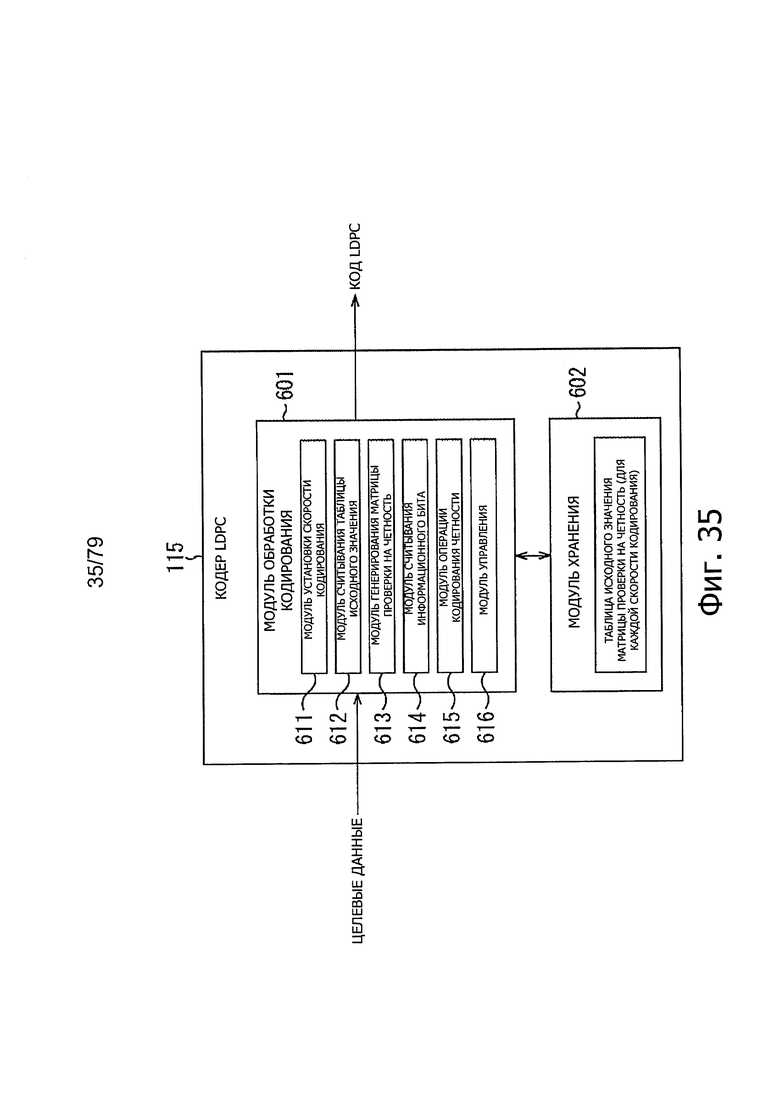

На фиг. 35 показана блок-схема, поясняющая пример конфигурации кодера 115 LDPC.

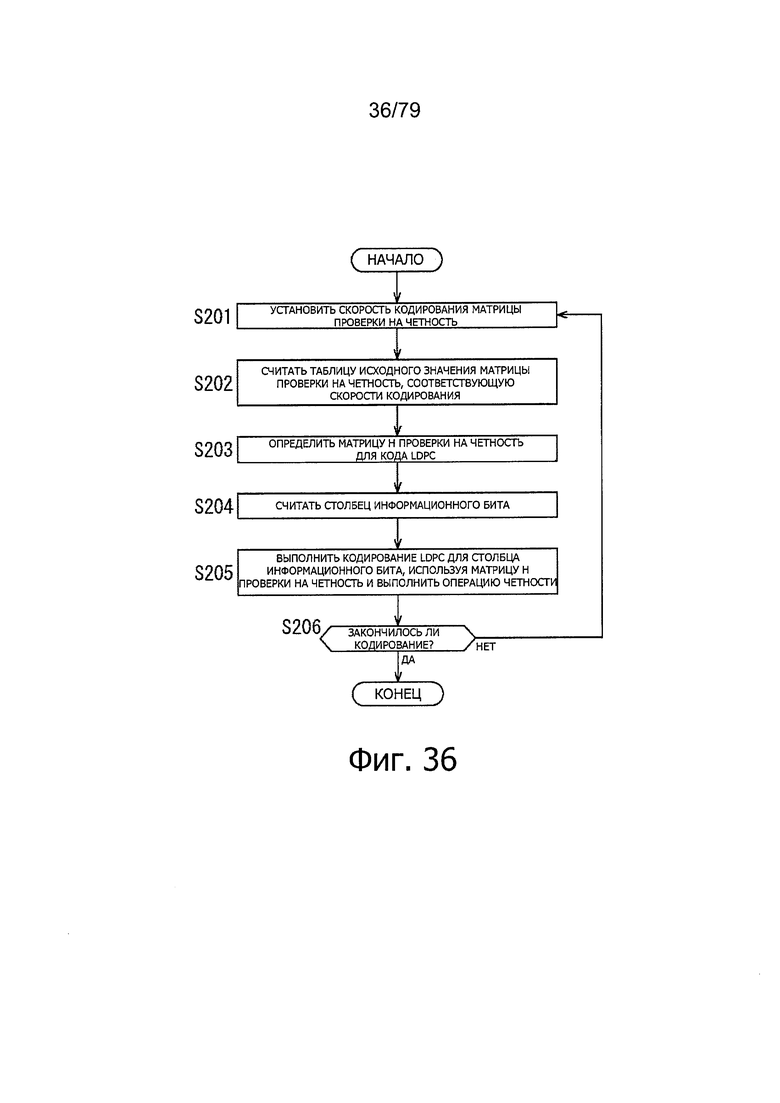

На фиг. 36 показана обработка, иллюстрирующая блок-схему последовательности операций кодера 115 LDPC.

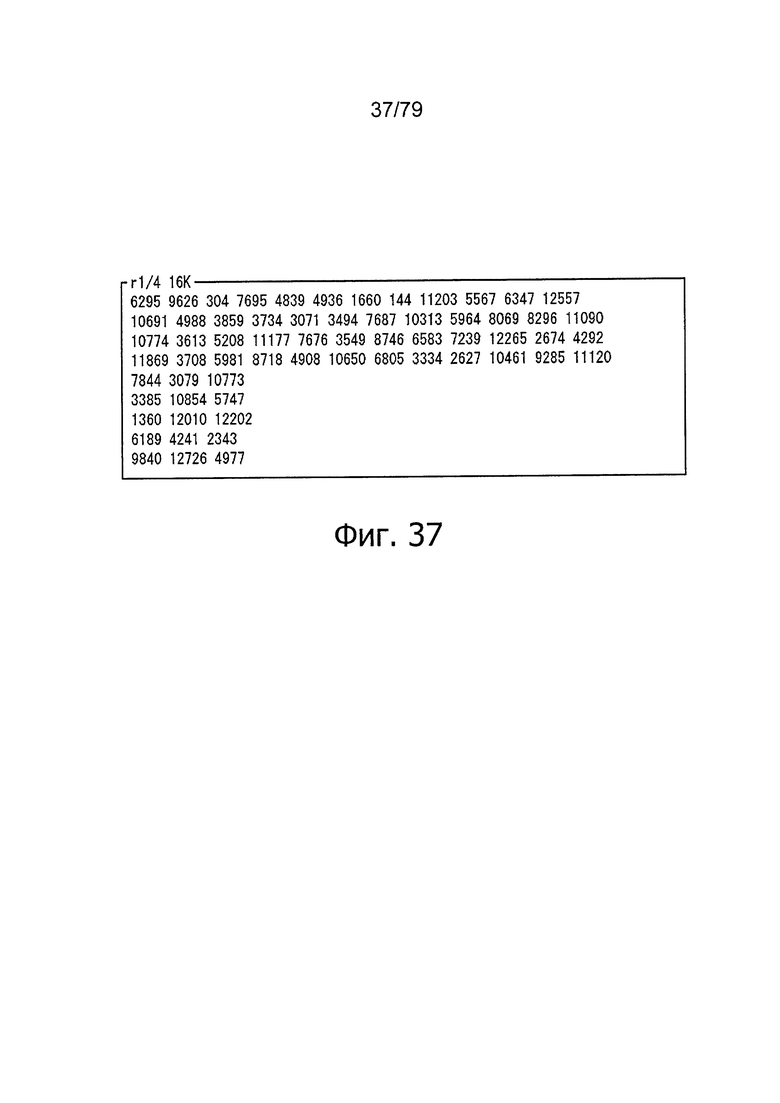

На фиг. 37 представлена иллюстрация примера таблицы исходного значения матрицы проверки на четность, в которой скорость кодирования составляет 1/4, и длина кода равна 16200.

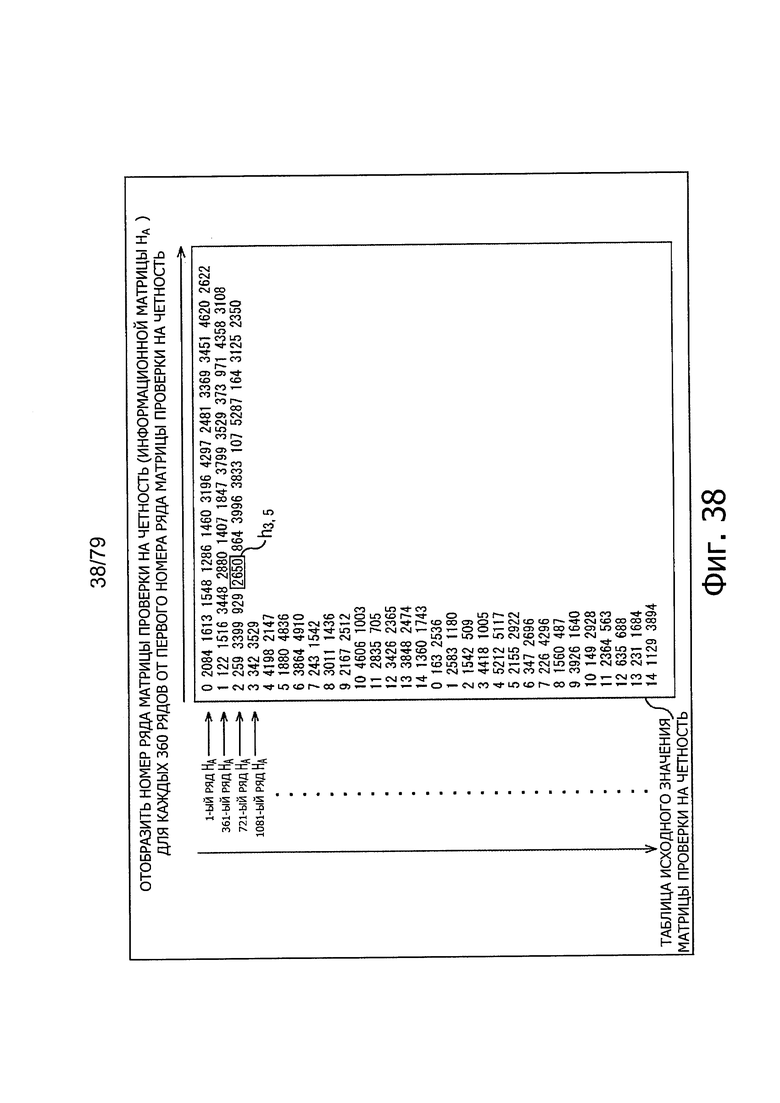

На фиг. 38 представлена иллюстрация способа вычисления матрицы Η проверки на четность из таблицы исходного значения матрицы проверки на четность.

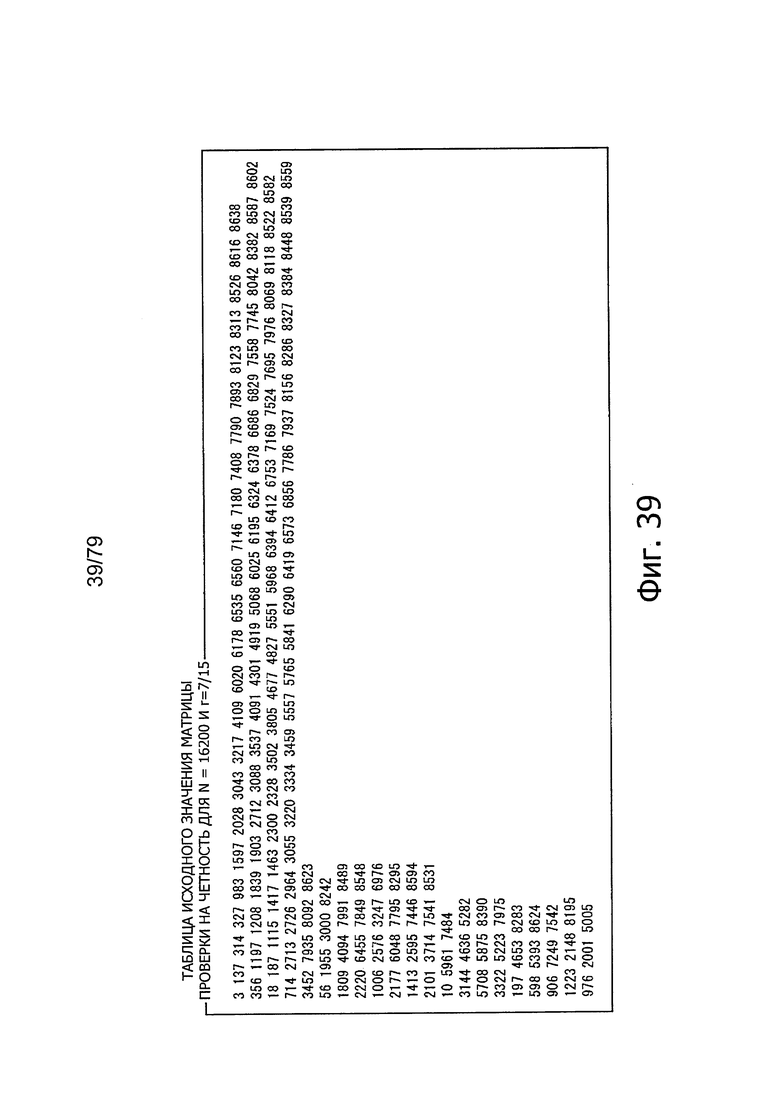

На фиг. 39 представлена иллюстрация примера таблицы исходного значения матрицы проверки на четность кода 16k для Sx при r=7/15.

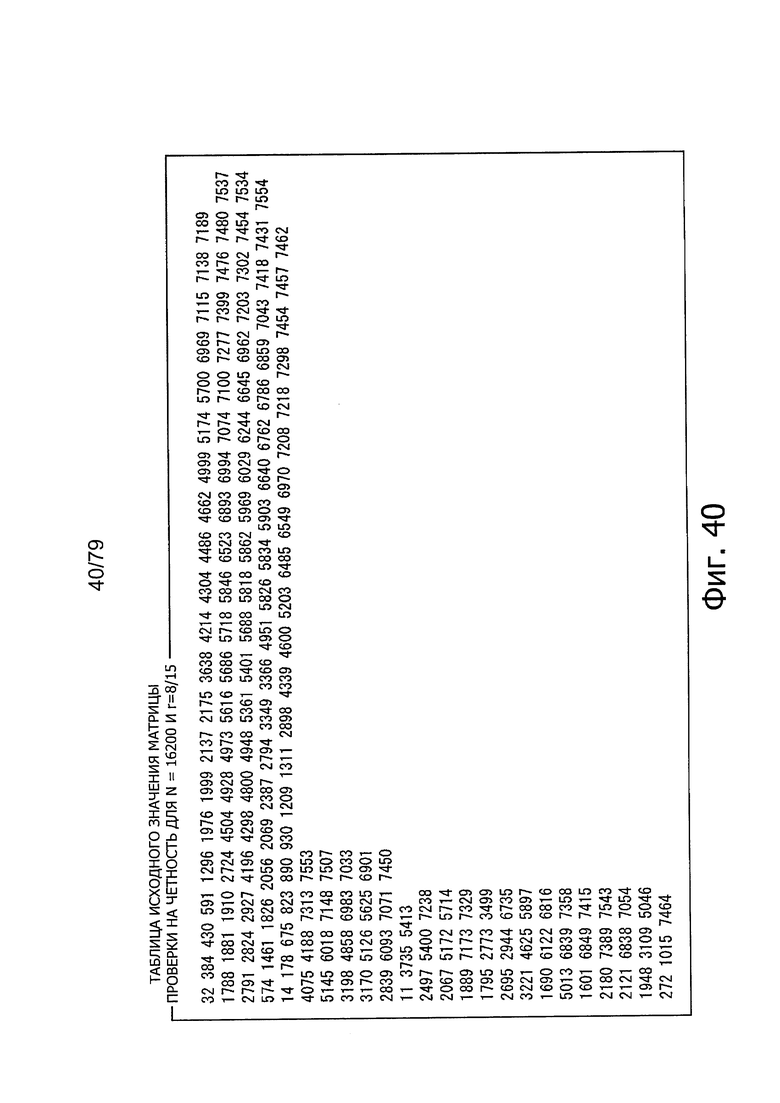

На фиг. 40 представлена иллюстрация примера таблицы исходного значения матрицы проверки на четность кода 16k для Sx при r=8/15.

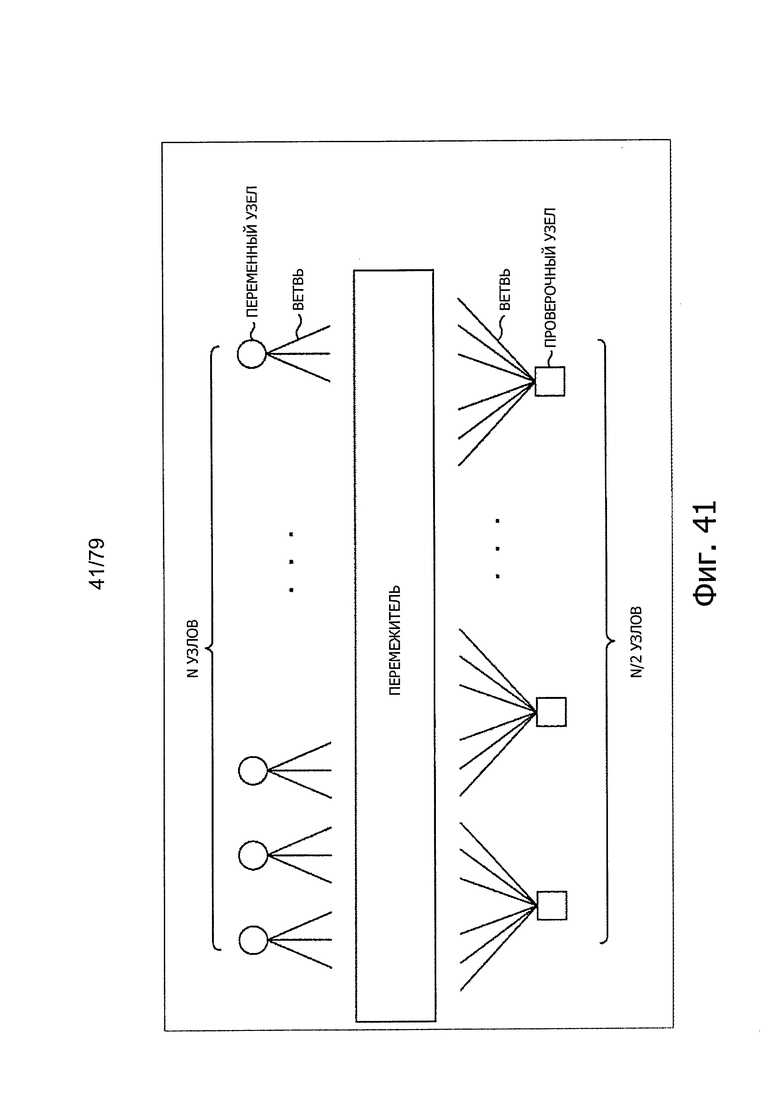

На фиг. 41 представлена иллюстрация примера графа Таннера такой группы последовательности степени, в которой вес столбца равен 3, и вес строки равен 6.

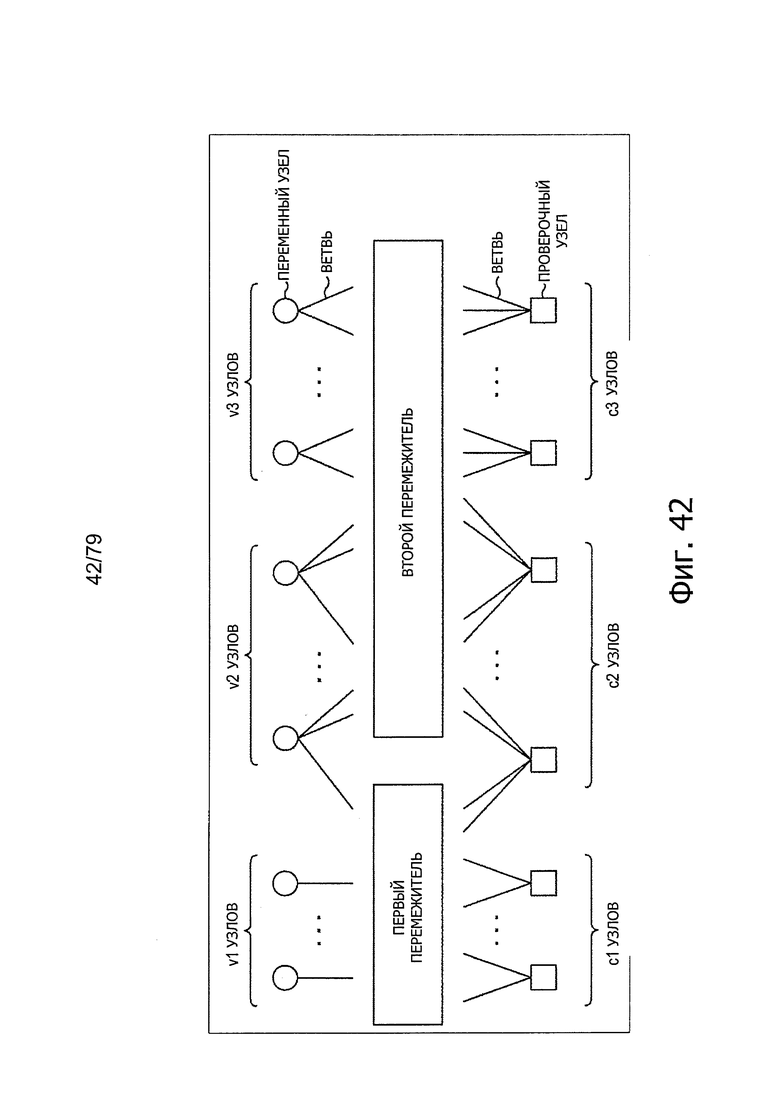

На фиг. 42 представлена иллюстрация примера графа Таннера группы типа с множеством ребер.

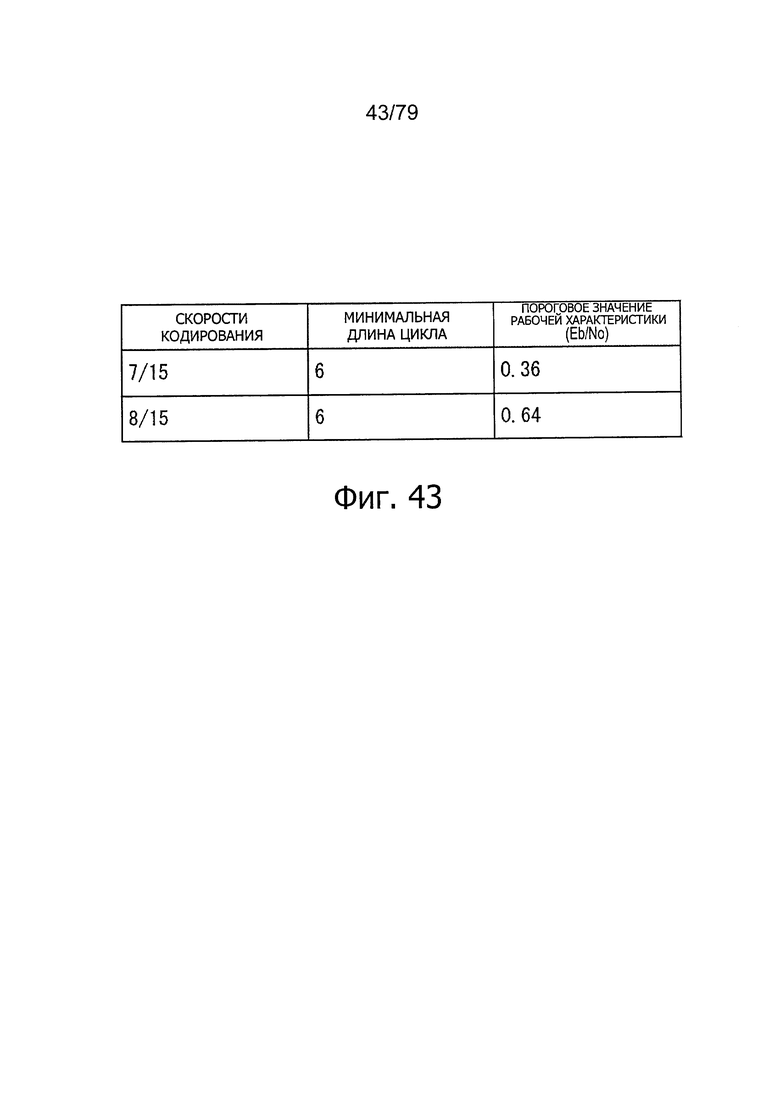

На фиг. 43 представлена иллюстрация минимальной длины цикла и с порогом рабочей характеристики матрицы проверки на четность кода 16k для Sx.

На фиг. 44 представлена иллюстрация матрицы проверки на четность кода 16k для Sx.

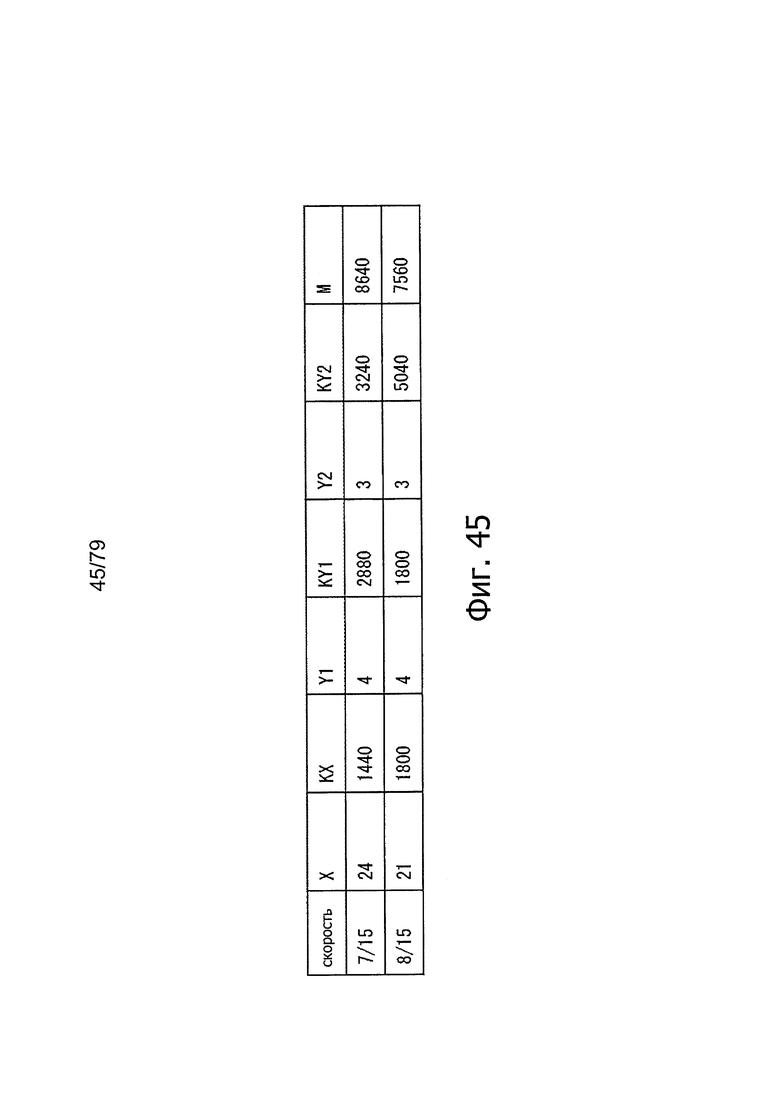

На фиг. 45 представлена иллюстрация матрицы проверки на четность кода 16k для Sx.

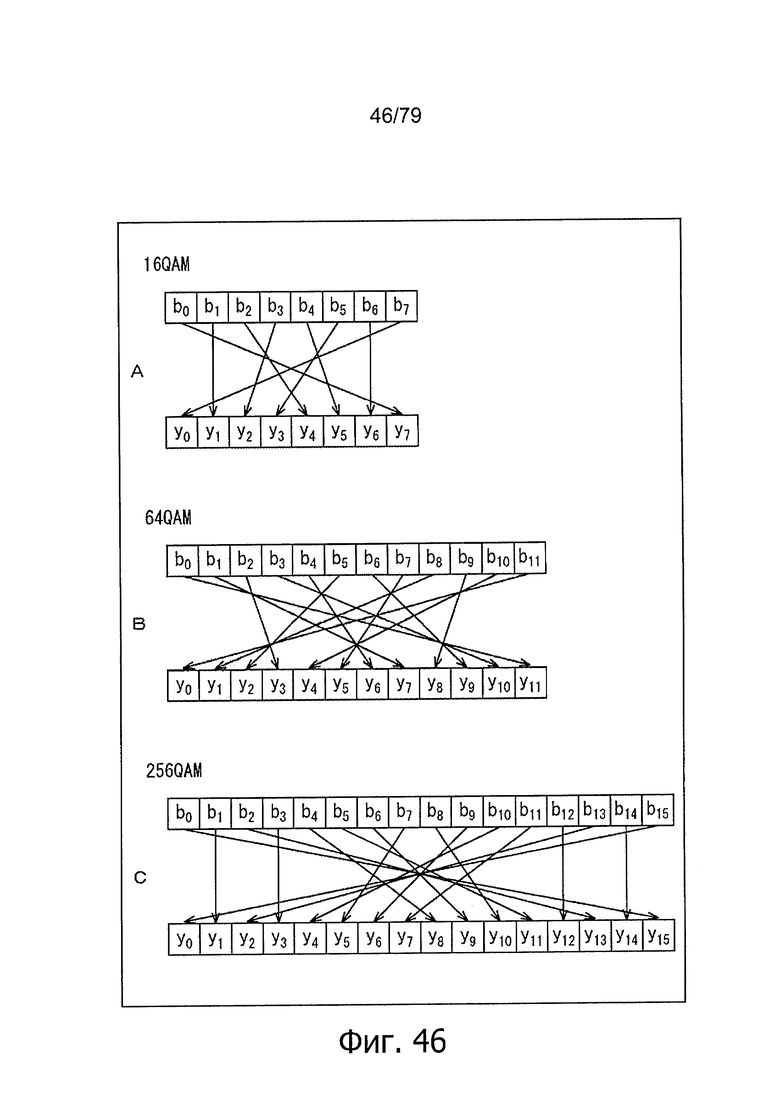

На фиг. 46 представлена иллюстрация обработки взаимного обмена, в соответствии с текущим способом.

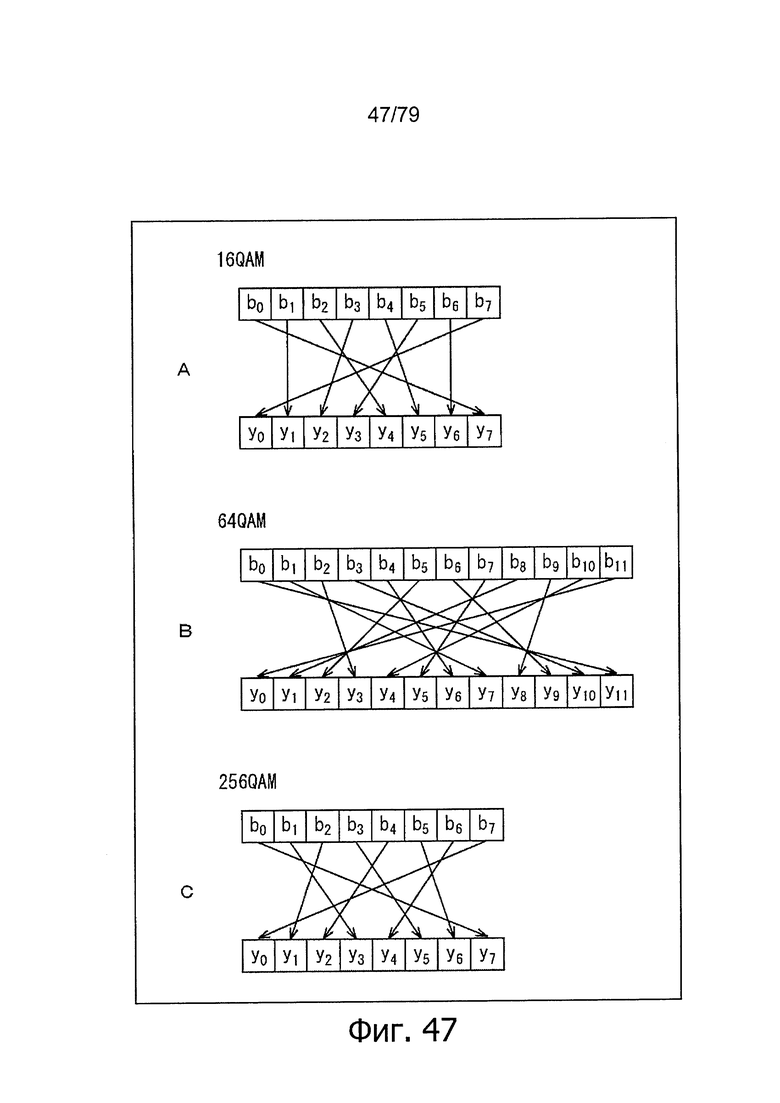

На фиг. 47 представлена иллюстрация обработки взаимного обмена, в соответствии с текущим способом.

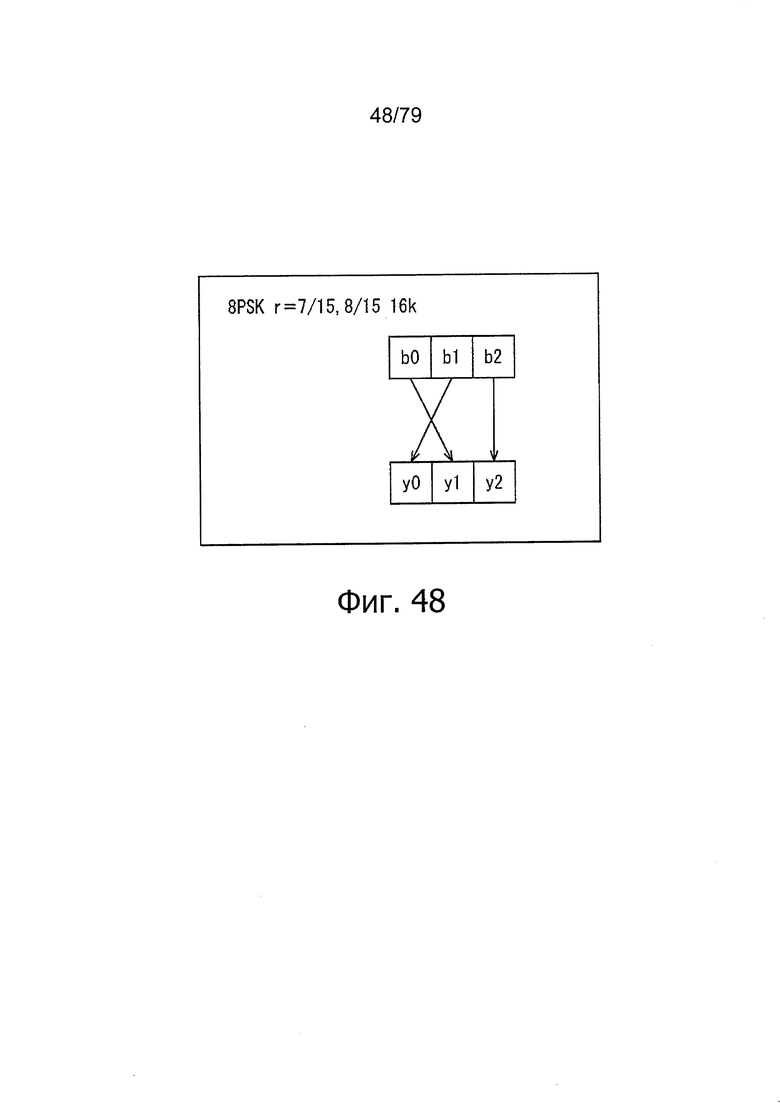

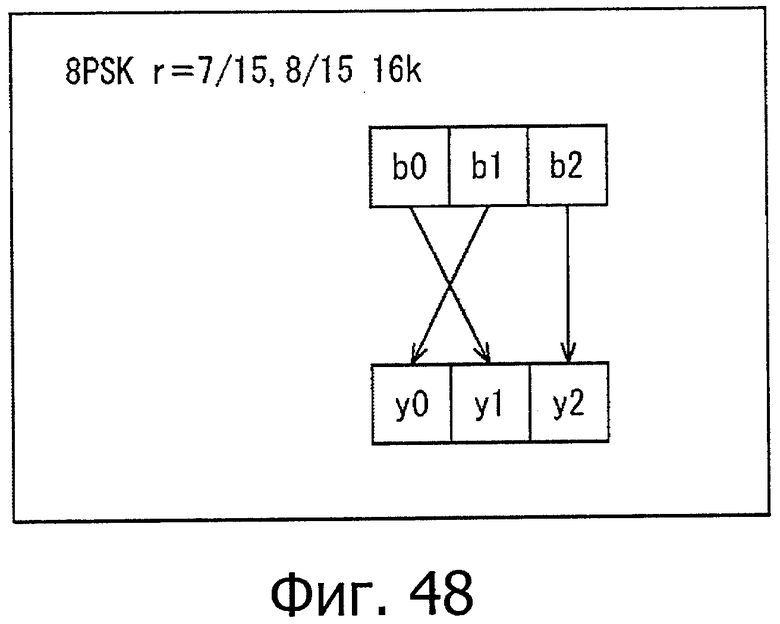

На фиг. 48 представлена иллюстрация первого примера обработки взаимного обмена, в соответствии со способом взаимного обмена для Sx, когда способ модуляции представляет собой 8PSK, и множитель b равен 1, при передаче данных, используя код 16k для Sx.

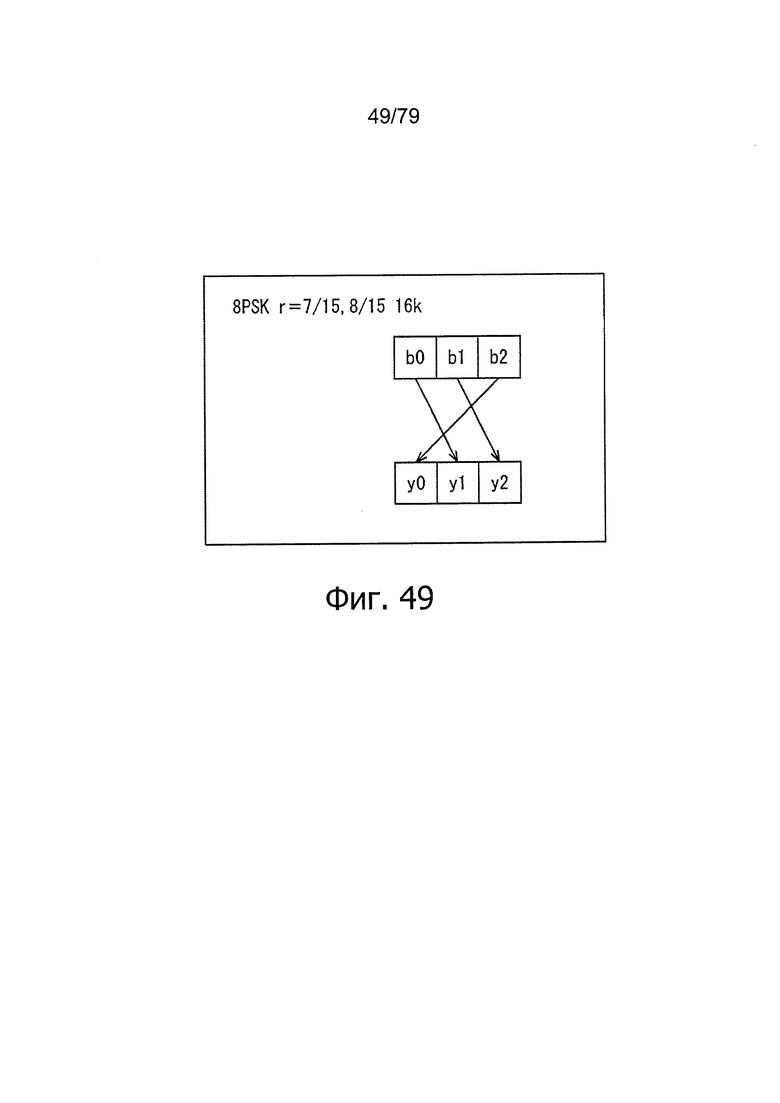

На фиг. 49 представлена иллюстрация второго примера обработки взаимного обмена, в соответствии со способом взаимного обмена для Sx, когда способ модуляции представляет собой 8PSK, и множитель b равен 1, при передаче данных, используя код 16k для Sx.

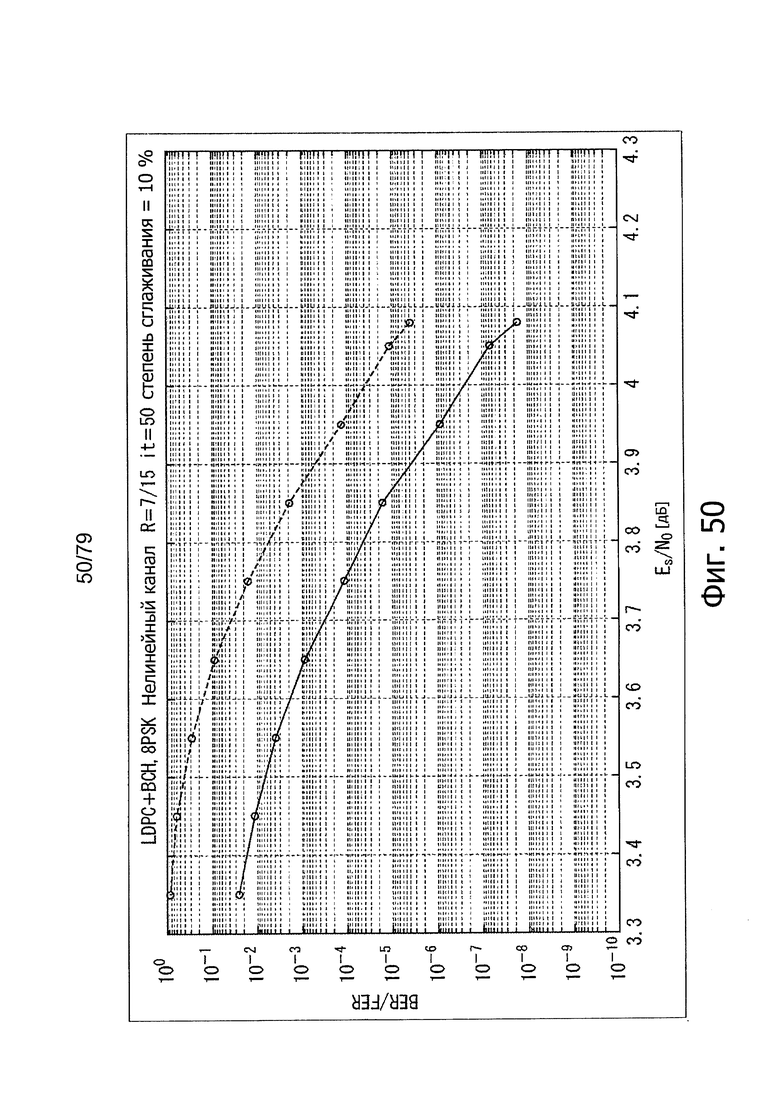

На фиг. 50 представлена иллюстрация результата моделирования для измерения BER/FER путем моделирования.

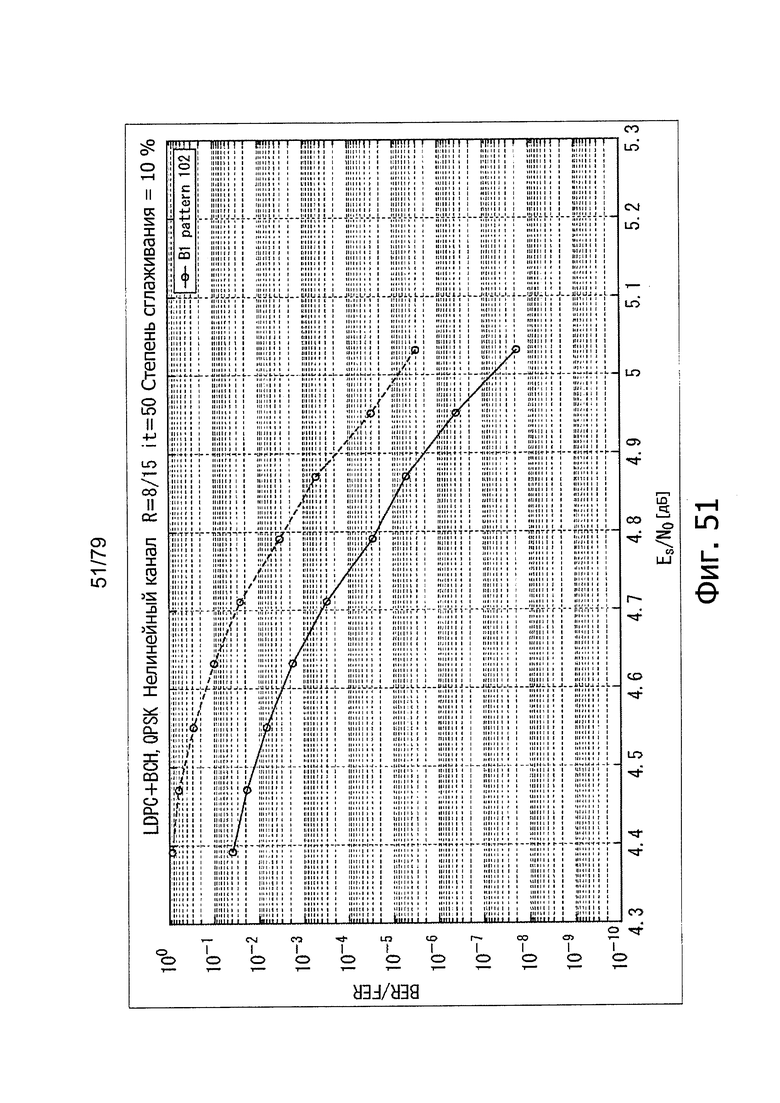

На фиг. 51 представлена иллюстрация результата моделирования для измерения BER/FER путем моделирования.

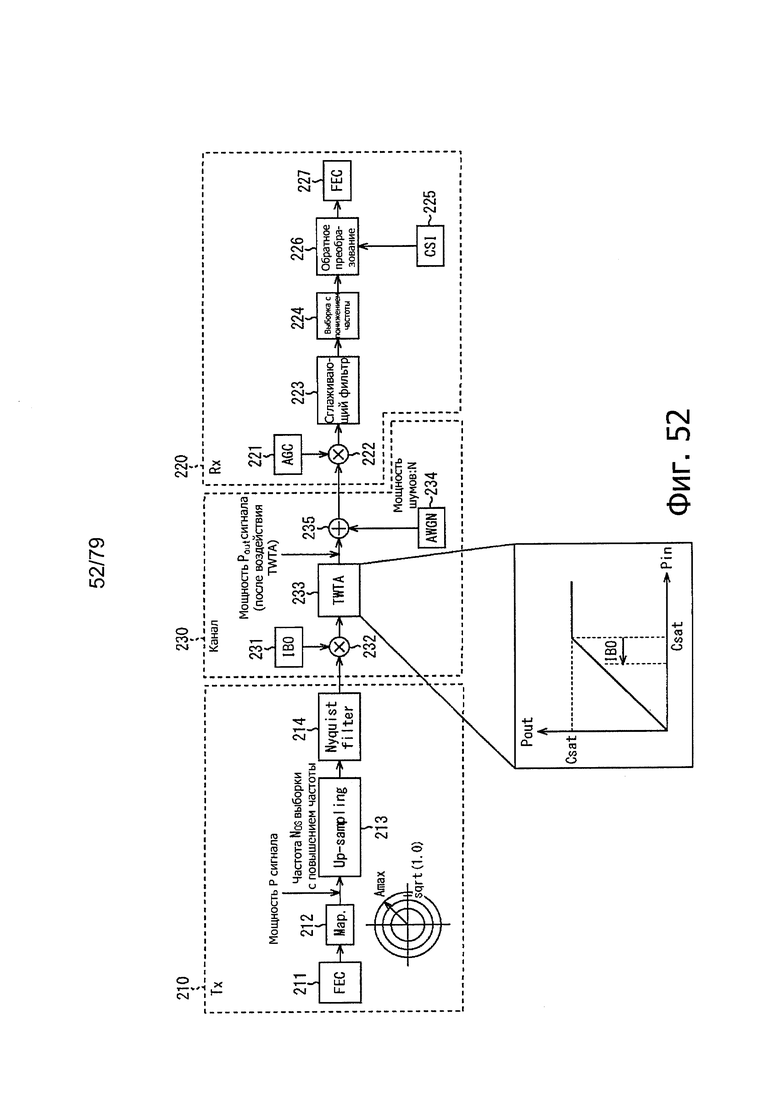

На фиг. 52 показана блок-схема, поясняющая модель системы передачи для системы передачи, в которой используется моделирование.

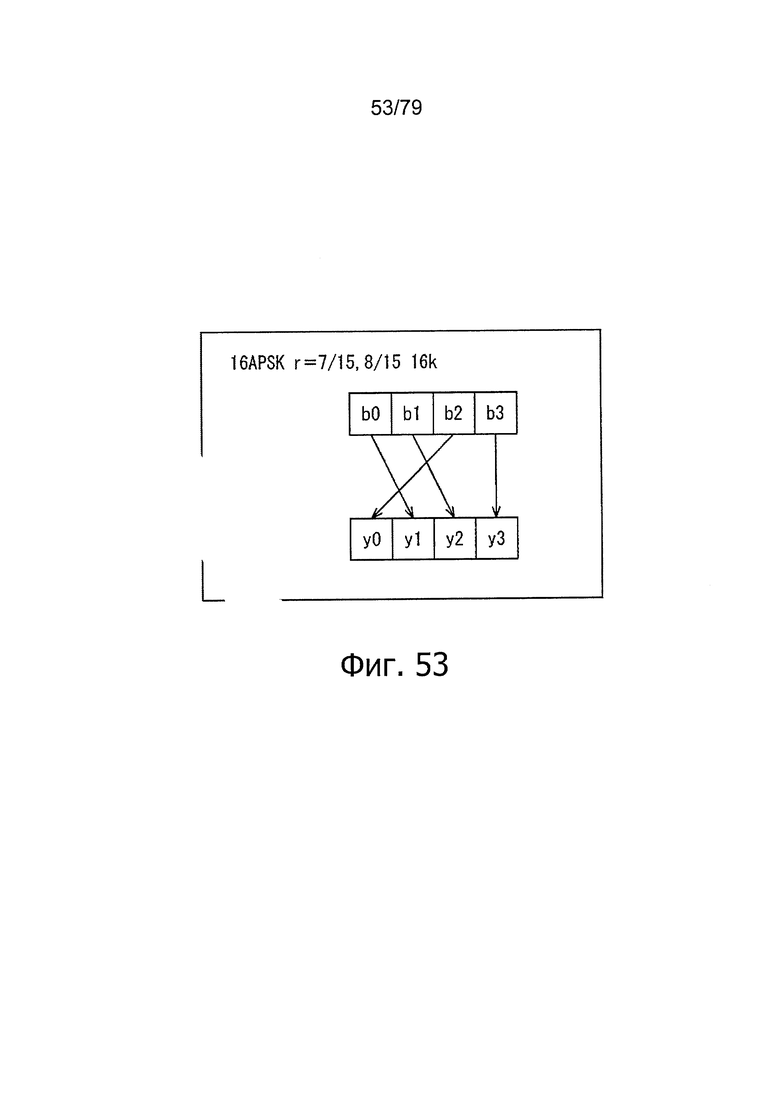

На фиг. 53 представлена иллюстрация первого примера обработки взаимного обмена, в соответствии со способом взаимного обмена для Sx, когда способ модуляции представляет собой 16APSK, и множитель b равен 1, при передаче данных, используя код 16k для Sx.

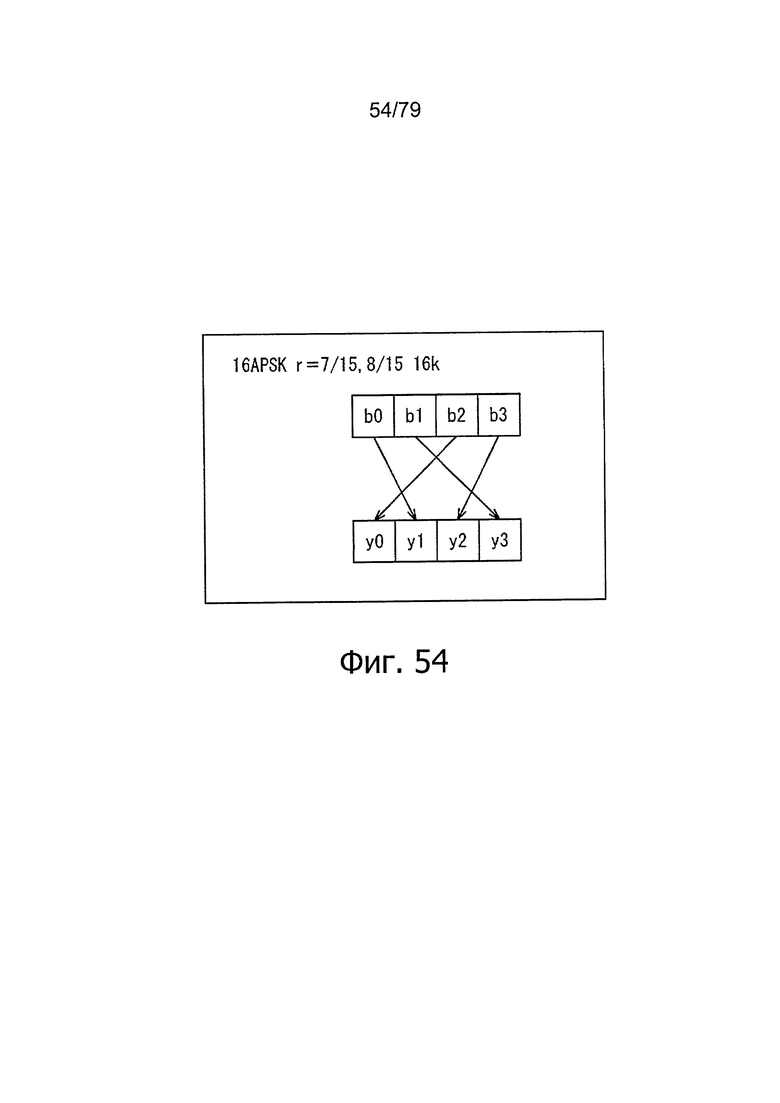

На фиг. 54 представлена иллюстрация второго примера обработки взаимного обмена, в соответствии со способом взаимного обмена для Sx, когда способ модуляции представляет собой 16APSK, и множитель b равен 1, при передаче данных, используя код 16k для Sx.

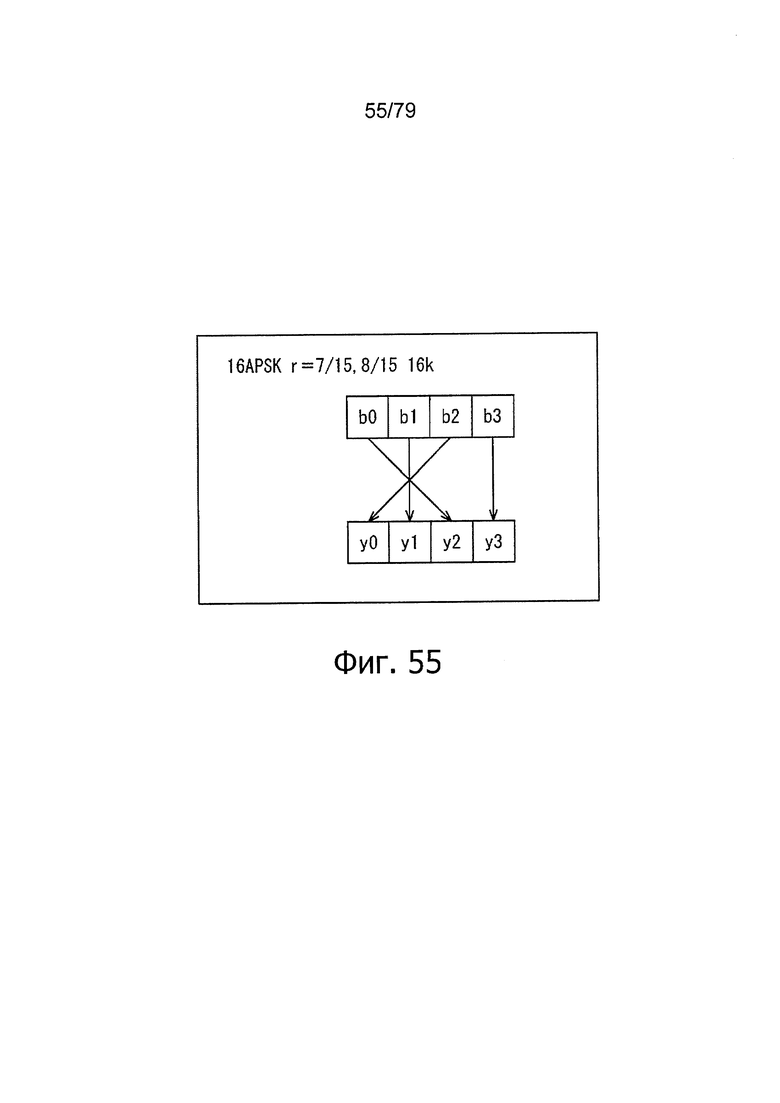

На фиг. 55 представлена иллюстрация третьего примера обработки взаимного обмена, в соответствии со способом взаимного обмена для Sx, когда способ модуляции представляет собой 16APSK, и множитель b равен 1, при передаче данных, используя код 16k для Sx.

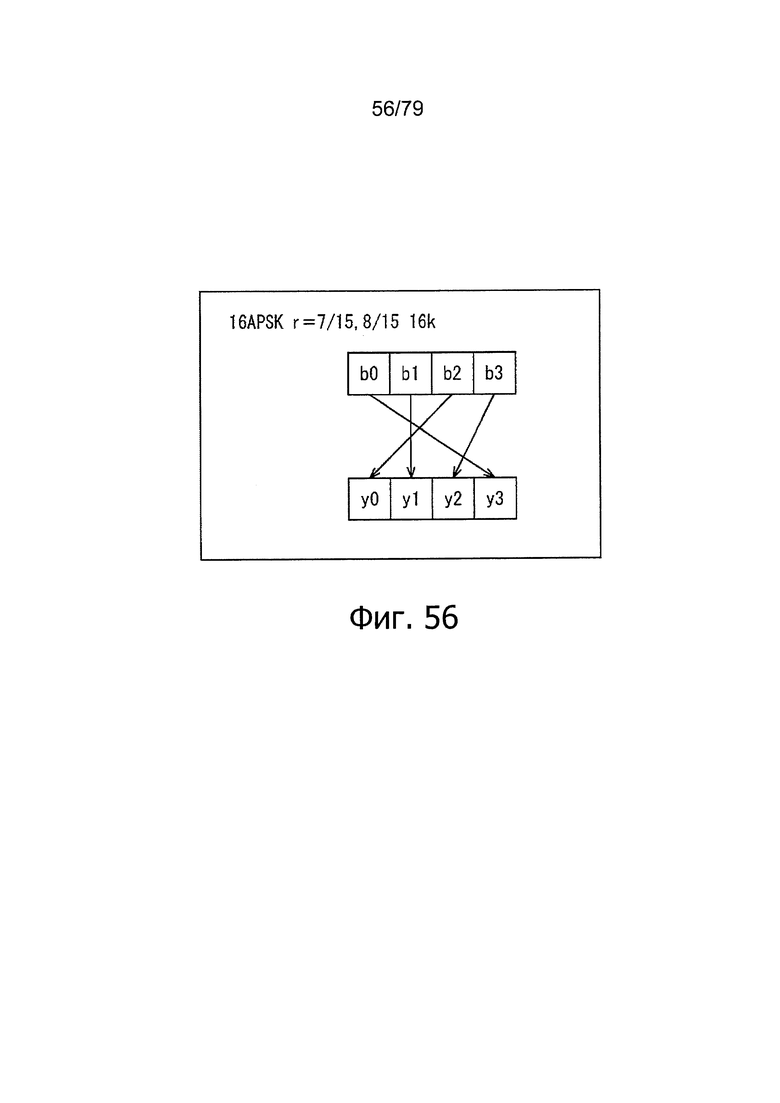

На фиг. 56 представлена иллюстрация четвертого примера обработки взаимного обмена, в соответствии со способом взаимного обмена для Sx, когда способ модуляции представляет собой 16APSK, и множитель b равен 1, при передаче данных, используя код 16k для Sx.

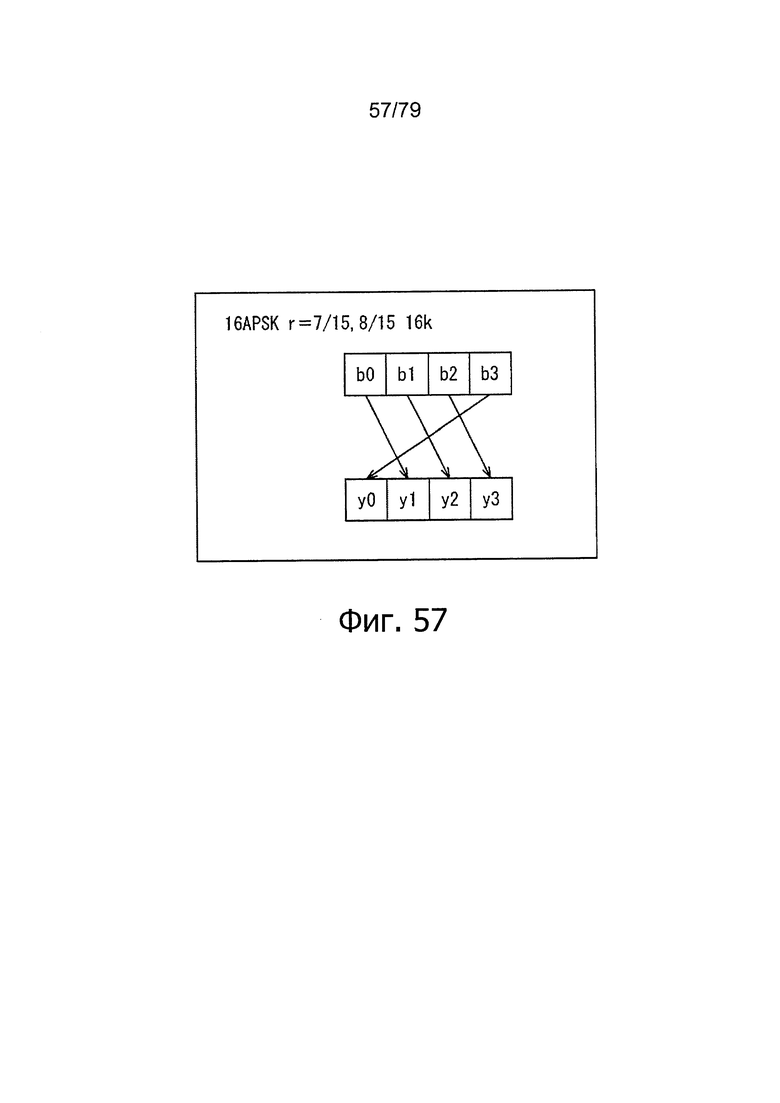

На фиг. 57 представлена иллюстрация пятого примера обработки взаимного обмена, в соответствии со способом взаимного обмена для Sx, когда способ модуляции представляет собой 16APSK, и множитель b равен 1, при передаче данных, используя код 16k для Sx.

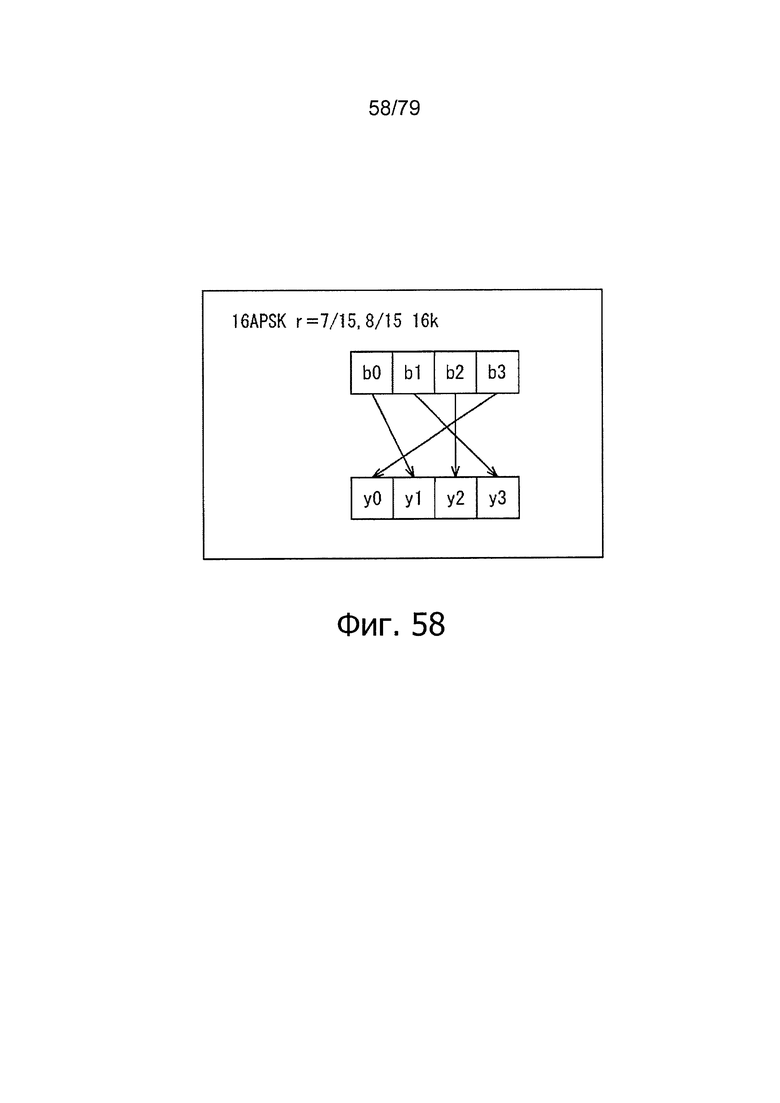

На фиг. 58 представлена иллюстрация шестого примера обработки взаимного обмена, в соответствии со способом взаимного обмена для Sx, когда способ модуляции представляет собой 16APSK, и множитель b равен 1, при передаче данных, используя код 16k для Sx.

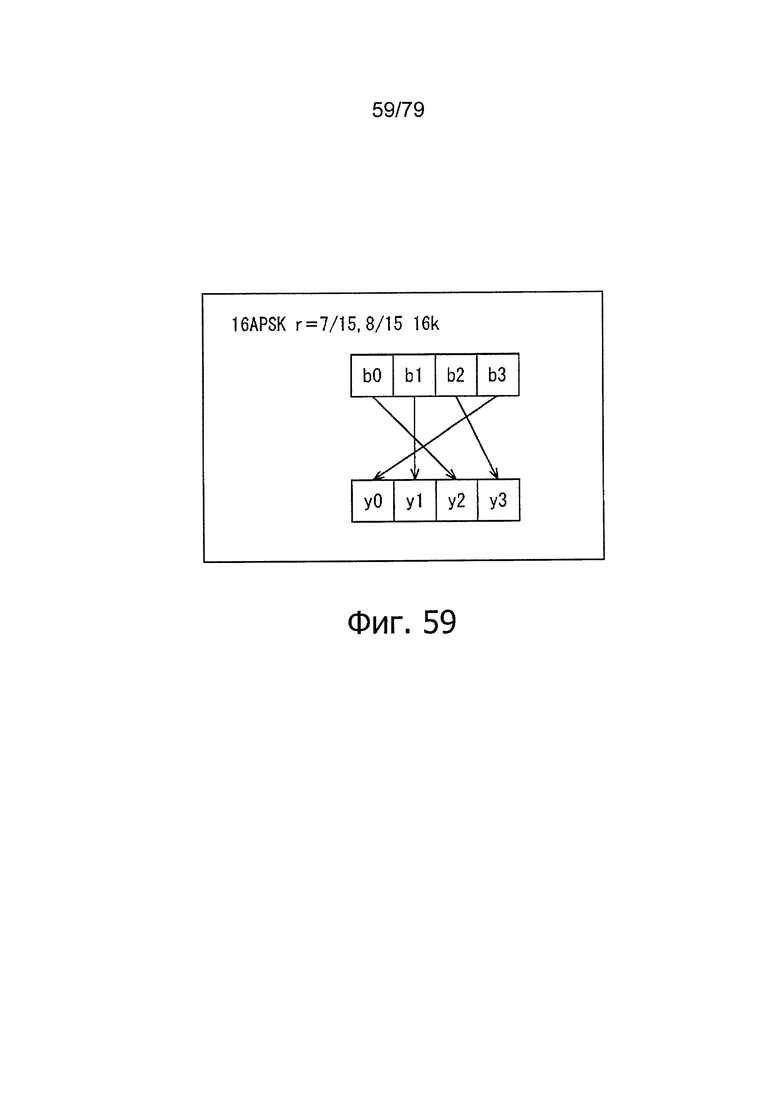

На фиг. 59 представлена иллюстрация седьмого примера обработки взаимного обмена, в соответствии со способом взаимного обмена для Sx, когда способ модуляции представляет собой 16APSK, и множитель b равен 1, при передаче данных, используя код 16k для Sx.

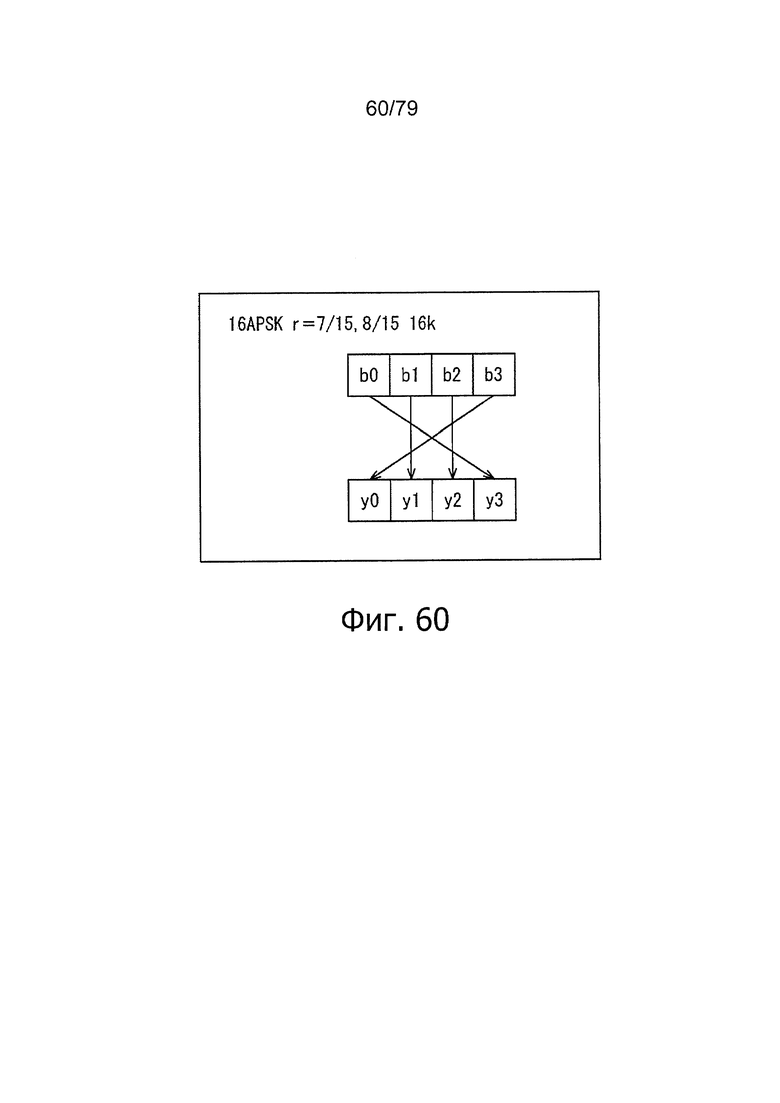

На фиг. 60 представлена иллюстрация восьмого примера обработки взаимного обмена, в соответствии со способом взаимного обмена для Sx, когда способ модуляции представляет собой 16APSK, и множитель b равен 1, при передаче данных, используя код 16k для Sx.

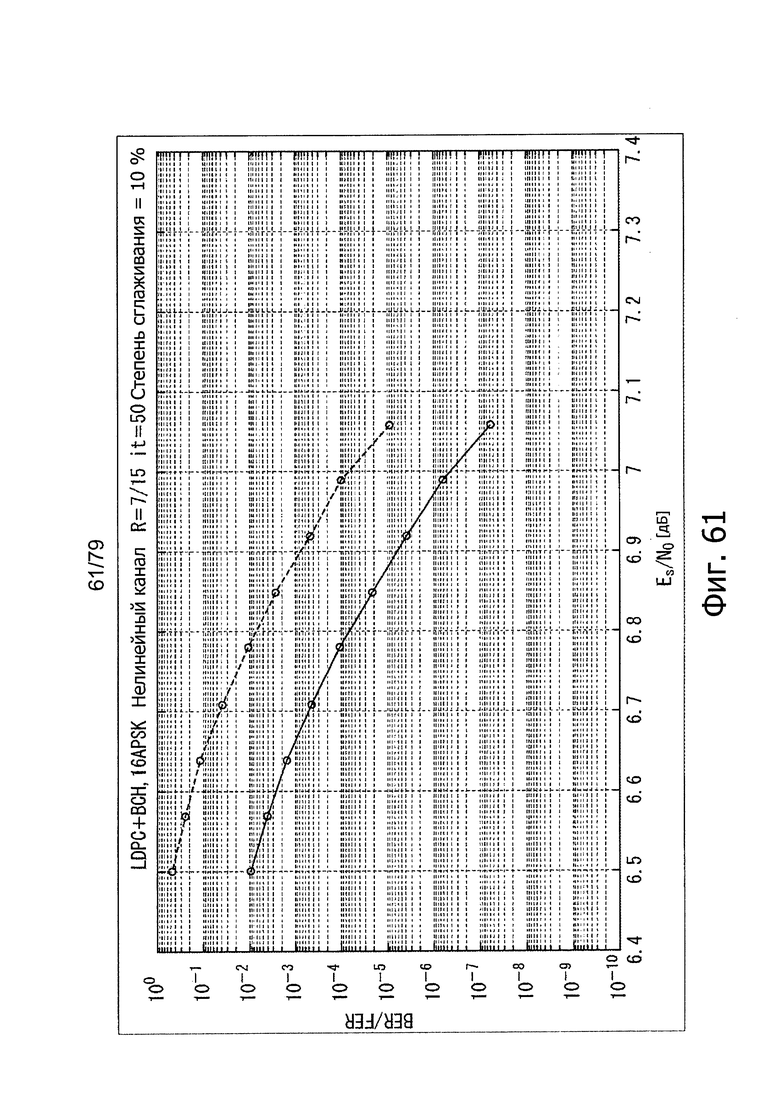

На фиг. 61 представлена иллюстрация результата моделирования для измерения BER/FER путем моделирования.

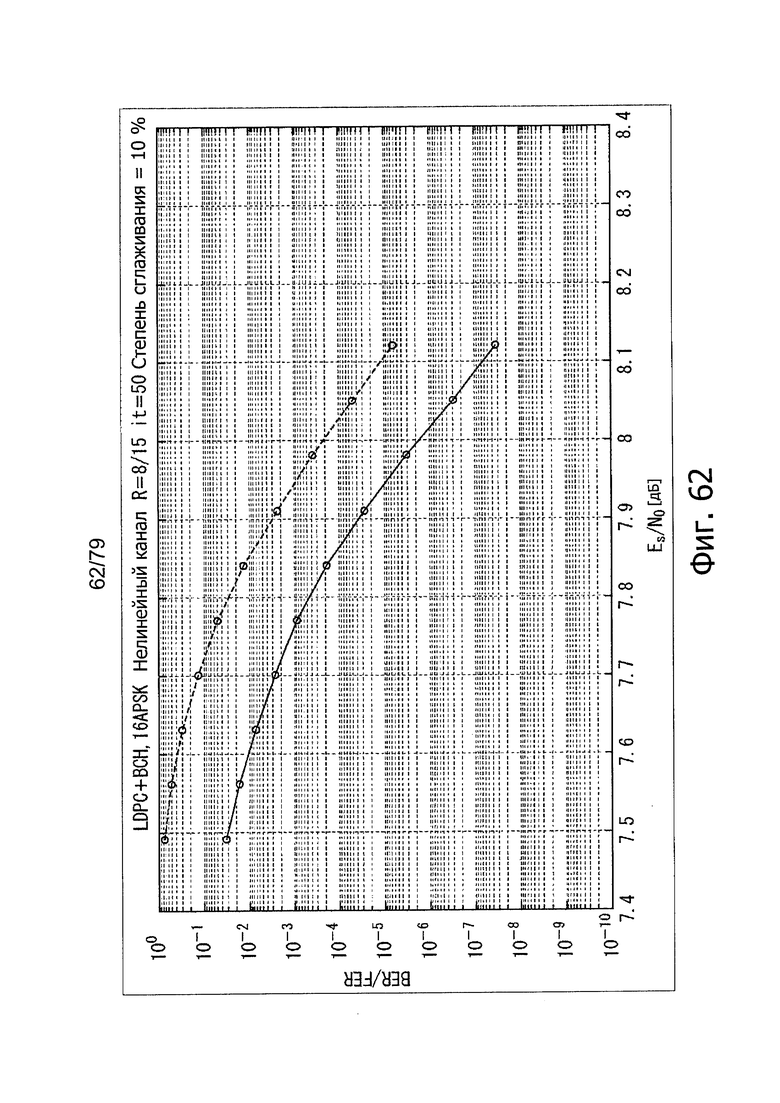

На фиг. 62 представлена иллюстрация результата моделирования для измерения BER/FER путем моделирования.

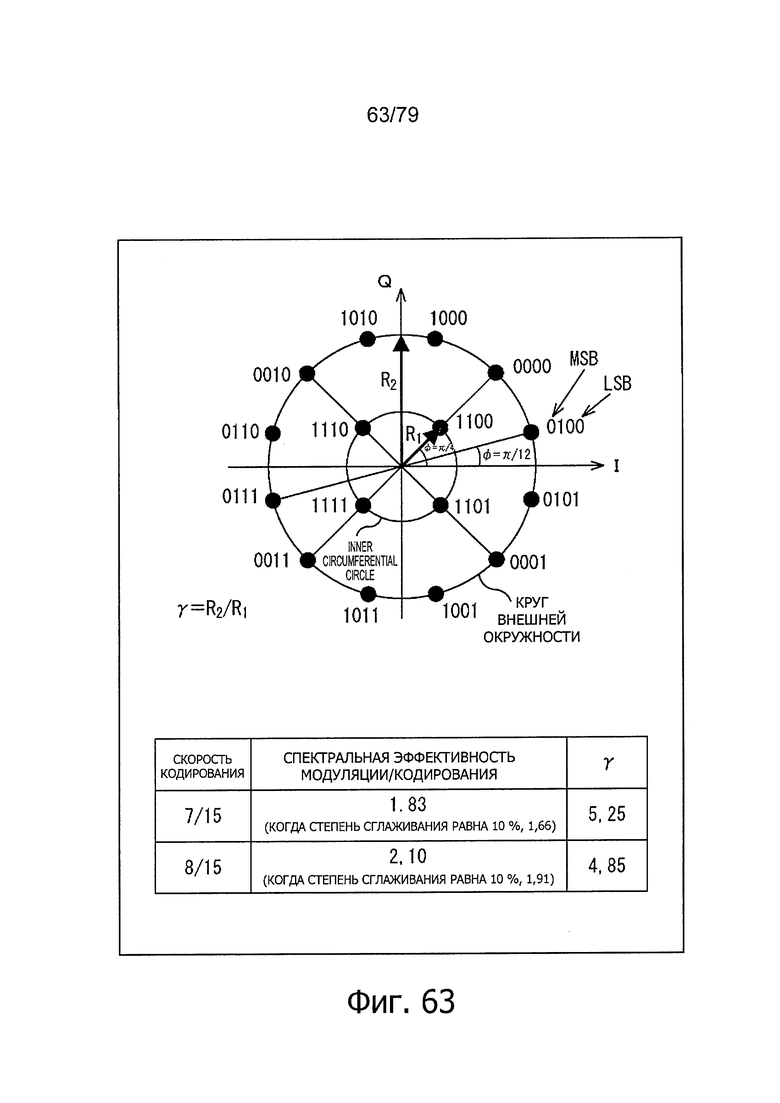

На фиг. 63 представлена иллюстрация примера компоновки точек сигнала 16APSK и отношения γ радиуса, когда 16APSK принят как способ модуляции.

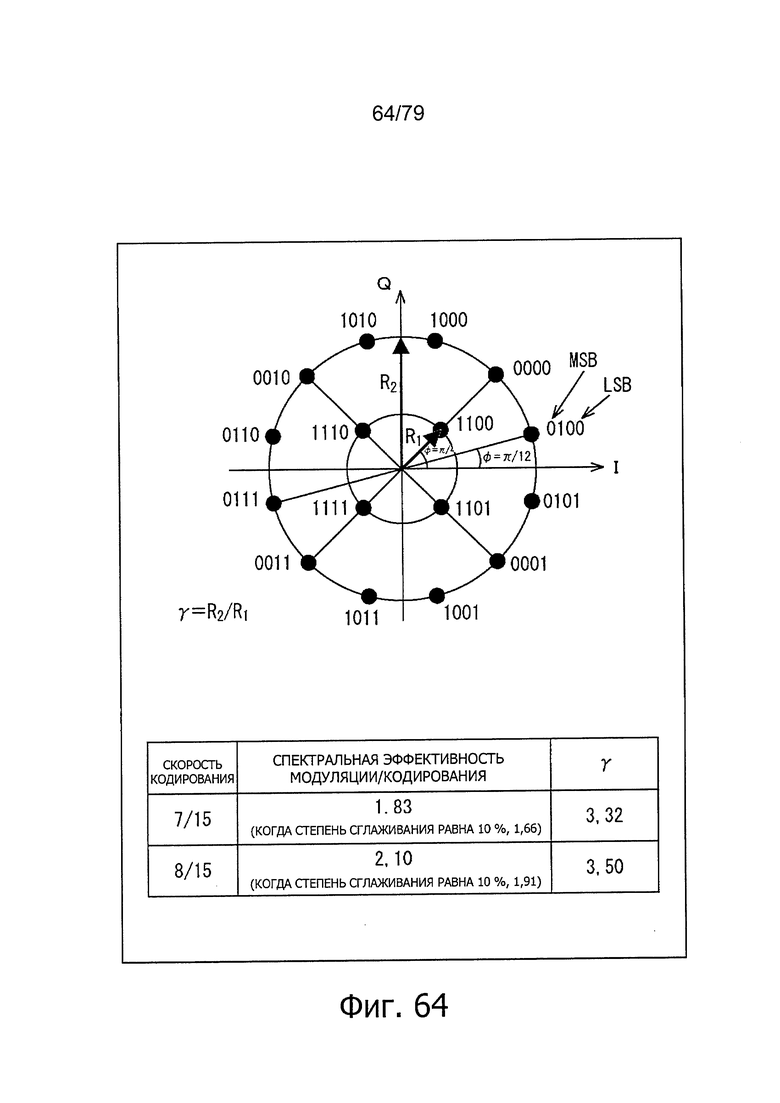

На фиг. 64 представлена иллюстрация примера компоновки точек сигнала 16APSK и отношения γ радиуса, когда 16APSK принят как способ модуляции.

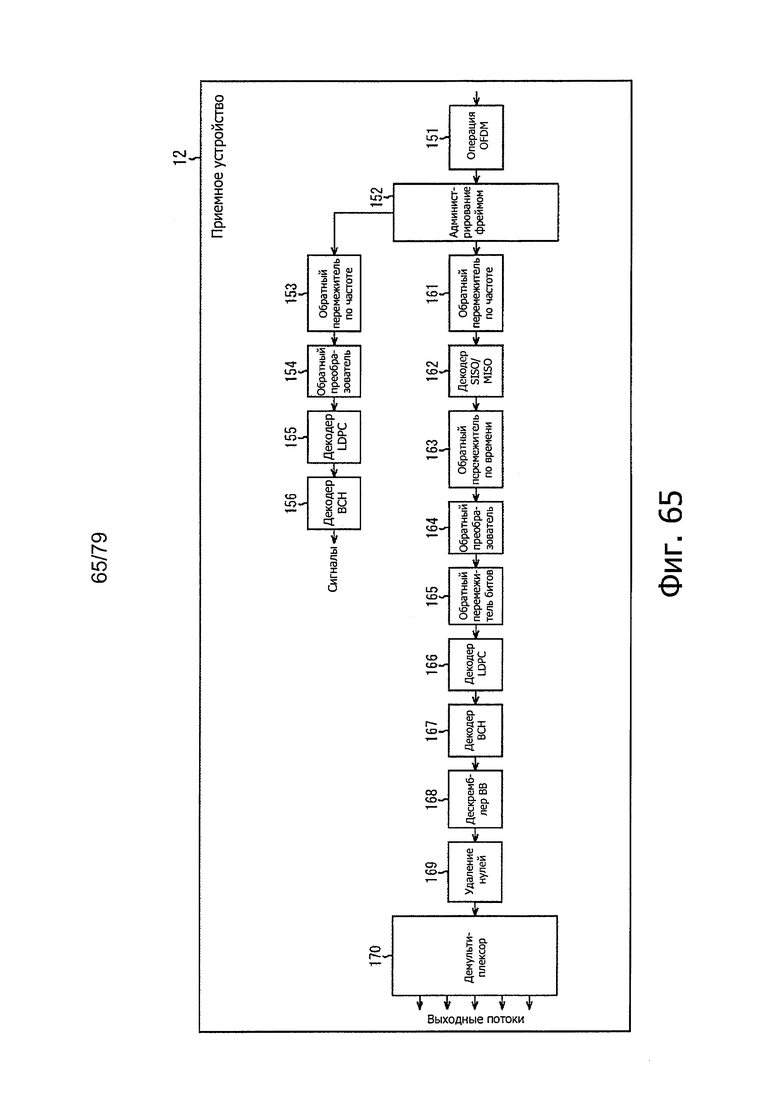

На фиг. 65 показана блок-схема, поясняющая пример конфигурации приемного устройства 12 на фиг. 7.

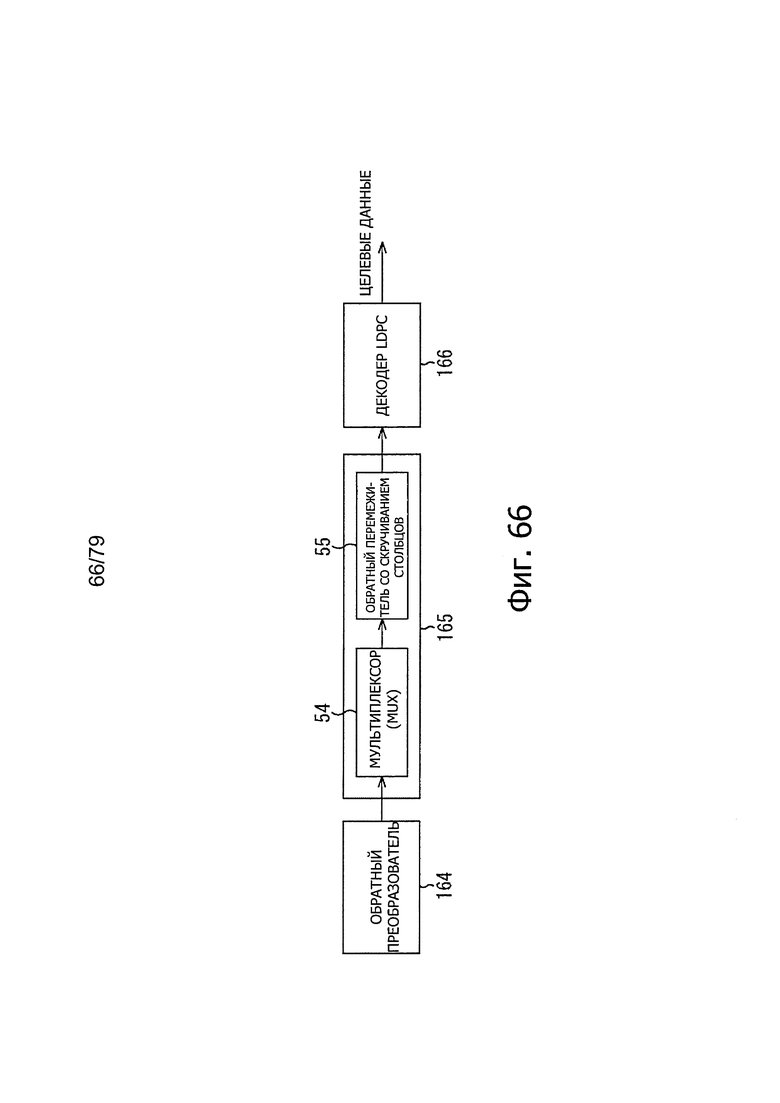

На фиг. 66 показана блок-схема, поясняющая пример конфигурации обратного перемежителя 165 битов

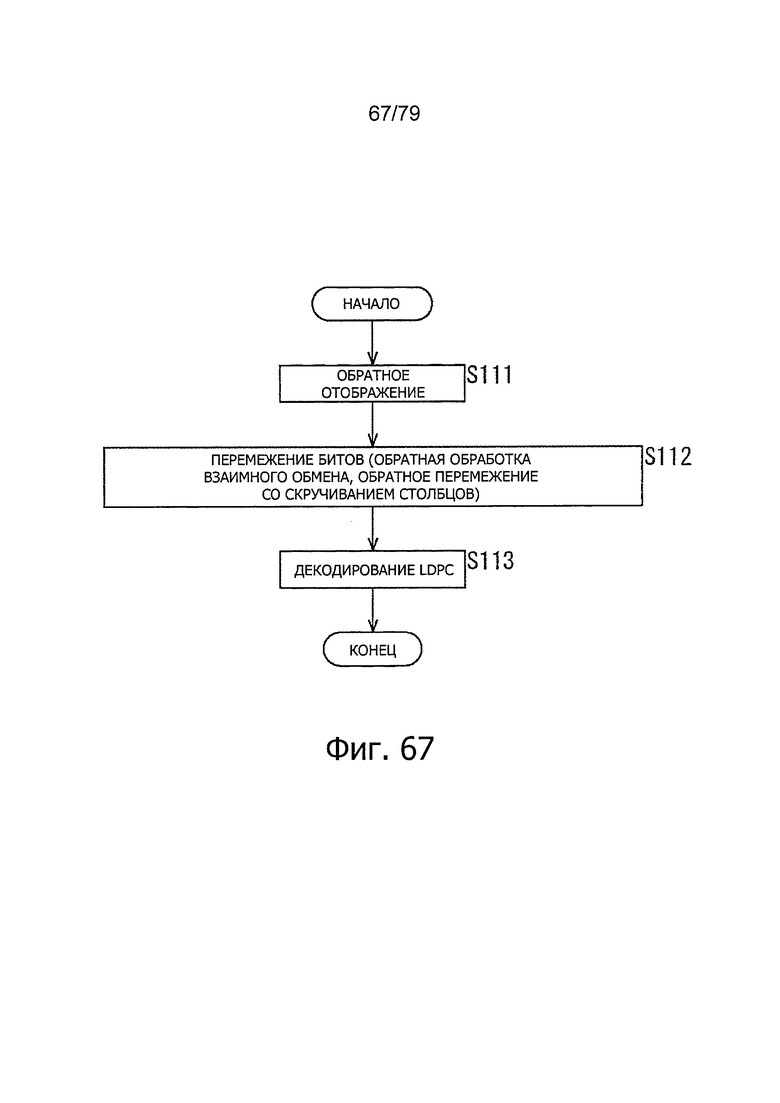

На фиг. 67 показана блок-схема последовательности операций, иллюстрирующая, обработку, выполняемую обратным преобразователем 164, обратным перемежителем 165 битов и декодером 166 LDPC.

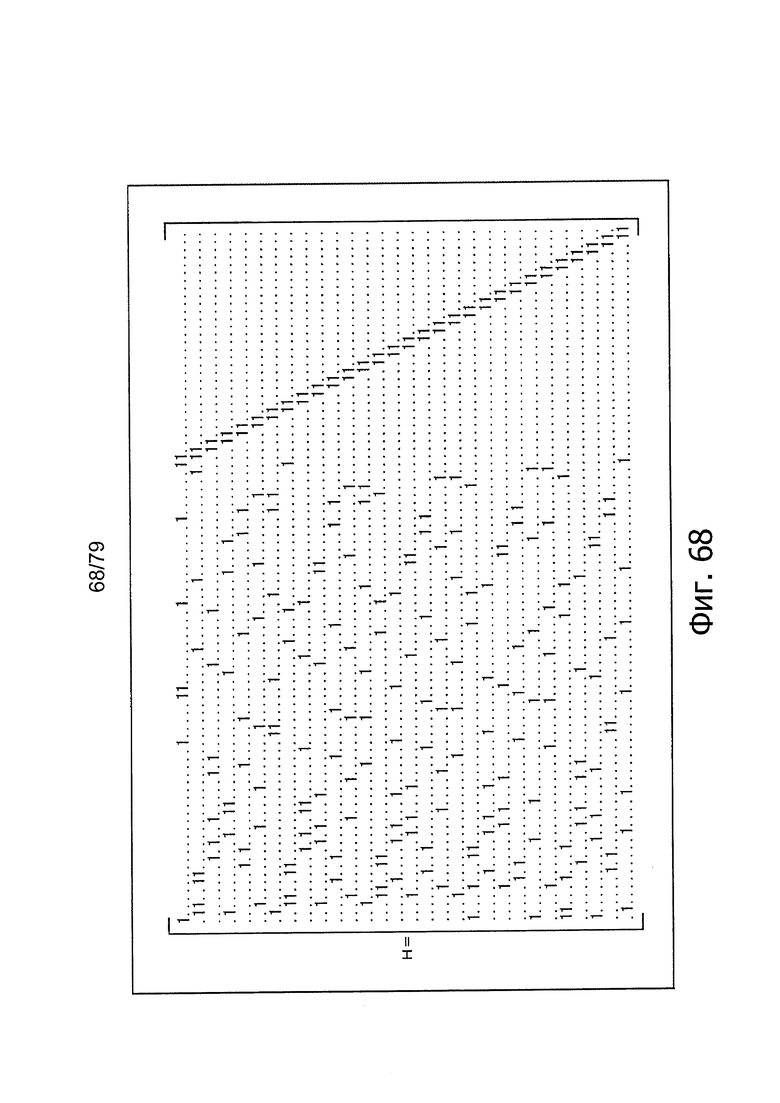

На фиг. 68 представлена иллюстрация примера матрицы проверки на четность кода LDPC.

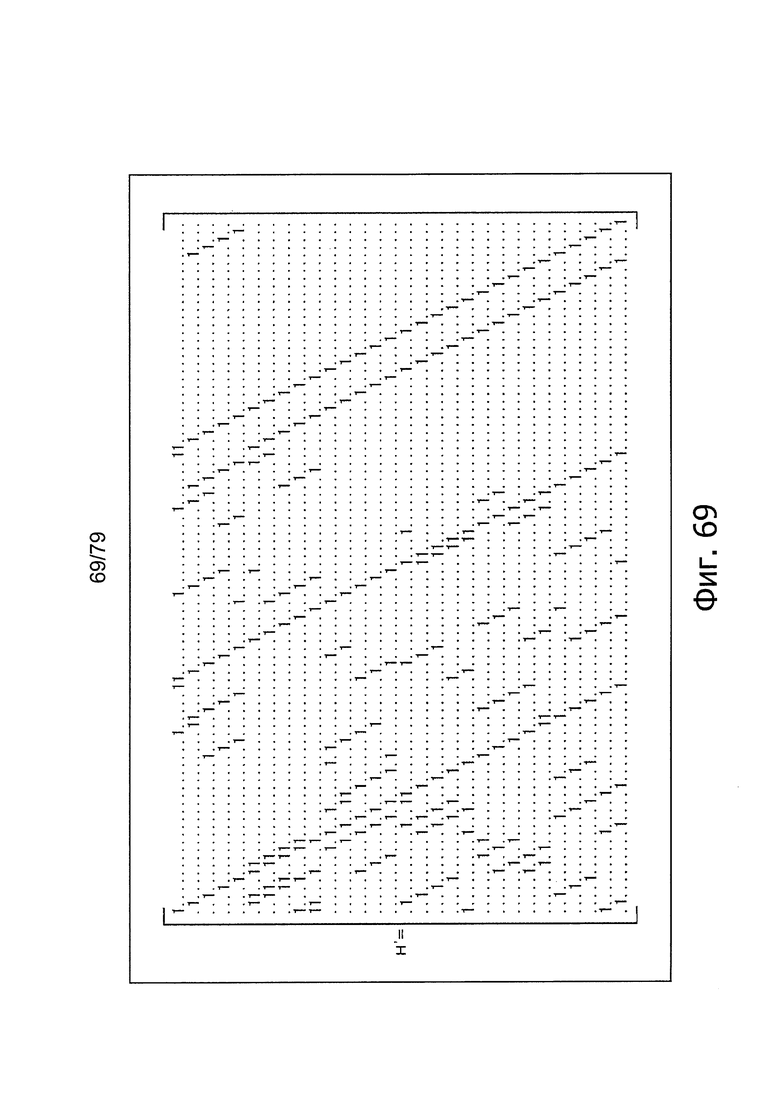

На фиг. 69 представлена иллюстрация матрицы (матрица проверки на четность), полученной при выполнении замены строки и замен столбца в отношении матрицы проверки на четность.

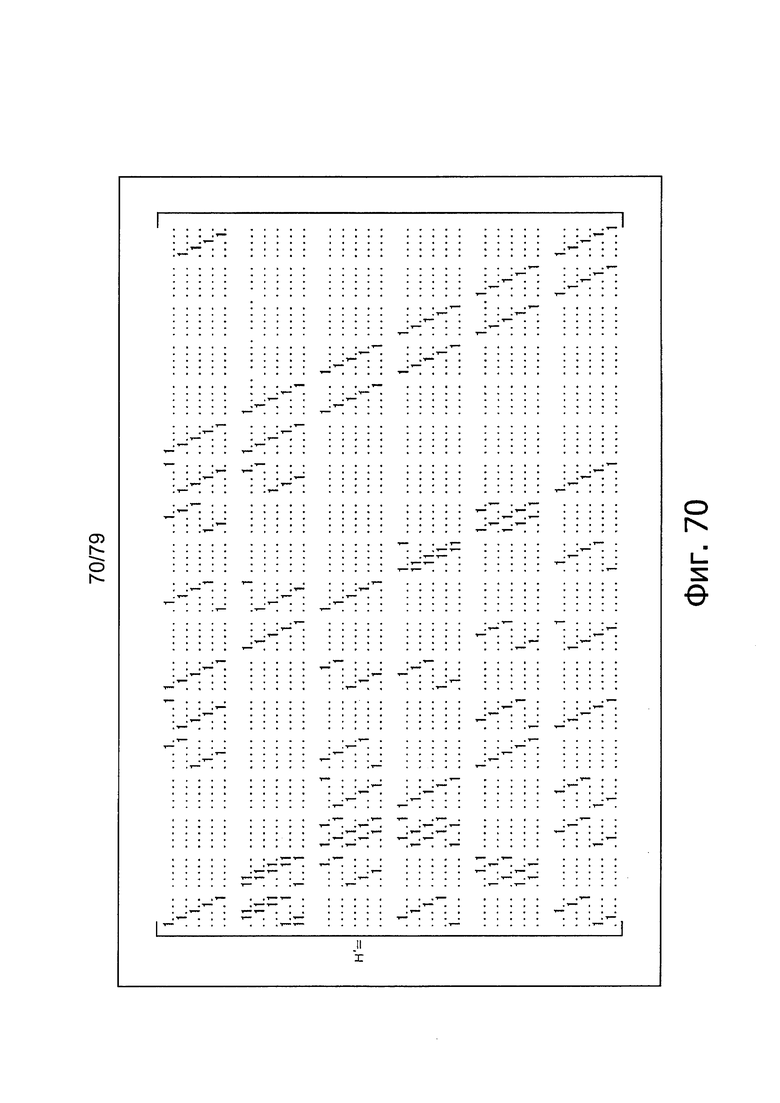

На фиг. 70 представлена иллюстрация матрицы проверки на четность, которая была разнесена в модулях матриц размером 5×5.

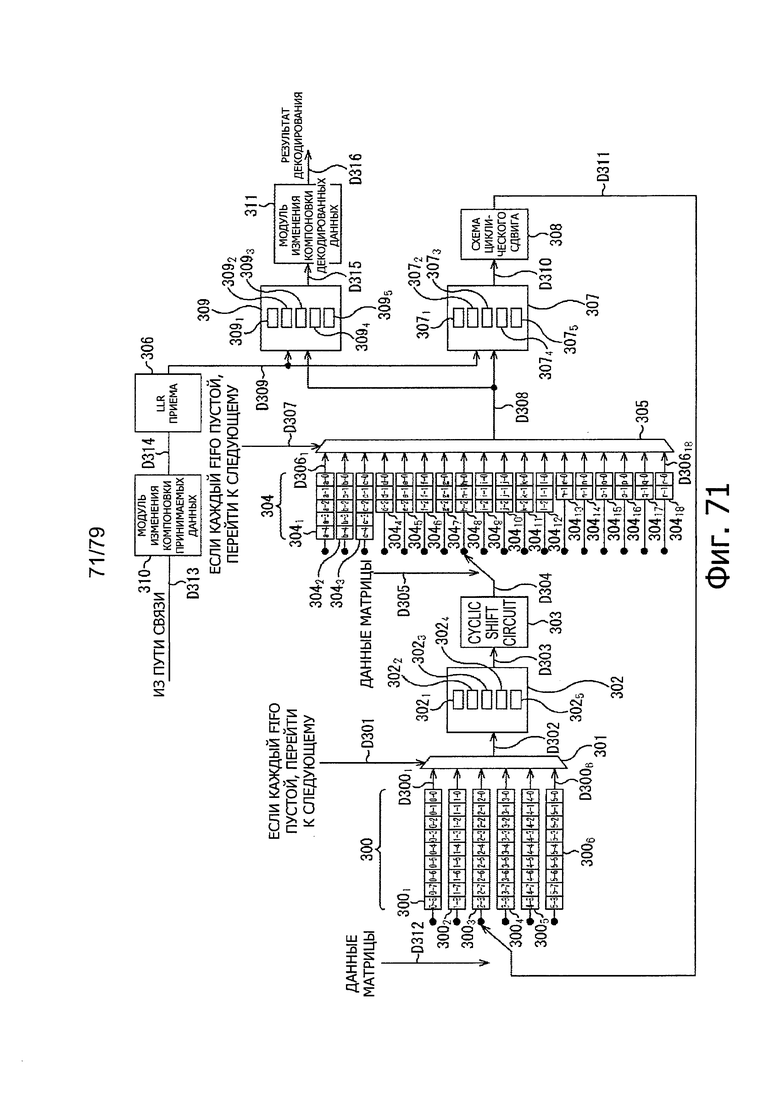

На фиг. 71 показана блок-схема, поясняющая пример конфигурации устройства декодирования, которое совместно выполняет операцию узла по Р.

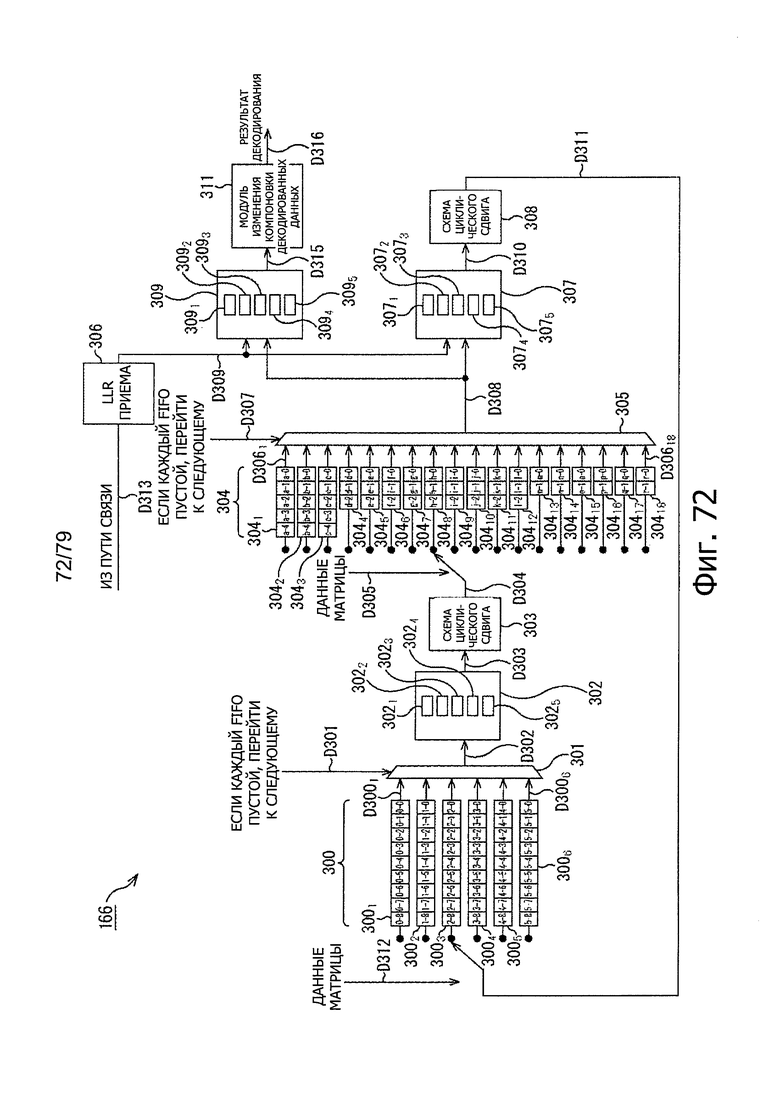

На фиг. 72 показана блок-схема, поясняющая пример конфигурации декодера 166 LDPC.

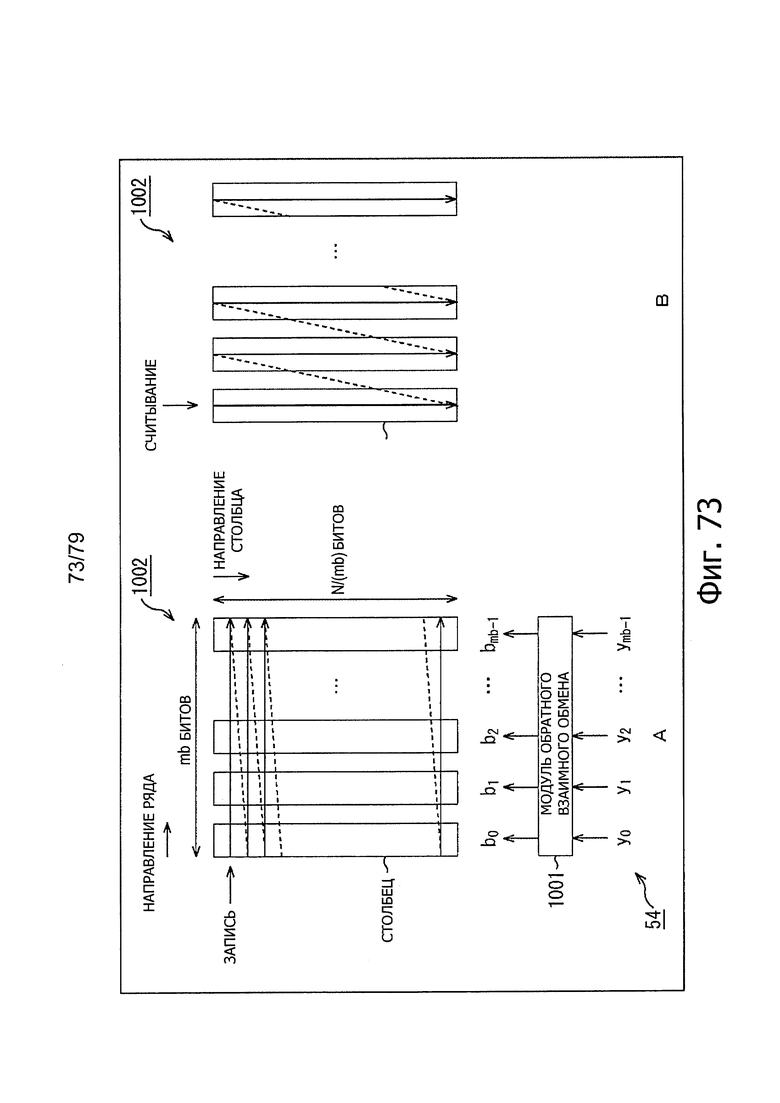

На фиг. 73 представлена иллюстрация обработки мультиплексора 54 образования обратного перемежителя 165 битов.

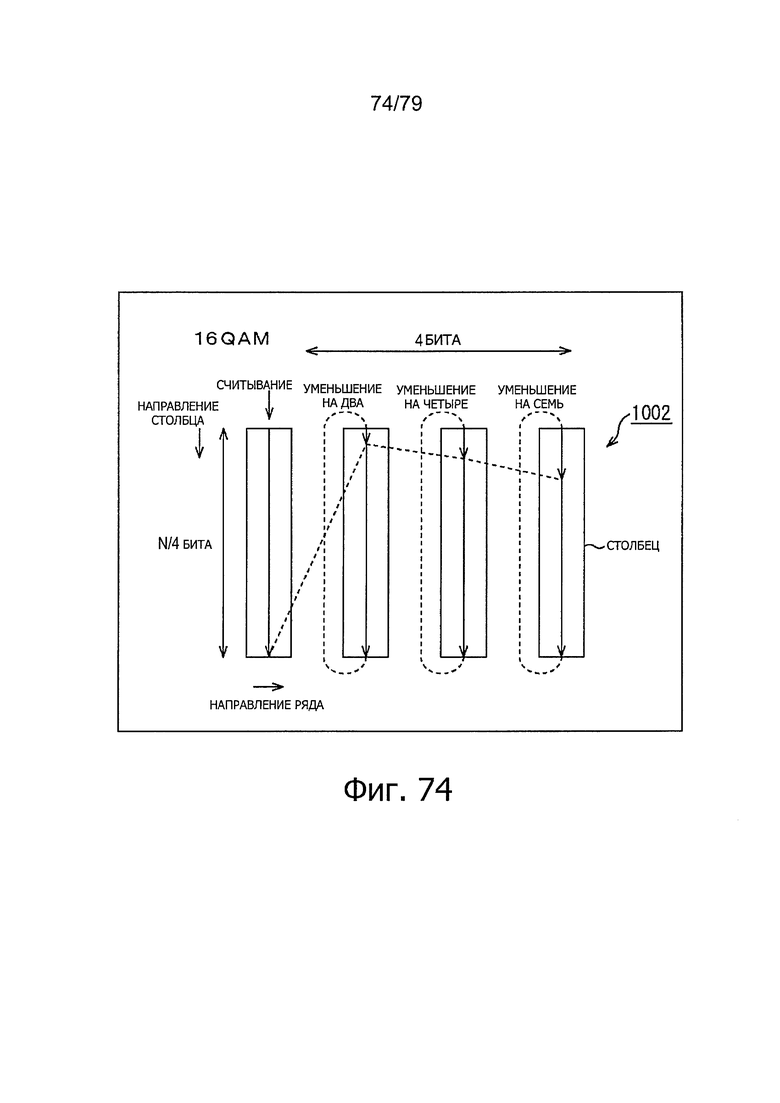

На фиг. 74 представлена иллюстрация обработки обратного перемежителя 55 со скручиванием столбцов.

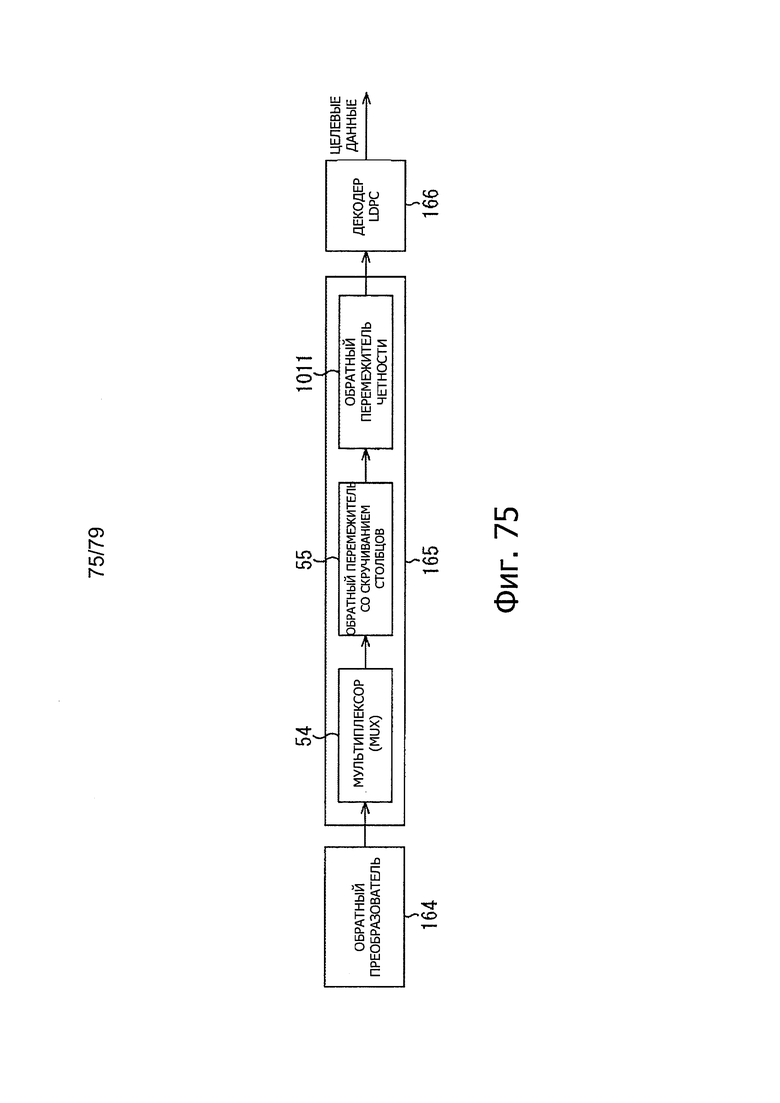

На фиг. 75 показана блок-схема, поясняющая другой пример конфигурации обратного перемежителя 165 битов.

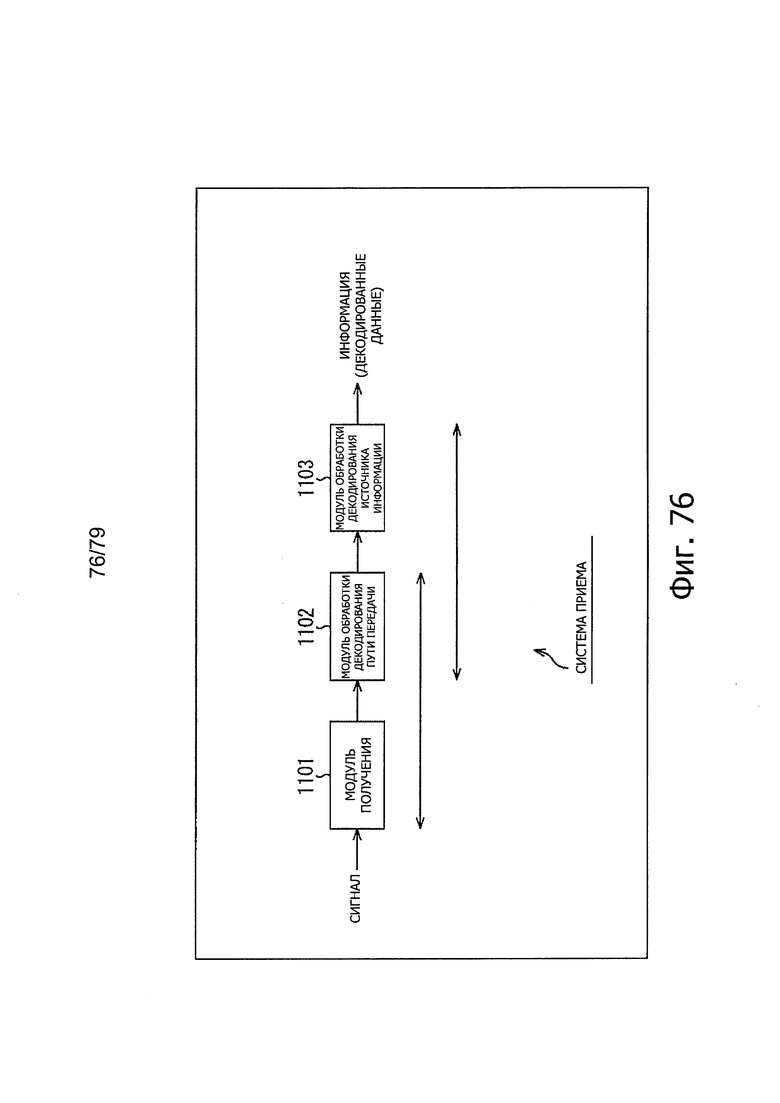

На фиг. 76 показана блок-схема, поясняющая первый пример конфигурации системы приема, которую можно применять в приемном устройстве 12.

На фиг. 77 показана блок-схема, поясняющая второй пример конфигурации системы приема, которую можно применять в приемном устройстве 12.

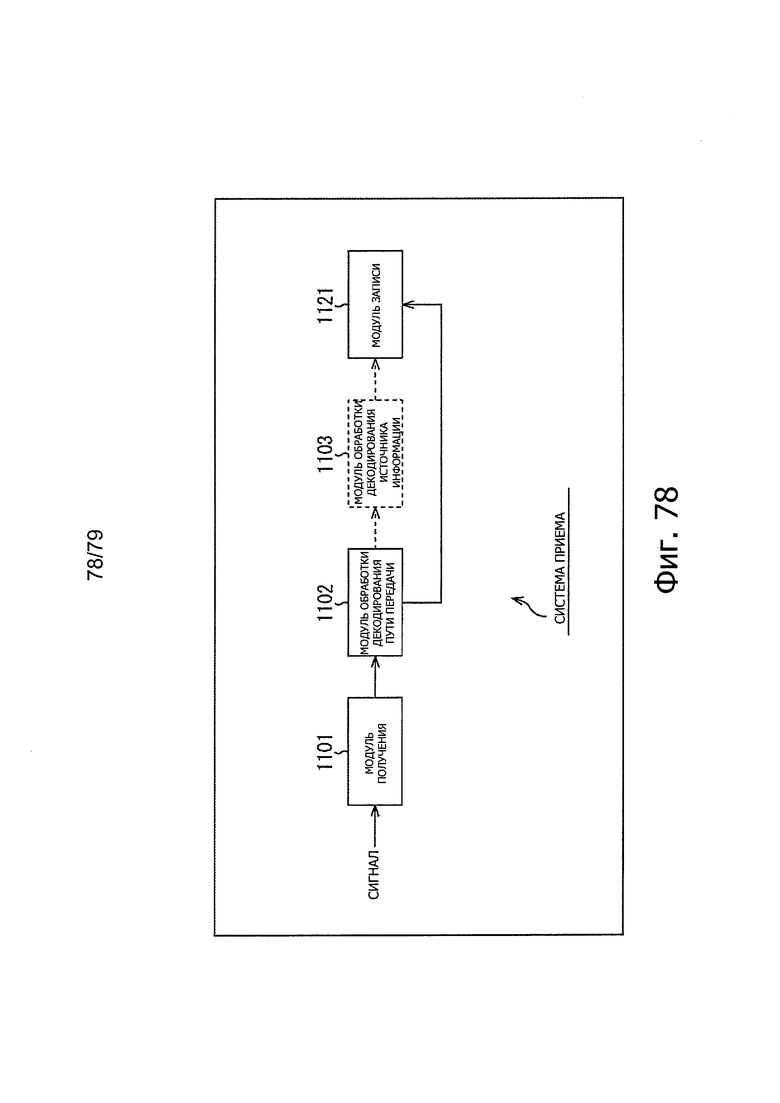

На фиг. 78 показана блок-схема, поясняющая третий пример конфигурации системы приема, которую можно применять в приемном устройстве 12.

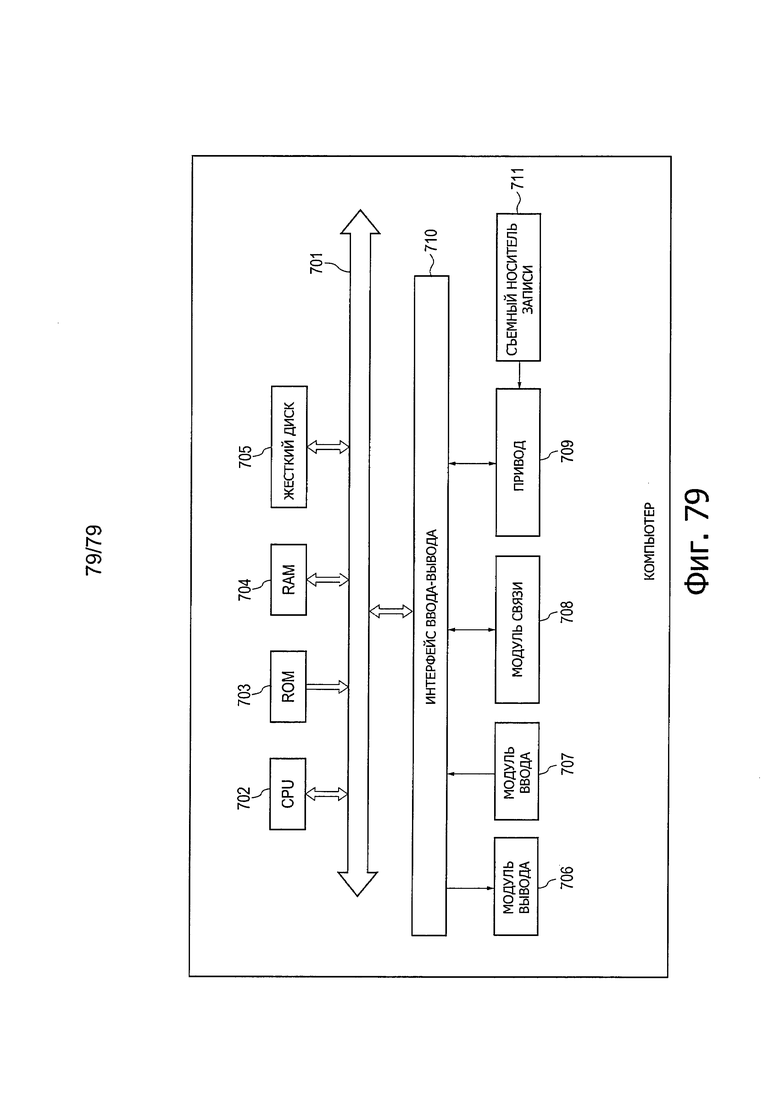

На фиг. 79 показана блок-схема, поясняющая пример конфигурации варианта осуществления компьютера, в котором применяется настоящая технология.

Осуществление изобретения

Ниже будет описан код LPDC перед описанием вариантов осуществления настоящей технологии.

Код LDPC

Код LDPC представляет собой линейный код, и код LDPC не обязательно должен представлять собой двоичный код. Однако, в данном случае, предполагается, что код LDPC представляет собой двоичный код.

Максимальная характеристика кода LDPC состоит в том, что матрица проверки на четность, определяющая код LDPC, является разреженной. В этом случае разреженная матрица представляет собой матрицу, в которой количество "1" среди элементов матрицы очень мало (матрица, в которой большинство элементов составляет 0).

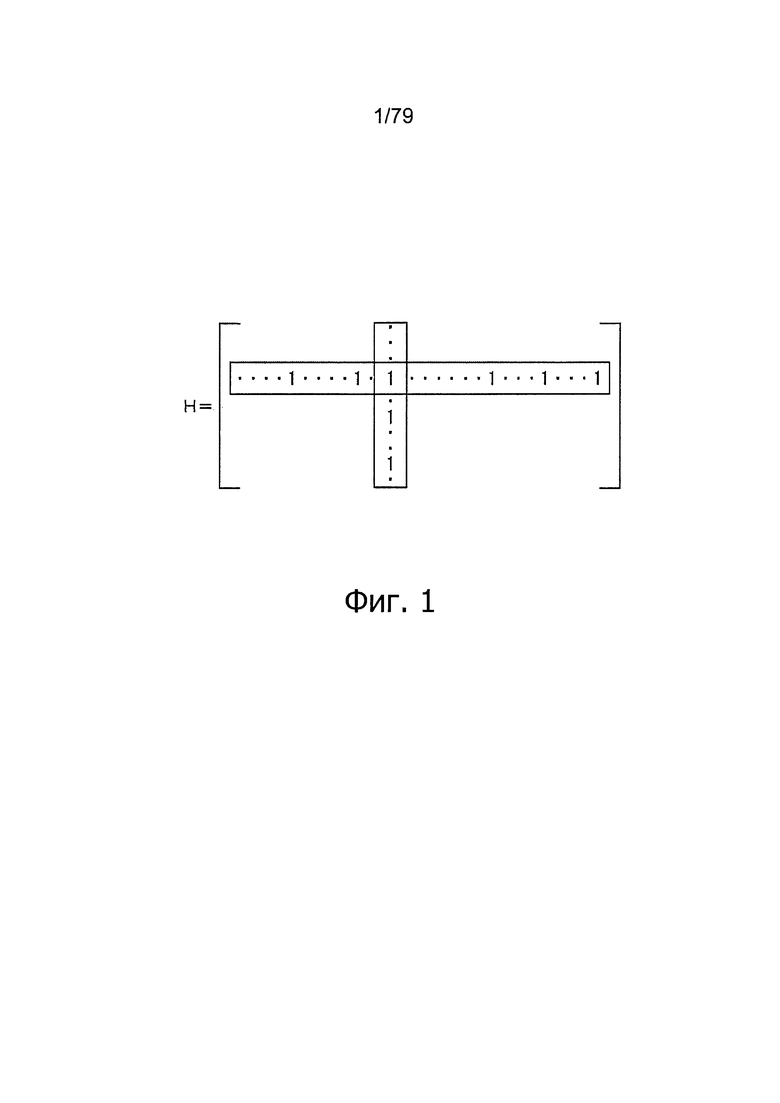

На фиг. 1 показана иллюстрация примера матрицы H проверки на четность кода LDPC.

В матрице H проверки на четность по фиг. 1 вес каждого столбца (вес столбца) (количество "1") становится равным "3", и вес каждого ряда (вес ряда) становится равным "6".

При кодировании используют код LDPC (кодирование LDPC), например, матрицу G генерирования генерируют на основе матрицы H проверки на четность, и матрицу G генерирования умножают на биты двоичной информации, таким образом, что генерируется кодовое слово (код LDPC).

В частности, устройство кодирования, которое выполняет кодирование LDPC, вначале рассчитывает матрицу G генерирования, в которой реализуется уравнение GHT=0, между транспонированной матрицей ΗT матрицы H проверки на четность и матрицей G генерирования. В этом случае, когда матрица G генерирования представляет собой матрицу K×N, устройство кодирования умножает матрицу G генерирования на строку битов (вектор u) информационных битов, включающих в себя K битов, и генерирует кодовое слово с (=uG), включающее в себя N битов. Кодовое слово (код LDPC), которое генерирует устройство кодирования, принимают на стороне приема, используя заданный путь связи.

Код LDPC может быть декодирован с использованием алгоритма, называемого вероятностным декодированием, предложенным Галлагером, то есть, с использованием алгоритма передачи сообщений, используя распространение доверия по, так называемому, графу Таннера, включающему в себя переменный узел (также называется узлом сообщения) и узел проверки. Ниже переменный узел и узел проверки, соответственно, называются просто узлами.

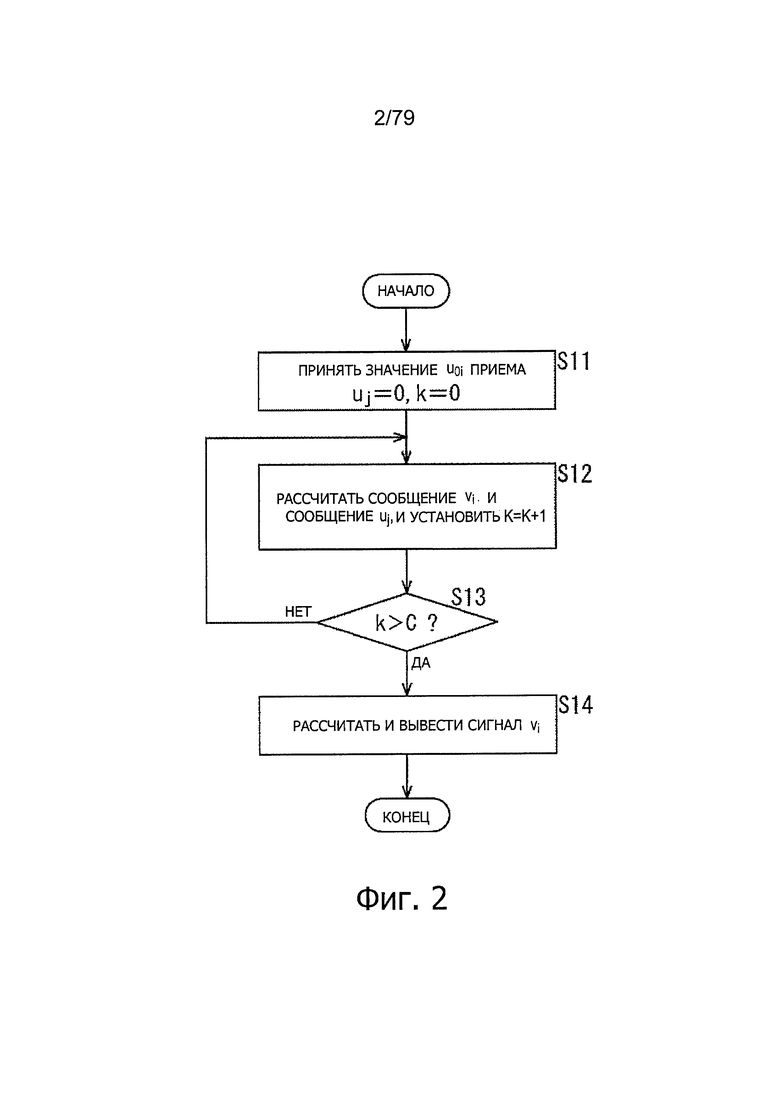

На фиг. 2 показана блок-схема последовательности операций, иллюстрирующая последовательность декодирования кода LDPC.

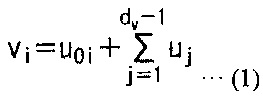

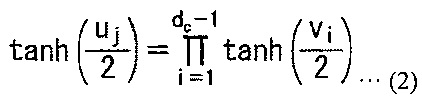

Ниже реальное значение (прием LLR), которое получают путем представления вероятности "0" значения в i-ом бите кода для кода LDPC (одного кодового слова), принятого стороной приема, логарифмом отношения вероятностей, соответственно, называются значением u0i приема. Кроме того, выход сообщения из узла проверки называют uj, и выход сообщения из переменного узла обозначают как vi.

Вначале, при декодировании кода LDPC, как представлено на фиг. 2, на этапе S11, принимают код LDPC, сообщение (сообщение узла проверки) uj инициализируют в "0", и переменную k, которая принимает значение целого числа, в качестве счетчика повторения обработки инициализируют в "0", и обработка переходит на этап S12. На этапе S12 сообщение (сообщение переменного узла) vi рассчитывают путем выполнения операции (операция переменного узла), представленной уравнением (1), на основе значения u0i приема, полученного при приеме кода LDPC, и сообщение uj рассчитывают путем выполнения операции (операции проверочного узла), представленной уравнением (2), на основе сообщения vi.

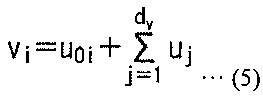

Уравнение 1

Уравнение 2

Здесь dv и dc в уравнении (1) и в уравнении (2), соответственно, представляют собой параметры, которые могут быть произвольно выбраны и иллюстрируется количество "1" в продольном направлении (столбец) и в поперечном направлении (ряд) в матрице Н проверки на четность. Например, в случае кода LDPC (код LDPC (3, 6)) в отношении матрицы Н проверки на четность с весом столбца 3 и весом ряда 6, как представлено на фиг. 1, устанавливают dv=3 и dc=6.

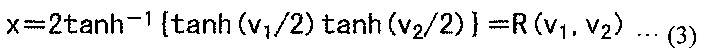

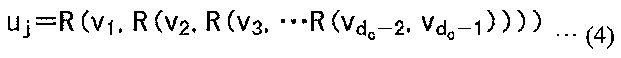

В операции переменного узла в уравнении (1) и в операции проверочного узла в уравнении (2), поскольку сообщение, введенное из ребра (линия, соединяющая переменный узел и проверочный узел) для вывода сообщения, не является целью операции, диапазон операции становится равным от 1 до dv-1 или от 1 до dc-1. Операция проверочного узла в соответствии с уравнением (2), выполняется фактически путем предварительного формирования таблицы функции R (v1, v2), представленной уравнением (3), определенной по выходу в отношении двух входных значений v1 и v2, и последовательно (рекурсивно) используя таблицу, как представлено уравнением (4).

Уравнение 3

Уравнение 4

На этапе S12, выполняют последовательное приращение переменной k на "1", и обработка переходит на этап S13. На этапе S13 определяют, превышает ли величина переменной k заданное число раз С повторений декодирований. Когда на этапе S13 определяют, что переменная k не больше чем С, обработка возвращается на этап S12, и ту же обработку повторяют ниже.

Когда на этапе S13 определяют, что переменная k больше, чем С, обработка переходит на этап S14, сообщение vi, которое соответствует результату декодирования, которое должно быть в конечном итоге выведено, рассчитывают путем выполнения операции, представленной уравнением (5), и выводят, и обработка декодирования кода LDPC заканчивается.

Уравнение 5

В этом случае, операция по уравнению (5) выполняется, используя сообщение uj из всех ребер, соединенных с переменным узлом, отличных от операции переменного узла в соответствии с уравнением (1).

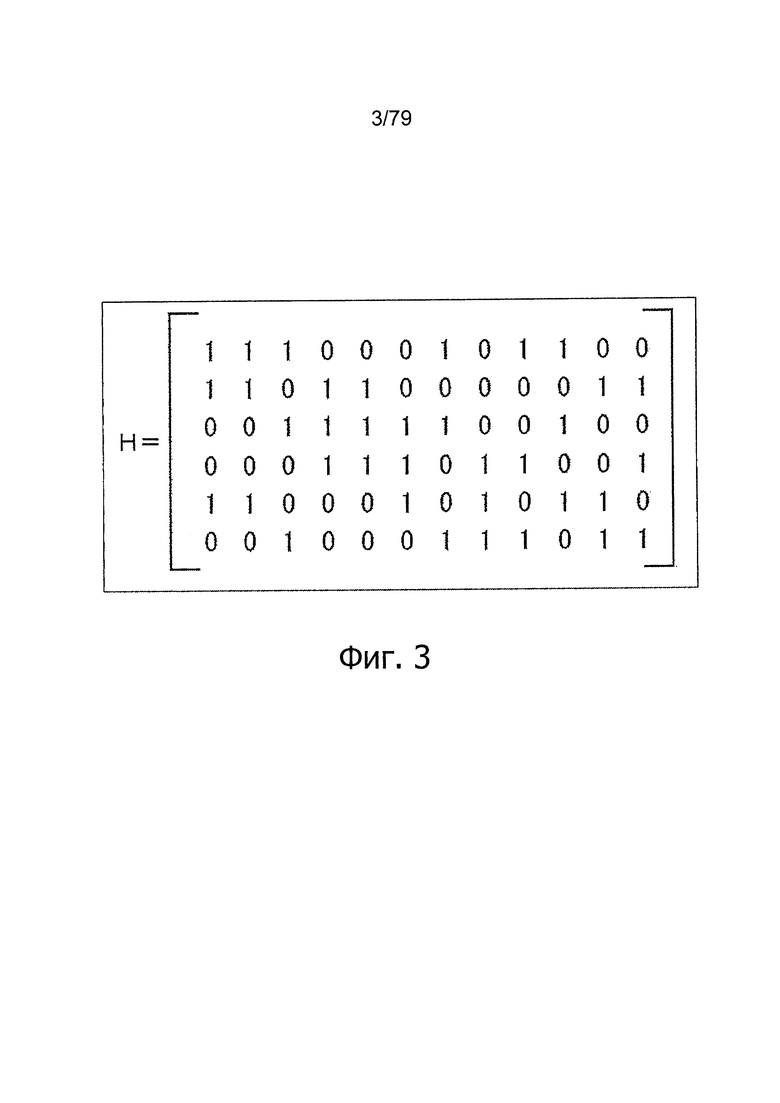

На фиг. 3 представлена иллюстрация примера матрицы Н проверки на четность для кода LDPC (3, 6) (скорость кодирования 1/2 и длина кода 12).

В матрице Н проверки на четность по фиг. 3 вес столбца установлен равным 3, и вес ряда установлен равным 6, аналогично фиг. 1.

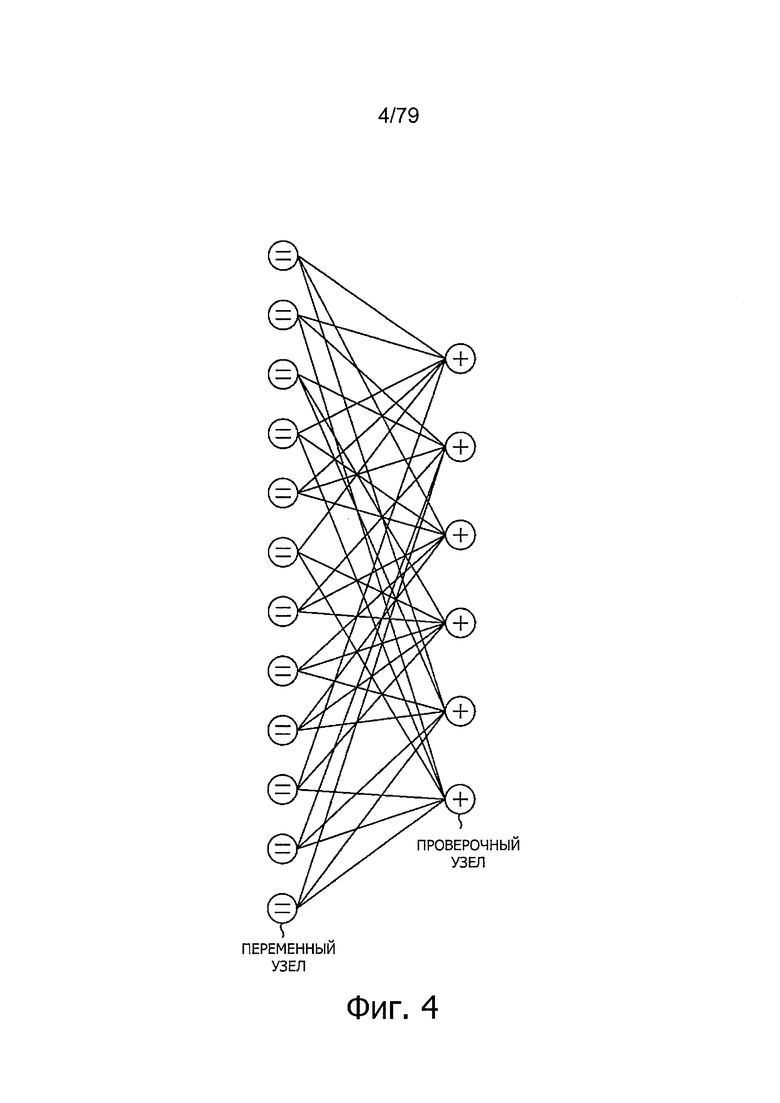

На фиг. 4 представлена иллюстрация графа Таннера матрицы Н проверки на четность по фиг. 3.

На фиг. 4 проверочный узел представлен "+" (плюс), и переменный узел представлен "=" (равенство). Проверочный узел и переменный узел соответствуют ряду и столбцу матрицы Н проверки на четность. Линия, которая соединяет проверочный узел и переменный узел, представляет собой кромку и соответствует "1" элементов матрицы проверки на четность.

Таким образом, когда элемент j-ого ряда и i-ого столбца матрицы проверки на четность равен 1, на фиг. 4, i-ый переменный узел (узел "=") с верхней стороны и j-ый проверочный узел (узел "+") с верхней стороны соединяются ребром. Ребро представляет, что бит кода, соответствующий переменному узлу, имеет состояние ограничения, соответствующее проверочному узлу.

В алгоритме произведения суммы, который представляет собой способ декодирования для кода LDPC, многократно выполняют операцию переменного узла и операцию проверочного узла.

На фиг. 5 показана иллюстрация операции переменного узла, которая выполняется переменным узлом.

В переменном узле сообщение vi, которое соответствует кромке для расчетов, рассчитывают с помощью операции переменного узла по уравнению (1), используя сообщения u1 и u2 из остальных ребер, соединенных с переменным узлом и значением u0i приема. Сообщения, которые соответствуют другим ребрам, также рассчитывают, используя тот же способ.

На фиг. 6 представлена иллюстрация операции проверочного узла, которую выполняет проверочный узел.

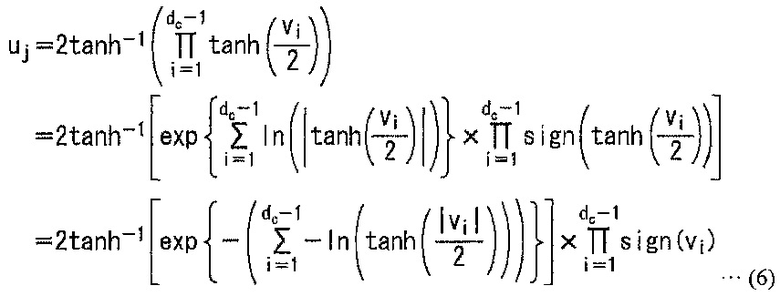

В этом случае, операция проверочного узла по уравнению (2) может быть перезаписана уравнением (6), используя соотношение уравнения а×b=exp{ln(|а |)+ln(|b|)}×sign(а)×sign(b). Однако, sign(x) равен 1, в случае х≥0, и равен -1, в случае х<0.

Уравнение 6

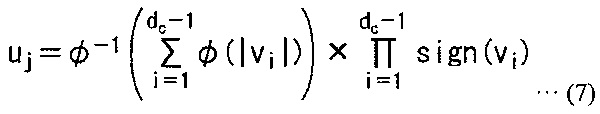

При х≥0, если функция φ(х) определена, как уравнение φ(х)=ln (tanh (х/2)), реализуется уравнение φ-1(х)=2tanh-1(e-x). По этой причине уравнение (6) может быть изменено в уравнение (7).

Уравнение 7

В проверочном узле операцию проверочного узла в соответствии с уравнением (2) выполняют в соответствии с уравнением (7).

Таким образом, в проверочном узле, как представлено на фиг. 6, сообщение uj, которое соответствует ребру для расчета, рассчитывают, используя операцию проверочного узла по уравнению (7), используя сообщения v1, v2, v3, v4 и v5 из оставшихся ребер, соединенных с проверочным узлом. Сообщения, которые соответствуют другим ребрам, также рассчитывают с помощью того же способа.

Функция φ(х) в уравнении (7) может быть представлена, как φ(х)=ln((ех+1)/(ех-1)), и φ(х)=φ-1(х) удовлетворяется при х>0. Когда функции φ(х) и φ-1(х) воплощают в виде аппаратных средств, функции φ(х) и φ-1(х) могут быть воплощены, используя LUT (справочную таблицу). Однако, обе функции φ(х) и φ-1(х) становятся одной LUT.

Пример конфигурации системы передачи, в которой применяется настоящая технология

На фиг. 7 показана иллюстрация примера конфигурации варианта осуществления системы передачи (термин система означает логическое объединение множества устройств, и устройство в каждой конфигурации может быть размещено или может не быть размещено в одном и том же корпусе), в котором применяется настоящее изобретение.

На фиг. 7 система передачи включает в себя устройство 11 передачи и устройство 12 приема.

Например, устройство 11 передачи передает (выполняет широковещательную передачу) (передает) программу телевизионной широковещательной передачи, и так далее. Таким образом, например, устройство 11 передачи кодирует целевые данные, которые представляют собой цель передачи, такие как данные изображения и аудиоданные, как программу, в кодах LDPC, и, например, передает их через путь 13 передачи данных, такой как спутниковый контур, наземная волна и кабель (проводной контур).

Устройство 12 приема принимает код LDPC, переданный из устройства 11 передачи через путь 13 передачи данных, декодирует код LDPC для получения целевых данных, и выводит эти целевые данные.

В этом случае, известно, что код LDPC, используемый системой передачи по фиг. 7, проявляет очень высокие возможности на пути передачи данных в условиях AWGN (аддитивного белого Гауссова шума).

В то же время, на пути 13 передачи данных могут быть сгенерированы пакетная ошибка или разрушение информации. В частности, в случае, когда путь 13 передачи данных представляет собой наземную волну, например, в системе OFDM (ортогональное мультиплексирование с частотным разделением), мощность определенного символа может стать равной 0 (разрушение информации) в соответствии с задержкой эхо-сигнала (другого канала распространения, чем основной канал), в среде с многолучевым распространением, в которой D/U (отношение желательного к нежелательному) составляет 0 дБ (мощность нежелательного = мощность эхо-сигнала, равная мощности желательного = основной канал распространения).

В случае частотного дрожания сигнала (канал передачи данных, в котором суммируют задержку, равную 0, и эхо-сигнал, имеющий допплеровскую частоту), когда D/U составляет 0 дБ, общая мощность символа OFDM в определенный момент времени может стать равной 0 (разрушение информации), из-за допплеровской частоты.

Кроме того, пакетная ошибка может быть сгенерирована из-за ситуации в проводной линии от модуля приема (не представлен на чертежах) стороны приемного устройства 12, такого как антенна, принимающая сигнал из устройства 11 передачи, в приемное устройство 12, или из-за нестабильности источника питания приемного устройства 12.

В то же время, при декодировании кода LDPC в переменном узле, в соответствии со столбцом матрицы H проверки на четность, и бита кода для кода LDPC, как представлено на фиг. 5, описанной выше, выполняется операция переменного узла, в соответствии с уравнением (1), с добавлением (значения приема u0i для) кода бита для кода LDPC. По этой причине, если генерируется ошибка в битах кода, используемых для операции переменного узла, точность рассчитанного сообщения ухудшается.

При декодировании кода LDPC, в проверочном узле, операция проверочного узла по уравнению (7) выполняется, используя сообщение, рассчитанное переменным узлом, соединенным с проверочным узлом. По этой причине, если увеличивается количество проверочных узлов, в которых генерируется ошибка (включая в себя разрушение информации), одновременно в множестве подключенных переменных узлов (кодах бита для кодов LDPC, соответствующих им), характеристика декодирования ухудшается.

Таким образом, если данные в двух или больше переменных узлах для переменных узлов, соединенных с проверочным узлом, одновременно будут разрушены, проверочный узел возвращает сообщение, в котором вероятность значения, равная 0, и вероятность значения, равная 1, равны друг другу для всех переменных узлов. В этом случае проверочный узел, который возвращает сообщение равных вероятностей, не способствует одной обработке декодирования (одному набору операции переменного узла и операции проверочного узла). В результате, необходимо увеличить количество раз повторений обработки декодирования, характеристики декодирования ухудшаются, и увеличивается потребление энергии питания приемного устройства 12, которое выполняет декодирование кода LDPC.

Поэтому, в системе передачи по фиг. 7, устойчивость к пакетным ошибкам или к разрушению может быть улучшена, в то время как рабочие характеристики канала передачи данных AWGN (канала AWGN) сохраняется.

Пример конфигурации устройства 11 передачи

На фиг. 8 показана блок-схема, иллюстрирующая пример конфигурации устройства 11 передачи по фиг. 7.

В устройстве 11 передачи, один или больше входных потоков, соответствующим целевым данным, подают в адаптацию режима/мультиплексор 111.

Адаптация режима/мультиплексор 111 выполняет выбор режима и выполняет такую обработку, как мультиплексирование одного или больше входных потоков, подаваемых в него, в соответствии с необходимостью, и подает полученные в результате данные в заполнитель 112.

Заполнитель 112 выполняет необходимое заполнение нулями (вставку нулей) в отношении данных, подаваемых из режима адаптации/мультиплексора 111, и подает полученные в результате данные в скремблер 113 ВВ.

Скремблер 113 ВВ выполняет скремблирование в основной полосе пропускания (скремблирование ВВ) в отношении данных, подаваемых из заполнителя 112, и подает полученные в результате данные в кодер 114 ВСН.

Кодер 114 ВСН выполняет кодирование ВСН в отношении данных, подаваемых из скремблера 113 ВВ, и подает полученные в результате данные, как целевые данные LDPC, которые представляют собой цель кодирования LDPC, в кодер 115 LDPC.

Кодер 115 LDPC выполняет кодирование LDPC, в соответствии с матрицей проверки на четность, в которой матрица четности, представляющая собой часть, соответствующую биту четности кода LDPC, становится ступенчатой структурой в отношении целевых данных LDPC, подаваемых из кодера 114 ВСН, и выводит код LDPC, в котором целевые данные LDPC представляют собой информационные биты.

Таким образом, кодер 115 LDPC выполняет кодирование LDPC для кодирования целевых данных LDPC с LDPC, таким как код LDPC (соответствующим матрице проверки на четность), определенным в заданном стандарте в DVB-S.2, DVB-T.2, DVB-C.2 и т.п., и выводит полученный в результате заданный код LDPC (соответствующий матрице проверки на четность) и т.п.

Код LDPC, определенный в стандарте DVB-S.2, DVB-T.2 и DVB-C.2, представляет собой код IRA (неравномерное накопление повторений), и матрица четности матрицы проверки на четность кода LDPC становятся ступенчатой структурой. Матрица четности и ступенчатая структура будут описаны ниже. Код IRA описан, например, в публикации "Irregular Repeat-Accumulate Codes", H. Jin, A. Khandekar, and R.J. McEliece, in Proceedings of 2nd International Symposium on Turb0 codes and Related Topics, pp. 1-8, Sept. 2000.

Код LDPC, который выводит кодер 115 LDPC, подают в перемежитель 116 битов.

Перемежитель 116 битов выполняет перемежение битов, которое будет описано ниже в отношении кода LDPC, подаваемого из кодера 115 LDPC, и подает код LDPC после перемежения битов в преобразователь 117.

Преобразователь 117 отображает код LDPC, подаваемый из перемежителя 116 битов, на точку сигнала, представляющую один символ ортогональной модуляции в модуле (модуле символа) битов кода одного или больше битов кода LDPC, и выполняет ортогональную модуляцию (многоуровневую модуляцию).

Таким образом, преобразователь 117 выполняет отображение кода LDPC, подаваемого из перемежителя 116 битов, на точку сигнала, определенную способом модуляции, выполняющим ортогональную модуляцию кода LDPC на плоскости IQ (совокупность IQ), определенной осью I, представляющей компонент I с той же фазой, что и несущая, и осью Q, представляющей компонент Q, ортогональный несущей, и выполняет ортогональную модуляцию.

В этом случае, в качестве способа модуляции для ортогональной модуляции, выполняемой преобразователем 117, существуют способы модуляции, включающие в себя способ модуляции, определенный в стандарте DVB-S.2, DVB-T.2, DVB-C.2 и т.п., и другой способ модуляции, то есть, BPSK (двоичная модуляция со сдвигом фазы), QPSK (квадратурная модуляция со сдвигом фазы), 8PSK (модуляция со сдвигом фазы), 16APSK (амплитудная модуляция со сдвигом фазы), 32APSK, 16QAM (квадратурная амплитудная модуляция), 64QAM, 256QAM, 1024QAM, 4096QAM, 4РАМ (импульсно-амплитудная модуляция), и т.п. В преобразователе 117 выполняется ортогональная модуляция, на основе которой был ранее установлен способ модуляции, в соответствии с операцией оператора устройства 11 передачи.

Данные (результат отображения, где символ отображен на точку в сигнале), которые были получены в результате обработки в преобразователе 117, подают в перемежитель 118 по времени.

Перемежитель 118 по времени выполняет перемежение по времени (перемежение в направлении времени) в модулях символов в отношении данных, подаваемых из преобразователя 117, и подает полученные в результате данные в кодер SISO/MISO (кодер SISO/MISO (один вход - один выход/множество входов - один выход)) 119.

Кодер 119 SISO/MISO выполняет пространственно-временное кодирование в отношении данных, подаваемых из перемежителя 118 по времени, и подает эти данные в перемежитель 120 по частоте.

Перемежитель 120 по частоте выполняет перемежение по частоте (перемежение в направлении частоты) в модулях символа в отношении данных, подаваемых из кодера 119 SISO/MISO, и подает эти данные в построитель фрейма/ модуль 131 выделения ресурсов.

С другой стороны, например, данные управления (сигналы) для передачи управления, такие как сигналы ВВ (сигналы в основной полосе пропускания) (заголовок ВВ), подают в кодер 121 ВСН.

Кодер 121 ВСН выполняет кодирование ВСН в отношении подаваемых в него сигналов и подает данные, полученные в результате, в кодер 122 LDPC, аналогично кодеру 114 ВСН.

Кодер 122 LDPC устанавливает данные, поданные из кодера 121 ВСН, как целевые данные LDPC, выполняет кодирование LDPC в отношении этих данных, и подает код LDPC, полученный в результате, в преобразователь 123, аналогичный кодеру 115 LDPC.

Преобразователь 123 отображает код LDPC, подаваемый из кодера 122 LDPC, на точку сигнала, представляющую один символ ортогональной модуляции в единицах (модулях символа) битов кода одного или больше битов кода LDPC, выполняет ортогональную модуляцию и подает полученные в результате данные в перемежитель 124 по частоте, аналогично преобразователю 117.

Перемежитель 124 по частоте выполняет перемежение частоты в модулях символа в отношении данных, подаваемых из кодера 123 QAM, и подает эти данные в модуль 131 построения фрейма/выделения ресурсов, аналогично перемежителю 120 по частоте.

Модуль 131 построения фрейма/выделения ресурсов вставляет символы пилотных сигналов в необходимые положения среди данных (символов), подаваемых из перемежителей 120 и 124 по частоте, выполняет конфигурирование фрейма (например, фрейма физического уровня (PL), фрейма Т2, фрейма С2 и так далее), включающего в себя заданное количество символов из данных (символов), полученных в результате, и подает этот фрейм в модуль 132 генерирования OFDM.

Модуль 132 генерирования OFDM генерирует сигнал OFDM, соответствующий фрейму, из фрейма, подаваемого из модуля 131 построения фрейма/выделения ресурсов, и передает сигнал OFDM через путь 13 передачи данных (фиг. 7).

Здесь, например, устройство 11 передачи может быть выполнено без включения части блоков, представленных на фиг. 8, таких как перемежитель 118 по времени, кодер 119 SISO/MISO, перемежитель 120 по частоте и перемежитель 124 по частоте.

На фиг. 9 иллюстрируется пример конфигурации перемежителя 116 битов по фиг. 8.

Перемежитель 116 битов включает в себя функцию для перемежения данных и включает в себя перемежитель 23 четности, перемежитель 24 со скручиванием столбцов и демультиплексор (DEMUX) 25. Здесь перемежитель 116 битов может быть сконфигурирован без включения одного или обоих из перемежителя 23 четности и перемежителя 24 со скручиванием столбцов.

Перемежитель 23 четности выполняет перемежение четности для перемежения битов четности кода LDPC, подаваемого из кодера 115 LDPC, в положения других битов четности и подает код LDPC после перемежения четности в перемежитель 24 со скручиванием столбцов.

Перемежитель 24 со скручиванием столбцов выполняет перемежение со скручиванием столбцов в отношении кода LDPC, подаваемого из перемежителя 23 четности, и подает код LDPC после перемежения скручивания столбцов в демультиплексор 25.

Таким образом, в преобразователе 117 на фиг. 8, биты кода одного или больше битов кода LDPC отображают на точку сигнала, представляющую один символ ортогональной модуляции, и передают.

В перемежителе 24 со скручиванием столбцов выполняют перемежение со скручиванием столбцов, которое будет описано ниже, как обработку изменения компоновки, для изменения компоновки битов кода для кода LDPC, подаваемого из перемежителя 23 четности, таким образом, что множество битов кода для кода LDPC, соответствующих 1 в любом одном ряду матрицы проверки на четность, используемой кодером 115 LDPC, не включено в один символ.

Демультиплексор 25 выполняет обработку взаимного обмена для положений взаимного обмена двух или больше битов кода для кода LDPC, который становится символом в отношении кода LDPC, подаваемого из перемежителя 24 со скручиванием столбцов, и получает код LDPC, в котором усиливается устойчивость к AWGN и т.п. Кроме того, демультиплексор 25 подает два или больше битов кода для кода LDPC, полученного путем обработки взаимного обмена, как символ, в преобразователь 117 (фиг. 8).

На фиг. 10 иллюстрируется матрица H проверки на четность, которая используется для кодирования LDPC кодером 115 LDPC на фиг. 8.

Матрица H проверки на четность становится структурой LDGM (матрица генерирования с низкой плотностью) и может быть представлена, как уравнение H=[HA|ΗT] (матрица, в которой элементы информационной матрицы HA установлены в левые элементы и элементы матрицы ΗT четности, установлены в правые элементы), используя информационную матрицу HA части, соответствующей информационным битам, среди битов кода для кода LDPC и матрицы ΗT четности, соответствующих битам четности.

В этом случае, количество битов для информационных битов среди битов кода для одного кода LDPC (одно кодовое слово) и количество битов для битов четности называются длиной К информации и длиной M четности, соответственно, и количество битов для битов кода одного кода LDPC называется длиной кода N (=K+М).

Длину K информации и длину M четности кода LDPC, имеющего определенную длину N кода, определяют по скорости кодирования. Матрица H проверки на четность становится матрицей, в которой количество рядов × на количество столбцов равно Μ×N. Информационная матрица HA становится матрицей с размером Μ×K и матрица ΗT четности становится матрицей Μ×M.

На фиг. 11 иллюстрируется матрица ΗT четности матрицы Η проверки на четность кода LDPC, которая определена в стандарте DVB-S.2, DVB-T.2 и DVB-C.2.

Матрица ΗT четности матрицы Η проверки на четность кода LDPC, которая определена в стандарте DVB-T.2 и т.п., становится матрицей ступенчатой структуры (нижней бидиагональной матрицей), в которой элементы, равные 1, размещены в форме лестницы, как представлено на фиг. 11. Вес ряда матрицы ΗT четности становится равным 1 в отношении первого ряда и становится равным 2 в отношении оставшихся рядов. Вес столбцов становится равным 1 в отношении конечного столбца и становится равным 2 в отношении оставшихся столбцов.

Как описано выше, код LDPC матрицы H проверки на четность, в которой матрица ΗT четности становится ступенчатой структурой, можно легко сгенерировать, используя матрицу Η проверки на четность.

Таким образом, код LDPC (одно кодовое слово) представлен вектором с ряда, и вектор столбца, полученный путем транспонирования вектора ряда, представлен, как CT. Кроме того, часть информационных битов вектора с ряда, которая должна стать кодом LDPC, представлена вектором А ряда, и часть битов четности представлена вектором Τ ряда.

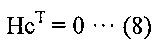

Вектор с ряда может быть представлен уравнением с=[А|Т] (вектор ряда, в котором элементы вектора А ряда установлены в левые элементы, и элементы вектора Τ ряда установлены в правые элементы), используя вектор В ряда, соответствующий информационным битам, и вектор Τ ряда, соответствующий битам четности.

В матрице Η проверки на четность и в векторе с=[А|Т], соответствующем коду LDPC, должно удовлетворяться уравнение HcT=0. Вектор Τ ряда, который соответствует битам четности, составляющим вектор ряда с=[А|Т], удовлетворяющий уравнению HcT=0, может быть последовательно рассчитан путем установки элементов каждого ряда в 0, последовательно (в порядке) от элементов первого ряда вектора HcT в уравнении HcT=0, когда матрица ΗT четности матрицы Η=[HA|ΗT] проверки на четность становится ступенчатой структурой, представленной на фиг. 11.

На фиг. 12 показана иллюстрация матрицы Η проверки на четность кода LDPC, который определен в стандарте DVB-T.2 и т.п.

Вес столбца становится равным X в отношении столбцов KX от первого столбца матрицы H проверки на четность кода LDPC, определенного в стандарте DVB-T.2 и т.п., становится равным 3 в отношении следующих K3 столбцов, становится равным 2 в отношении следующих (М-1) столбцов, и становится равным 1 в отношении конечного столбца.

В этом случае, KX+K3+М-1+1 равно длине N кода.

На фиг. 13 представлена иллюстрация количества KX, K3, и M столбцов и веса X столбца в отношении каждого значения скорости r кодирования кода LDPC, определенного в стандарте DVB-T.2 и т.п.

В стандарте DVB-T.2 и т.п. определены коды LDPC, которые имеют длину кода N 64800 битов и 16200 битов.

Что касается кода LDPC, имеющего длину N кода 64800 битов, определены 11 скоростей кодирования (номинальных скоростей) 1/4, 1/3, 2/5, 1/2, 3/5, 2/3, 3/4, 4/5, 5/6, 8/9 и 9/10. Что касается кода LDPC, имеющего длину N кода 16200 битов, определены 10 скоростей кодирования 1/4, 1/3, 2/5, 1/2, 3/5, 2/3, 3/4, 4/5, 5/6 и 8/9.

Далее длина N кода 64800 битов называется 64 килобита, и длина N кода 16200 битов называется 16 килобит.

Что касается LDPC, частота ошибки проявляет тенденцию быть низкой в бите кода, соответствующем столбцу, вес столбца которого в матрице H проверки на четность велик.

В матрице H проверки на четность, которая представлена на фиг. 12 и 13 и определена в стандарте DVB-T.2 и т.п., вес столбца для столбца стороны заголовка (левой стороны) проявляет тенденцию быть большим. Поэтому, что касается кода LDPC, соответствующего матрице H проверки на четность, бит кода стороны заголовка проявляет тенденцию быть сильным в отношении ошибки (существует устойчивость в отношении ошибок), и бит кода завершающей стороны проявляет тенденцию быть слабым в отношении ошибки.

На фиг. 14 иллюстрируется пример компоновки 16 символов (точек сигнала, соответствующих им) на плоскости IQ, когда выполняется 16QAM преобразователем 117 по фиг. 8.

Таким образом, буква А на фиг. 14 иллюстрирует символы 16QAM в DVB-T.2 (точка сигнала, соответствующая символу).

В 16QAM существует один символ, представленный 4 битами и 16 символами (=24). Эти 16 символов размещены таким образом, что направление I × направление Q принимает форму квадрата 4×4, на основе исходной точки на плоскости IQ.

Если (i+1)-ый бит от старшего значащего бита из строки битов, представленной одним символом, будет представлен, как бит yi, 4 бита, представленные одним символом 16QAM, могут быть представлен, как биты y0, у1, y2 и у3, соответственно, последовательно от старшего значащего бита из. Когда способ модуляции представляет 16QAM, 4 бита кодовых битов для кода LDPC становятся символом (значение символа), равным 4 бита y0-у3 (символизированы).

На фиг. 14 иллюстрируется граница битов в отношении каждого из 4 битов (ниже называются символьными битами) y0-у3, представленными символом 16QAM.

В этом случае граница битов в отношении символьного бита yi (на фиг. 14, i=0, 1, 2 и 3) означает границу символа, в которой символьный бит yi становится равным 0, и символа, в котором символьный бит yi становится равным 1.

Как представлено буквой В на фиг. 14, только одно место на оси Q в плоскости IQ становится границей бита в отношении старшего значащего символьного бита y0 из 4 битов символьных битов y0-у3, представленных символом 16QAM, и только одно место на оси I плоскости IQ становится границей битов в отношении второго (второго от старшего значащего бита из) символьного бита у1.

Что касается третьего символьного бита у2, два места на плоскости между первым и вторым столбцами с левой стороны, и место между третьим и четвертым столбцами среди символов 4×4, становятся границами бита.

Что касается четвертого символьного бита у3, два места на месте между первым и вторым рядами с верхней стороны и место между третьим и четвертым рядами, среди символов 4×4, становятся границами бита.

В символьных битах yi, которые представлены символами, когда количество символов за пределами границ бита велико, трудно сгенерировать ошибку (вероятность ошибки будет низкой), и когда количество символов, близкое к границам бита, велико, ошибку легко сгенерировать (высокая вероятность ошибки).

Если биты (сильные в отношении ошибки), в которых с трудом генерируется ошибка, назвать "сильными битами", и биты (слабые в отношении ошибки), в которых легко генерируется ошибка, назвать "слабыми битами", в отношении 4 битов символьных битов y0-у3 символа 16QAM, старший значащий символьный бит y0 и второй символьный бит y1 становятся сильными битами, и третий символьный бит у2, и четвертый символьный бит у3 становятся слабыми битами.

На фиг. 15-17 иллюстрируется пример компоновки (точек сигнала, соответствующих) 64 символов на плоскости IQ, то есть, символов 16QAM DVB-T.2, когда 64QAM выполняется с помощью преобразователя 117 на фиг. 8.

В 64QAM один символ представляет 6 битов, и существуют 64 символа (=26). Эти 64 символа располагаются таким образом, что направление I × направление Q образует форму квадрата размером 8×8 на основе исходной точки плоскости IQ.

Символьные биты одного символа 64QAM могут быть представлены, как y0, у1, y2, у3, y4 и y5 последовательно от старшего значащего бита. Когда способ модуляции представляет собой 64QAM, 6 битов из битов кода для кода LDPC становятся символом для символьных битов от y0 до y5 из 6 битов.

В этом случае, на фиг. 15 иллюстрируются границы битов в отношении каждого из старшего значащего символьного бита y0 и второго символьного бита y1 среди символьных битов от y0 до y5 символа 64QAM, на фиг. 16 иллюстрируются границы битов в отношении каждого из третьего символьного бита у2 и четвертого символьного бита у3, и на фиг. 17 иллюстрируются границы битов в отношении каждого из пятого символьного бита y4 и шестого символьного бита y5.

Как представлено на фиг. 15, граница бита в отношении каждого из старшего значащего символьного бита y0 и второго символьного бита y1 становится одним местом. Как представлено на фиг. 16, границы битов в отношении каждого из третьего символьного бита у2 и четвертого символьного бита у3 становятся двумя местами. Как представлено на фиг. 17, границы битов в отношении каждого из пятого символьного бита y4 и шестого символьного бита y5 становятся четырьмя местами.

Поэтому, что касается символьных битов y0-y5 для символа 64QAM, старший значащий символьный бит y0 и второй символьный бит y1 становятся сильными битами, и третий символьный бит у2, и четвертый символьный бит у3 становятся следующими сильными битами. Кроме того, пятый символьный бит y4 и шестой символьный бит y5 становятся слабыми битами.

На фиг. 14 и 15-17 можно видеть, что в отношении символьных битов для символа ортогональной модуляции верхние биты проявляют тенденцию становиться сильными битами, и нижние биты проявляют тенденцию становиться слабыми битами.

На фиг. 18 представлена иллюстрация примера компоновки плоскости IQ (для точек сигнала, соответствующих) 4 символов в случае, когда спутниковый контур принят в качестве канала 13 передачи данных (фиг. 7), и QPSK выполняют в преобразователе 117 на фиг. 8, то есть, например, иллюстрация компоновки точки сигнала QPSK в DVB-S.2.

В QPSK для DVB-S.2 символ отображают на любую из 4 точек сигналов на окружности круга, радиус которого с центром в исходной точке плоскости IQ равен р.

На фиг. 19 представлена иллюстрация примера компоновки плоскости IQ из 8 символов в случае, когда спутниковый контур принят, как канал 13 передачи данных (фиг. 7) и 8PSK выполняют в преобразователе 117 на фиг. 8, то есть, например, иллюстрация компоновки точек сигнала 8PSK для DVB-S.2.

При 8PSK для DVB-S.2, символ отображают на любую из 8 точек сигнала на окружности круга, радиус которого с центром в исходной точке плоскости IQ равен р.

На фиг. 20 показан пример компоновки на плоскости IQ из 16 символов в случае, когда спутниковый контур принят, как канал 13 передачи данных (фиг. 7) и 16APSK выполняют в преобразователе 117 на фиг. 8, то есть, например, иллюстрация компоновки точек сигналов 16APSK для DVB-S.2.

Буква А на фиг. 20 обозначает совокупность 16APSK для DVB-S.2.

В 16APSK для DVB-S.2 символ отображается на любую из в сумме 16 точек сигнала для 4 точек сигнала на окружности круга, радиус которого с центром в исходной точке плоскости IQ составляет R1, и 12 точек сигнала на окружности круга, радиус которого составляет R2 (>R1).

Буквой В на фиг. 20 иллюстрируется γ=R2/R1, что представляет собой отношение радиусов R2 и R1 в совокупности 16APSK для DVB-S.2.

В совокупности 16APSK для DVB-S.2, отношение γ радиусов R2 и R1 изменяется в зависимости от каждой скорости кодирования.

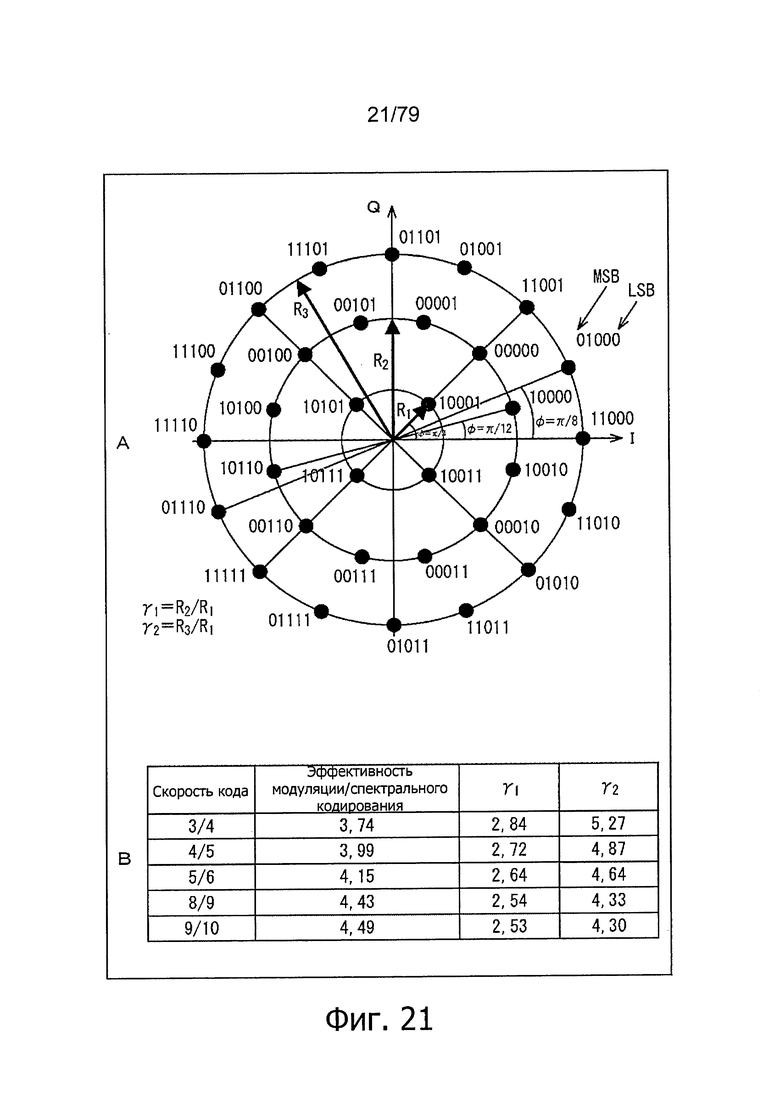

На фиг. 21 показан пример компоновки на плоскости IQ из 32 символов в случае, когда спутниковый контур принят, как канал 13 передачи данных (фиг. 7), и 32APSK выполняют в преобразователе 117 на фиг. 8, то есть, например, иллюстрация компоновки точек сигнала 32APSK для DVB-S.2.

В позиции А на фиг. 21 иллюстрируется совокупность 32APSK для DVB-S.2.

При 32APSK для DVB-S.2 символ отображается на любую из в сумме 32 точек сигнала из 4 точек сигнала на окружности круга, радиус которого с центром в исходной точке на плоскости IQ составляет R1, 12 точек сигнала на окружности круга, радиус которого составляет R2 (>R1) и 16 точек сигнала на окружности круга, радиус которого составляет R3 (>R2).

В позиции В на фиг. 21 иллюстрируется γ1=R2/R1, что представляет собой отношение радиусов R2 и R1 в совокупности 32APSK для DVB-S.2 и γ2=R3/R1, что представляет собой отношение радиусов R3 и R1.

В совокупности 32APSK для DVB-S.2, отношение γ1 радиусов R2 и R1 и отношение γ2 радиусов R3 и R1 изменяются в зависимости от каждой скорости кодирования.

Даже для символьных битов из символов каждой квадратурной модуляции (QPSK, 8PSK, 16APSK и 32APSK) в DVB-S.2, с иллюстрацией совокупностей на фиг. 18 - фиг. 21, аналогично случаям, показанным на фиг. 14 - фиг. 17, существуют сильные биты и слабые биты.

Как описано со ссылкой на фиг. 12 и фиг. 13, в отношении кода LDPC, выводимого кодером 115 LDPC (фиг. 8), существуют биты кода, сильные в отношении ошибки, и биты кодов, слабые в отношении ошибки.

Как описано со ссылкой на фиг. 14-21, в отношении символьных битов для символа ортогональной модуляции, выполняемой преобразователем 117, существуют сильные биты и слабые биты.

Поэтому, если биты кодов для кода LDPC, сильного в отношении ошибок, выделяют для слабых символьных битов для символа ортогональной модуляции, может быть в целом снижена устойчивость к ошибке.

Поэтому, рассматривается перемежитель, который выполняет перемежение битов кодов для кода LDPC таким образом, что биты кода для кода LDPC, слабого в отношении ошибки, выделяют для сильных битов (символьных битов) символа ортогональной модуляции.

Демультиплексор 25 на фиг. 9 может выполнять обработку перемежителя.

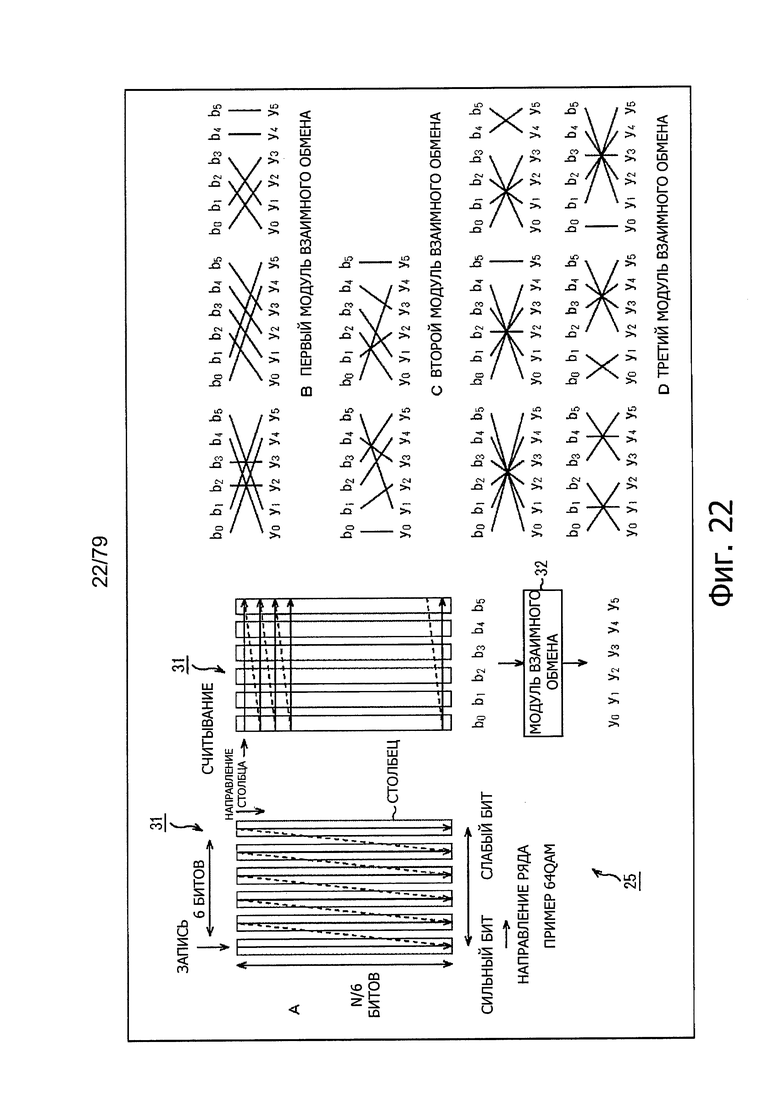

На фиг. 22 представлена иллюстрация обработки демультиплексора 25 по фиг. 9.

Таким образом, в позиции А на фиг. 18 иллюстрируется пример функциональной конфигурации демультиплексора 25.

Демультиплексор 25 включает в себя запоминающее устройство 31 и модуль 32 взаимного обмена.

Код LDPC подают из кодера 115 LDPC в запоминающее устройство 31.

Запоминающее устройство 31 имеет емкость хранения для хранения mb битов в направлении ряда (в поперечном направлении) и хранения N/(mb) битов в направлении столбца (в продольном) направлении. Запоминающее устройство 31 записывает биты кода для кодов LDPC, подаваемых в него в направлении столбца, считывает биты кода в направлении ряда, и подает биты кода в модуль 32 взаимного обмена.

В этом случае N (= длина информации K + длина M четности) представляет длину кода для кода LDPC, как описано выше.

Кроме того, m представляет количество битов для битов кода для кода LDPC, которое становится одним символом, и b представляет множитель, который является заданным положительным целым числом и используется для выполнения целочисленного умножения m. Демультиплексор 25 символизирует биты кода для кода LDPC в модулях заданных битов m. Однако множитель b представляет количество символов, полученных однократной символизацией в демультиплексоре 25.

В позиции А на фиг. 22 иллюстрируется пример конфигурации демультиплексора 25 в случае, когда способ модуляции представляет собой 64QAM и т.п., при котором выполняют отображение для любой из 64 точек сигнала, и, поэтому, количество m битов кода для кода LDPC, становящимся одним символом, составляет 6 битов.

В позиции А на фиг. 22 множитель b становится равным 1. Поэтому, запоминающее устройство 31 имеет емкость хранения, в которой произведение направления столбца × направление ряда составляет N/(6×1)×(6×1) битов.

В этом случае, область хранения запоминающего устройства 31, в которой направление ряда составляет 1 бит, и которая продолжается в направлении столбца, соответствующим образом называется ниже столбцом. В позиции А на фиг. 22 запоминающее устройство 31 включает в себя 6 (=6×1) столбцов.

В демультиплексоре 25 запись битов кода для кода LDPC в направлении вниз (направление столбца) с верхней стороны столбцов, составляющих запоминающее устройство 31, выполняют в направлении столбцов, представляющем собой направление направо с левой стороны.

Если запись битов кода заканчивается в нижней части самого правого столбца, биты кода считывают в модулях по 6 битов (mb битов) в направлении ряда с первого ряда всех столбцов, составляющих запоминающее устройство 31, и подают в модуль 32 взаимного обмена.

Модуль 32 взаимного обмена выполняет обработку взаимного обмена для положений взаимного обмена битов кода для 6 битов из запоминающего устройства 31, и выводит 6 битов, полученных в результате, как 6 символьных битов y0, у1, у2, у3, y4 и y5, представляющих один символ 64QAM.

Таким образом, биты кода, состоящие из mb битов (в данном случае, 6 битов) считывают из запоминающего устройства 31 в направлении ряда. Однако, если i-ый (i=0, 1, …, и mb-1) бит от старшего значащего бита из битов кода, состоящего из mb битов, считанных из запоминающего устройства 31, будет представлен, как бит bi, биты кода для 6 битов, которые считывают из запоминающего устройства 31 в направлении ряда, могут быть представлены, как биты b0, b1, b2, b3, b4 и b5, последовательно от старшего значащего бита.

Что касается весов столбцов, описанных со ссылкой на фиг. 12 и 13, бит кода в направлении бита b0 становится битом кода, сильным в отношении ошибки, и бит кода в направлении бита b5 становится битом кода, слабым в отношении ошибки.

В модуле 32 взаимного обмена может быть выполнена обработка взаимного обмена для взаимного обмена положениями битов кода b0-b5 из 6 битов из запоминающего устройства 31, таким образом, что биты кода, слабые в отношении ошибки, среди битов кода b0-b5 из 6 битов из запоминающего устройства 31, выделяют для сильных битов среди символьных битов y0-y5 одного символа 64QAM.

В этом случае, в качестве способов взаимного обмена, для выполнения взаимного обмена битами кодов b0-b5 из 6 битов из запоминающего устройства 31 и выделения битов кода от b0 до b5 из 6 битов для 6 символьных битов y0-y5, представляющих один символ 64QAM, рассматриваются различные способы, предложенные отдельными компаниями.

В позиции В на фиг. 22 иллюстрируется первый способ взаимного обмена, в позиции С на фиг. 22 иллюстрируется второй способ взаимного обмена, и в позиции D на фиг. 22 иллюстрируется третий способ взаимного обмена.

В позиции В на фиг. 22 - в позиции D на фиг. 22 (так же, как и на фиг. 23, которая будет описана ниже), сегмент линии, соединяющий биты bi и yj, означает, что бит bi кода выделен для символьного бита yj для символа (для которого был выполнен обмен с положением символьного бита yj).

В качестве первого способа взаимного обмена в позиции на В позиции В на фиг. 22, предлагается использование любого одного из трех видов способов взаимного обмена. В качестве второго способа взаимного обмена, показанного в позиции С на фиг. 22, предлагается использовать любой один из двух видов способов взаимного обмена.

В качестве третьего способа взаимного обмена, показанного в позиции D на фиг. 22, предлагается последовательно выбирать шесть видов способов взаимного обмена и использовать способ взаимного обмена.

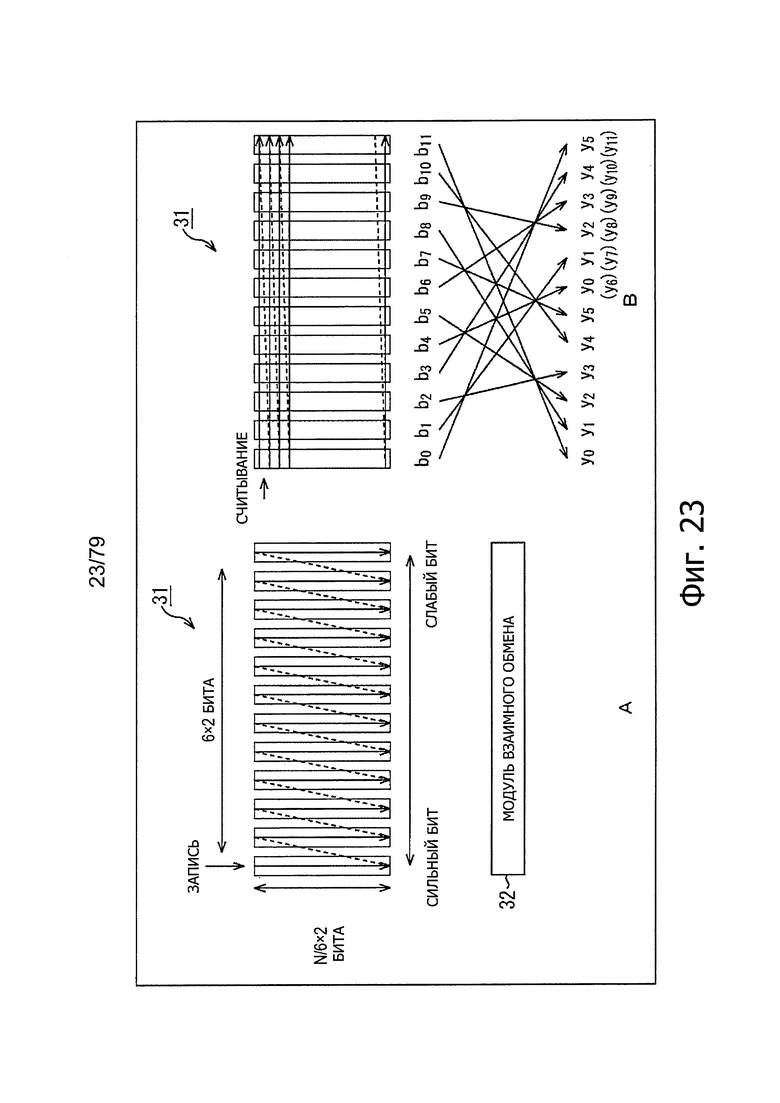

На фиг. 23 иллюстрируется пример конфигурации демультиплексора 25 в случае, когда способ модуляции представляет собой 64QAM и т.п., при котором выполняют отображение на любую из 64 точек сигнала (поэтому, количество m битов из битов кода для кода LDPC, отображенных на один символ, составляет 6 битов, так же, как на фиг. 22), и множитель b равен 2, и четвертый способ взаимного обмена.

Когда множитель b равен 2, запоминающее устройство 31 имеет емкость хранения, в которой направление столбцов × направление рядов составляет N/(6×2)×(6×2) битов и включает в себя 12 (=6×2) столбцов.

На фиг. 23 иллюстрируется последовательность записи кода LDPC в запоминающее устройство 31.

В демультиплексоре 25, как описано со ссылкой на фиг. 22, запись битов кода для кода LDPC в направлении вниз (направление столбцов) с верхней стороны столбцов, составляющих запоминающее устройство 31, выполняют в направлении столбцов, в направлении назад с левой стороны.

Если запись битов кода заканчивается на нижней части самого правого столбца (если запись кодового слова была закончена), биты кода считывают в модуле из 12 битов (mb битов) в направлении ряда из первого ряда всех столбцов, составляющих запоминающее устройство 31, и подают в модуль 32 взаимного обмена.

Модуль 32 взаимного обмена выполняет обработку взаимного обмена для взаимного обмена положениями битов кода из 12 битов, поступивших из запоминающего устройства 31, используя четвертый способ взаимного обмена, и выводит 12 битов, полученных в результате, как 12 битов, представляющих два символа (b символов) для 64QAM, то есть, шесть символьных битов y0, у1, у2, у3, y4 и y5, представляющих один символ для 64QAM, и шесть символьных битов y0, у1, у2, у3, y4 и y5, представляющих следующий один символ.

В этом случае, в позиции В на фиг. 23 иллюстрируется четвертый способ взаимного обмена для обработки взаимного обмена с использованием модуля 32 взаимного обмена, показанного в позиции А на фиг. 23.

Когда множитель b равен 2 (или 3, или больше), при обработке взаимного обмена, биты кода для mb битов выделяют для символьных битов для mb битов, для b последовательных символов. В дальнейшем пояснении, включающем в себя пояснение на фиг. 23, (i+1)-ый бит от старшего значащего бита из символьных битов mb битов из b последовательных символов представлено, как бит (символьный бит) yi, для удобства пояснения.

Какой вид битов кода соответствует для взаимного обмена, то есть, для улучшения частоты ошибок в канале передачи данных AWGN и т.п., зависит от скорости кодирования или длины кода для кода LDPC и способа модуляции.

Перемежение четности

Далее, со ссылкой на фиг. 24-26, будет описано перемежение четности, выполняемое перемежителем 23 четности по фиг. 9

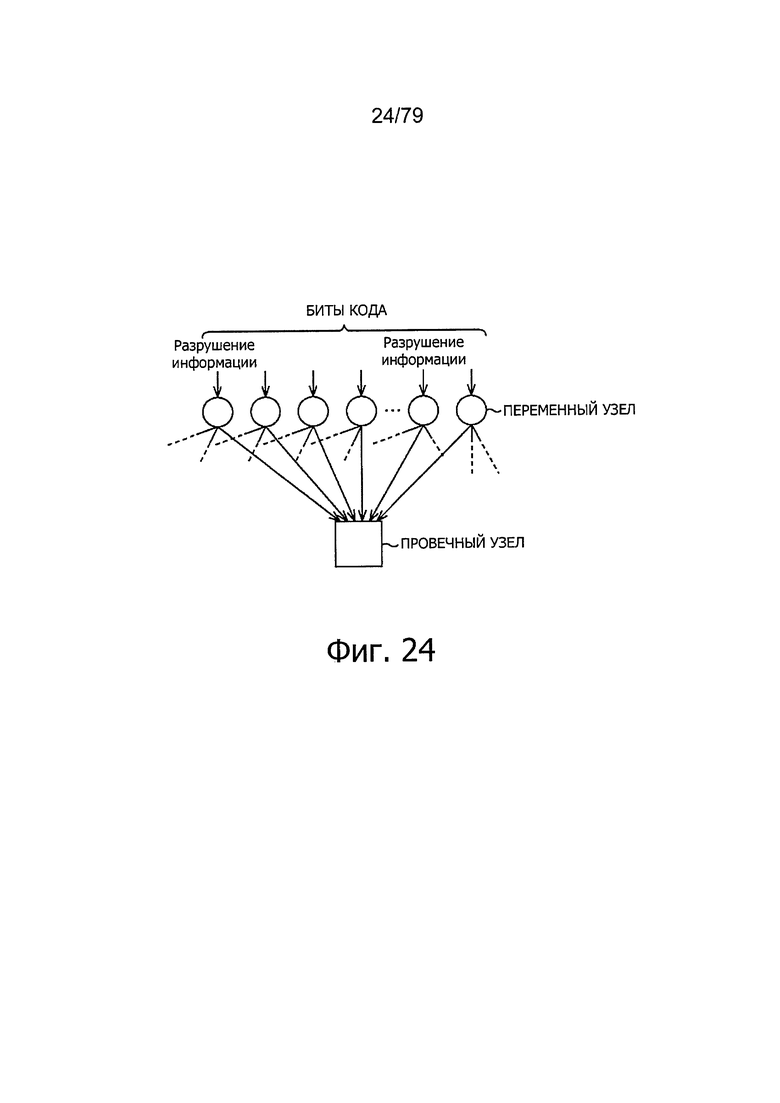

На фиг. 24 иллюстрируется (часть) графа Таннера матрицы проверки на четность кода LDPC.

Как представлено на фиг. 24, если множество, например, два переменных узла среди переменных узлов (соответствующих им битов кода), одновременно подключенных к проверочному узлу, становятся ошибкой, например в случае разрушения информации, проверочный узел возвращает сообщение, в котором вероятность того, что значение равно О, и вероятность того, значение равно 1, равны друг другу, во все переменные узлы, подключенные к проверочному узлу. По этой причине, если во множестве переменных узлов, подключенных к одному проверочному узлу, одновременно происходит разрушение информации, происходит ухудшение характеристик декодирования.

В то же время, код LDPC, который выводит кодер 115 LDPC по фиг. 8, и который определен в стандарте DVB-S.2 и т.п., представляет собой код IRA, и матрица ΗT четности матрицы Η проверки на четность становится ступенчатой структурой, как представлено на фиг. 11.

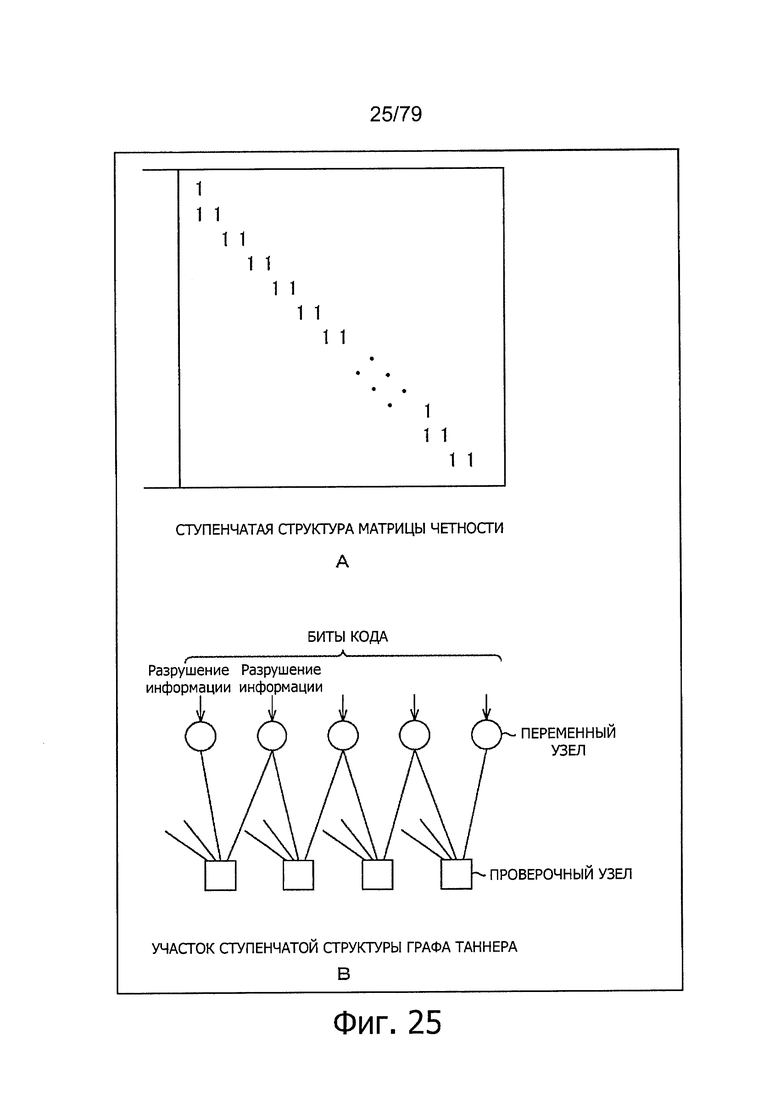

На фиг. 25 иллюстрируется матрица ΗT четности, становящаяся ступенчатой структурой, и граф Таннера, соответствующий матрице ΗT четности.

Таким образом, в позиции А на фиг. 25 иллюстрируется матрица ΗT четности, становящаяся ступенчатой структурой, и в позиции В на фиг. 25 иллюстрируется граф Таннера, соответствующий матрице ΗT четности, показанный в позиции А на фиг. 25.

В матрице ΗT четности с ступенчатой структурой элементы, равные 1, расположены рядом в каждом ряду (исключая первый ряд). Поэтому, в графе Таннера матрицы ΗT четности два соседних переменных узла, соответствующих столбцу из двух соседних элементов, в которых значение матрицы ΗT четности равно 1, соединены с одним и тем же проверочным узлом.

Поэтому, когда биты четности, соответствующие двум упомянутым выше соседним переменным узлам, становятся ошибками одновременно, из-за пакетной ошибки и разрушения данных, и так далее, проверочный узел, подключенный к двум переменным узлам (переменным узлам для поиска сообщения путем использования битов четности), соответствующим тем двум битам четности, которые стали ошибкой, возвращает сообщение о том, что вероятность для значения 0 и вероятность для значения 1 представляют собой равные значения вероятности, в переменные узлы, подключенные к проверочному узлу, и, поэтому, характеристики декодирования ухудшаются. Кроме того, когда первая длина пакета (количество битов из битов четности, которые непрерывно становятся ошибками) становится большой, количество проверочных узлов, которые возвращают сообщение равной вероятности, увеличивается, и рабочая характеристика декодирования дополнительно ухудшается.

Поэтому, перемежитель 23 четности (фиг. 9) выполняет перемежение четности для перемежения битов четности кода LDPC из кодера 115 LDPC в положения других битов четности, для предотвращения ухудшения характеристик декодирования.

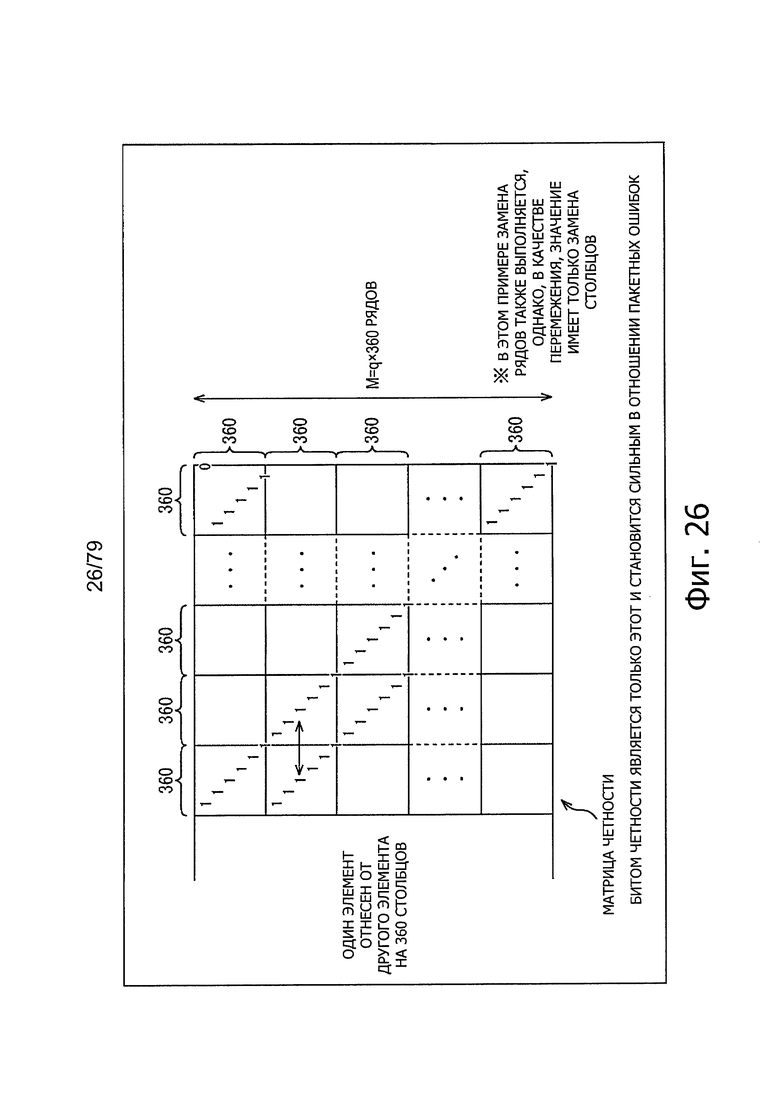

На фиг. 26 показана матрица ΗT четности из матрицы Η проверки на четность, соответствующей коду LDPC после выполнения перемежения четности перемежителем 23 четности по фиг. 9.

В этом случае, информационная матрица HA матрицы Η проверки на четность, соответствующая коду LDPC, которую выводит кодер 115 LDPC и определенная в стандарте DVB-S.2 и т.п., становится циклической структурой.

Циклическая структура означает структуру, в которой определенный столбец соответствует столбцу, получаемому в результате циклического сдвига другого столбца. Например, циклическая структура включает в себя структуру, в которой положение 1 каждого ряда Ρ из столбцов становится положением, полученным в результате циклического сдвига первого столбца из Ρ столбцов в направлении столбцов на величину, пропорциональную значению q, полученному путем деления длины M четности, для каждого из Ρ столбцов. Далее Ρ столбцов в циклической структуре соответствующим образом называются количеством столбцов модуля циклической структуры.

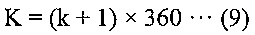

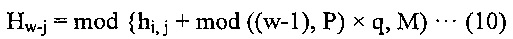

В качестве кода LDPC, определенного в стандарте, таком как DVB-S.2, как описано со ссылкой на фиг. 12 и фиг. 13, существуют два вида кодов LDPC, длина N кода которых составляет 64800 битов и 16200 битов, и для обоих из этих двух видов кодов LDPC количеством Ρ столбцов, которое составляет модуль циклической структуры, определено, как 360, число, которое представляет собой один из делителей, исключая 1 и M среди делителей длины M четности.

Длина M четности принимает значение, кроме простых чисел, представленное уравнением M=q×Ρ=q×360, используя разные значения q, в соответствии со скоростью кодирования. Поэтому, аналогично количеству Ρ столбцов модуля циклической структуры, значение q представляет другое значение, чем 1 и M среди делителей длины M четности, и его получают путем деления длины M четности на количество Ρ столбцов модуля циклической структуры (произведение Ρ и q, которые представляют собой делители длины M четности, становится равным длине M четности).

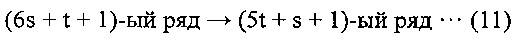

Как описано выше, когда предполагается, что длина информации становится равной K, предполагается, что целое число, равное или большее, чем 0 и меньшее, чем Р, равно х, и предполагается, что целое число, равное или большее, чем 0 и меньшее, чем q, равно у, перемежитель 23 четности выполняет перемежение K+qx+y+1-ого бита кода среди битов кода для кода LDPC из N битов до положения K+Ру+х+1-ого бита кода, в качестве перемежения четности.

Поскольку как K+qx+y+1-ый бит кода, так и K+Py+x+1-ый бит кода, представляют собой биты кода после K+1-ого бита, они являются битами четности, и, поэтому, положения битов четности кода LDPC перемещаются в соответствии с перемежением четности.

В соответствии с перемежением четности (соответствующие им биты четности), переменные узлы, соединенные с проверочным узлом, разделяют по количеству Ρ столбцов модуля циклической структуры, то есть, 360 битов в этом случае. По этой причине, когда длина пакета меньше, чем 360 битов, можно предотвратить ситуацию, когда множество переменных узлов, подключенных к одному и тому же проверочному узлу, одновременно становятся ошибкой. В результате, устойчивость к пакетным ошибкам может быть улучшена.

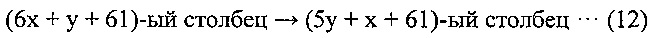

Код LDPC после перемежения, для перемежения (K+qx+у+1)-ого бита кода в положение (K+Ру+x+1)-ого бита кода сопоставляют с кодом LDPC матрицы проверки на четность (ниже называется преобразованной матрицей проверки на четность) полученной в результате выполнения замены столбца, для замены (K+qx+у+1)-ого столбца исходной матрицы Η проверки на четность на (K+Ру+x+1)-ый столбец.

В матрице четности преобразованной матрицы проверки на четность, как представлено на фиг. 26, появляется псевдоциклическая структура, в которой используется Ρ столбцов (на фиг. 26, 360 столбцов) в качестве модуля.

В этом случае, псевдоциклическая структура означает структуру, в которой формируется циклическая структура, за исключением ее части. Преобразованная матрица проверки на четность, которая получается в результате выполнения замены столбца, соответствующая перемежению четности в отношении матрицы проверки на четность кода LDPC, определенного в стандарте DVB-S.2 и т.п., становится псевдоциклической структурой, а не (идеальной) циклической структурой, поскольку количество элементов, равных 1, меньше чем 1 (существуют элементы, равные 0) в части (матрица со сдвигом, которая будет описана ниже) 360 рядов × 360 столбцов в ее части в правом углу.

Преобразованная матрица проверки на четность по фиг. 26 становится матрицей, которую получают в результате выполнения замены столбца, соответствующей перемежению четности, и замены (замены рядов) ряда для конфигурирования преобразованной матрицы проверки на четность с составляющей марицей, которая будет описана ниже, в отношении исходной матрицы Η проверки на четность.

Перемежение со скручиванием столбцов

Далее, со ссылкой на фиг. 27-30, будет описано перемежение со скручиванием столбцов, соответствующее обработке с изменением компоновки перемежителем 24 со скручиванием столбцов по фиг. 9.

В устройстве 11 передачи на фиг. 8, один или больше битов из битов кода для кода LDPC передают, как один символ. Таким образом, когда два бита из битов кода установлены, как один символ, используют QPSK, как способ модуляции и, когда четыре бита из битов кода установлены, как один символ, используют APSK или 16QAM, как способ модуляции.

Таким образом, когда два или больше бита из битов кода передают, как один символ, если генерируется разрушение информации в определенном символе, все из битов кода этого символа становятся ошибкой (разрушенной информацией).

Поэтому, необходимо предотвратить соединение переменных узлов, соответствующих битам кода одного символа с одним и тем же проверочным узлом для уменьшения вероятности того, что множество переменных узлов, подключенных к одному проверочному узлу (битов кода, соответствующих им), одновременно становятся разрушенной информацией для улучшения характеристик декодирования.

В то же время, как описано выше, в матрице H проверки на четность кода LDPC, который выводится кодером 115 LDPC и определен в стандарте DVB-S.2 и т.п., матрица HA информации имеет циклическую структуру, и матрица HT четности имеет ступенчатую структуру. Как описано со ссылкой на фиг. 26, в преобразованной матрице проверки на четность, которая становится матрицей проверки на четность кода LDPC после перемежения четности, циклическая структура (фактически, псевдоциклическая структура, как описано выше) появляется в матрице четности.

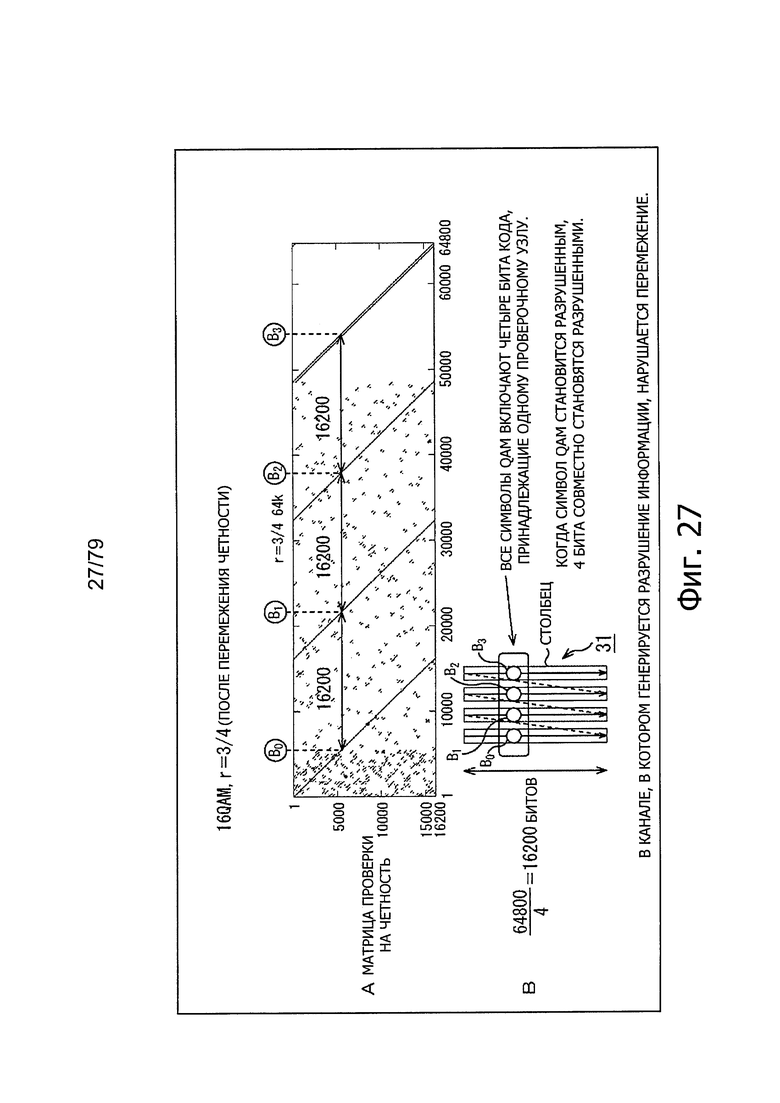

На фиг. 27 иллюстрируется преобразованная матрица проверки на четность.

Таким образом, в позиции А на фиг. 27 иллюстрируется преобразованная матрица проверки на четность матрицы H проверки на четность кода LDPC, в которой длина N кода составляет 64800 битов, и скорость (r) кодирования составляет 3/4.

В позиции А на фиг. 27, в преобразованной матрице проверки на четность, положение элемента, в котором значение становится 1, показано точкой (⋅).

В позиции В на фиг. 27 иллюстрируется обработка, выполняемая демультиплексором 25 (фиг. 9), в отношении кода LDPC преобразованной матрицы проверки на четность, показанной в позиции А на фиг. 27, то есть, кода LDPC после перемежения четности.

В позиции В на фиг. 27, на основе предположения, что способ модуляции представляет собой способ, в котором символ отображается на любую из 16 точек сигнала, таких как 16APSK и 16QAM, биты кода для кода LDPC после перемежения четности записывают в четырех столбцах, формирующих запоминающее устройство 31 демультиплексора 25 в направлении столбца.

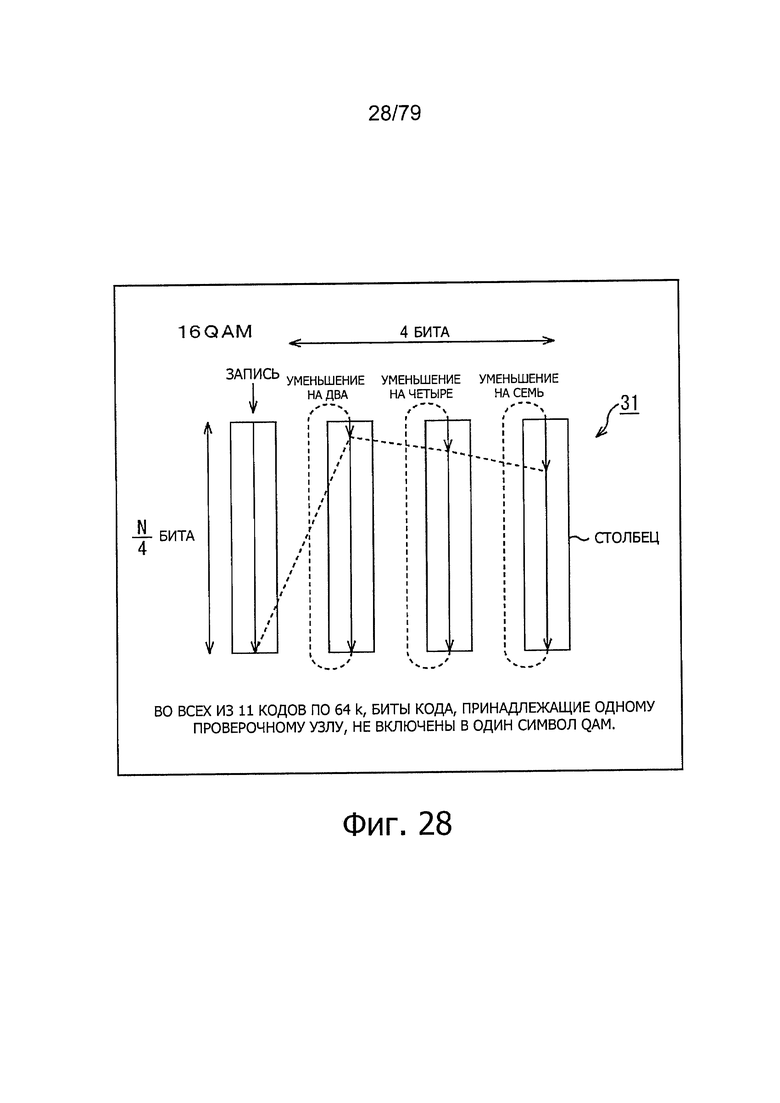

Биты кода, которые записаны в направлении столбца в четырех столбцах, составляющих запоминающее устройство 31, считывают в модуле из четырех битов в направлении ряда, и они становятся одним символом.