Область техники, к которой относится изобретение

Настоящее изобретение касается устройства обработки данных и способа обработки данных и, например, в частности касается устройства обработки данных и способа обработки данных, которые способны обеспечить хорошее качество связи при передаче данных с использованием LDPC кода.

Уровень техники

LDPC-код (Код с малой плотностью проверок на четность) обладает высокой способностью исправления ошибок и в последние годы широко применяется в системах передачи, в том числе в системах цифрового спутникового вещания, таких как используемая в Европе система DVB-S.2 (цифровое телевидение) (смотри, например, непатентный документ 1). Кроме того, исследована возможность применения LDPC-кода в наземном цифровом вещании следующего поколения, таком как DVB-T.2.

В последних исследованиях показано, что LDPC-код показывает характеристики, близкие к границе Шеннона при увеличении длины кода аналогично турбо-коду. Так как для LDPC-кода кратчайшее расстояние пропорционально длине кода, то этот код отличается превосходной вероятностной характеристикой исправления блоков ошибок и редко имеет место так называемый эффект замедления падения вероятности ошибки, который наблюдается при декодировании турбо-кода.

Список цитируемой литературы

Литература, не относящаяся к патентам

Непатентный документ 1: DVB-S.2: ETSIEN 302 307 V1.2.1 (2009-08)

Раскрытие изобретения

Техническая задача

В стандартах DVB, таких как DVB-S.2, DVB-T.2 и DVB-C.2, в которых используют LDPC-код, LDPC-код является символом (преобразован в символ) ортогональной модуляции (цифровой модуляции), такой как QPSK (квадратурная фазовая манипуляция) и символ преобразуют в сигнальную точку ортогональной модуляции и передают.

При передаче данных с использованием LDPC-кода, такой как описанный выше стандарт DVB-S.2, обязательно обеспечивают хорошее качество связи.

С учетом указанных обстоятельств, в соответствии с вариантом осуществления настоящего изобретения, желательно обеспечить хорошее качество связи при передаче данных с использованием LDPC-кода.

Решение задачи

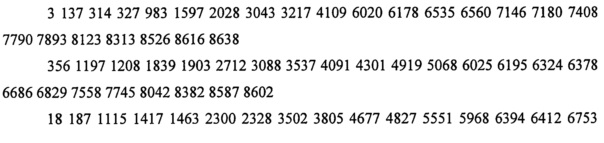

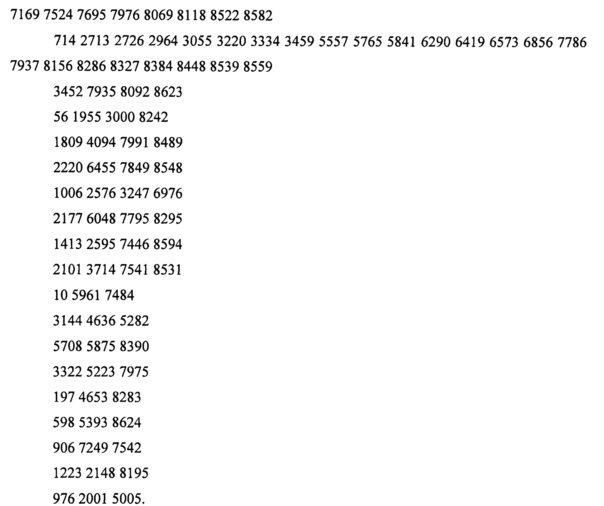

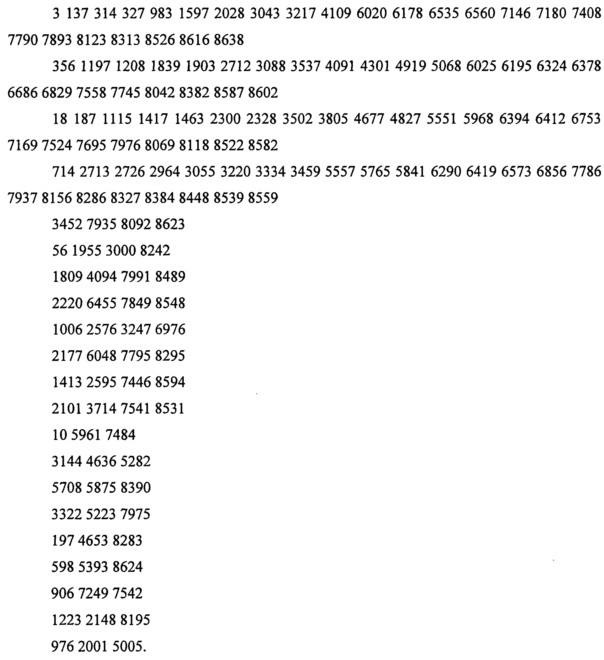

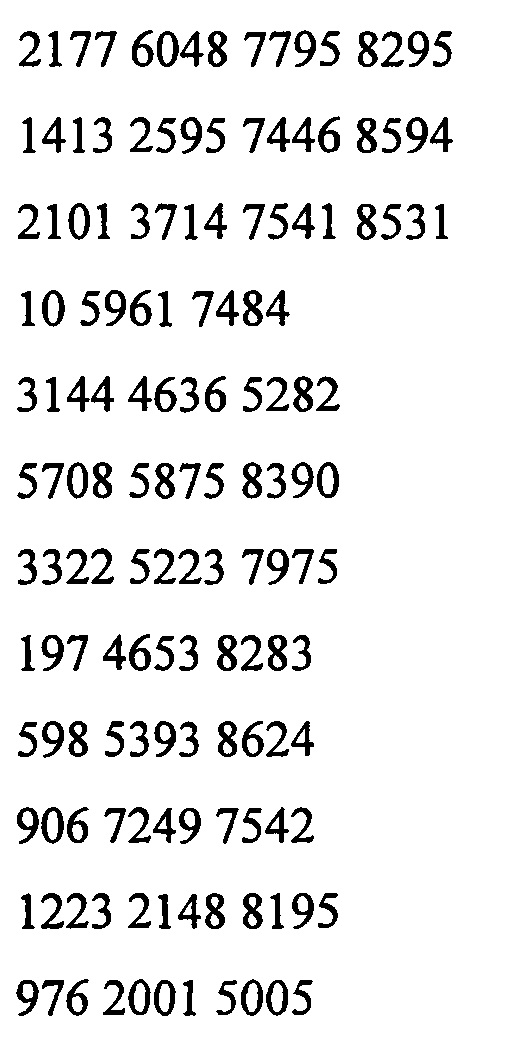

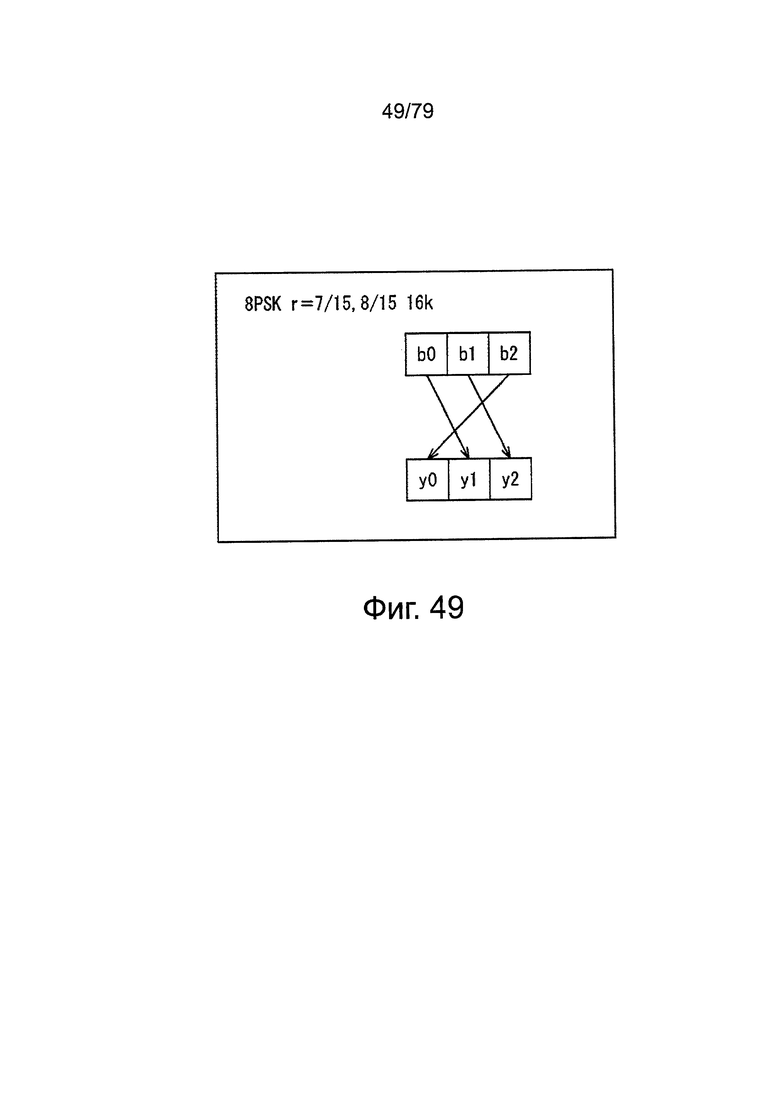

Первое устройство обработки данных или способ обработки данных по настоящему изобретению представляет собой устройство обработки данных или способ обработки данных, которые включают в себя следующее: блок/этап обратной перестановки для осуществления обработки обратной перестановки, для возвращения исходной позиции переставленного бита кода, полученного из данных, переданных от устройства передачи; и блок/этап декодирования для декодирования LDPC-кода, полученного при обработке обратной перестановки, при этом устройство передачи содержит блок кодирования, выполненный с возможностью осуществления LDPC кодирования на основе проверочной матрицы четности LDPC-кода, для которого длина кода равна 16200 битам и скорость кодирования равна 7/15, и блок перестановки, выполненный с возможностью перестановки бита LDPC-кода, для которого длина кода равна 16200 битам и скорость кодирования равна 7/15, с битом символа, соответствующим любой из 8 сигнальных точек, определенных 8-позиционной PSK. Когда 3 бита из битов кода, сохранены в трех блоках памятей емкостью 16200/3 битов и считываются побитно из блоков памятей, выделяются одному символу, (#i+1)-й бит от самого старшего бита из 3 битов из битов кода устанавливается в бит b#i, (#i+1)-й бит от самого старшего бита из 3 битов из битов символа одного символа устанавливается в бит y#i, а блок перестановки выполнен с возможностью перестановки: бита b0 и бита y1, бита b1 и бита y0, и бита b2 и бита y2. LDPC-код содержит информационный бит и бит четности. Проверочная матрица четности содержит часть информационной матрицы, соответствующую информационному биту, и часть матрицы четности, соответствующую биту четности. Часть информационной матрицы показана таблицей исходных значений для проверочной матрицы. Таблица исходных значений для проверочной матрицы четности является таблицей, показывающей позиции элементов, равных 1, части информационной матрицы для каждых 360 столбцов и имеет вид:

В первом устройстве обработки данных и способе обработки данных по настоящему изобретению осуществляют обработку обратной перестановки для возвращения исходной позиции переставленного бита кода, полученного из данных, переданных устройством передачи; и декодирование LDPC кода полученного посредством указанной обработки обратной перестановки. Устройство передачи содержит блок кодирования, выполненный с возможностью осуществления LDPC кодирования на основе проверочной матрицы четности LDPC-кода, для которого длина кода равна 16200 битам и скорость кодирования равна 7/15, блок перестановки, выполненный с возможностью перестановки бита LDPC-кода, для которого длина кода равна 16200 битам и скорость кодирования равна 7/15, с битом символа, соответствующим любой из 8 сигнальных точек, определенных 8-позиционной PSK. Когда 3 бита из битов кода, сохранены в трех блоках памятей емкостью 16200/3 битов и считываются побитно из блоков памятей, выделяются одному символу, (#i+1)-й бит от самого старшего бита из 3 битов из битов кода устанавливаются в бит b#i, (#i+1)-й бит от самого старшего бита из 3 битов из битов символа одного символа устанавливается в бит y#i, а блок перестановки выполнен с возможностью перестановки: бита b0 и бита y1, бита b1 и бита y0, и бита b2 и бита y2. LDPC-код содержит информационный бит и бит четности. Проверочная матрица четности содержит часть информационной матрицы, соответствующую информационному биту, и часть матрицы четности, соответствующую биту четности. Часть информационной матрицы показана таблицей исходных значений для проверочной матрицы. Таблица исходных значений для проверочной матрицы четности является таблицей, показывающей позиции элементов, равных 1, части информационной матрицы для каждых 360 столбцов и имеет вид:

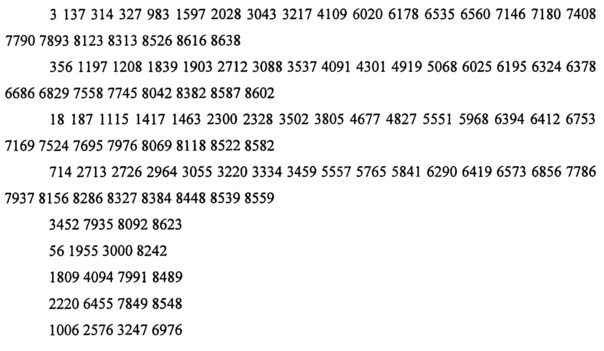

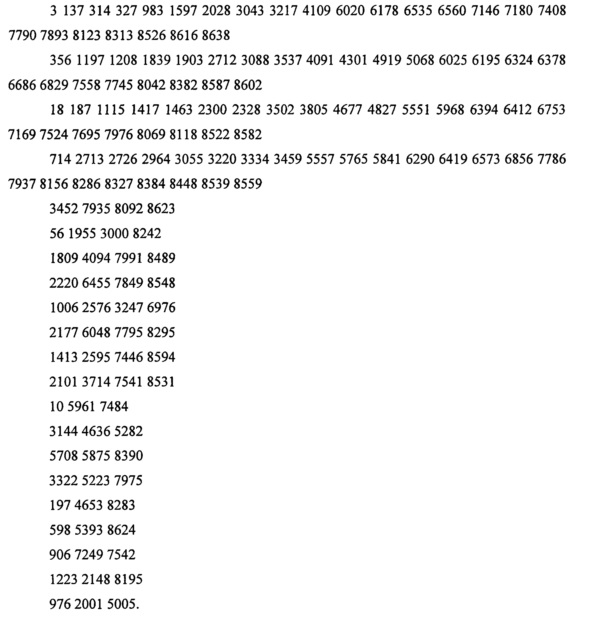

Второе устройство обработки данных или способ обработки данных по настоящему изобретению представляет собой устройство обработки данных или способ обработки данных, которые включают в себя следующее: блок/этап обратной перестановки для осуществления обработки обратной перестановки, для возвращения исходной позиции переставленного бита кода, полученного из данных, переданных от устройства передачи; и блок/этап декодирования для декодирования LDPC-кода, полученного при обработке обратной перестановки, при этом устройство передачи содержит блок кодирования, выполненный с возможностью осуществления LDPC кодирования на основе проверочной матрицы четности LDPC-кода, для которого длина кода равна 16200 битам и скорость кодирования равна 7/15, и блок перестановки, выполненный с возможностью перестановки бита LDPC-кода, для которого длина кода равна 16200 битам и скорость кодирования равна 7/15, с битом символа, соответствующим любой из 16 сигнальных точек, определенных 16-позиционной APSK. Когда 4 бита кода, которые сохранены в четырех блоках памятей емкостью 16200/4 битов и которые побитно считаны из блоков памятей, сопоставляют одному символу, (#i+1)-й бит от самого старшего бита из 4 битов кода обозначают через бит b#i, (#i+1)-й бит от самого старшего бита из 4 битов символа одного символа обозначают через бит y#i, и в блоке перестановки сопоставляют бит b0 и бит y2, бит b1 и бит y1, бит b2 и бит y0 и бит b3 и бит y3. LDPC-код содержит информационный бит и бит четности. Проверочная матрица четности содержит часть информационной матрицы, соответствующую информационному биту, и часть матрицы четности, соответствующую биту четности. Часть информационной матрицы показана таблицей исходных значений для проверочной матрицы. Таблица исходных значений для проверочной матрицы четности является таблицей, показывающей позиции элементов, равных 1, части информационной матрицы для каждых 360 столбцов и имеет вид:

Во втором устройстве обработки данных и способе обработки данных по настоящему изобретению осуществляют обработку обратной перестановки для возвращения исходной позиции переставленного бита кода, полученного из данных, переданных устройством передачи; и декодирование LDPC кода полученного посредством указанной обработки обратной перестановки. Устройство передачи содержит блок кодирования, выполненный с возможностью осуществления LDPC кодирования на основе проверочной матрицы четности LDPC-кода, для которого длина кода равна 16200 битам и скорость кодирования равна 7/15, блок перестановки, выполненный с возможностью перестановки бита LDPC-кода, для которого длина кода равна 16200 битам и скорость кодирования равна 7/15, с битом символа, соответствующим любой из 16 сигнальных точек, определенных 16-позиционной APSK. Когда 4 бита кода, которые сохранены в четырех блоках памятей емкостью 16200/4 битов и которые побитно считаны из блоков памятей, сопоставляют одному символу, (#i+1)-й бит от самого старшего бита из 4 битов кода обозначают через бит b#i, (#i+1)-й бит от самого старшего бита из 4 битов символа одного символа обозначают через бит y#i, и в блоке перестановки сопоставляют бит b0 и бит y2, бит b1 и бит y1, бит b2 и бит y0 и бит b3 и бит y3. LDPC-код содержит информационный бит и бит четности. Проверочная матрица четности содержит часть информационной матрицы, соответствующую информационному биту, и часть матрицы четности, соответствующую биту четности. Часть информационной матрицы показана таблицей исходных значений для проверочной матрицы. Таблица исходных значений для проверочной матрицы четности является таблицей, показывающей позиции элементов, равных 1, части информационной матрицы для каждых 360 столбцов и имеет вид:

Устройство обработки данных может являться независимым устройством и может являться внутренним блоком, входящим в состав одного устройства.

Полезные свойства изобретения

В соответствии с вариантом осуществления настоящего изобретения возможно обеспечить хорошее качество связи при передаче данных с использованием LDPC-кода.

Полезные свойства, описанные в настоящем документе, являются только примерами и полезные свойства некоторого варианта осуществления настоящего изобретения не ограничены полезными свойствами, описанными в настоящем документе, и могут существовать другие полезные свойства.

Краткое описание чертежей

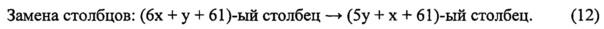

Фиг. 1 - вид, показывающий проверочную матрицу Н LDPC-кода;

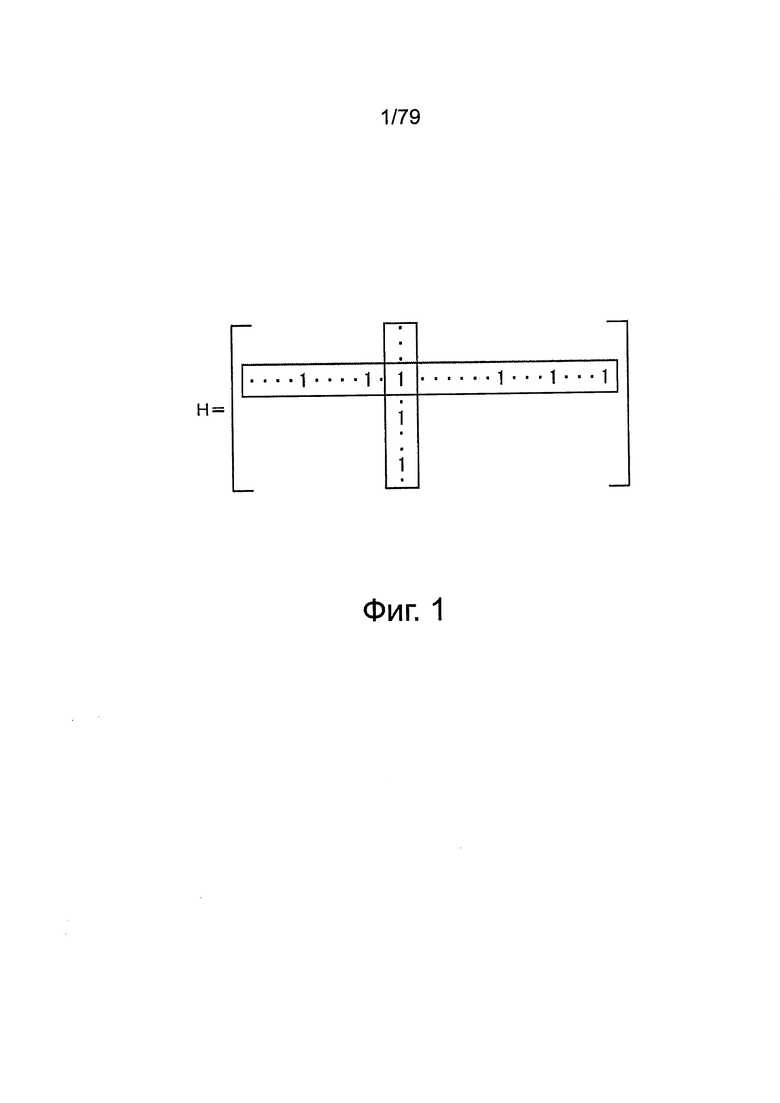

фиг. 2 - вид, показывающий блок-схему, иллюстрирующую последовательность декодирования LDPC-кода;

фиг. 3 - вид, показывающий пример проверочной матрицы LDPC-кода;

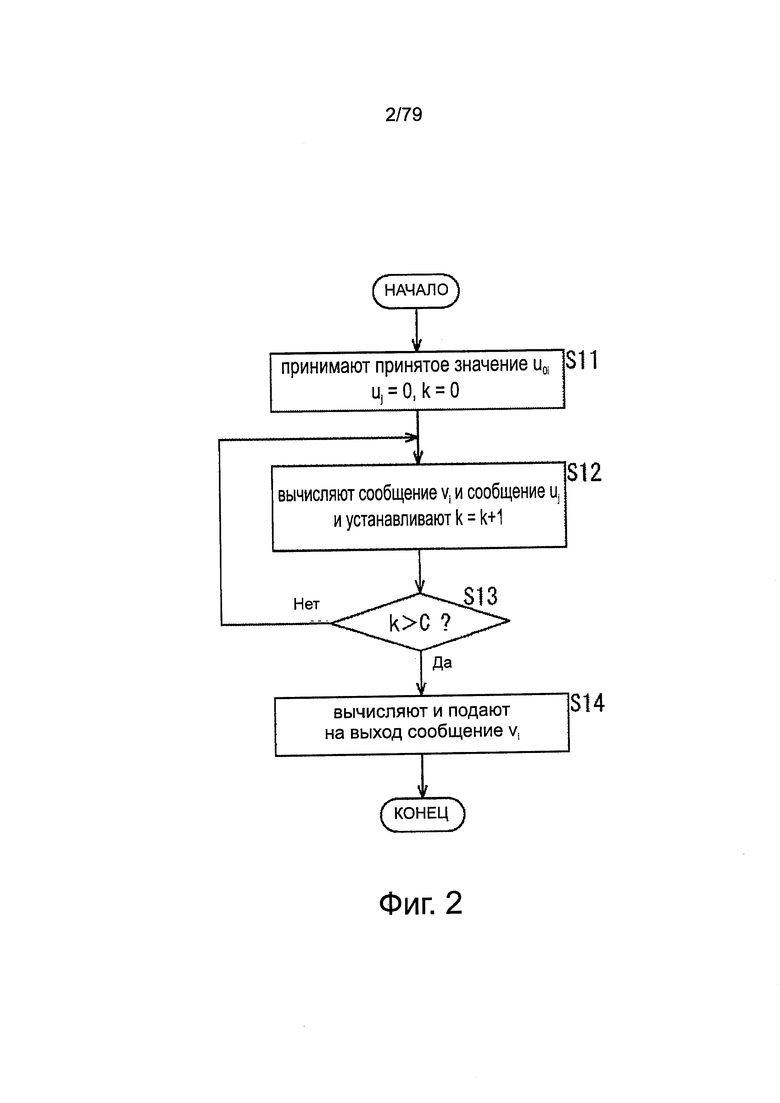

фиг. 4 - вид, показывающий граф Таннера проверочной матрицы;

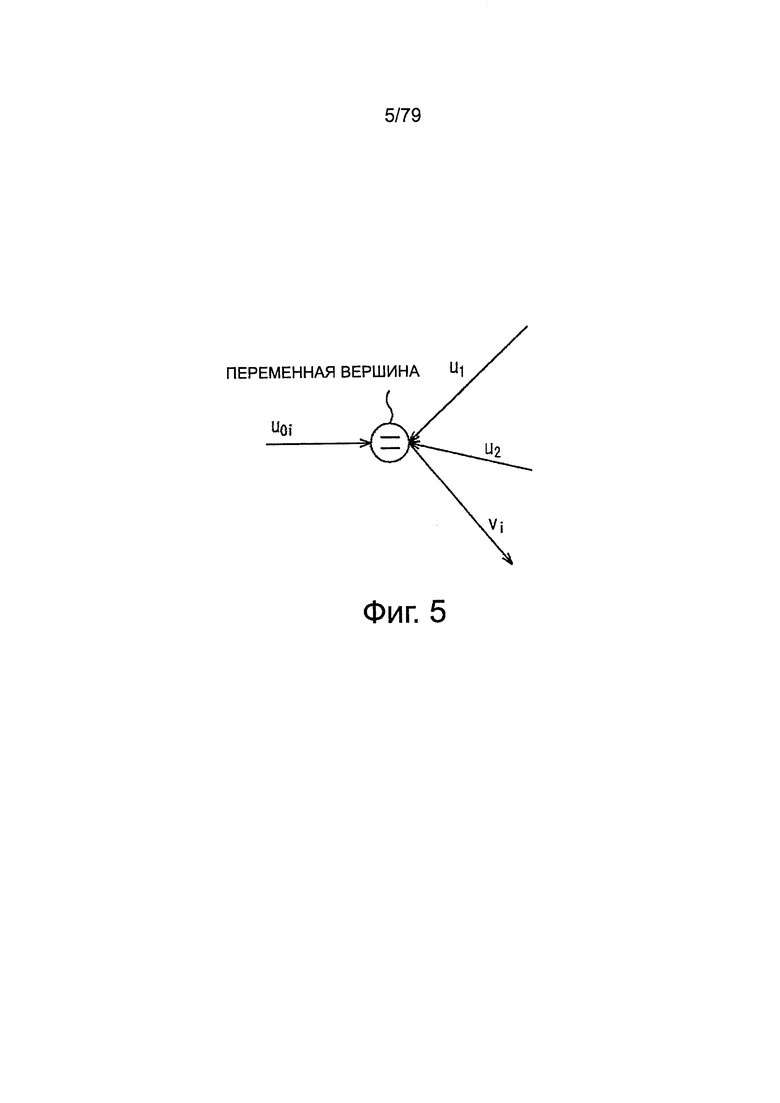

фиг. 5 - вид, показывающий переменную вершину;

фиг. 6 - вид, показывающий проверочную вершину;

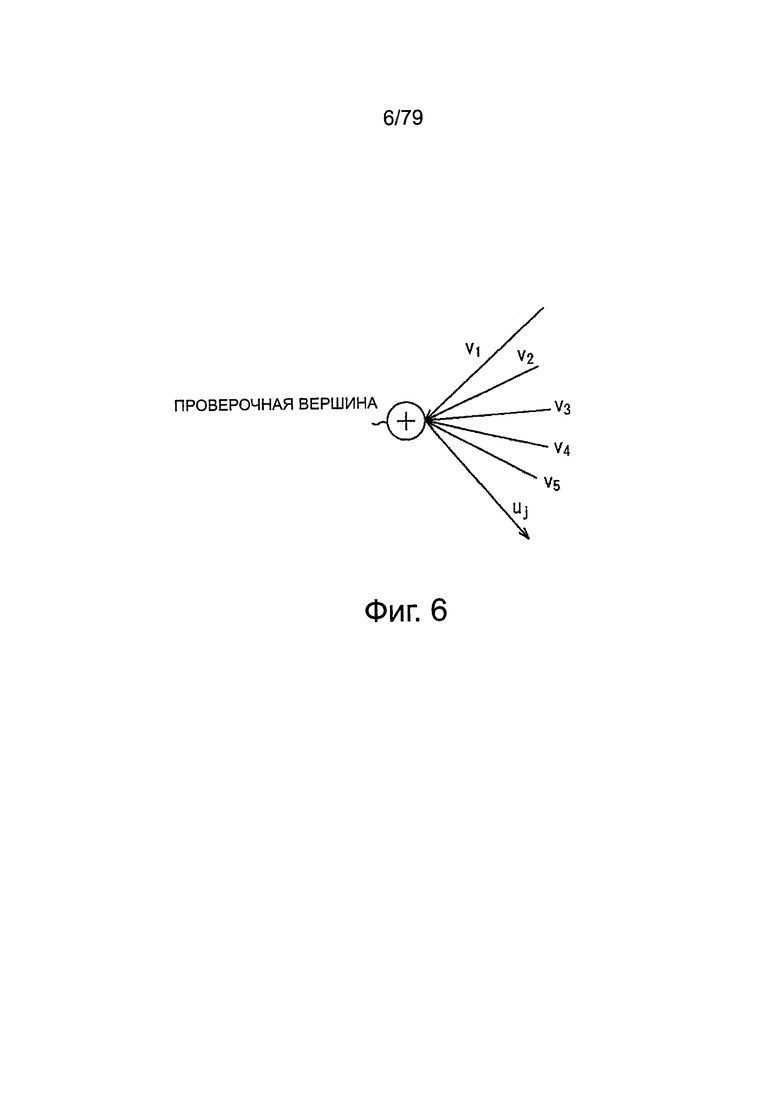

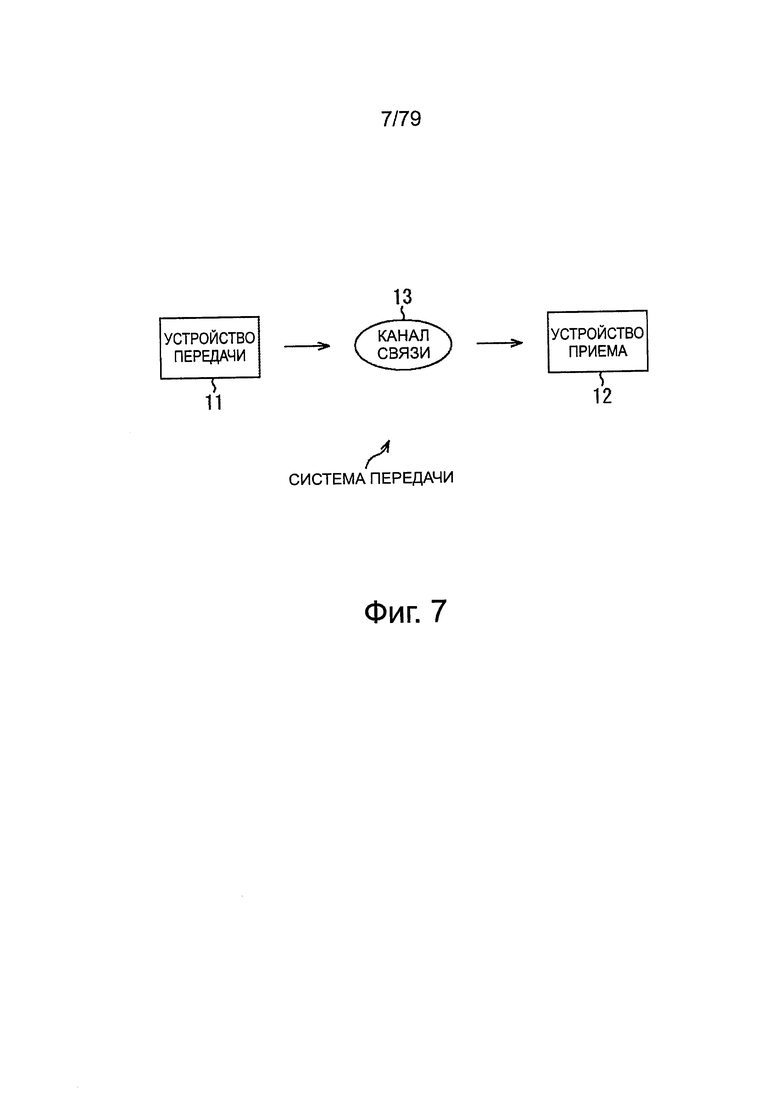

фиг. 7 - вид, показывающий пример конфигурации варианта осуществления системы передачи, в которой применено настоящее изобретение;

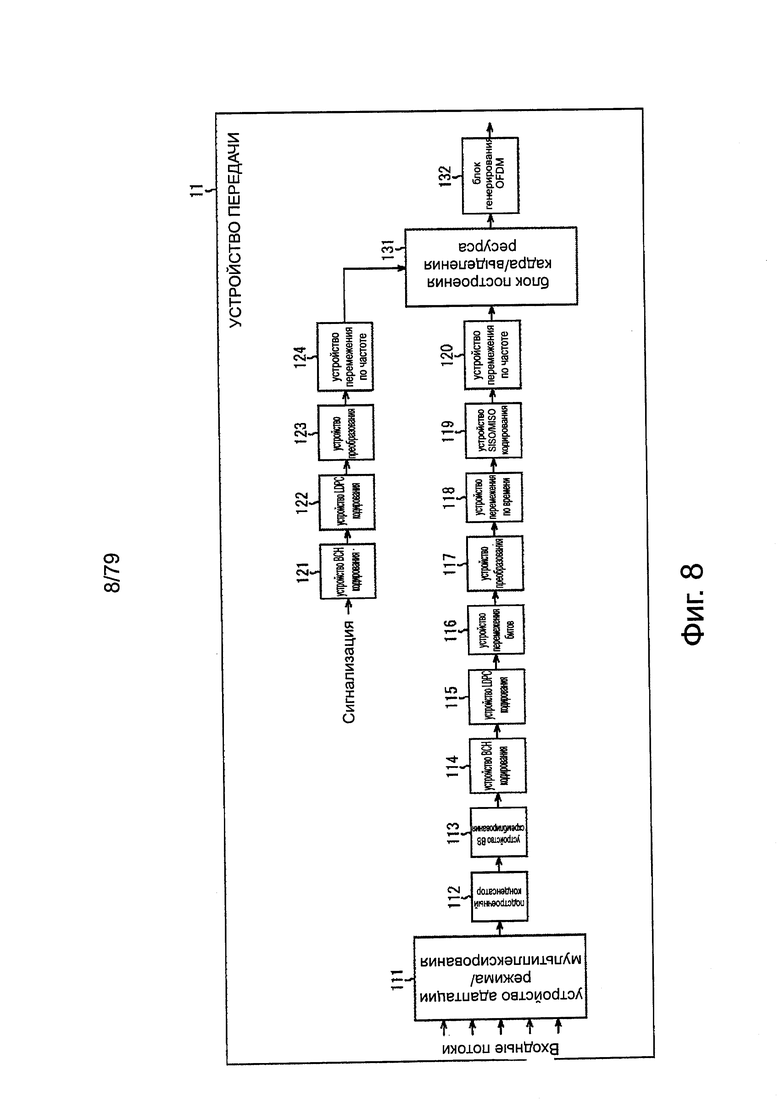

фиг. 8 - вид, иллюстрирующий структурную схему, показывающую пример конфигурации устройства 11 передачи;

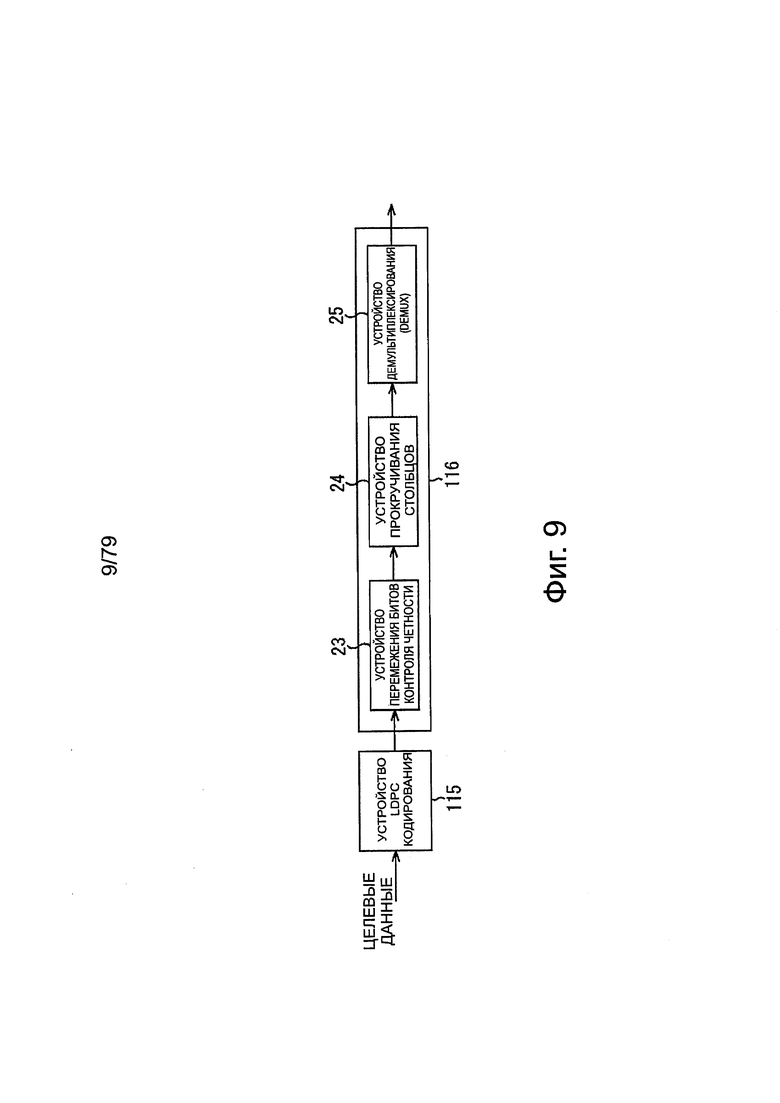

фиг. 9 - вид, иллюстрирующий структурную схему, показывающую пример конфигурации устройства 116 перемежения битов;

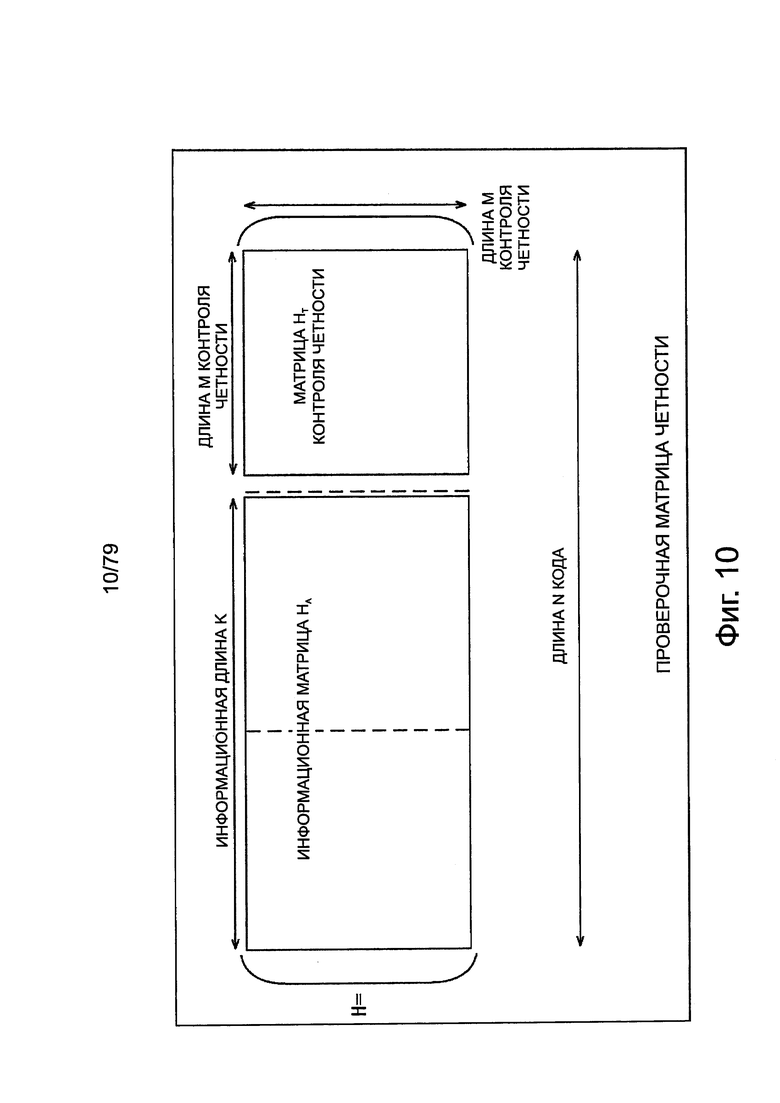

фиг. 10 - вид, показывающий проверочную матрицу;

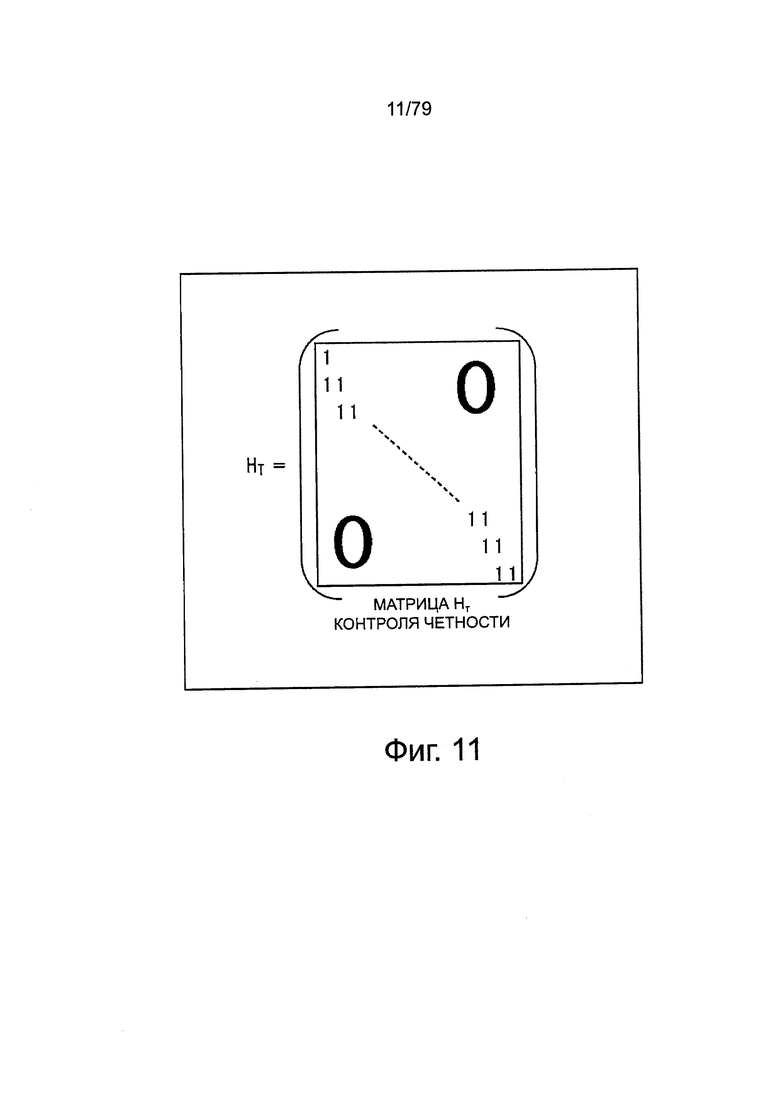

фиг. 11 - вид, показывающий матрицу контроля четности;

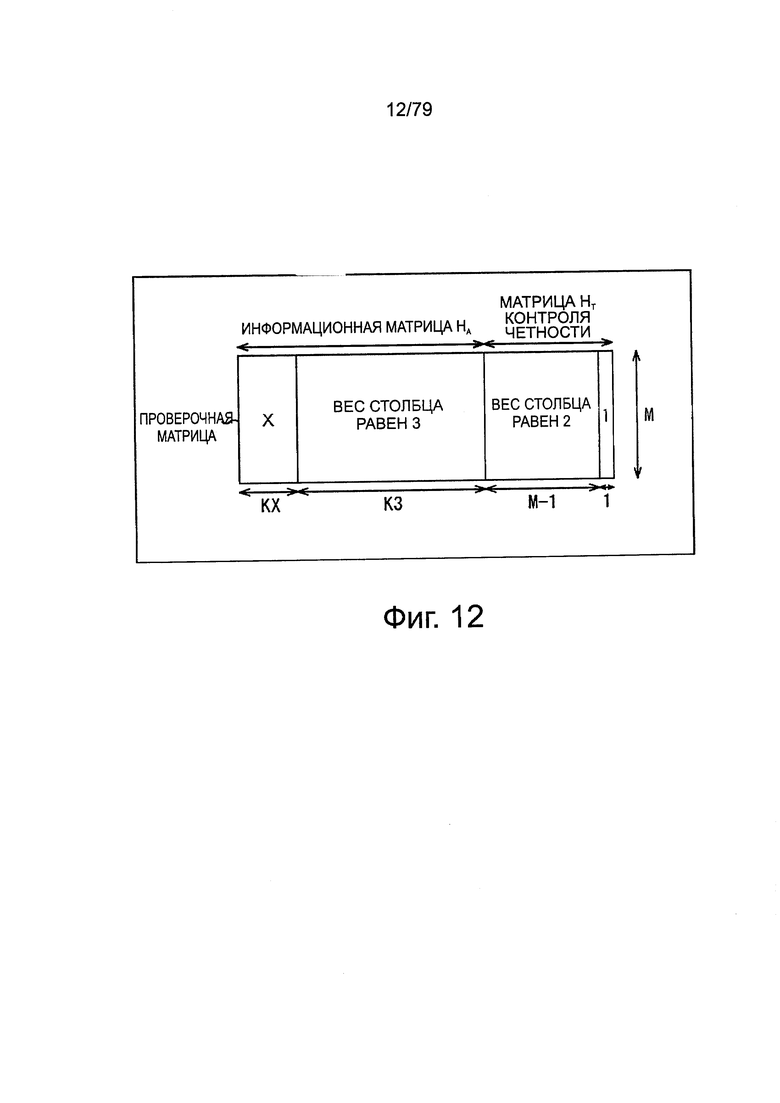

фиг. 12 - вид, показывающий проверочную матрицу LDPC-кода, определенного в стандарте DVB-S.2;

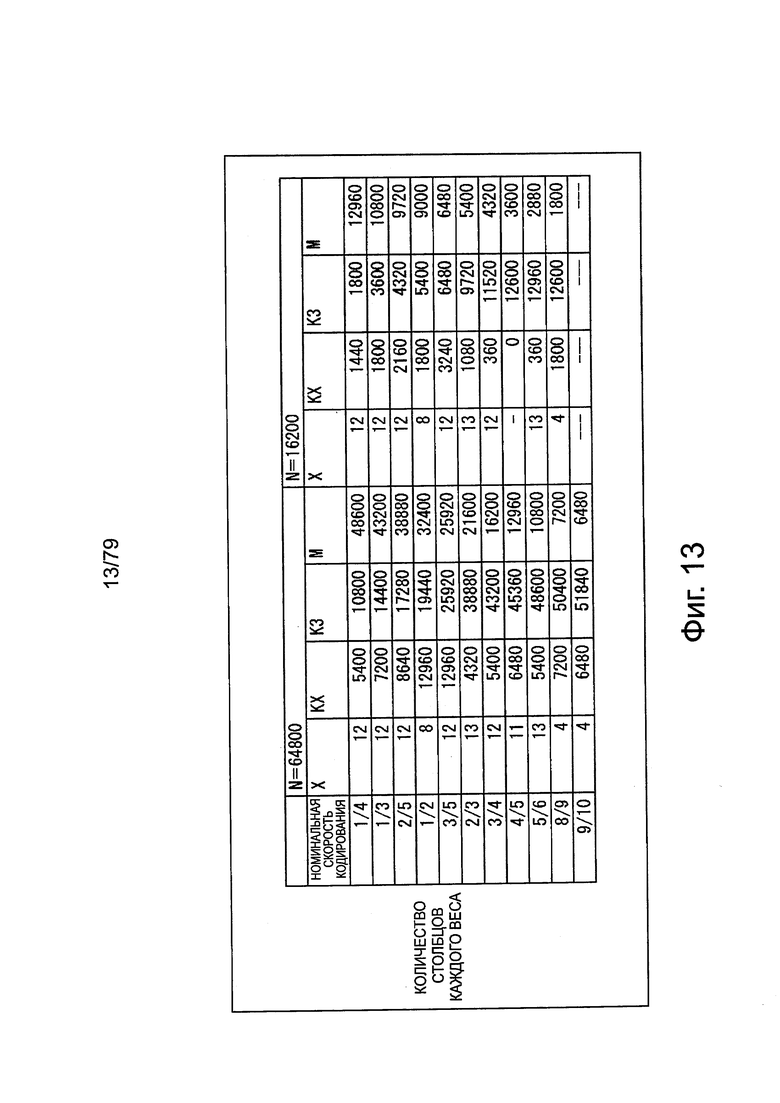

фиг. 13 - вид, показывающий проверочную матрицу LDPC-кода, определенного в стандарте DVB-S.2;

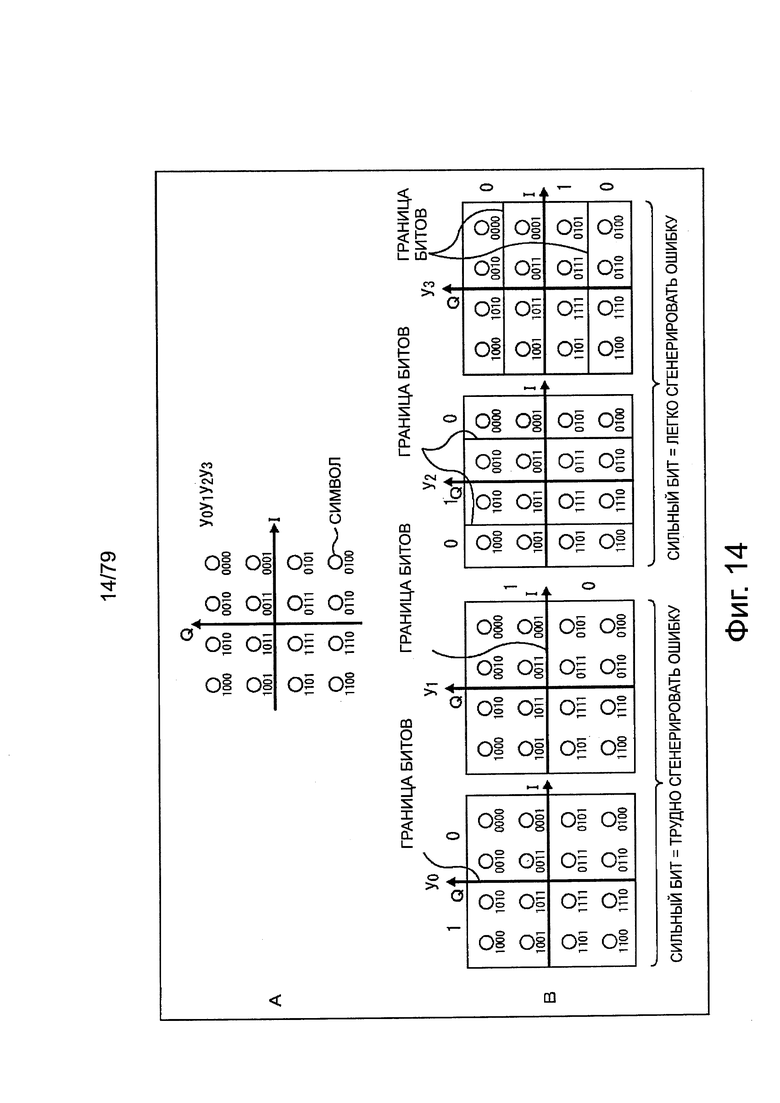

фиг. 14 - вид, показывающий расположение сигнальных точек 16-позиционной QAM;

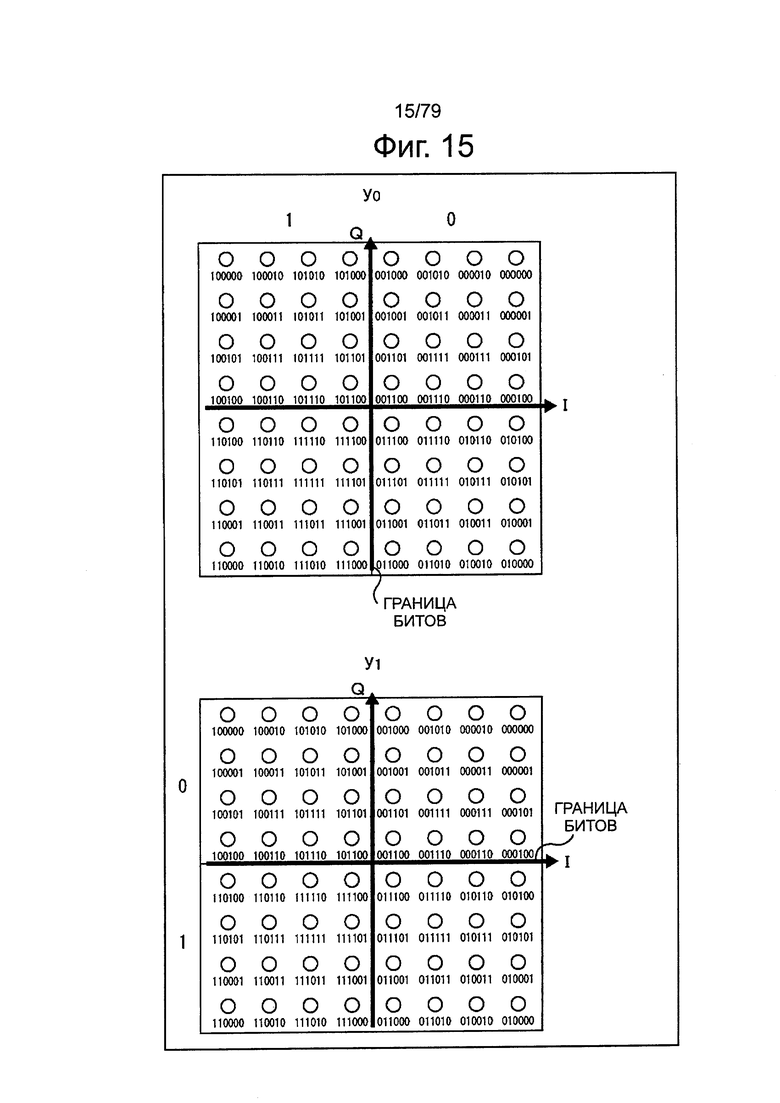

фиг. 15 - вид, показывающий расположение сигнальных точек 64-позиционной QAM;

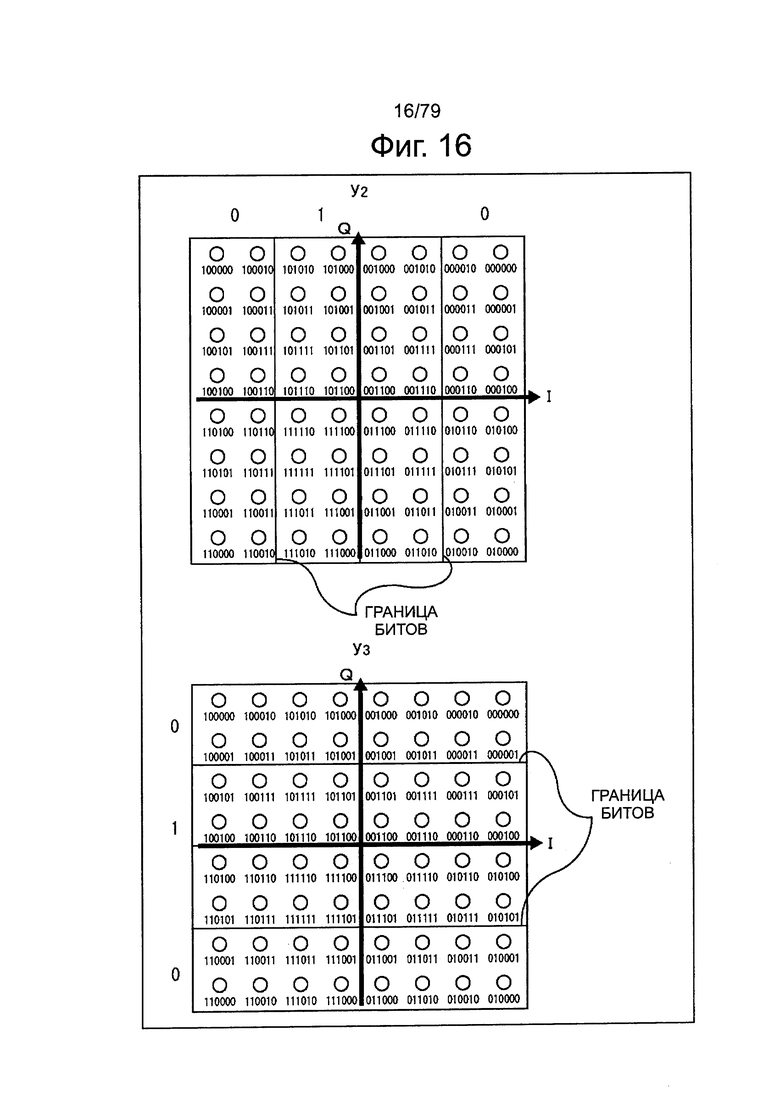

фиг. 16 - вид, показывающий расположение сигнальных точек 64-позиционной QAM;

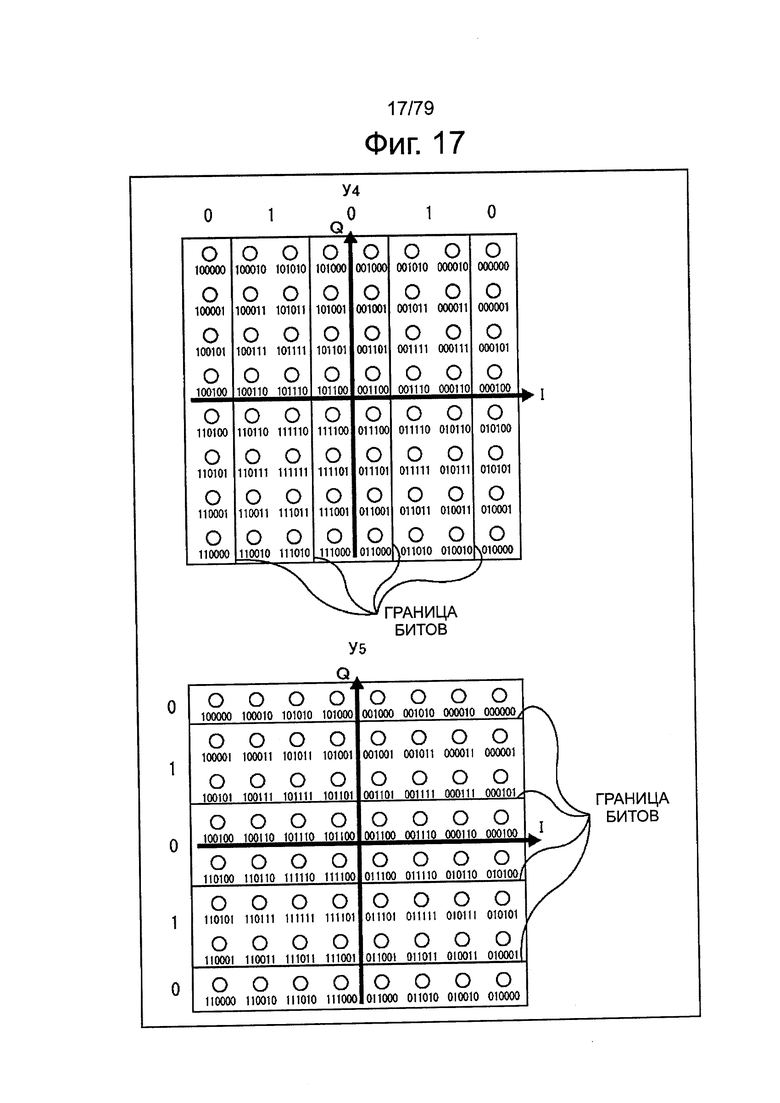

фиг. 17 - вид, показывающий расположение сигнальных точек 64-позиционной QAM;

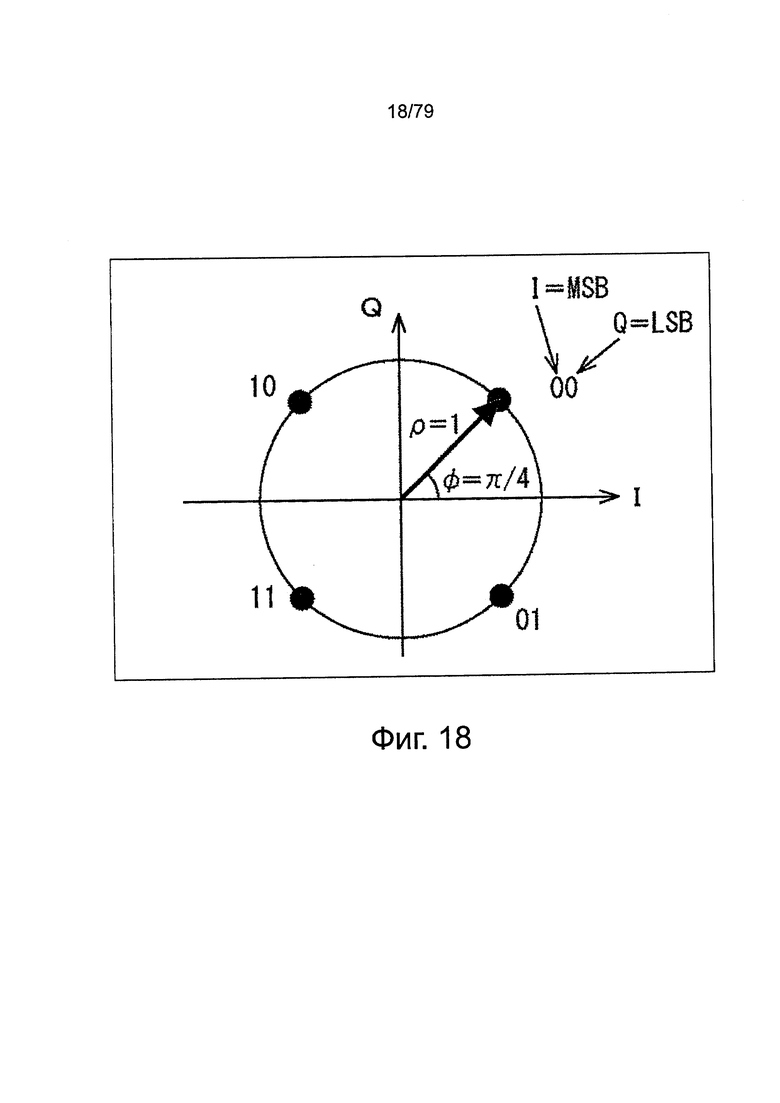

фиг. 18 - вид, показывающий расположение сигнальных точек, определенное в стандарте DVB-S.2;

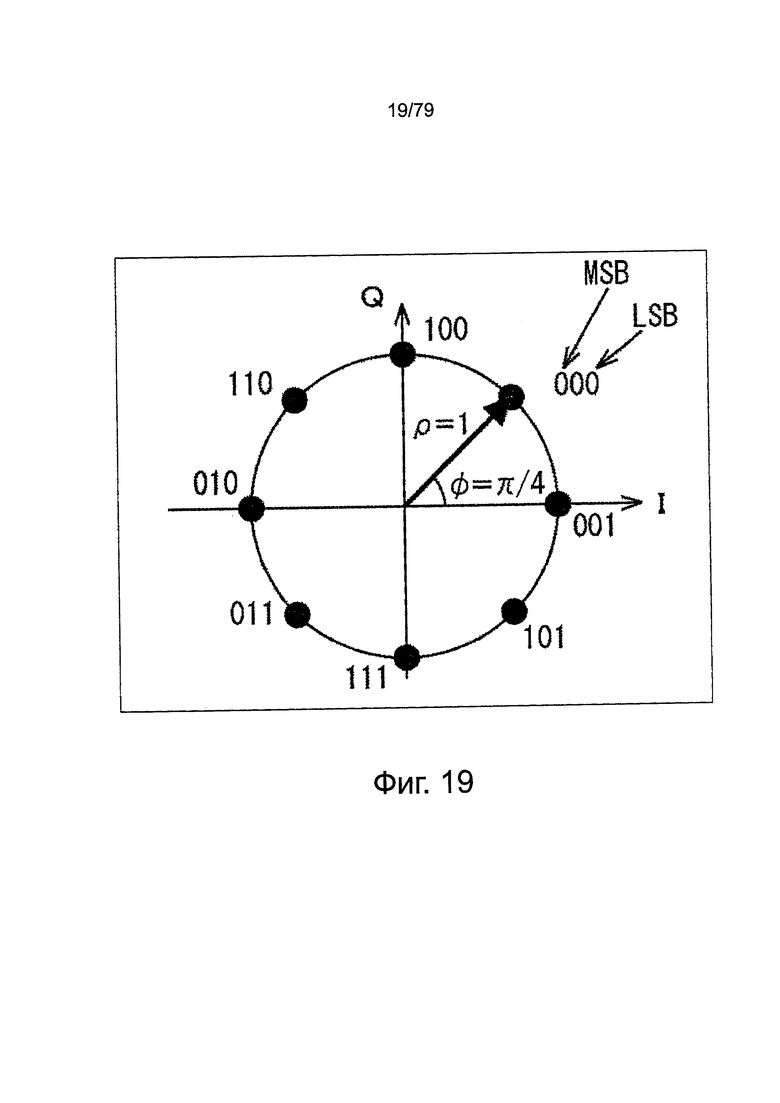

фиг. 19 - вид, показывающий расположение сигнальных точек, определенное в стандарте DVB-S.2;

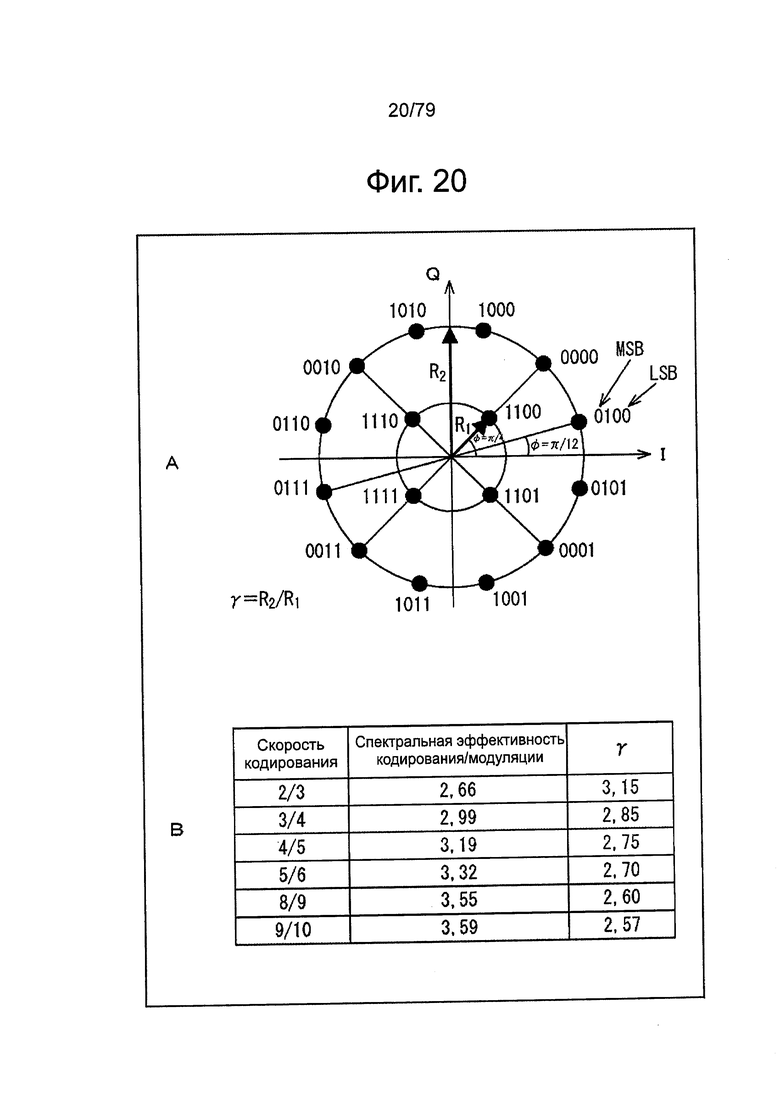

фиг. 20 - вид, показывающий расположение сигнальных точек, определенное в стандарте DVB-S.2;

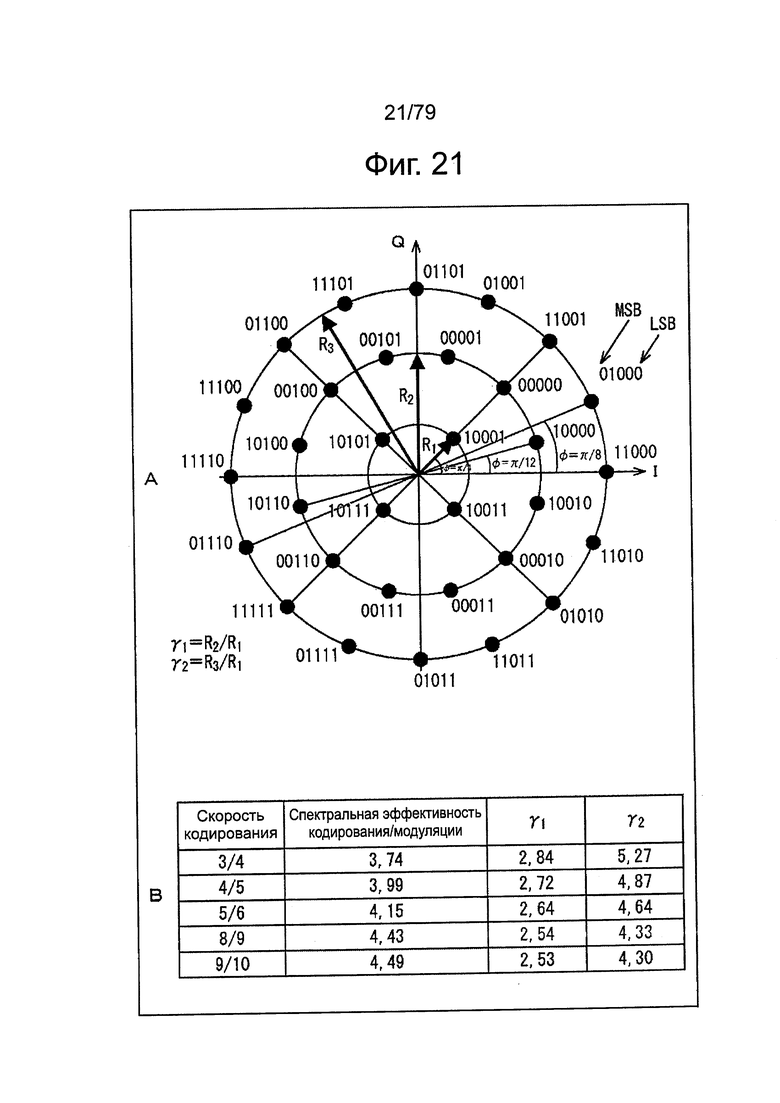

фиг. 21 - вид, показывающий расположение сигнальных точек, определенное в стандарте DVB-S.2;

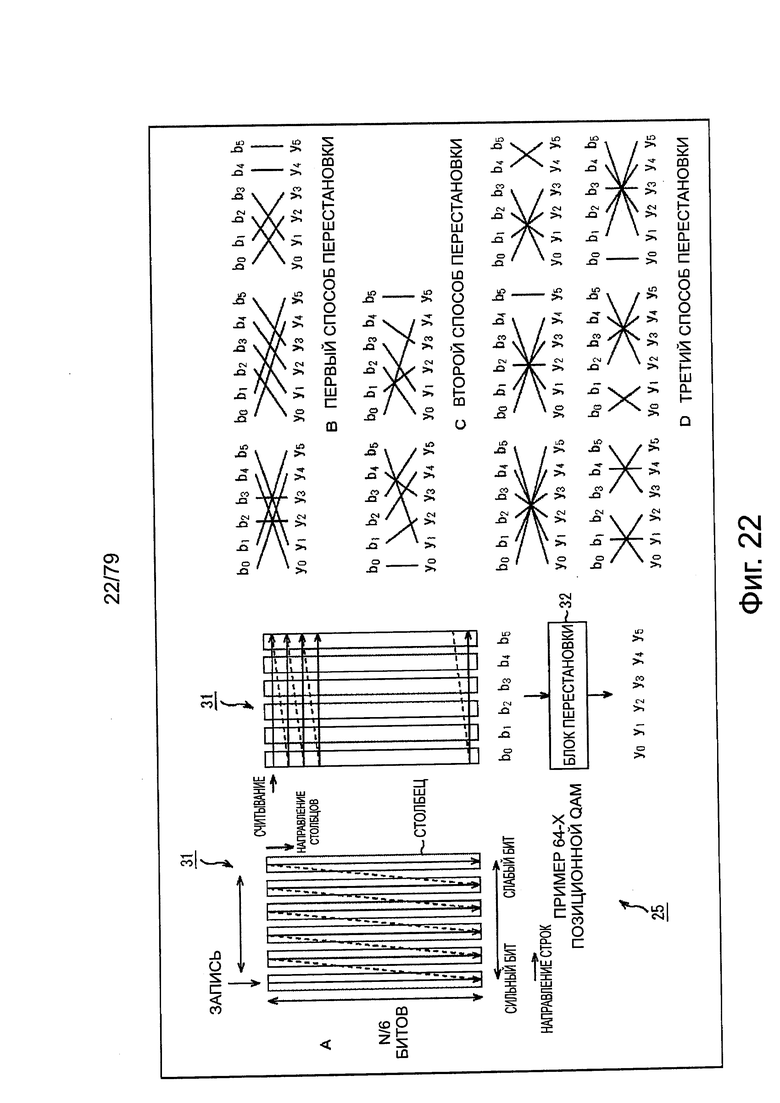

фиг. 22 - вид, показывающий обработку, осуществляемую в устройстве 25 демультиплексирования;

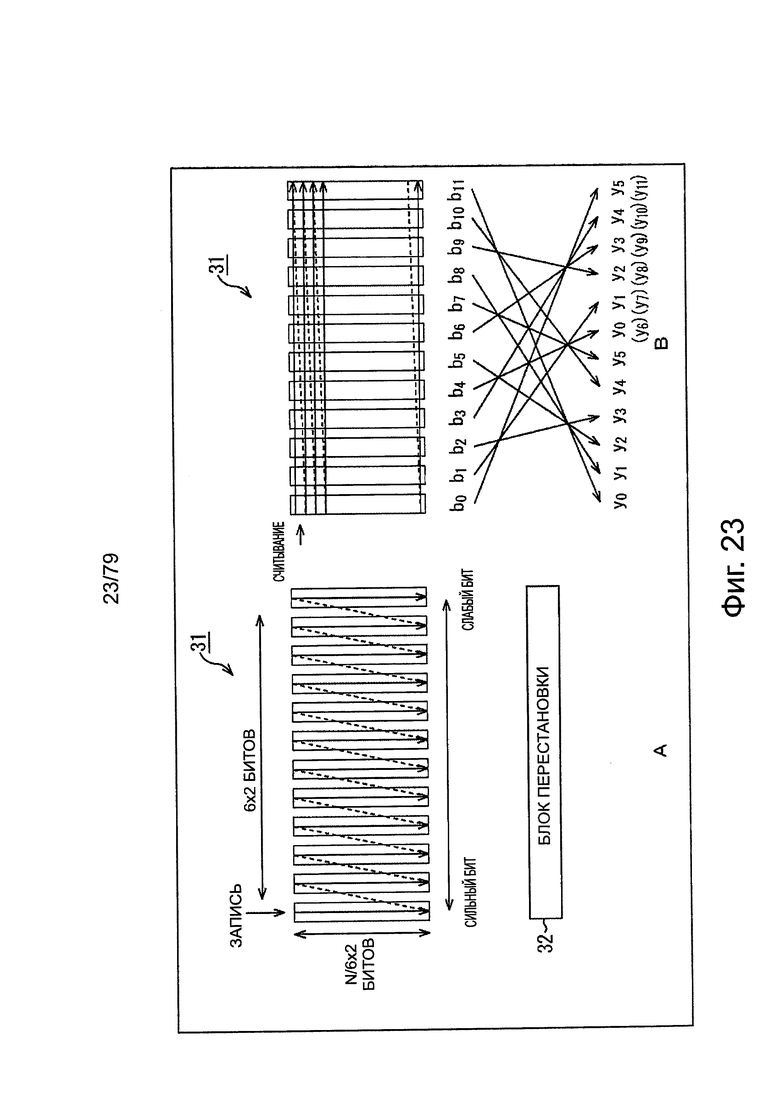

фиг. 23 - вид, показывающий обработку, осуществляемую в устройстве 25 демультиплексирования;

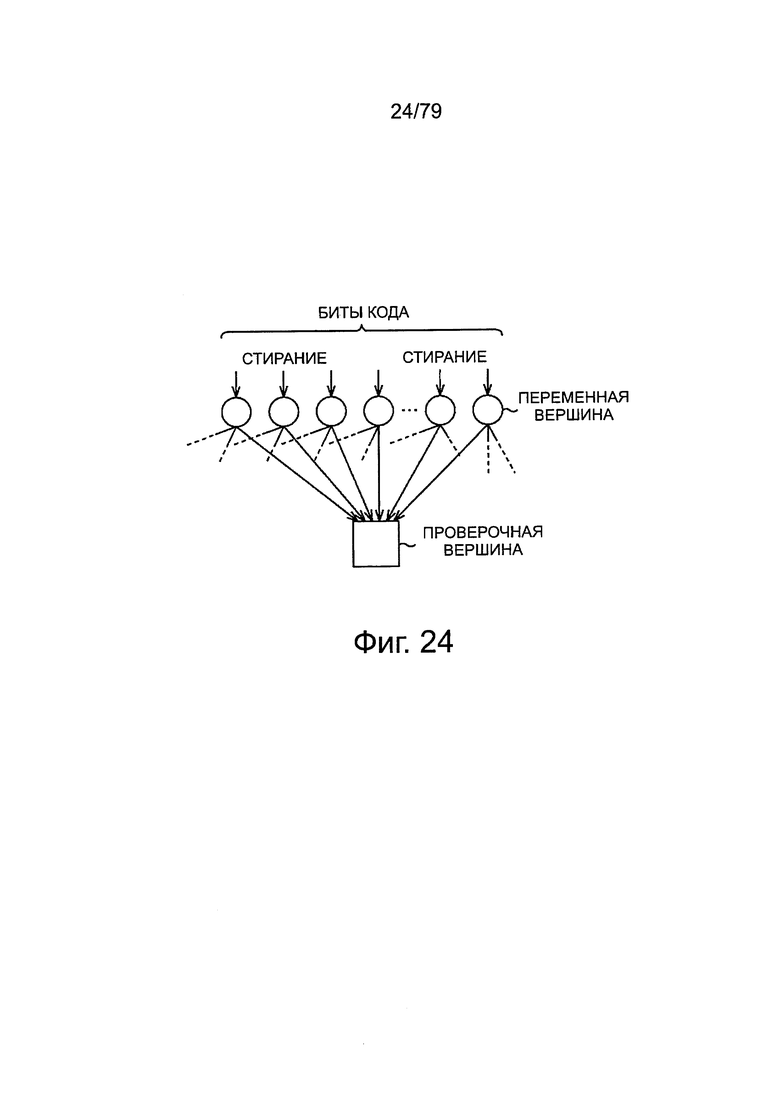

фиг. 24 - вид, показывающий граф Таннера для декодирования LDPC-кода;

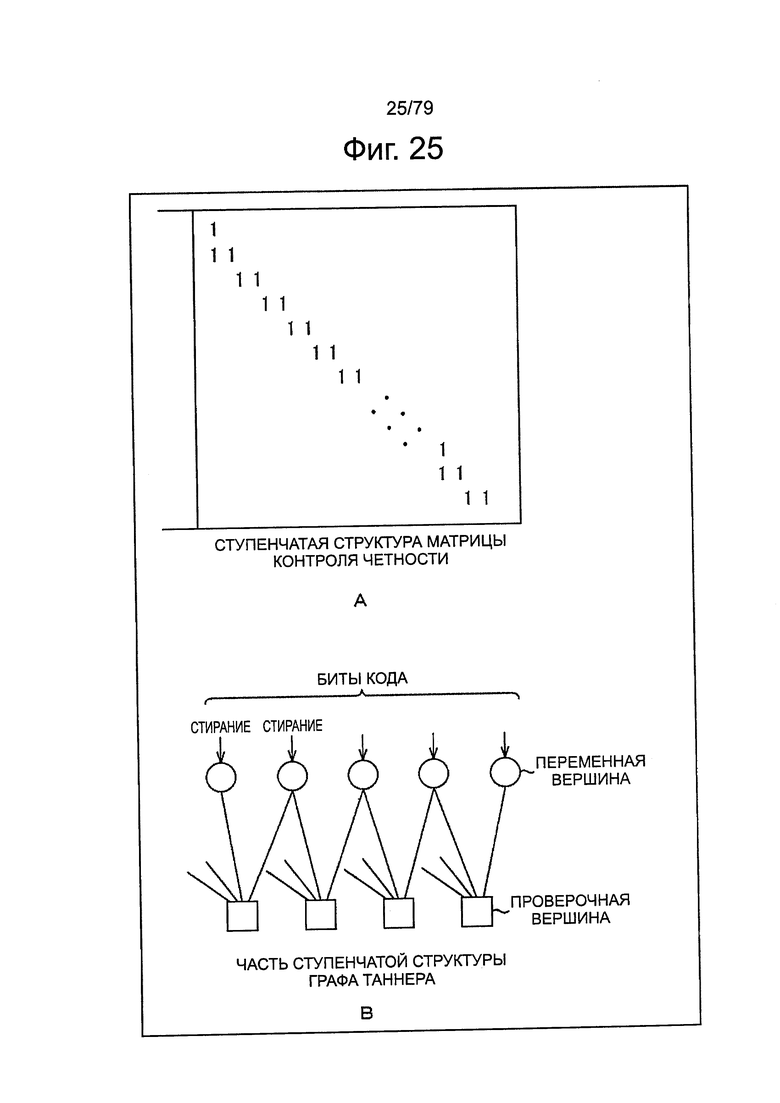

фиг. 25 - вид, показывающий матрицу HT контроля четности, имеющую ступенчатую структуру, и граф Таннера, соответствующий матрице HT контроля четности;

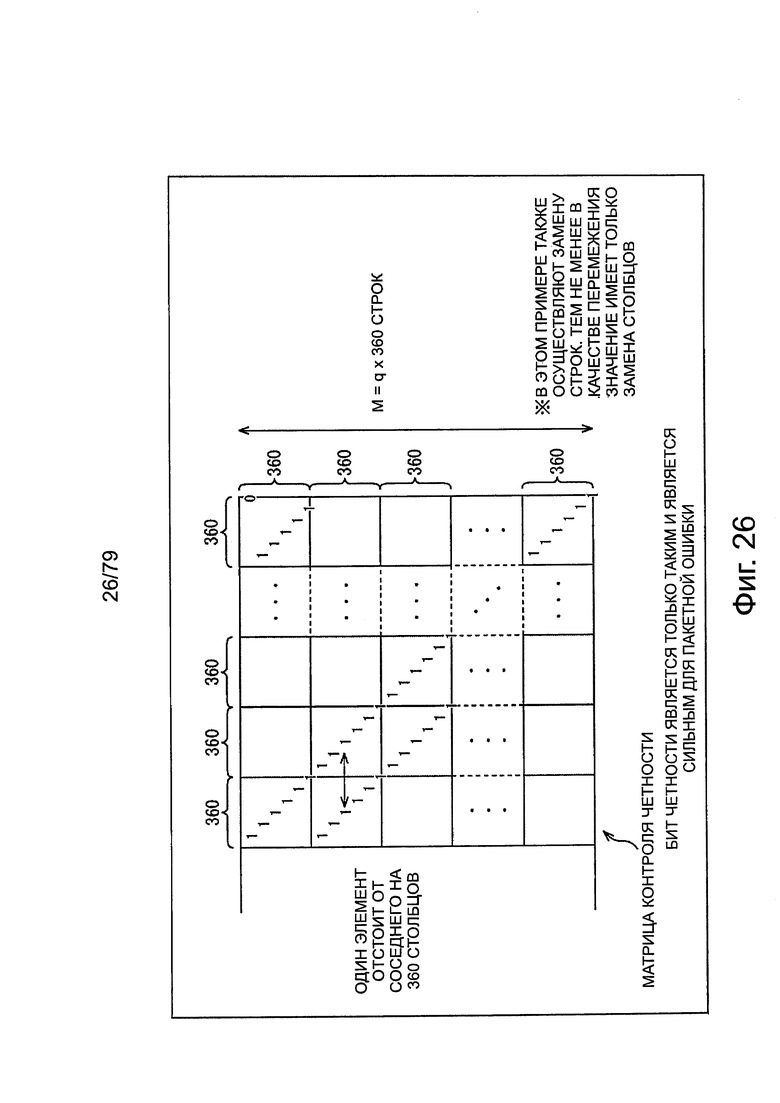

фиг. 26 - вид, показывающий матрицу HT контроля четности проверочной матрицы H, которая соответствует LDPC-коду после перемежения битов контроля четности;

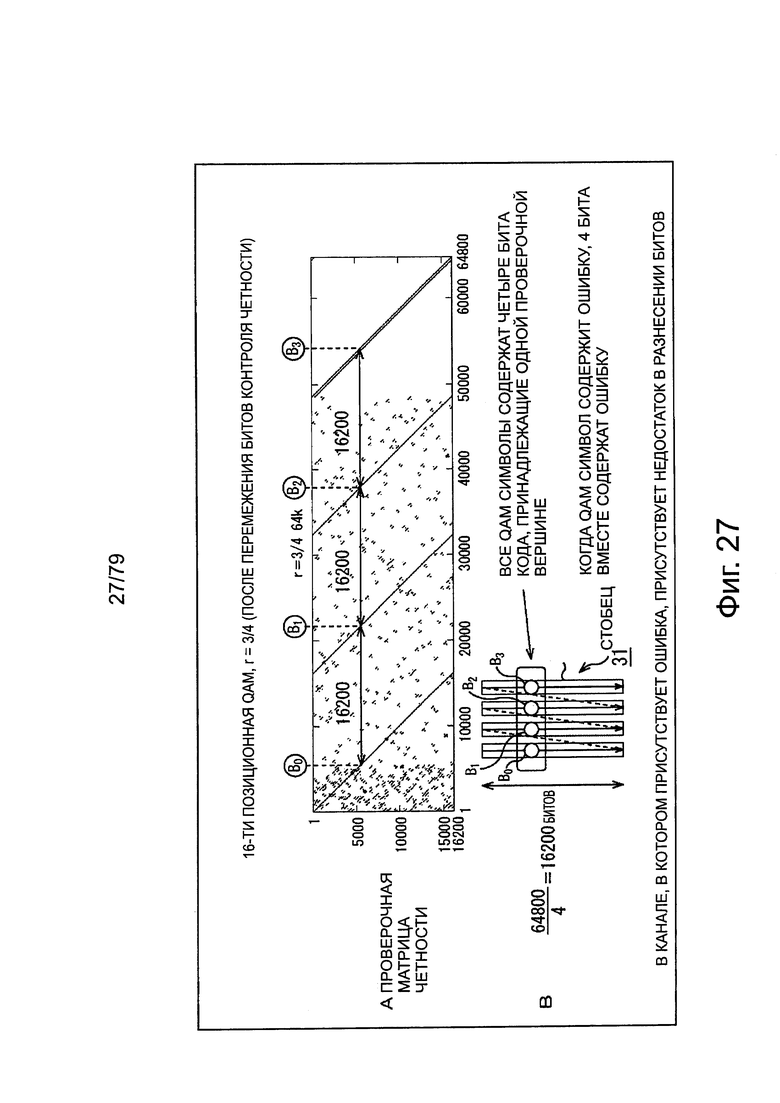

фиг. 27 - вид, показывающий преобразованную проверочную матрицу;

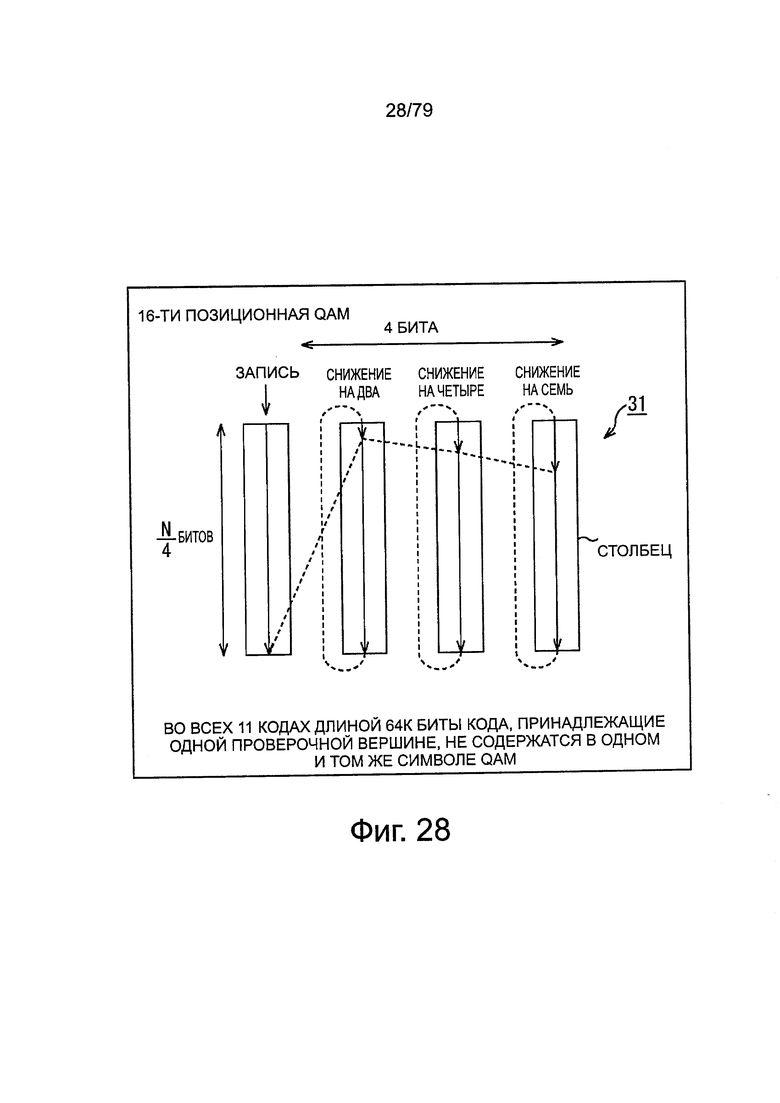

фиг. 28 - вид, показывающий обработку, осуществляемую в устройстве 24 прокручивания

столбцов;

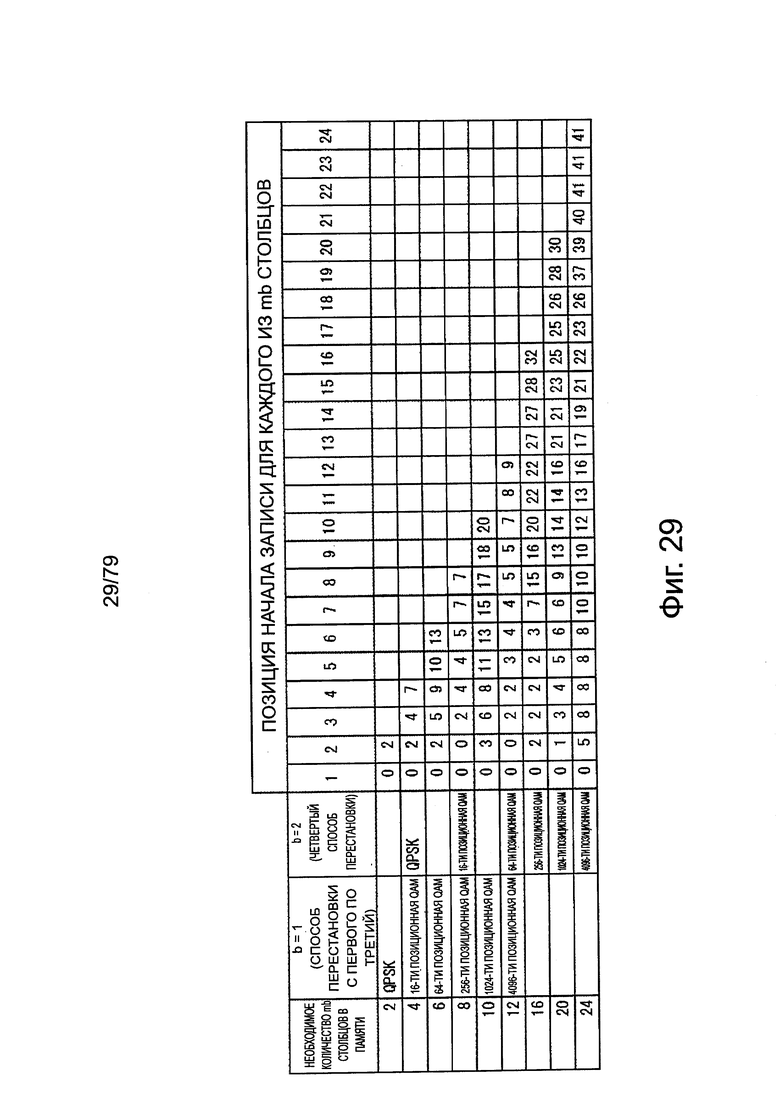

фиг. 29 - вид, показывающий количество столбцов в памяти 31, необходимое для прокручивания столбцов и адрес позиции начала записи;

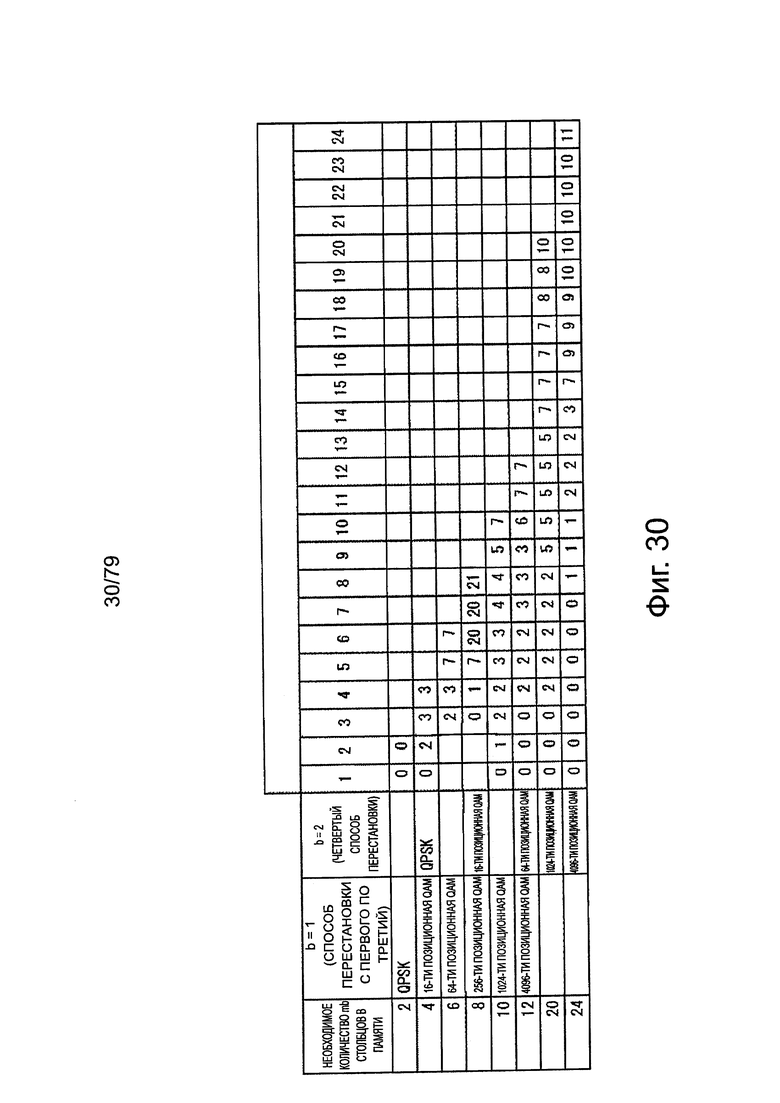

фиг. 30 - вид, показывающий количество столбцов в памяти 31, необходимое для прокручивания столбцов и адрес позиции начала записи;

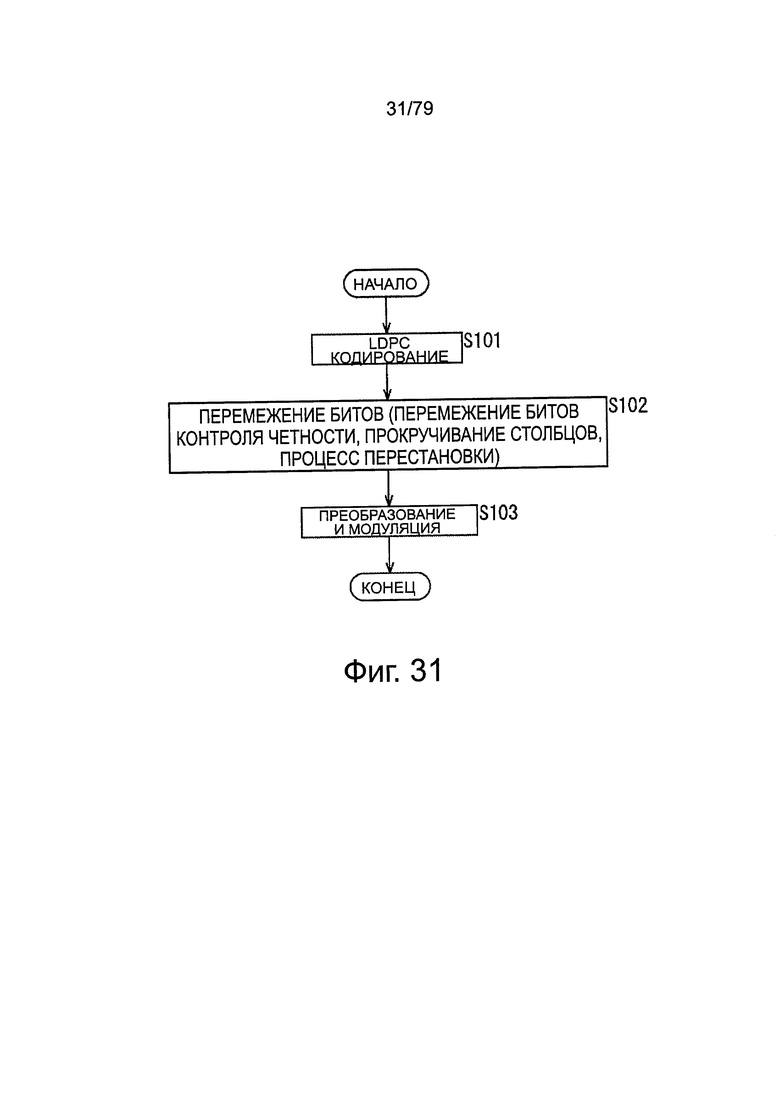

фиг. 31 - вид, показывающий блок-схему, иллюстрирующую процесс обработки, осуществляемый в устройстве 116 перемежения битов и устройстве 117 преобразования;

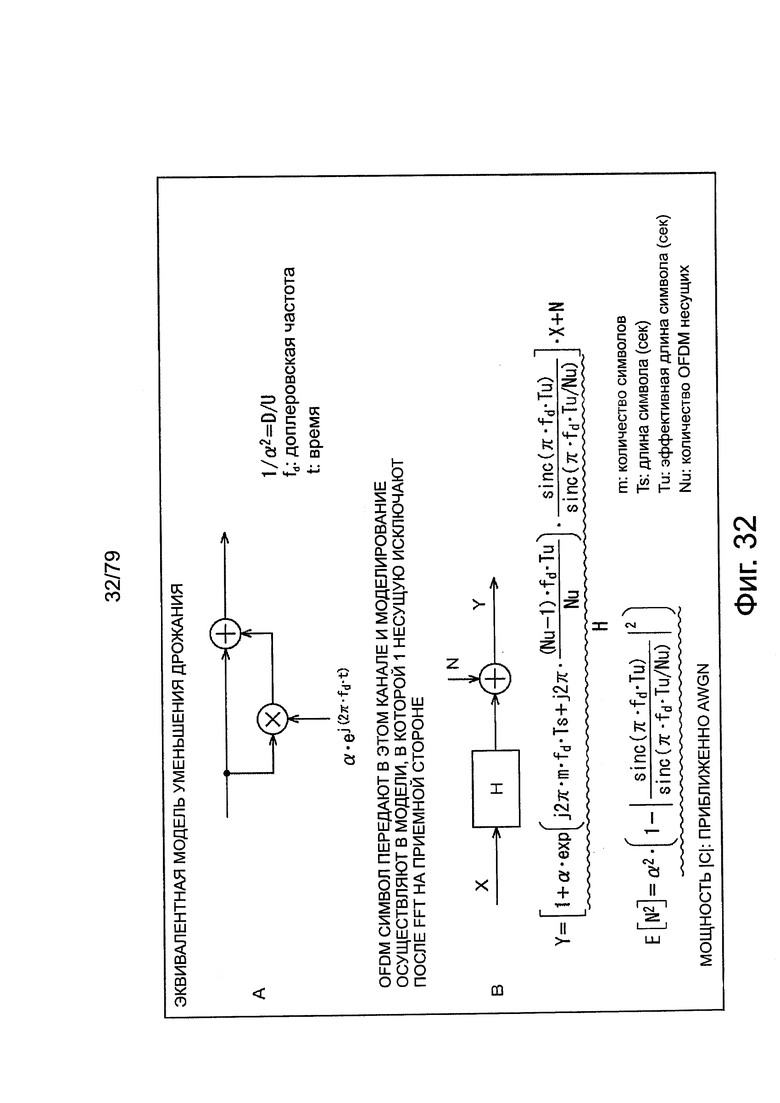

фиг. 32 - вид, показывающий модель канала связи, которая применялась для моделирования;

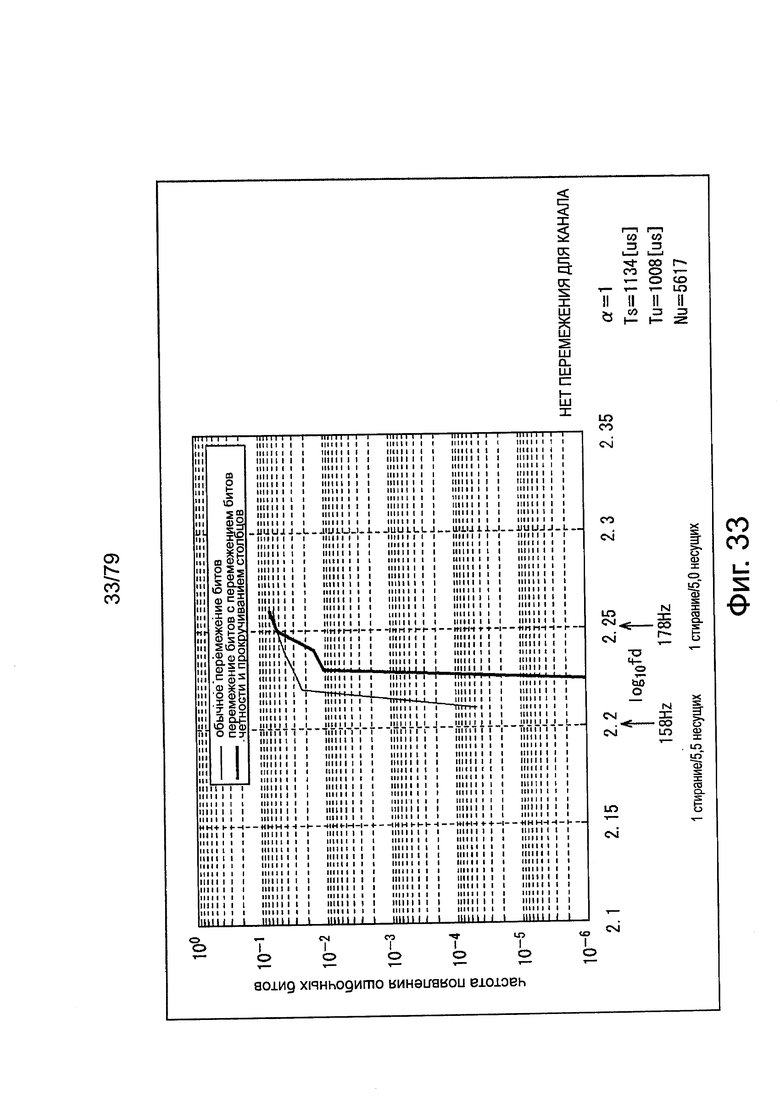

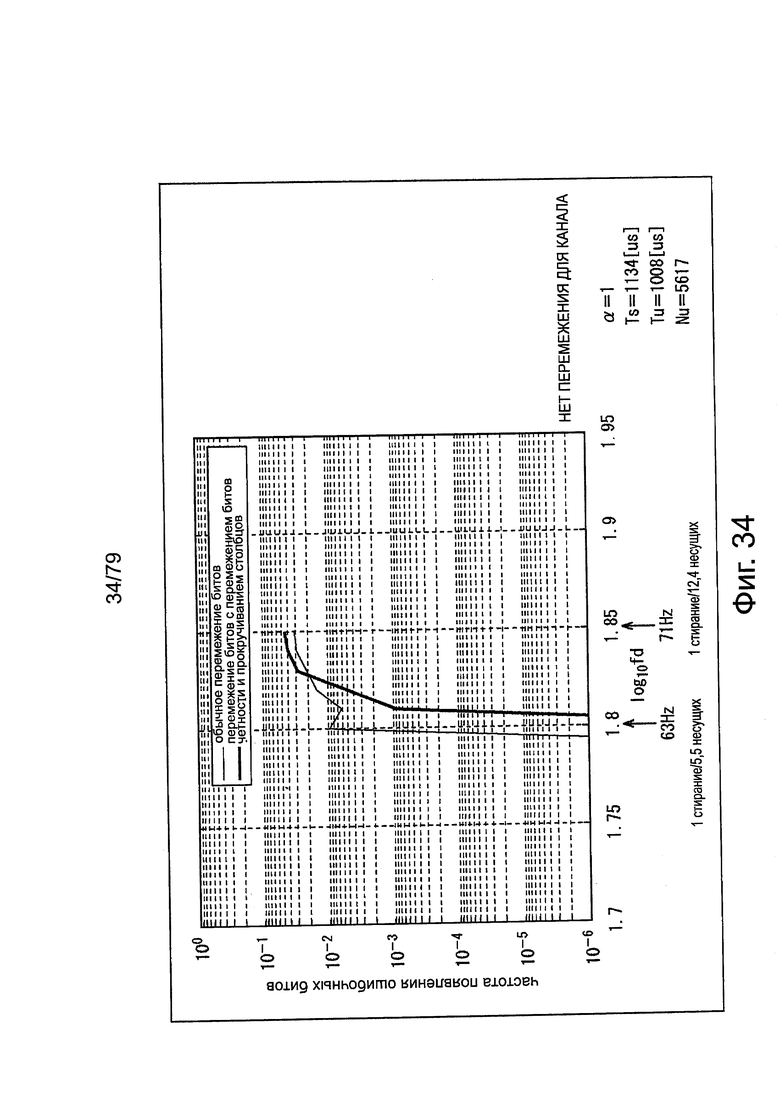

фиг. 33 - вид, показывающий взаимосвязь частоты появления ошибки, которая получена при моделировании, и доплеровской частоты fd дрожания;

фиг. 34 - вид, показывающий взаимосвязь частоты появления ошибки, которая получена при моделировании, и доплеровской частоты fd дрожания;

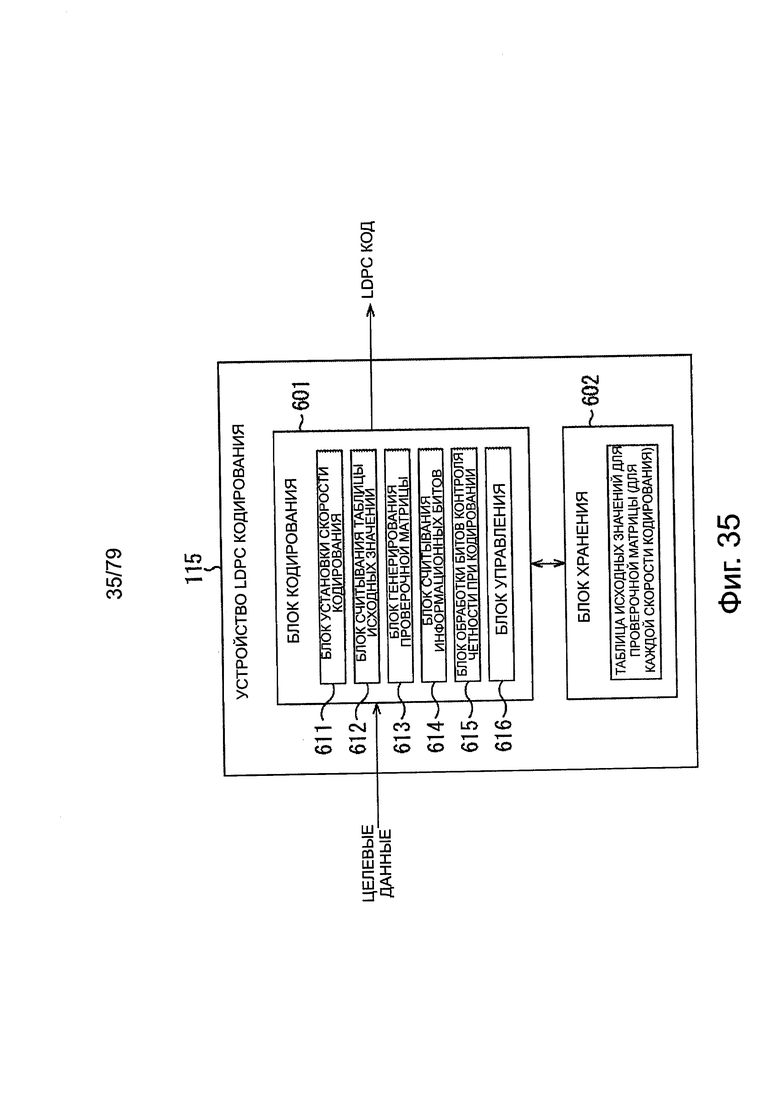

фиг. 35 - вид, иллюстрирующий структурную схему, показывающую пример конфигурации устройства 115 LDPC кодирования;

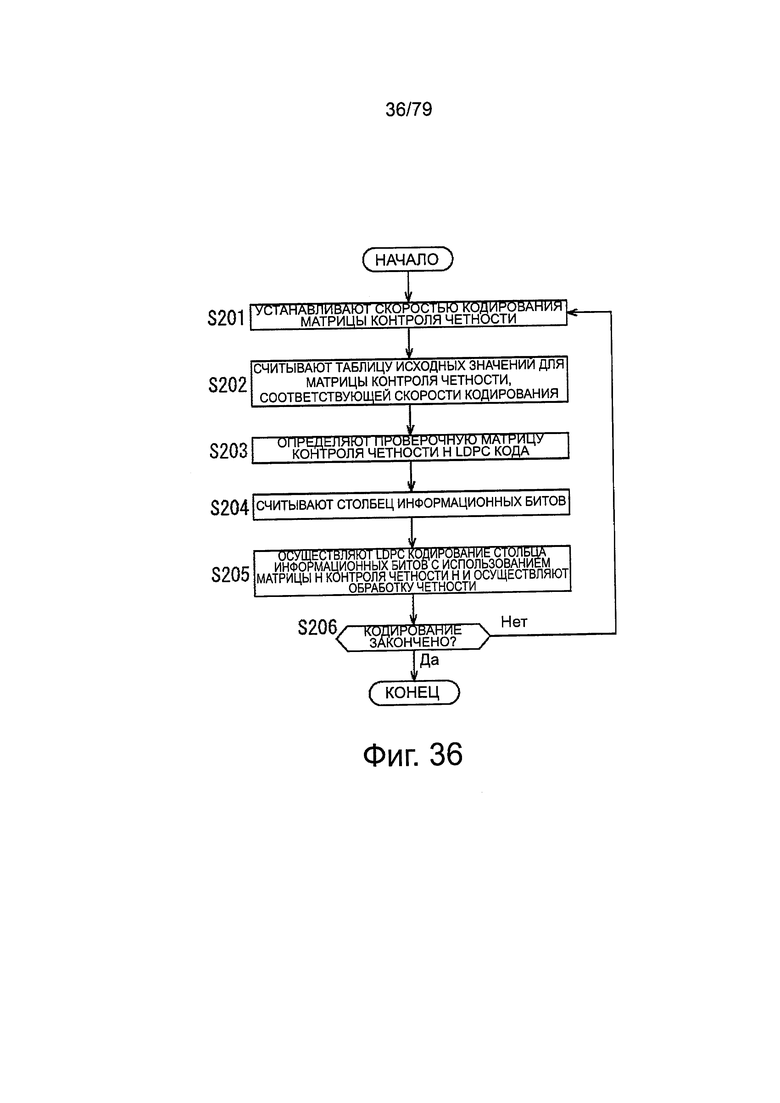

фиг. 36 - вид, иллюстрирующий блок-схему, показывающую процесс обработки, осуществляемый в устройстве 115 LDPC кодирования;

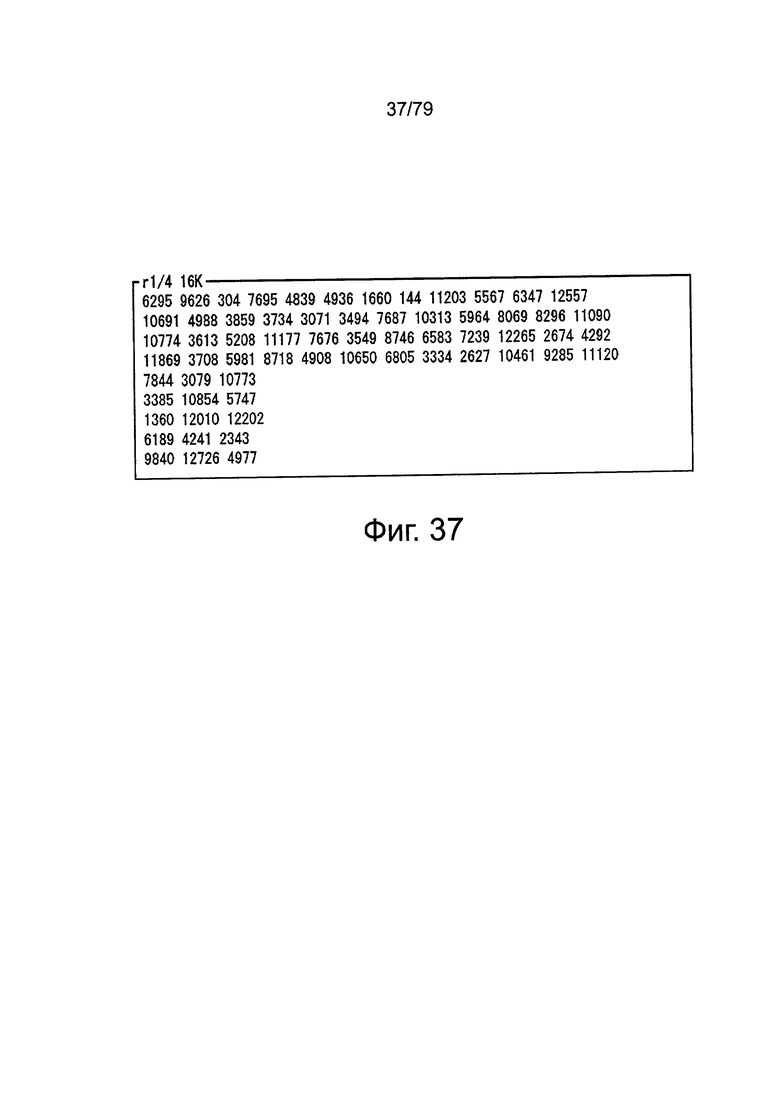

фиг. 37 - вид, показывающий пример таблицы исходных значений для проверочной матрицы кода со скоростью кодирования, равной 1/4, и длиной кода, равной 16200;

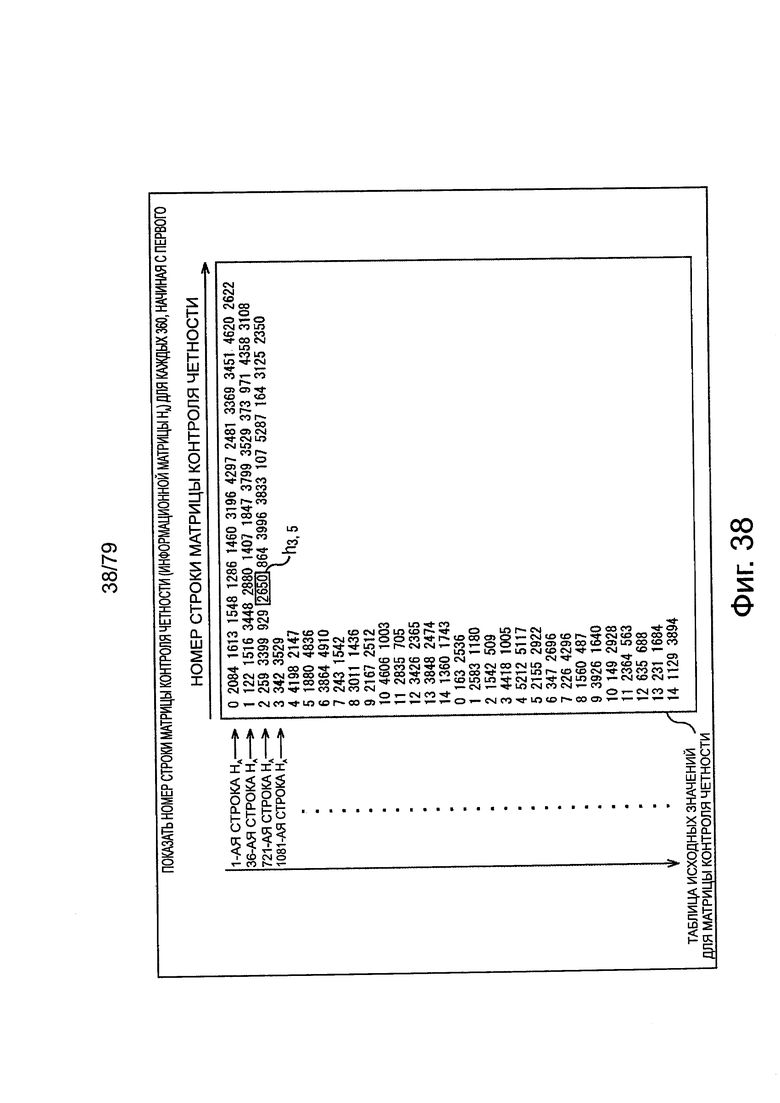

фиг. 38 - вид, иллюстрирующий способ вычисления проверочной матрицы H по таблице исходных значений для проверочной матрицы;

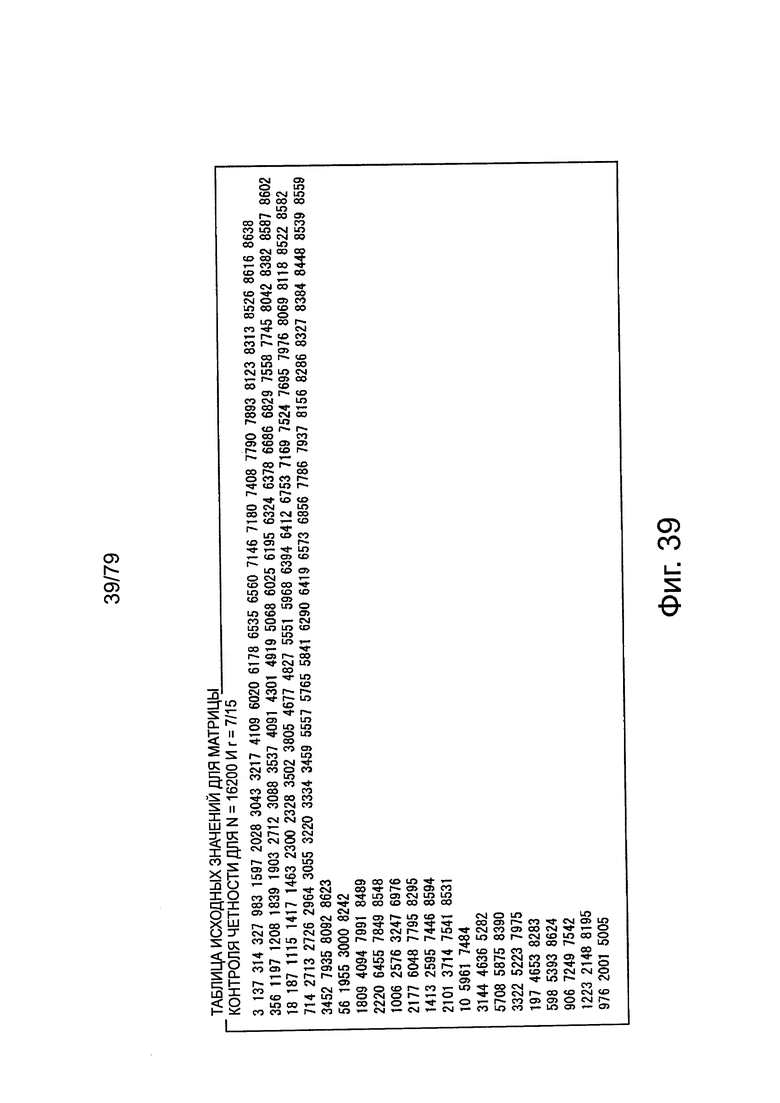

фиг. 39 - вид, показывающий пример таблицы исходных значений для проверочной матрицы 16К кода для Sx с r=7/15;

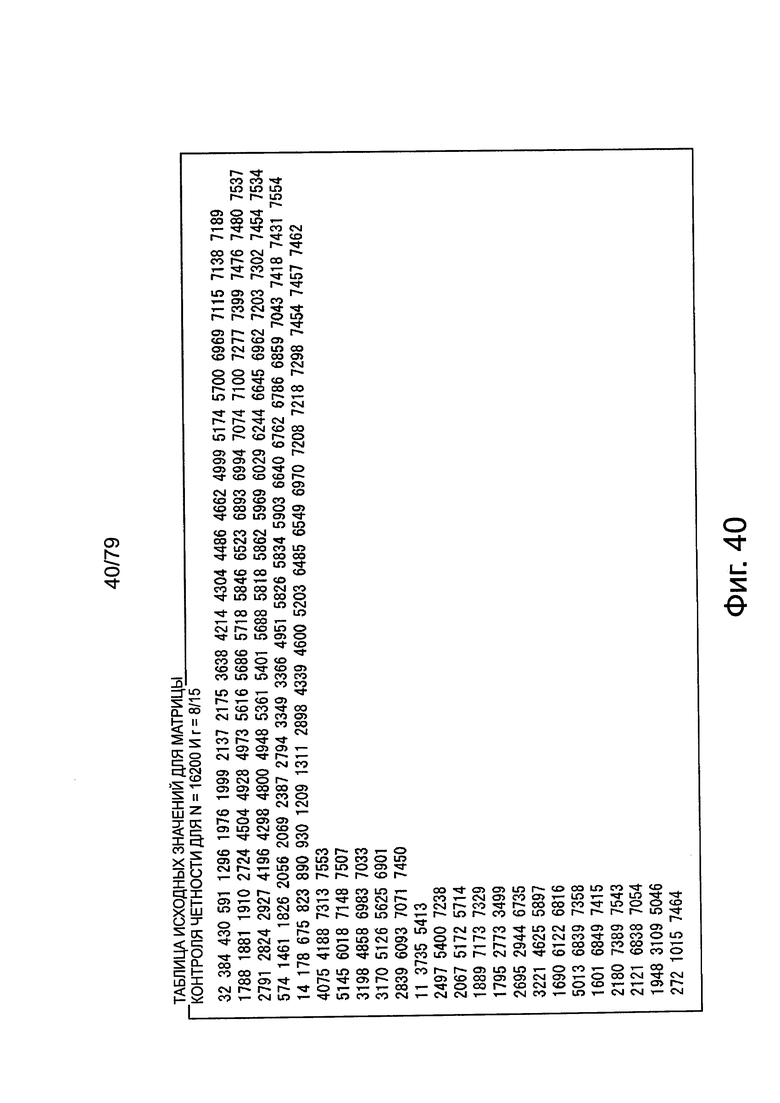

фиг. 40 - вид, показывающий пример таблицы исходных значений для проверочной матрицы 16К кода для Sx с r=8/15;

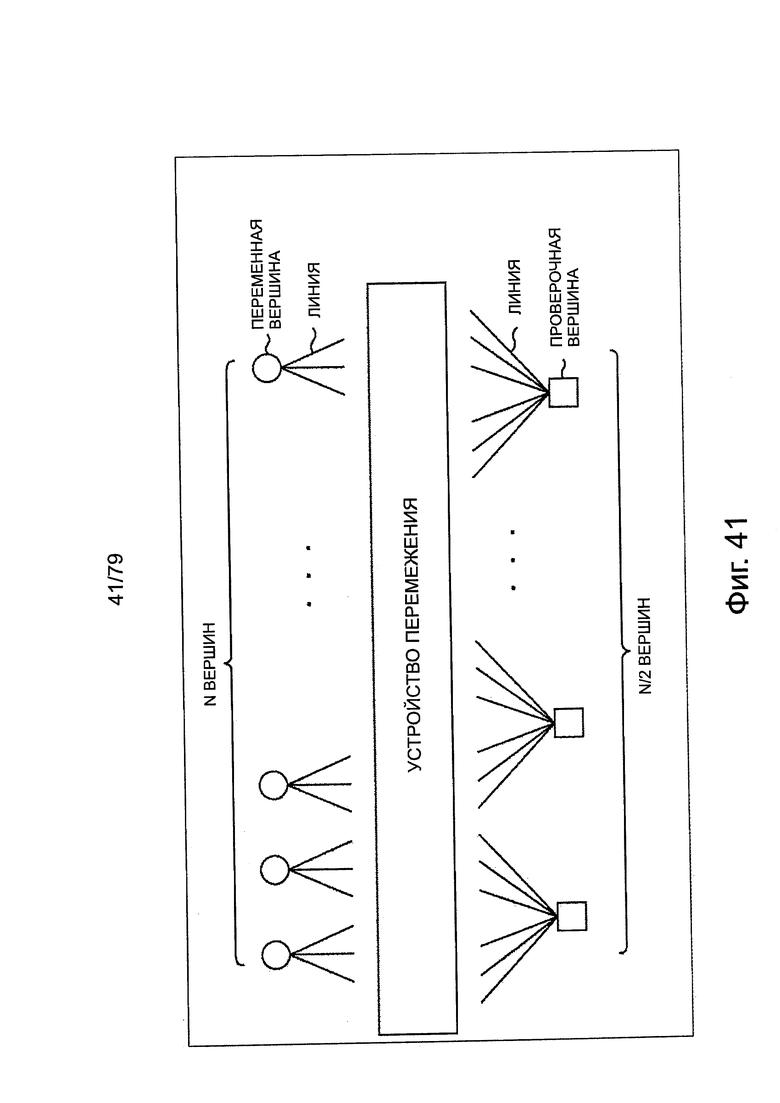

фиг. 41 - вид, показывающий пример графа Таннера такого сочетания с последовательностью степеней, в которой вес столбца равен 3, а вес строки равен 6;

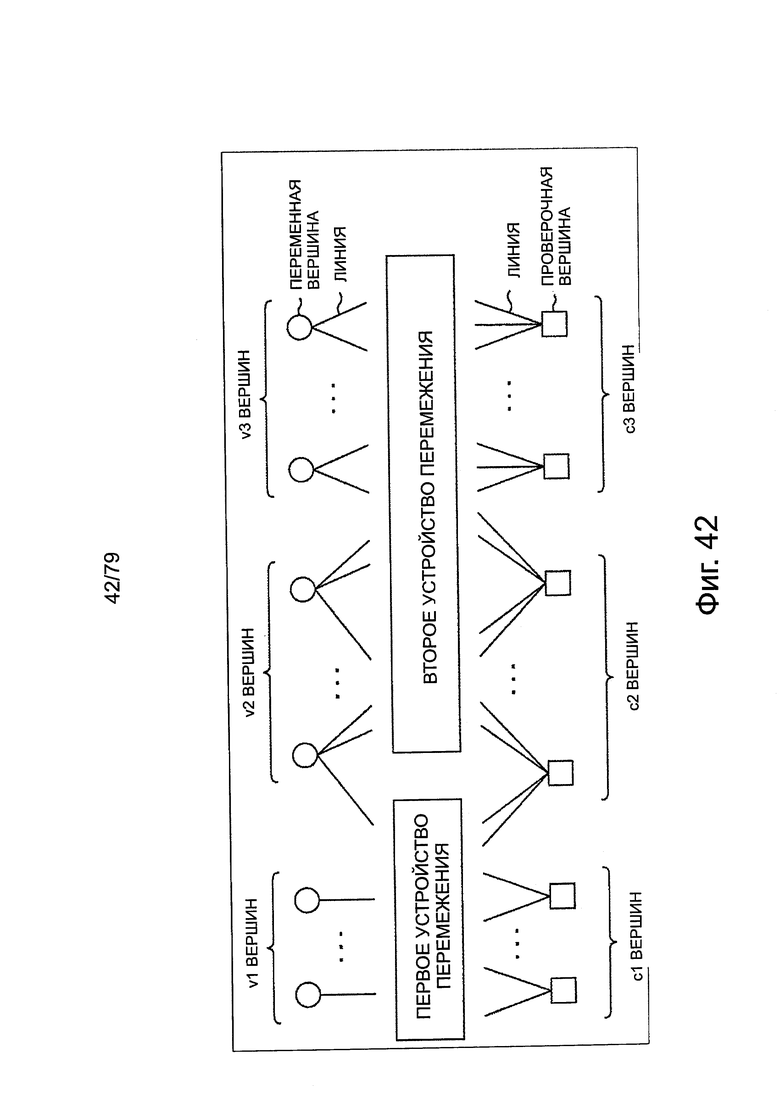

фиг. 42 - вид, показывающий пример графа Таннера сочетания многореберного типа;

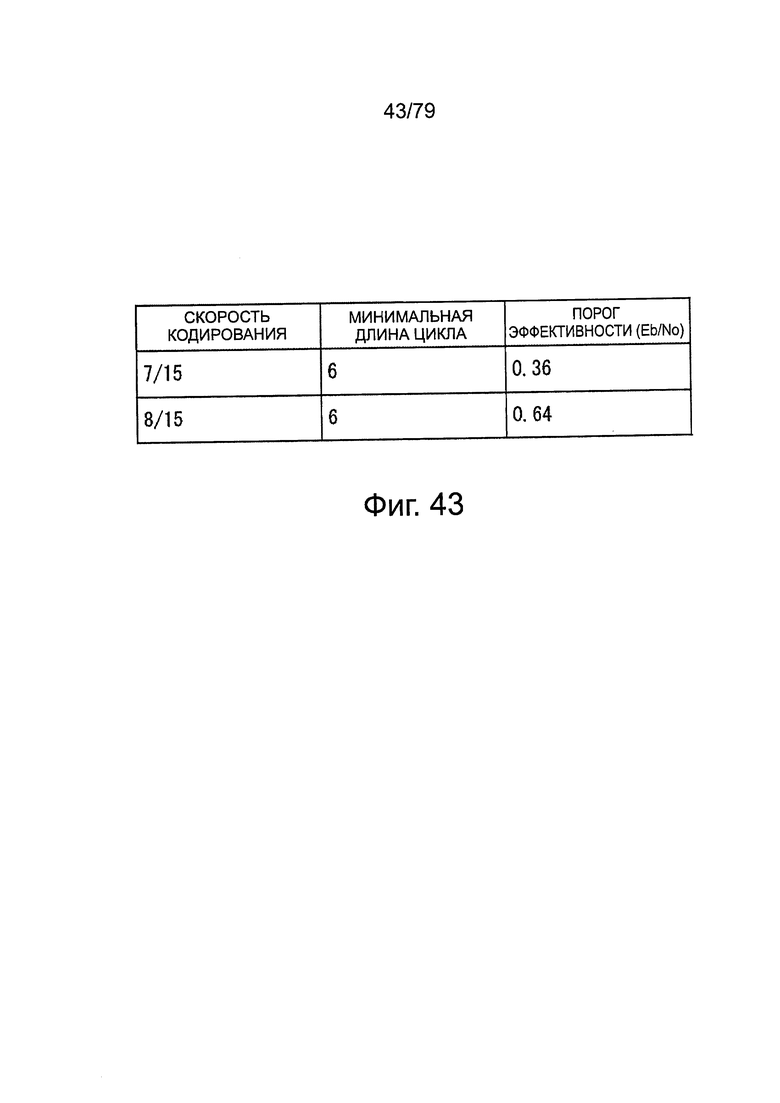

фиг. 43 - вид, показывающий минимальную длину цикла и порог эффективности проверочной матрицы 16К кода для Sx;

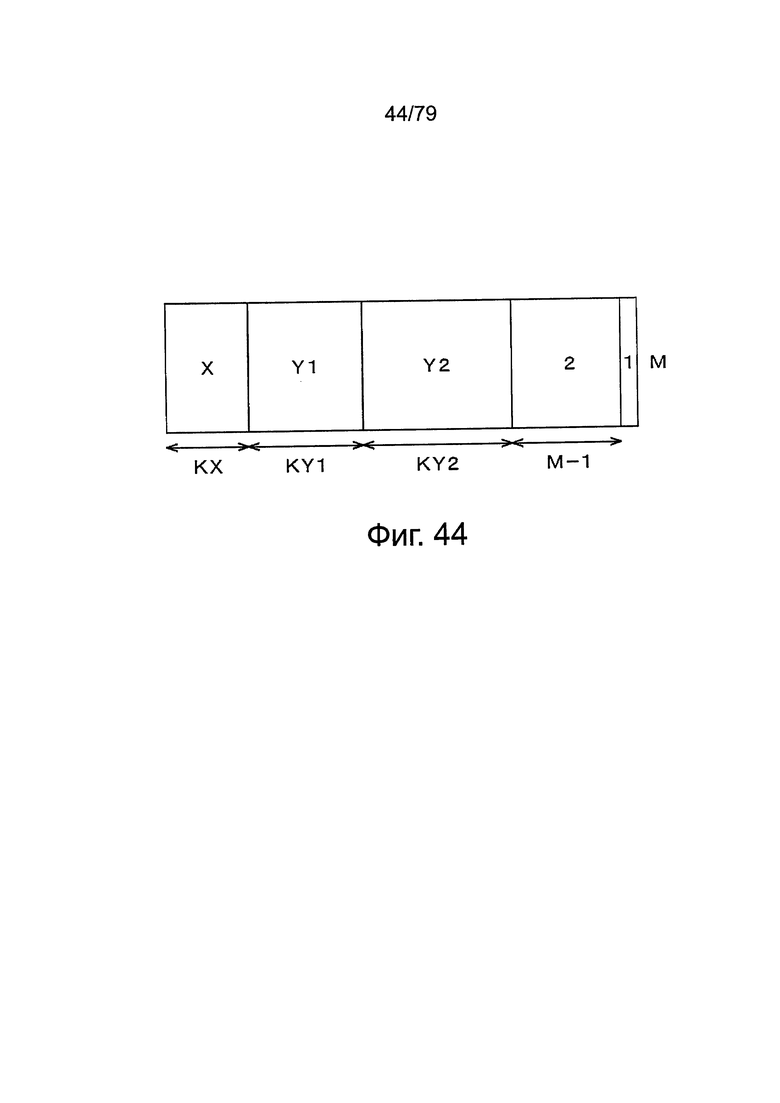

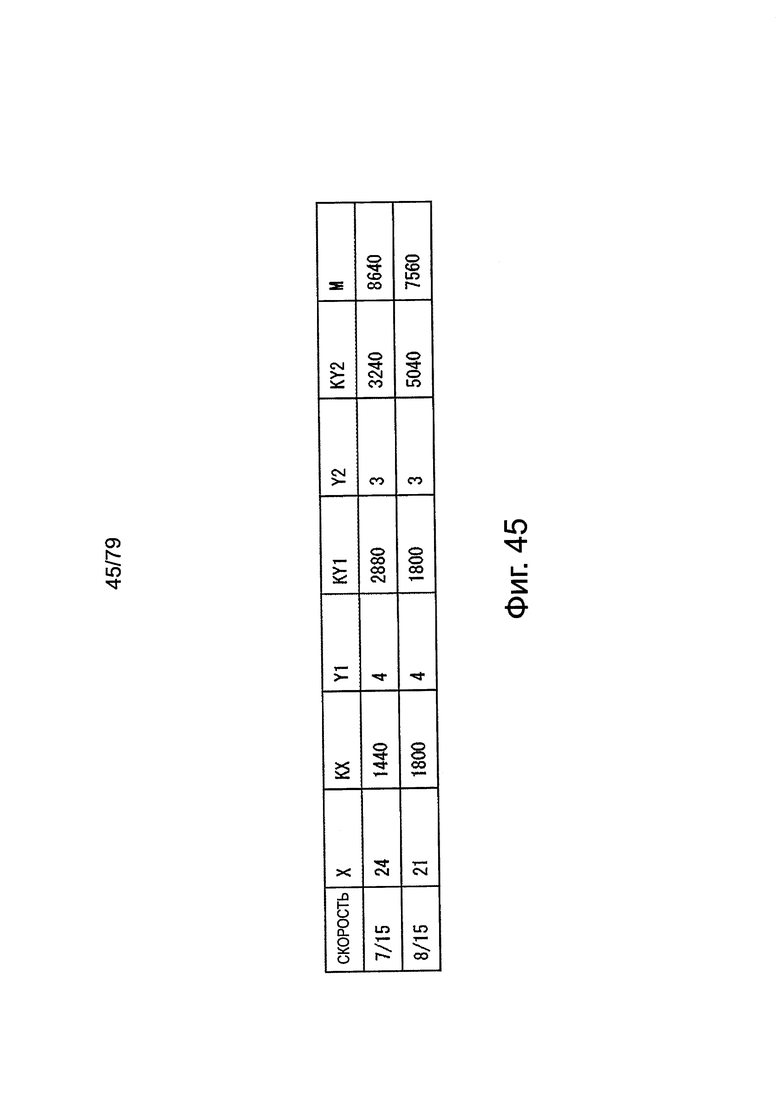

фиг. 44 - вид, показывающий проверочную матрицу 16К кода для Sx;

фиг. 45 - вид, показывающий проверочную матрицу 16К кода для Sx;

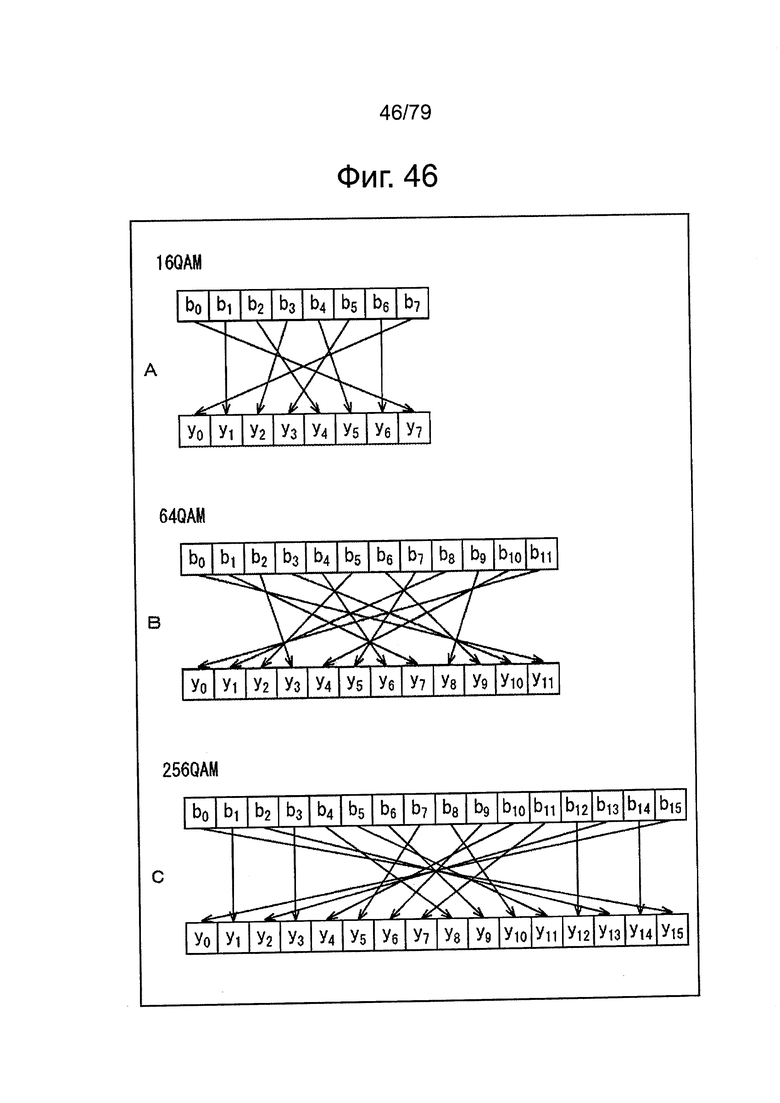

фиг. 46 - вид, показывающий процесс перестановки в соответствии с настоящим способом;

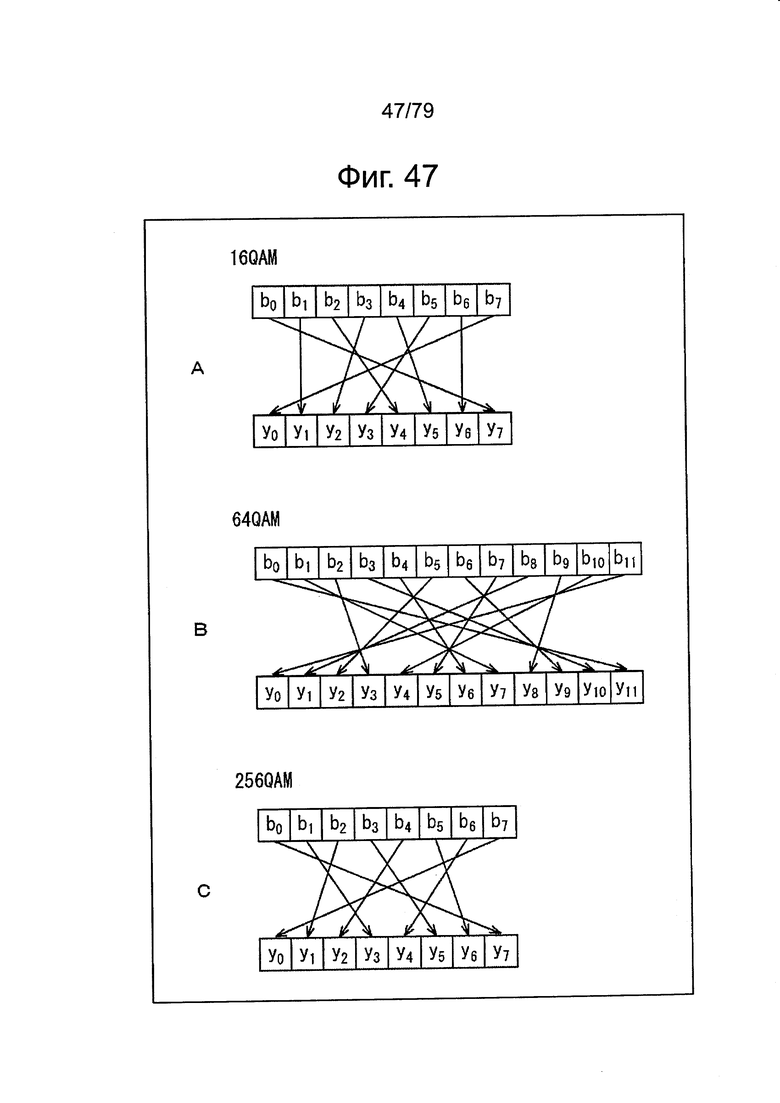

фиг. 47 - вид, показывающий процесс перестановки в соответствии с настоящим способом;

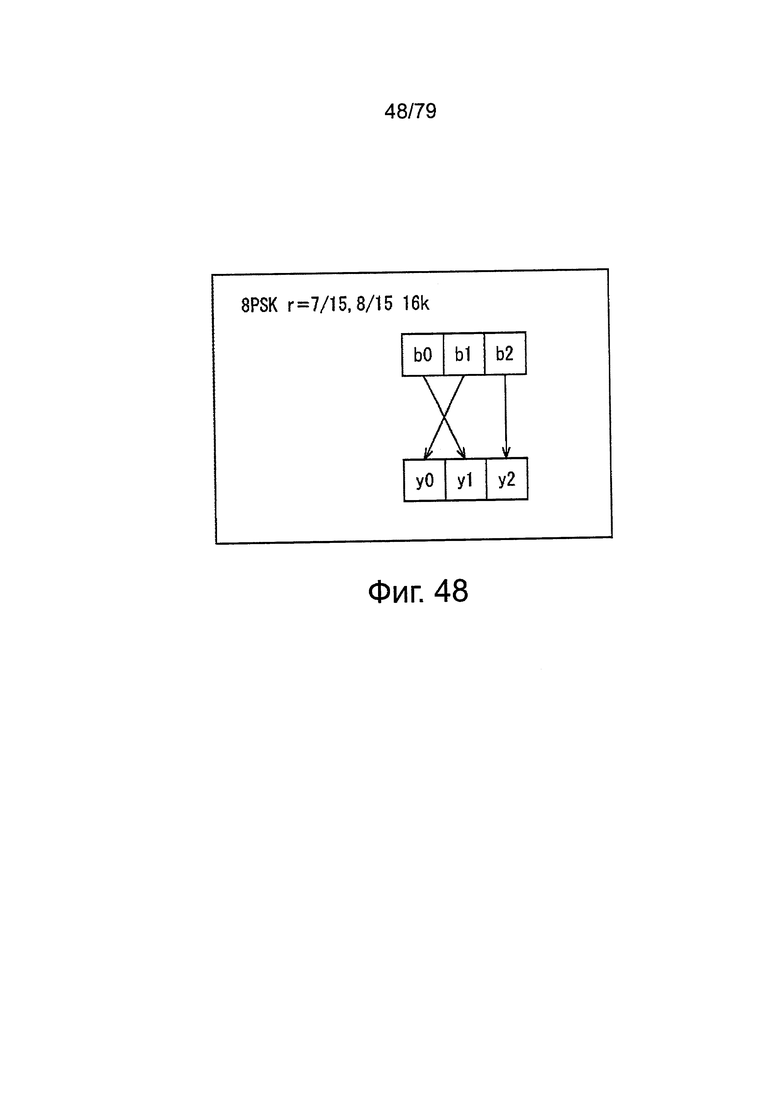

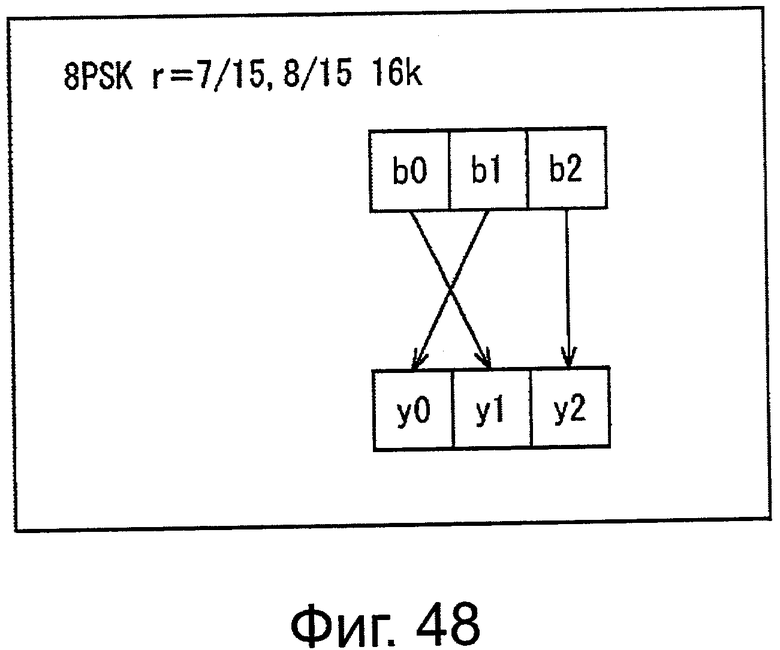

фиг. 48 - вид, показывающий первый пример процесса перестановки в соответствии со способом перестановки для Sx, когда способом модуляции является 8-позиционная PSK и множитель b равен 1 при передаче данных с использованием 16К кода для Sx;

фиг. 49 - вид, показывающий второй пример процесса перестановки в соответствии со способом перестановки для Sx, когда способом модуляции является 8-позиционная PSK и множитель b равен 1 при передаче данных с использованием 16К кода для Sx;

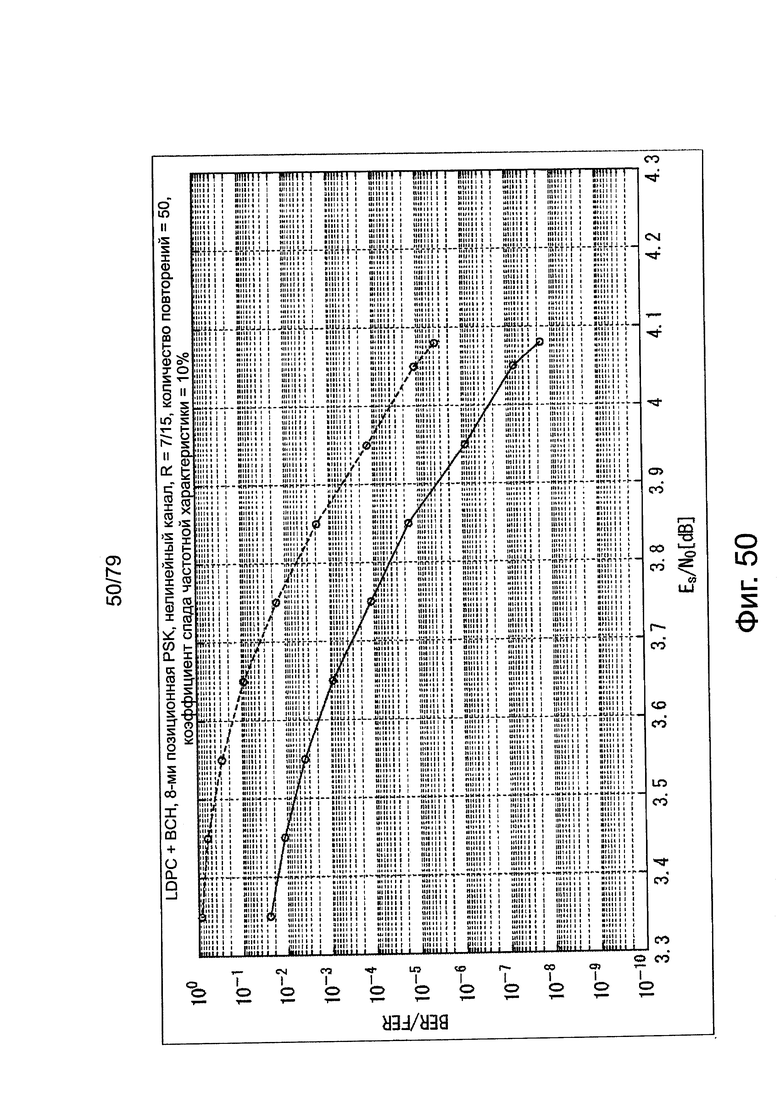

фиг. 50 - вид, показывающий результат моделирования при измерении BER/FER в ходе моделирования;

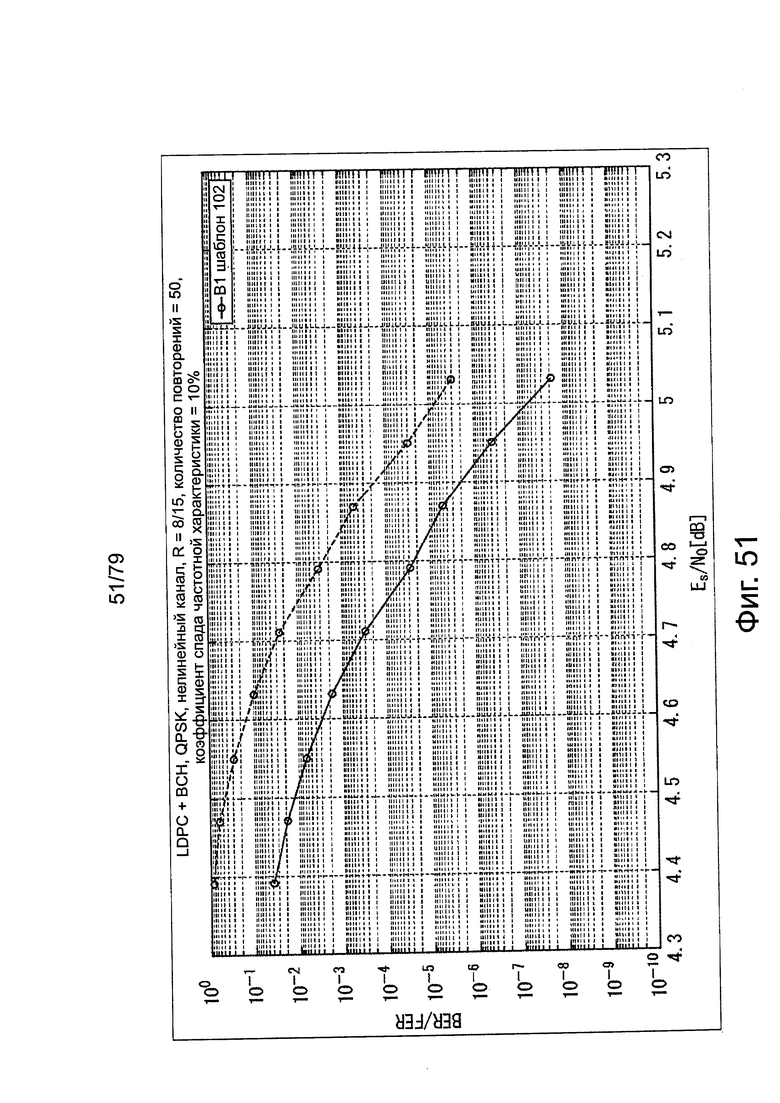

фиг. 51 - вид, показывающий результат моделирования при измерении BER/FER в ходе моделирования;

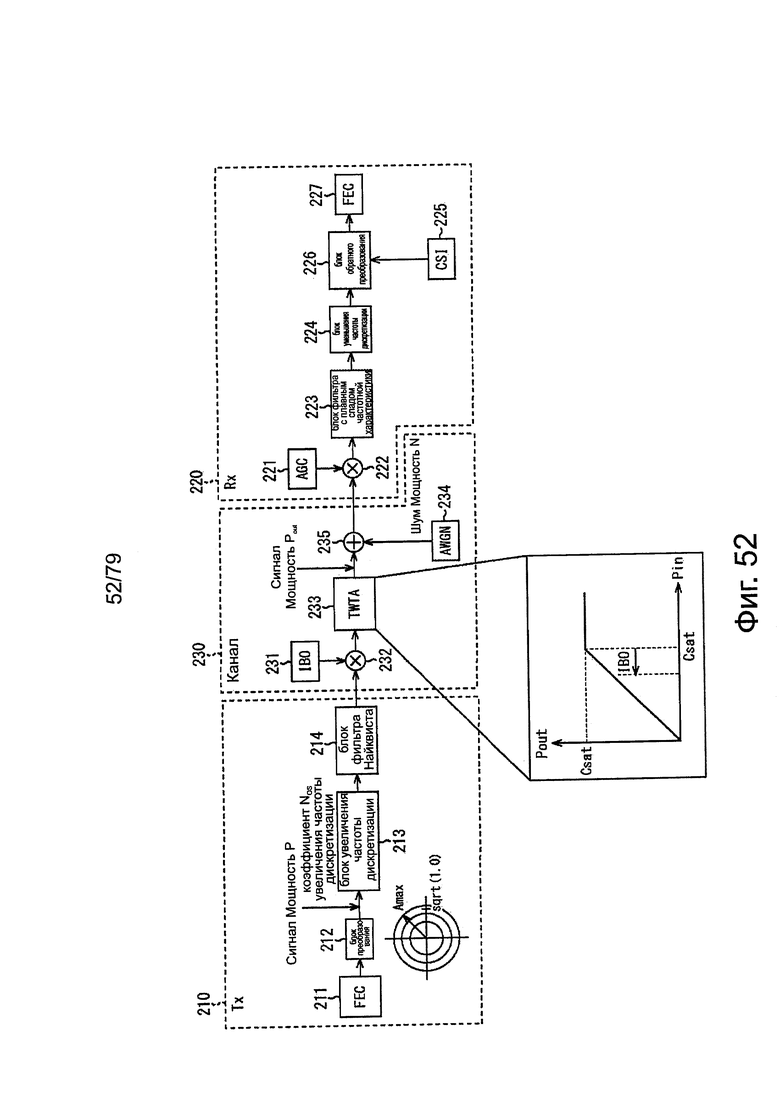

фиг. 52 - вид, показывающий структурную схему, иллюстрирующую модель системы передачи, используемой при моделировании;

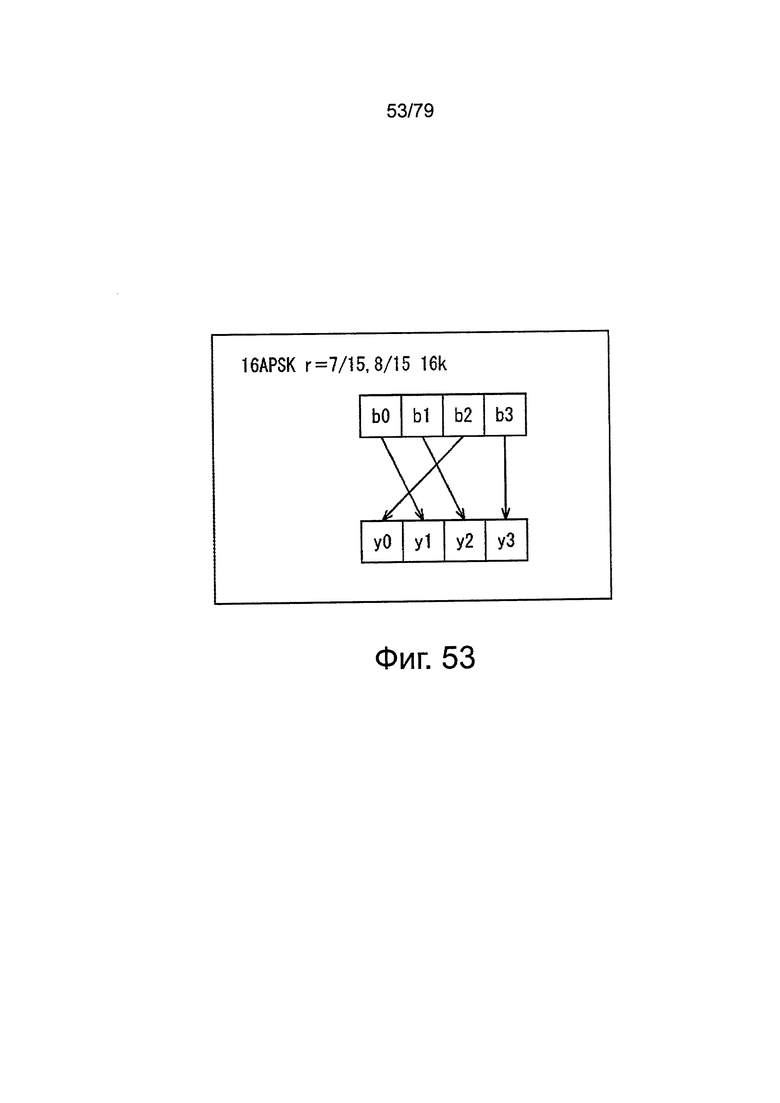

фиг. 53 - вид, показывающий первый пример процесса перестановки в соответствии со способом перестановки для Sx, когда способом модуляции является 16-позиционная APSK и множитель b равен 1 при передаче данных с использованием 16К кода для Sx;

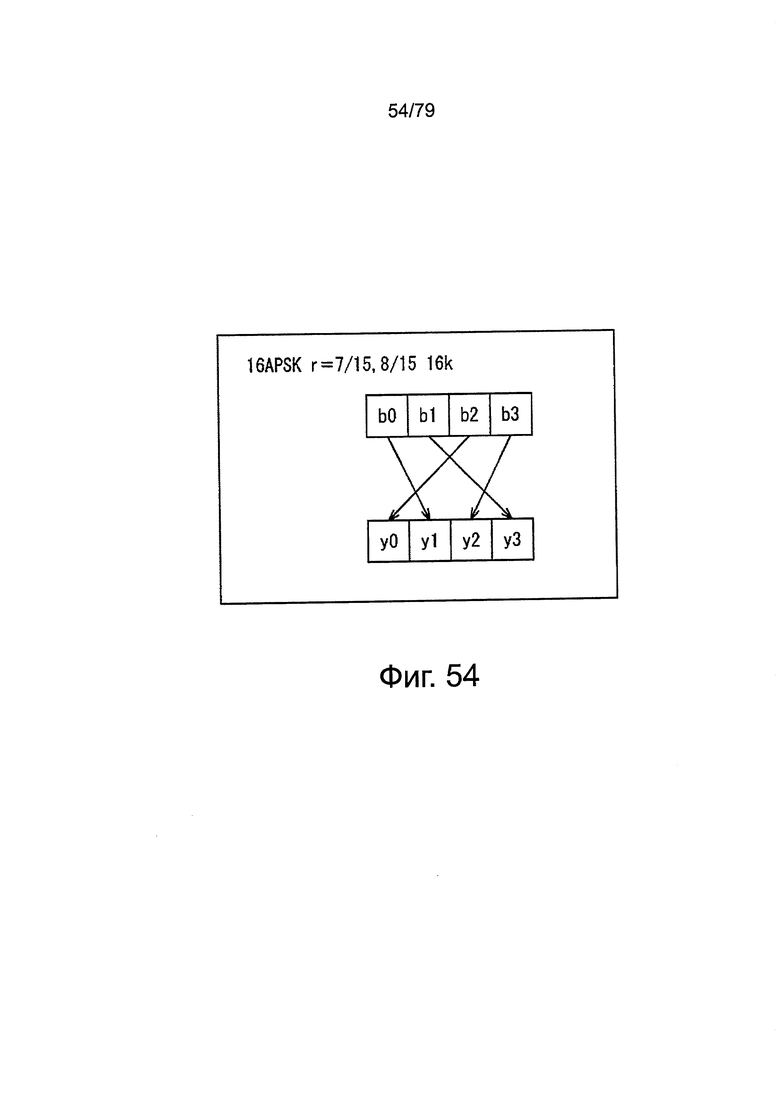

фиг. 54 - вид, показывающий второй пример процесса перестановки в соответствии со способом перестановки для Sx, когда способом модуляции является 16-позиционная APSK и множитель b равен 1 при передаче данных с использованием 16К кода для Sx;

фиг. 55 - вид, показывающий третий пример процесса перестановки в соответствии со способом перестановки для Sx, когда способом модуляции является 16-позиционная APSK и множитель b равен 1 при передаче данных с использованием 16К кода для Sx;

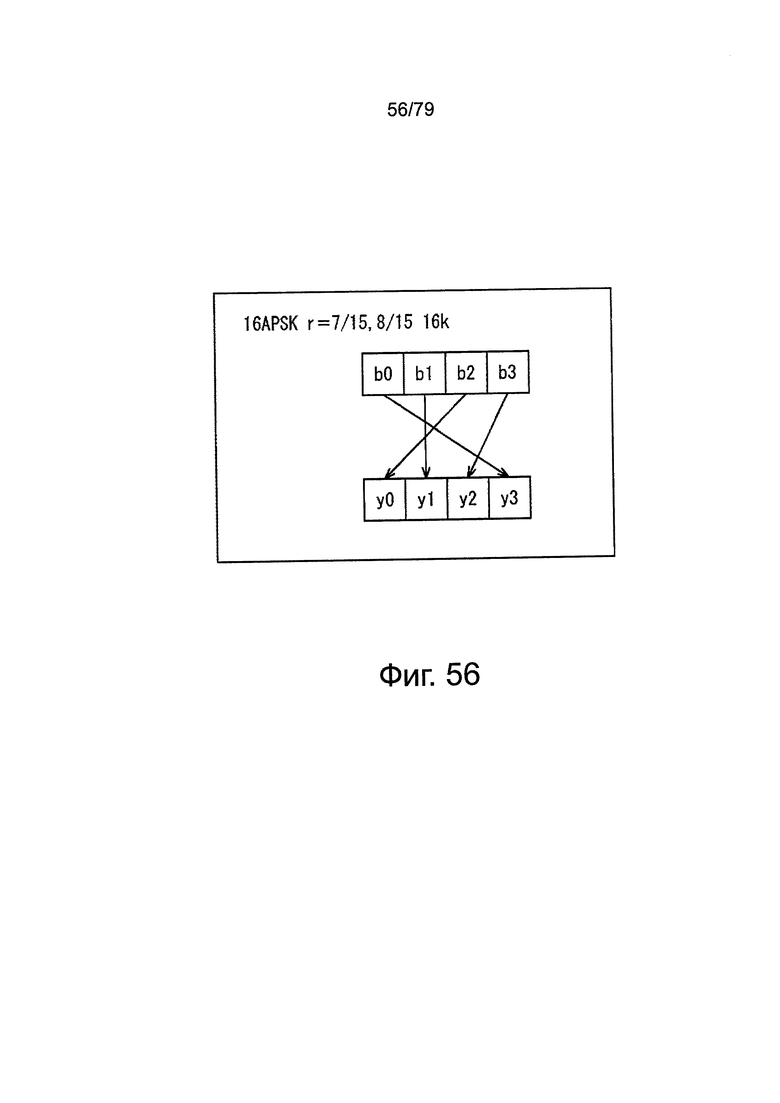

фиг. 56 - вид, показывающий четвертый пример процесса перестановки в соответствии со способом перестановки для Sx, когда способом модуляции является 16-позиционная APSK и множитель b равен 1 при передаче данных с использованием 16К кода для Sx;

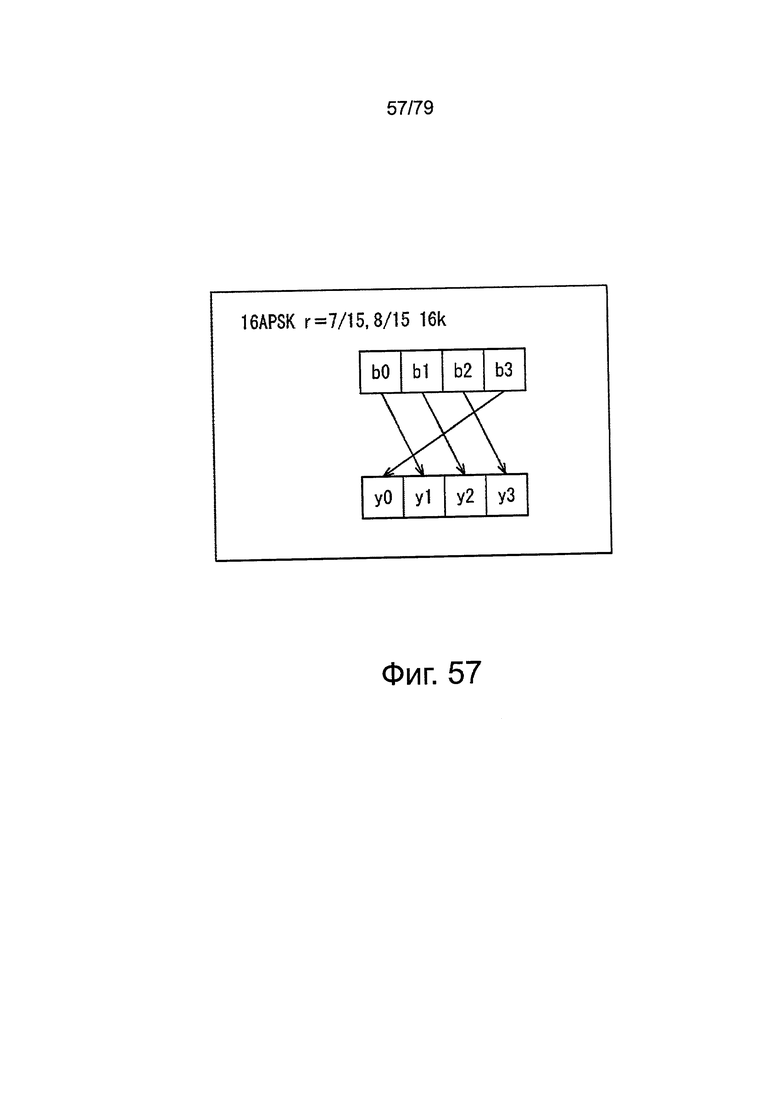

фиг. 57 - вид, показывающий пятый пример процесса перестановки в соответствии со способом перестановки для Sx, когда способом модуляции является 16-позиционная APSK и множитель b равен 1 при передаче данных с использованием 16К кода для Sx;

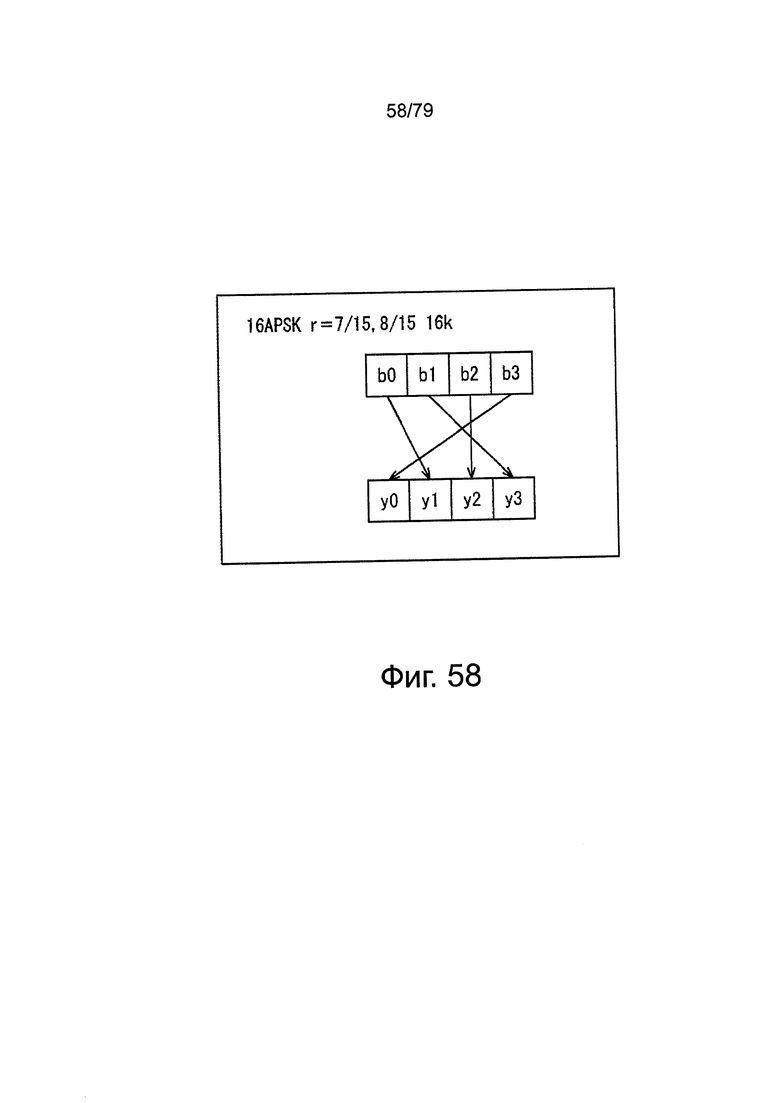

фиг. 58 - вид, показывающий шестой пример процесса перестановки в соответствии со способом перестановки для Sx, когда способом модуляции является 16-позиционная APSK и множитель b равен 1 при передаче данных с использованием 16К кода для Sx;

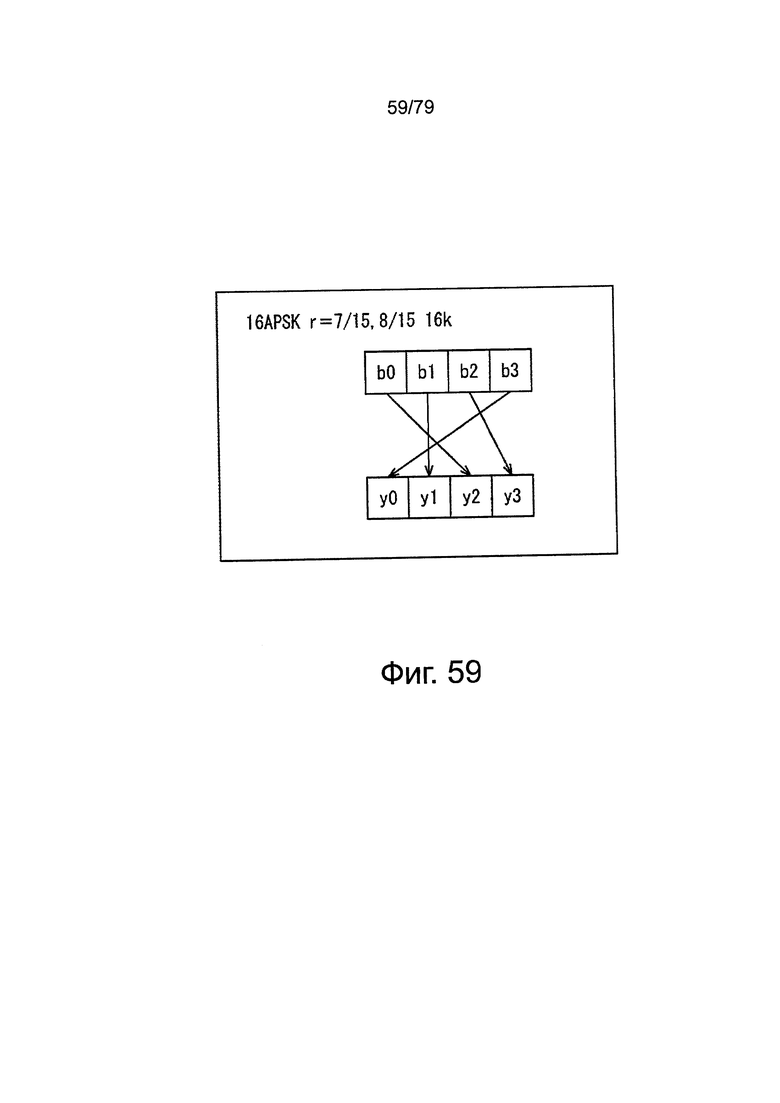

фиг. 59 - вид, показывающий седьмой пример процесса перестановки в соответствии со способом перестановки для Sx, когда способом модуляции является 16-позиционная APSK и множитель b равен 1 при передаче данных с использованием 16К кода для Sx;

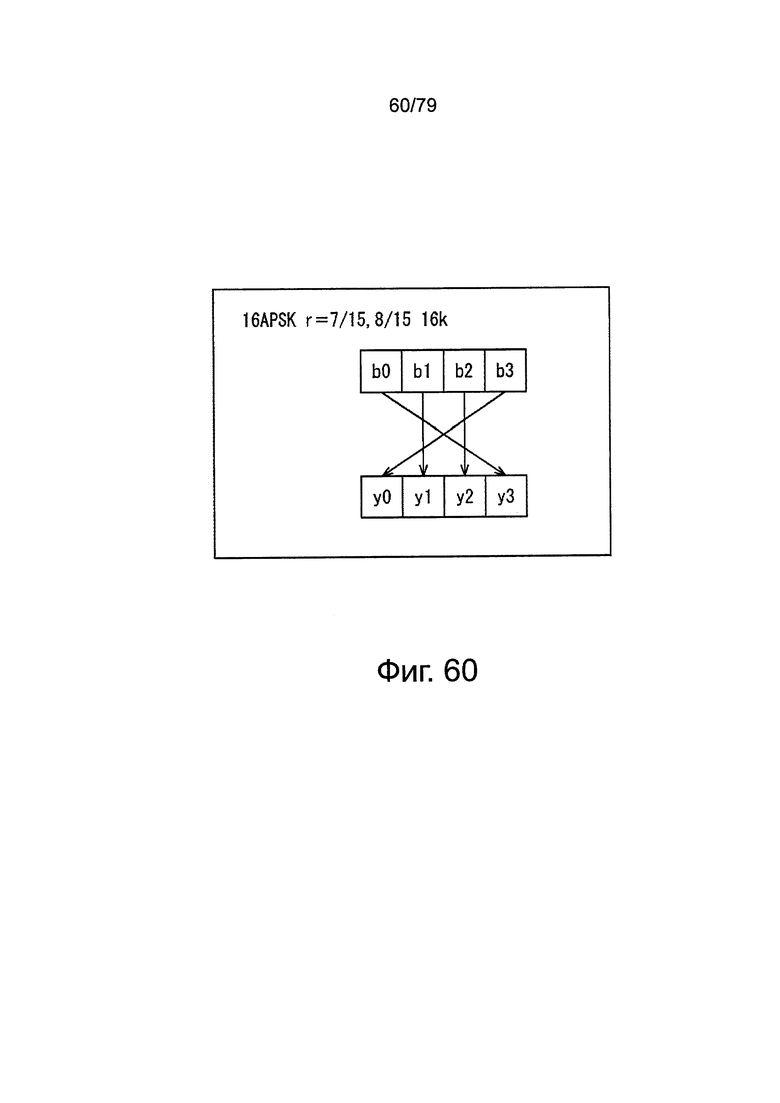

фиг. 60 - вид, показывающий восьмой пример процесса перестановки в соответствии со способом перестановки для Sx, когда способом модуляции является 16-позиционная APSK и множитель b равен 1 при передаче данных с использованием 16К кода для Sx;

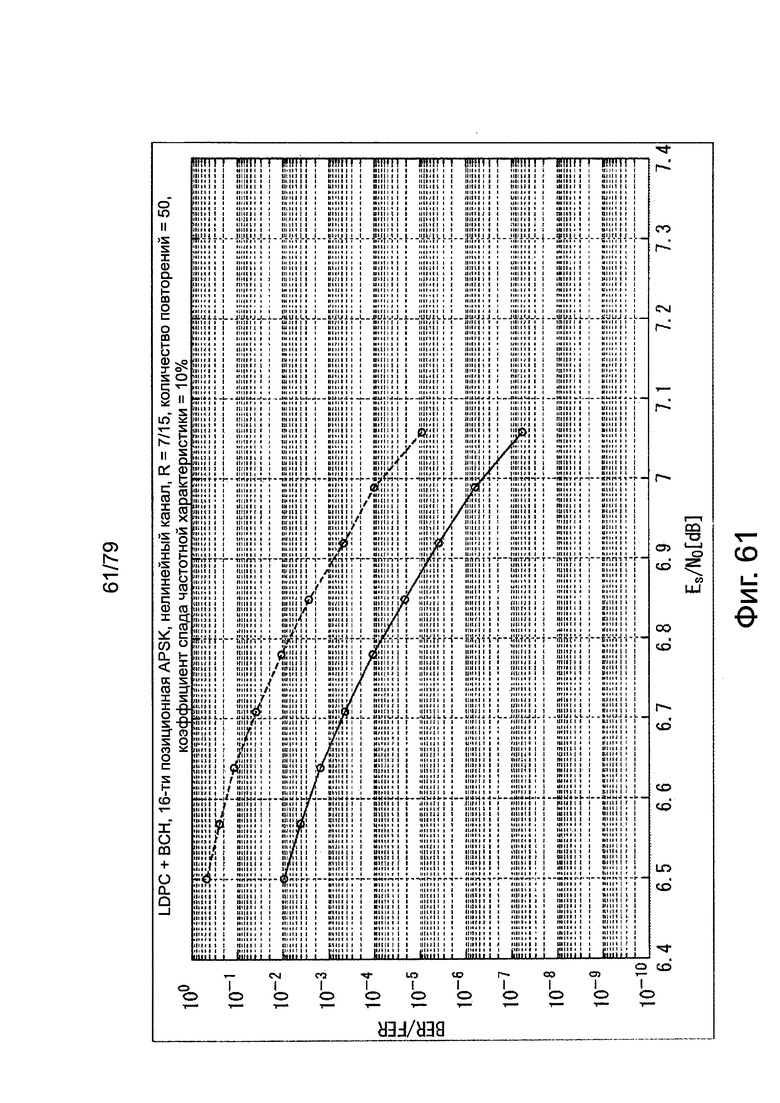

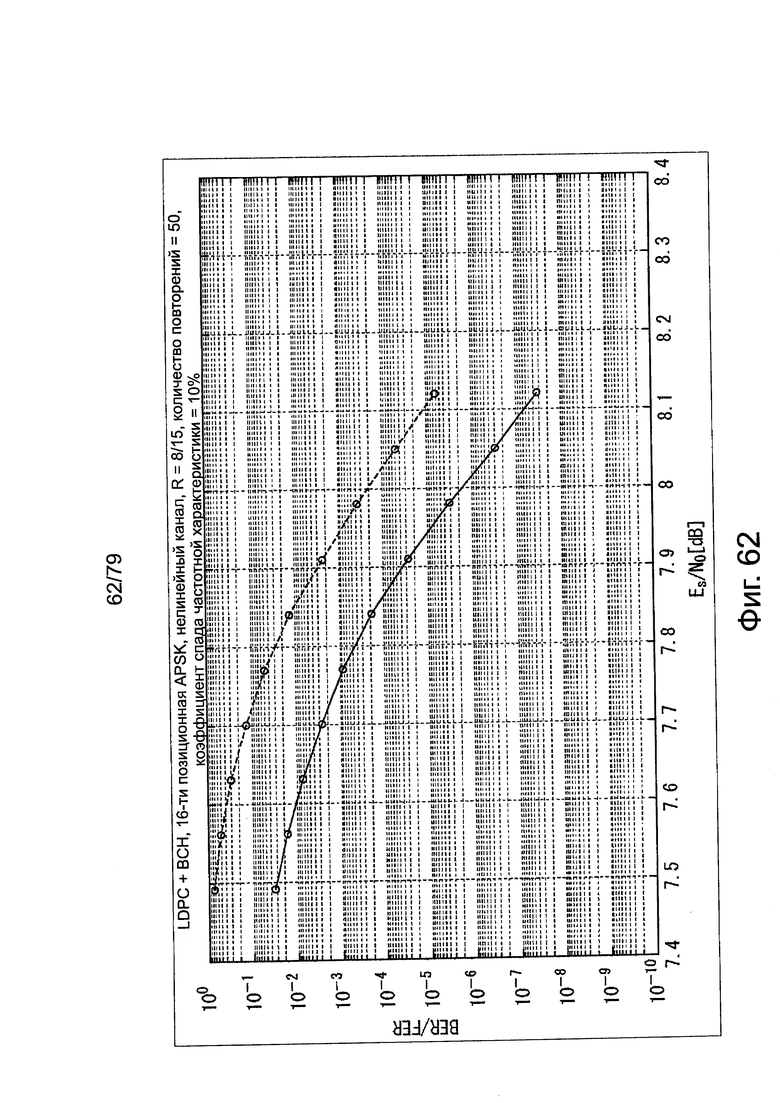

фиг. 61 - вид, показывающий результат моделирования при измерении BER/FER в ходе моделирования;

фиг. 62 - вид, показывающий результат моделирования при измерении BER/FER в ходе моделирования;

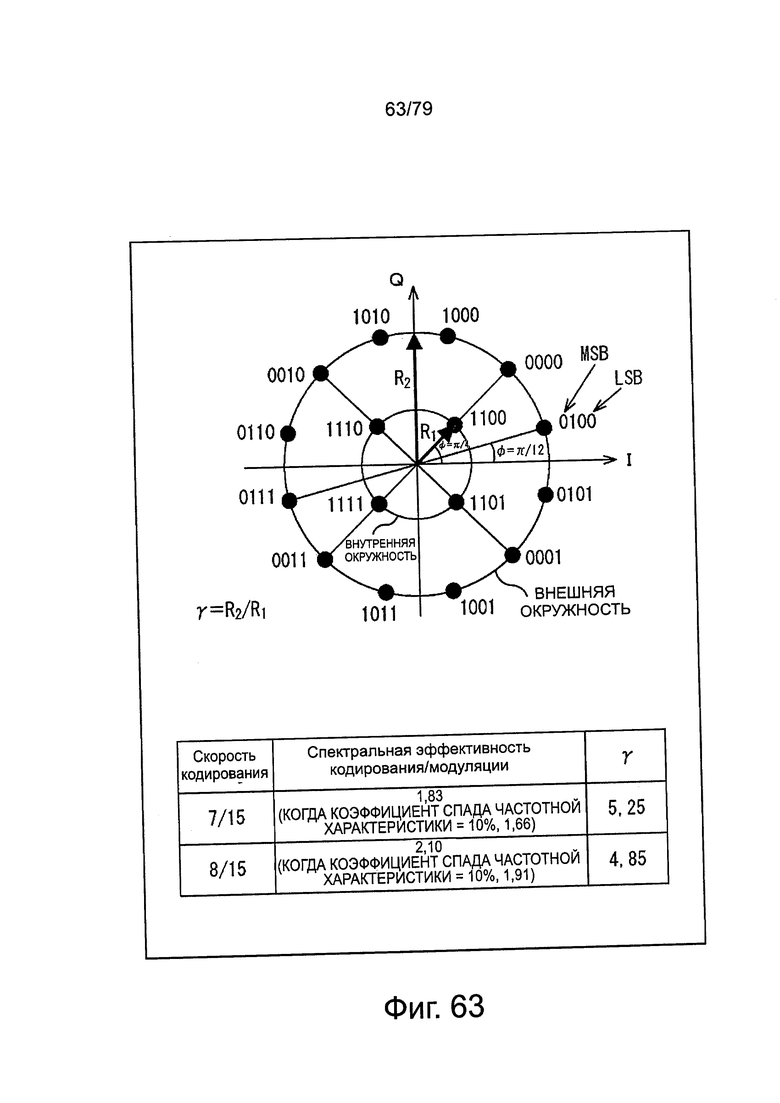

фиг. 63 - вид, показывающий пример расположения сигнальных точек 16-позиционной APSK и отношение γрадиусов, когда 16-позиционную APSK используют в качестве способа модуляции.

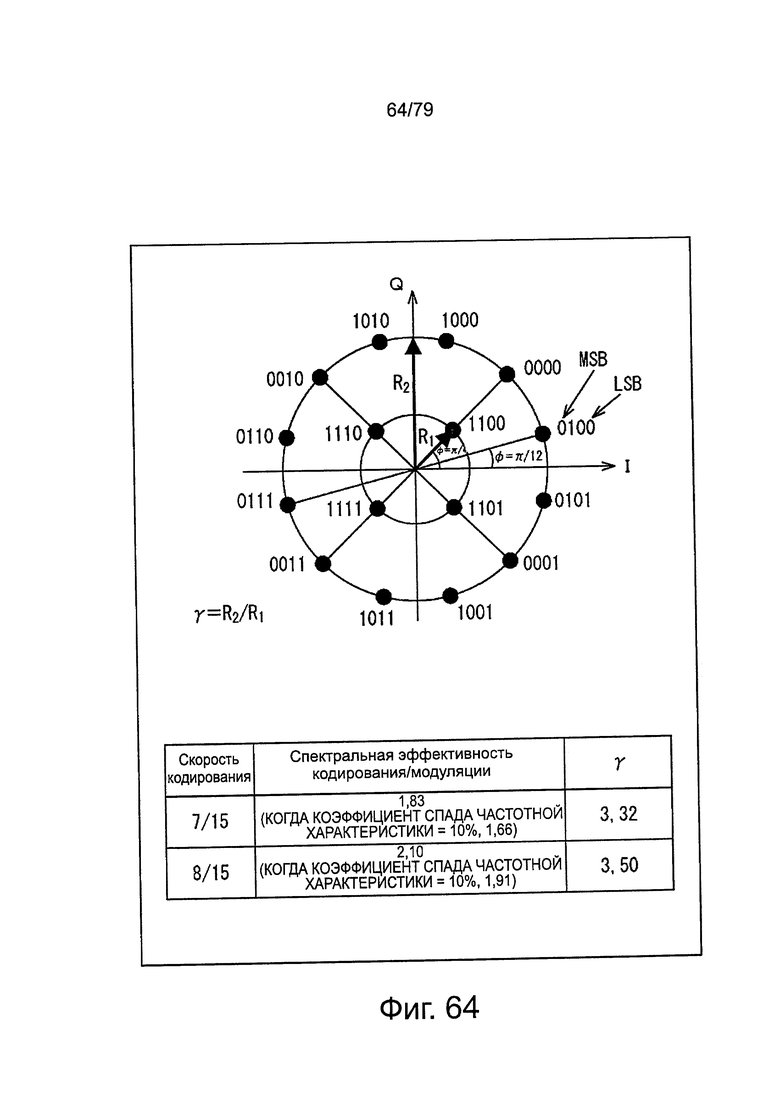

фиг. 64 - вид, показывающий пример расположения сигнальных точек 16-позиционной APSK и отношение γрадиусов, когда 16-позиционную APSK используют в качестве способа модуляции.

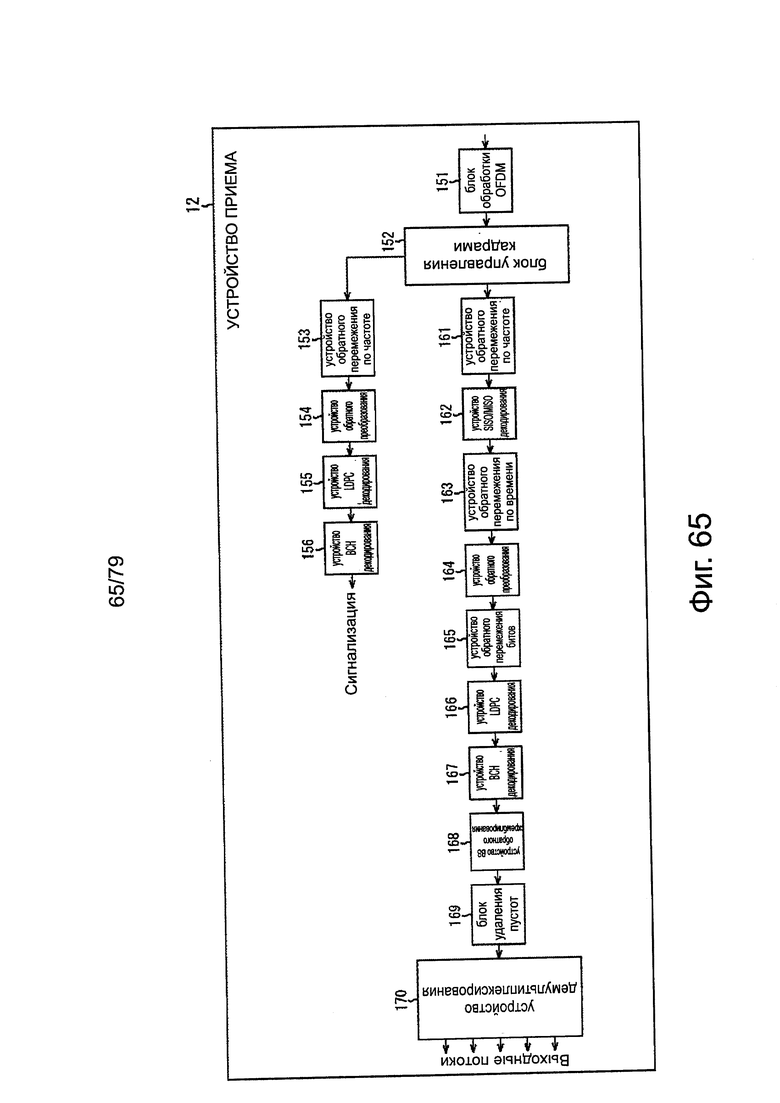

фиг. 65 - вид, показывающий структурную схему примера конфигурации устройства 12 приема с фиг. 7;

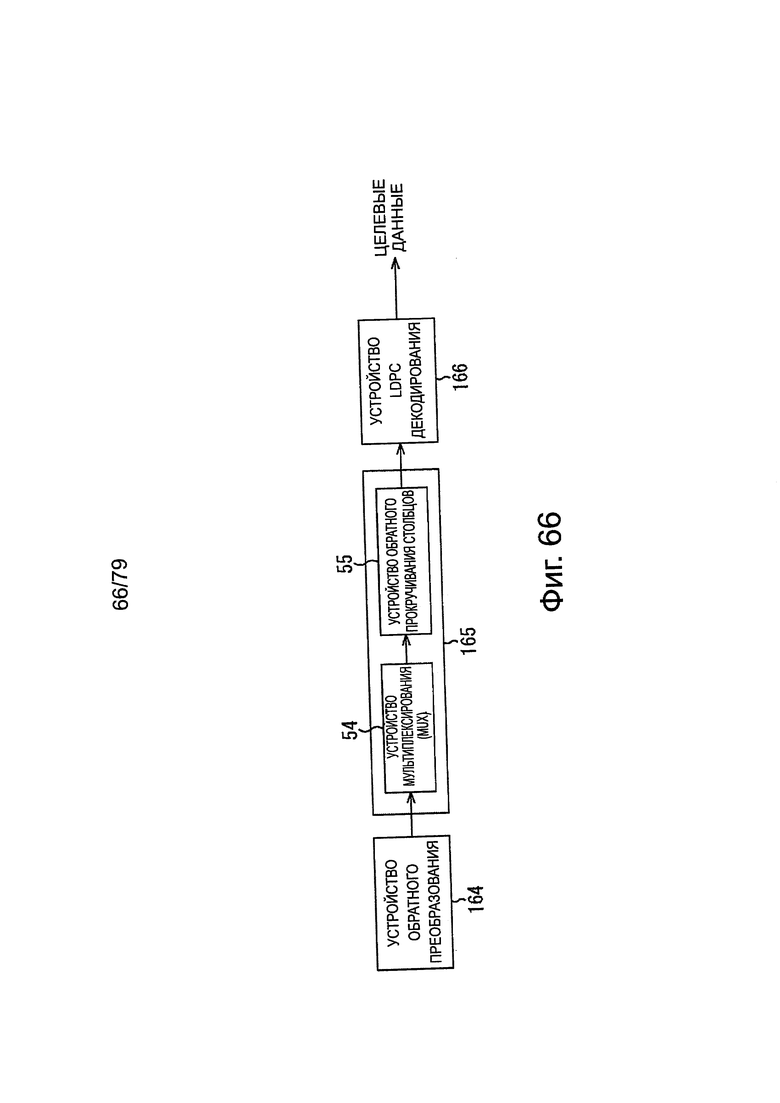

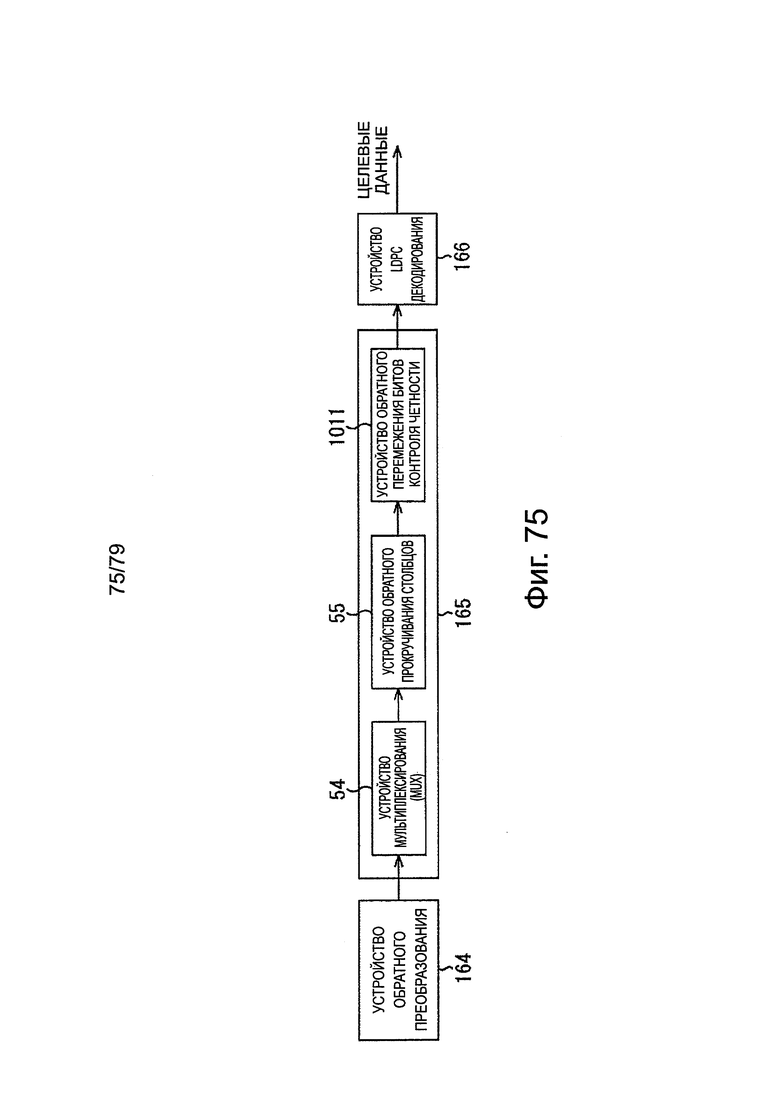

фиг. 66 - вид, иллюстрирующий структурную схему, показывающую пример конфигурации устройства 165 обращения перемежения битов;

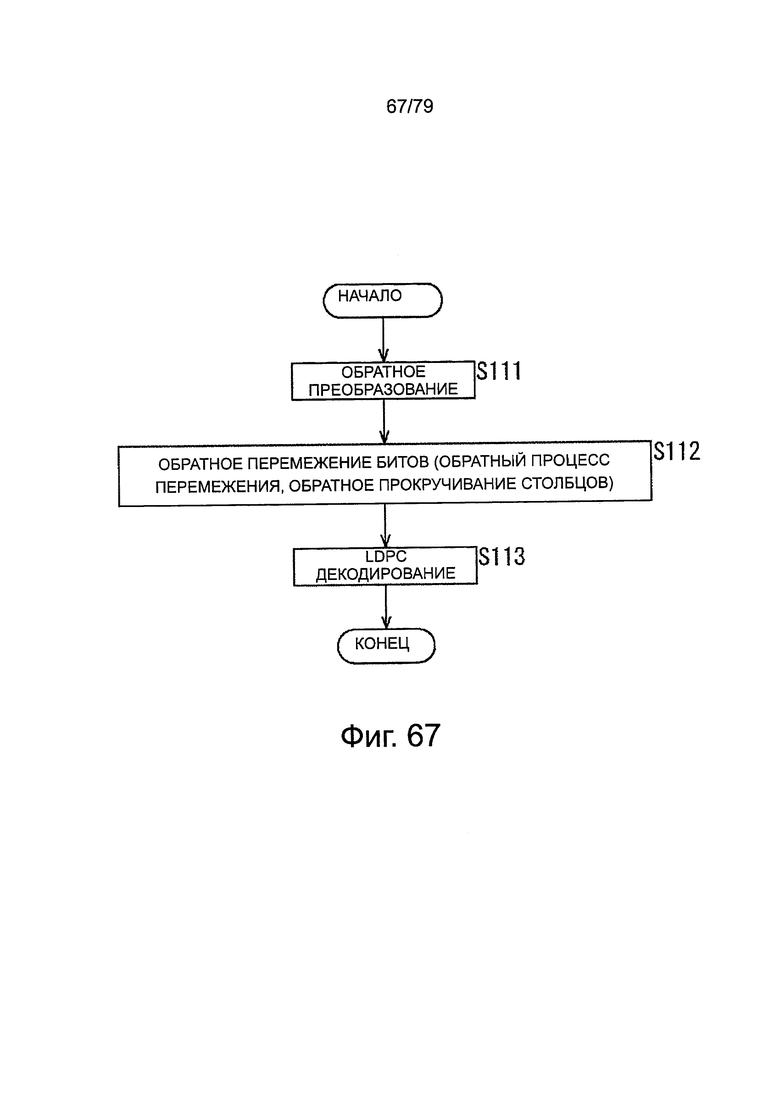

фиг. 67 - вид, показывающий блок-схему, иллюстрирующую процесс обработки, осуществляемый в устройстве 164 обратного преобразования, устройстве 165 обратного перемежения битов и устройстве 166 LDPC декодирования;

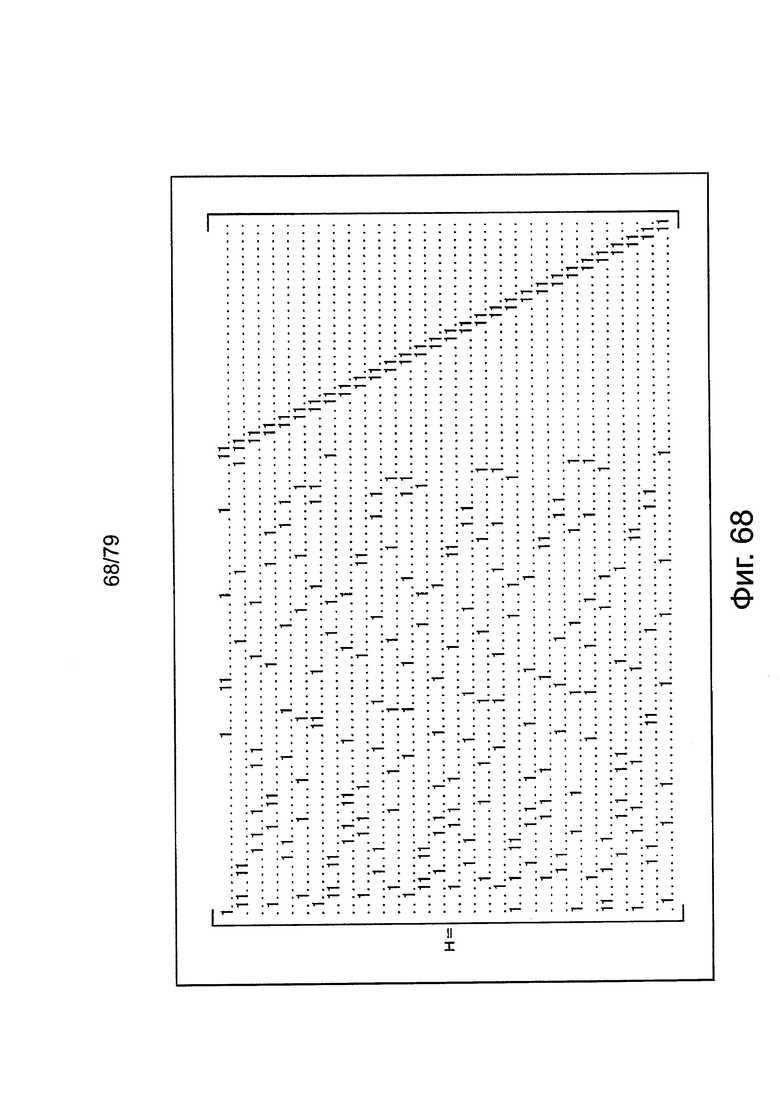

фиг. 68 - вид, показывающий пример проверочной матрицы LDPC-кода;

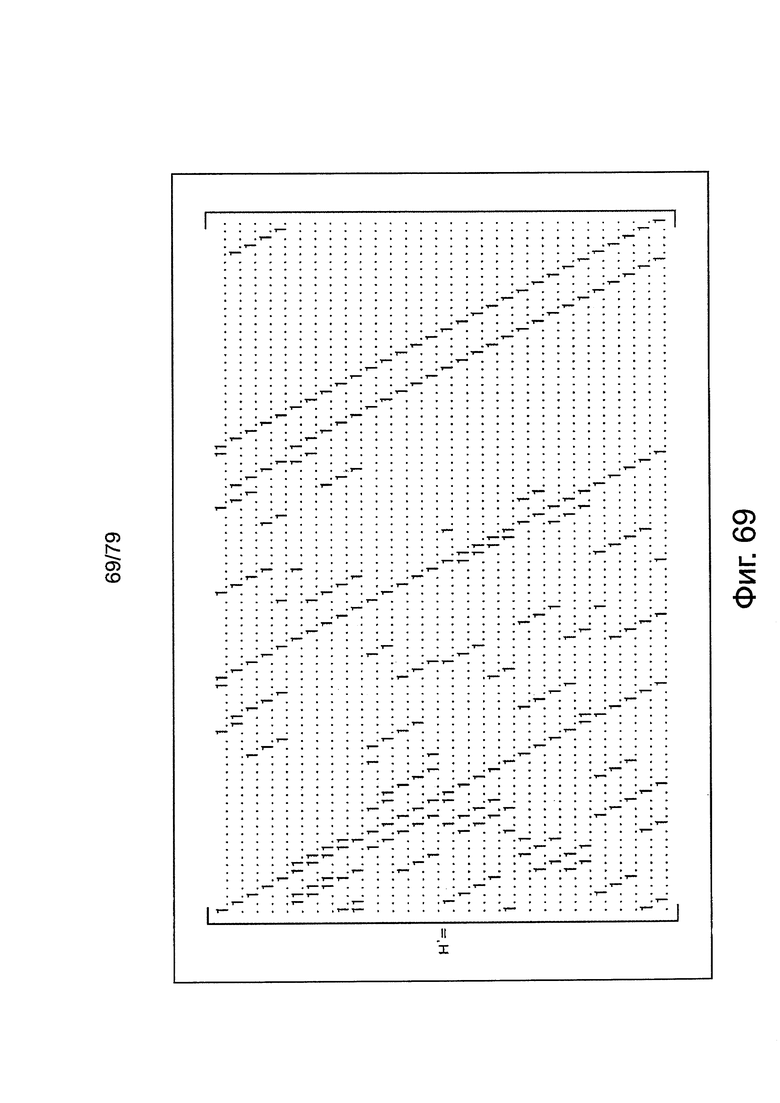

фиг. 69 - вид, показывающий матрицу (проверочная матрица), полученную путем применения замены строк и замены столбцов к проверочной матрице;

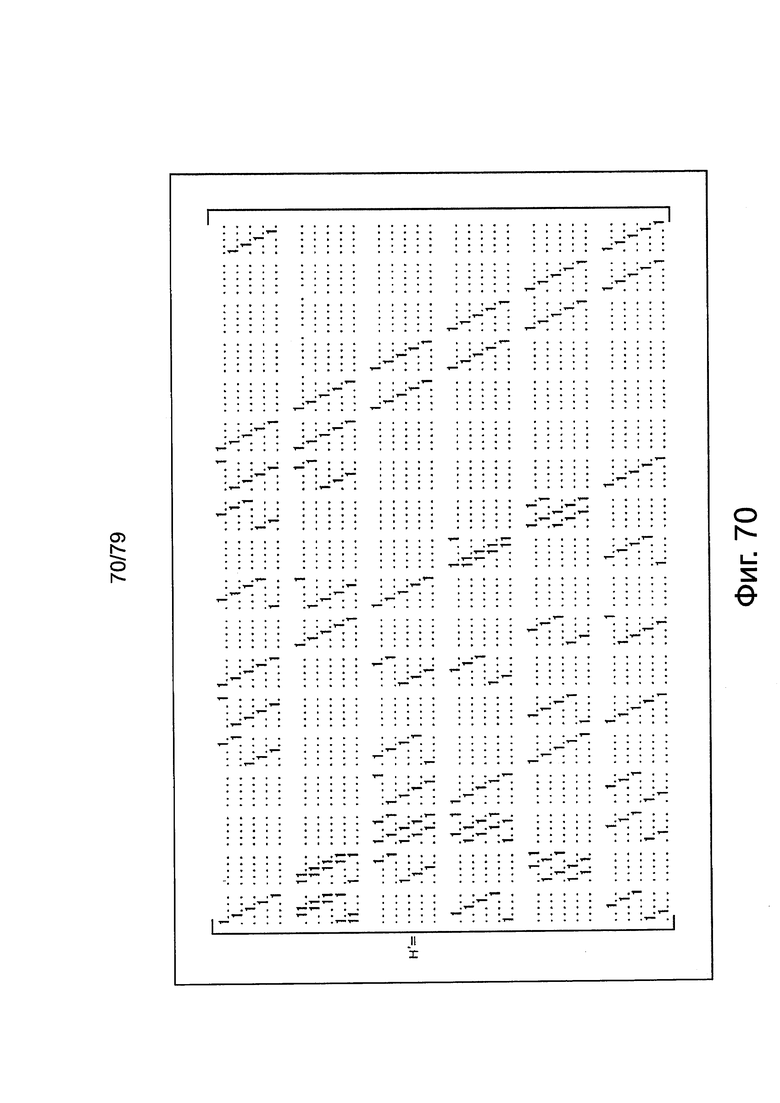

фиг. 70 - вид, показывающий проверочную матрицу, разделенную на блоки из матриц размера 5×5;

фиг. 71 - вид, иллюстрирующий структурную схему, показывающую пример конфигурации устройства декодирования, в котором осуществляют совместно Р преобразований вершины;

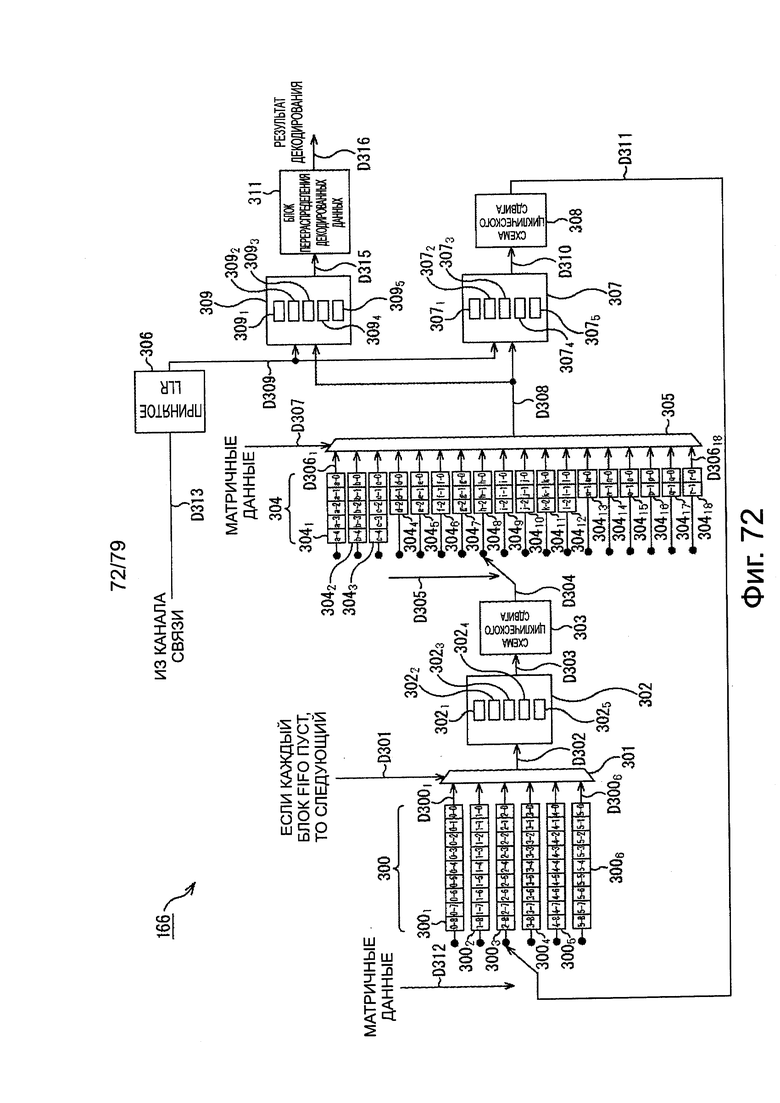

фиг. 72 - вид, иллюстрирующий структурную схему, показывающую пример конфигурации устройства 166 LDPC декодирования;

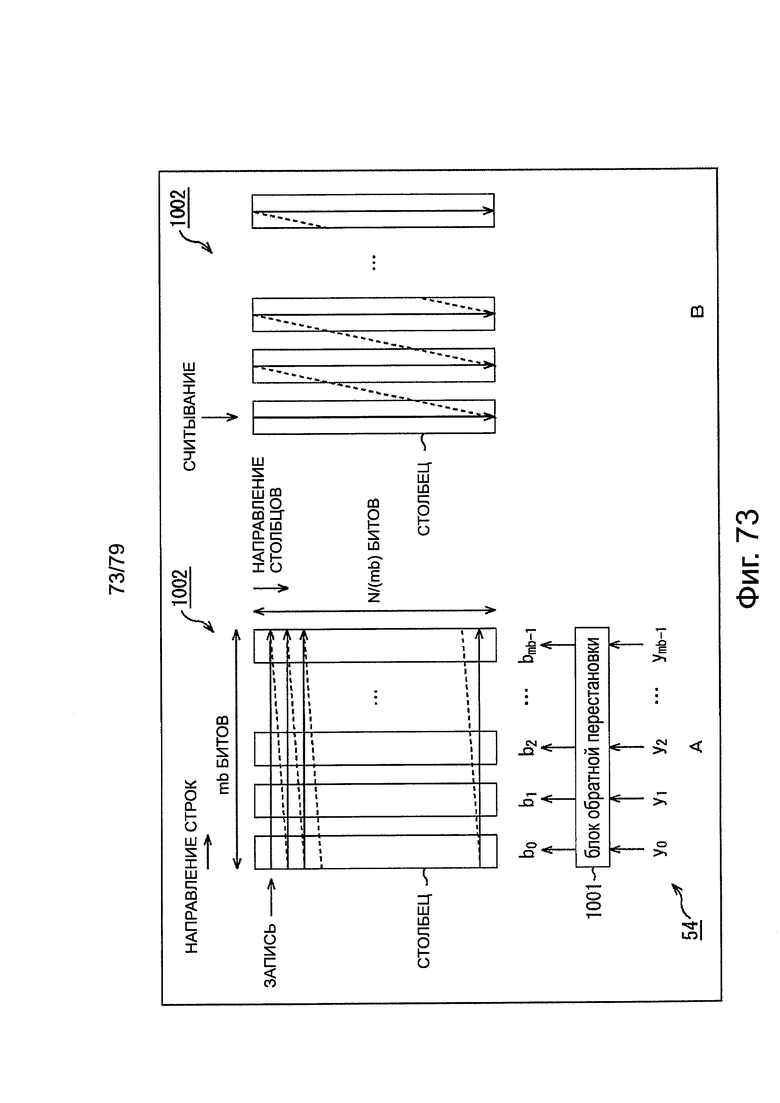

фиг. 73 - вид, показывающий обработку, осуществляемую устройством 54 мультиплексирования, входящим в состав устройства 165 обращения перемежения битов;

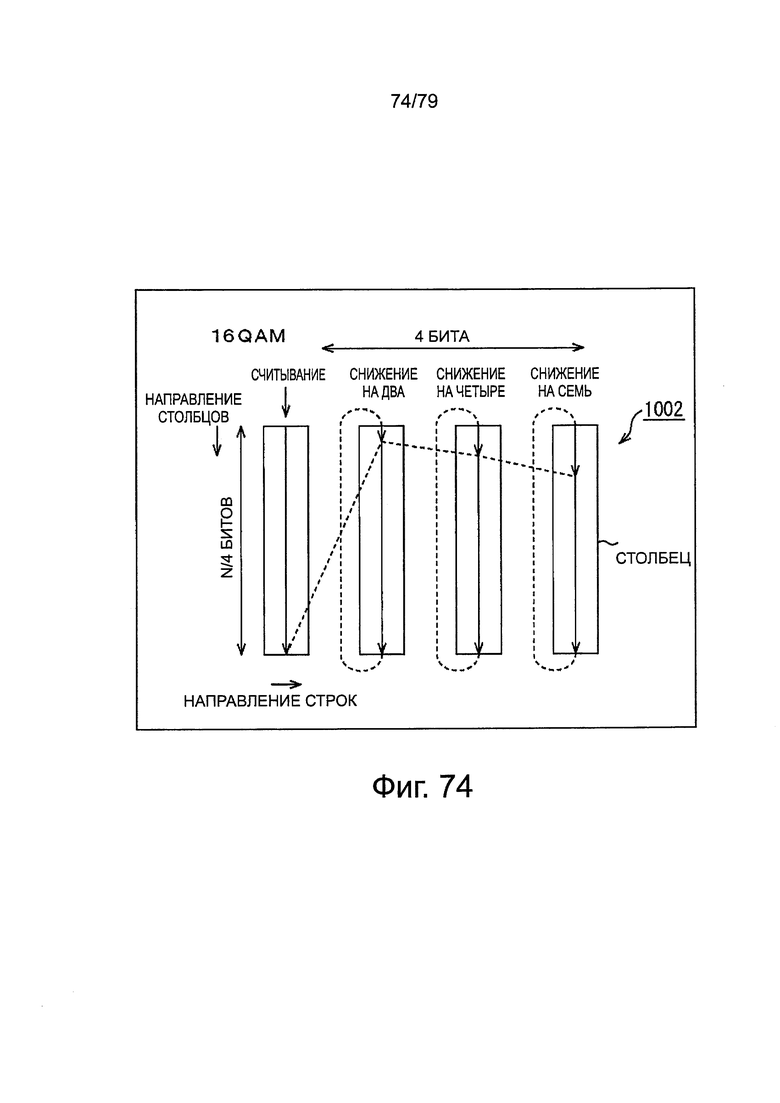

фиг. 74 - вид, показывающий обработку, осуществляемую устройством 55 обращения прокручивания столбцов;

фиг. 75 - вид, иллюстрирующий структурную схему, показывающую другой пример конфигурации устройства 165 обращения перемежения битов;

фиг. 76 показана структурная схема, иллюстрирующая первый пример конфигурации системы приема, которая может быть применена в устройстве 12 приема,

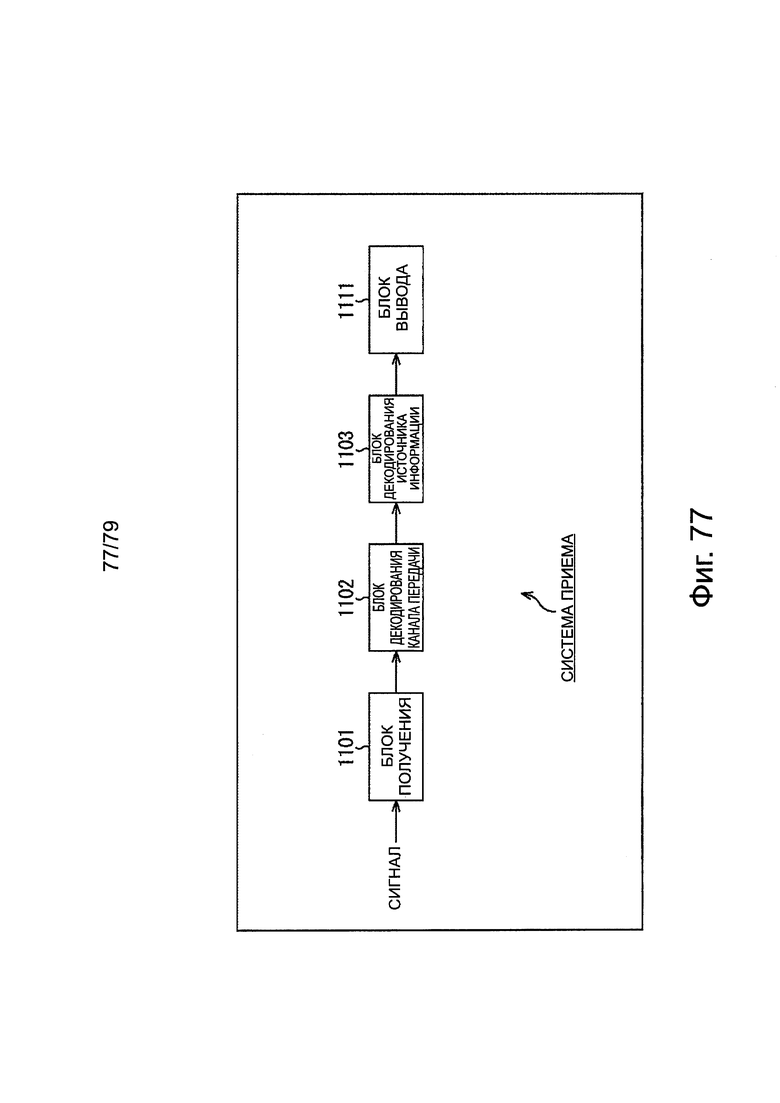

фиг. 77 - вид, иллюстрирующий структурную схему, показывающую второй пример конфигурации системы приема, которая может быть применена в устройстве 12 приема;

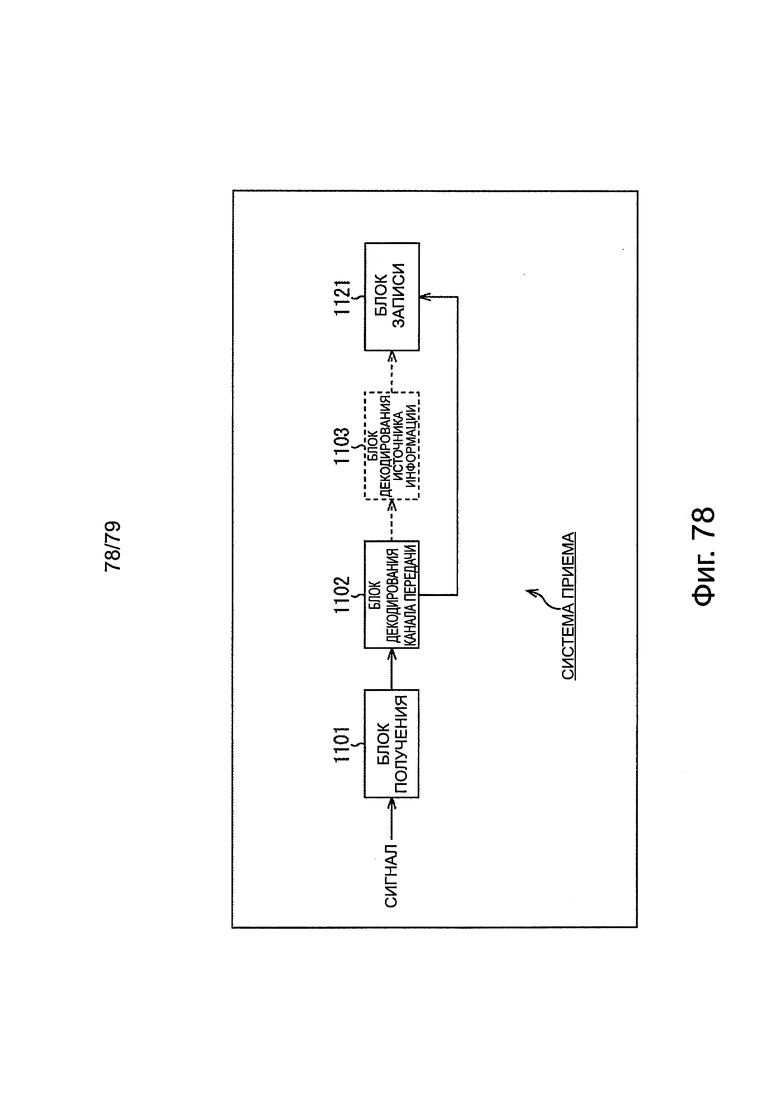

фиг. 78 - вид, иллюстрирующую структурную схему, показывающую третий пример конфигурации системы приема, которая может быть применена в устройстве 12 приема;

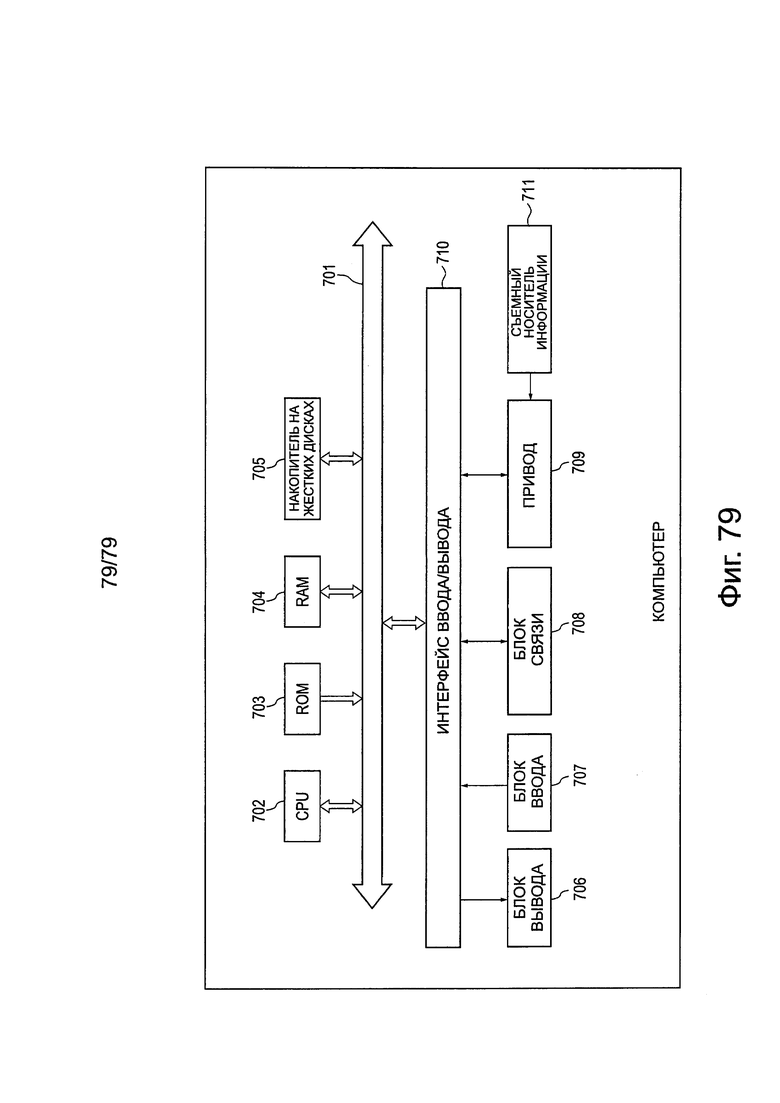

фиг. 79 - вид, показывающий структурную схему, иллюстрирующую пример конфигурации варианта осуществления компьютера, в котором применено настоящее изобретение.

Осуществление изобретения

Далее перед описанием вариантов осуществления настоящего изобретения будет описан LDPC-код.

LDPC-код

LDPC-код является линейным кодом и LDPC-код не обязательно является двоичным кодом. Тем не менее, в рассматриваемом случае предполагаем, что LDPC-код является двоичным кодом.

Наиболее значительное свойство LDPC-кода заключается в том, что проверочная матрица, определяющая LDPC-код, является разряженной. В рассматриваемом случае под разряженной матрицей понимается матрица, в которой очень мало количество элементов, равных «1» (практически все элементы матрицы равны 0).

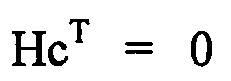

На фиг. 1 показан пример проверочной матрицы Н LDPC-кода.

В проверочной матрице Н с фиг. 1 вес каждого столбца (вес столбца) (количество элементов, равных «1») равен «3», а вес каждой строки (вес строки) равен «6».

При осуществлении кодирования, например, с помощью LDPC-кода (LDPC кодирование) на основе проверочной матрицы Н получают порождающую матрицу G и для получения кодового слова (LDPC-кода) эту порождающую матрицу G умножают на двоичные информационные биты.

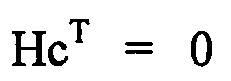

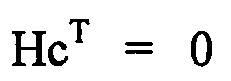

В частности, в устройстве кодирования, осуществляющем LDPC кодирование, сначала вычисляют порождающую матрицу G, которая удовлетворяет равенству GHT=0 для транспонированной матрицы HT проверочной матрицы Н и порождающей матрицы G. В этом случае порождающая матрица G является K×N матрицей, в устройстве кодирования умножают порождающую матрицу G на строку битов (вектор u), которая состоит из K информационных бит, в результате чего получают кодовое слово с (=uG), состоящее из N бит. Кодовое слово (LDPC-код), полученное в устройстве кодирования, передают по заранее заданному каналу связи и получают на приемной стороне.

LDPC-код можно декодировать с помощью алгоритма, называемого вероятностным декодированием и предложенного Галлагером (Gallager), то есть алгоритма передачи сообщений с использованием распространения надежности на, так называемом, графе Таннера, который содержит переменную вершину (также называемую вершиной сообщения) и проверочную вершину. Здесь и далее и переменную вершину, и проверочную вершину будем называть просто вершиной.

На фиг. 2 показана процедура декодирования LDPC-кода.

Здесь и далее действительное число (принятое LLR), полученное представлением правдоподобия «0» значения i-го бита LDPC-кода (одно кодовое слово), полученного на приемной стороне, в виде логарифма отношения правдоподобия, называют принятым значением u0i. Кроме того, сообщение, выходящее из проверочной вершины, обозначаем через uj, а сообщение, выходящее из переменной вершины, обозначаем через vi.

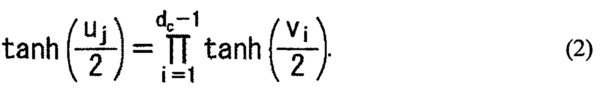

При декодировании LDPC-кода сначала, как показано на фиг. 2, на этапе S11 принимают LDPC-код и сообщению (сообщению проверочной вершины) uj присваивают значение «0», а переменной k, которая является целым числом и представляет собой счетчик повторений процесса обработки, присваивают значение «0», после чего обработка переходит на этап S12. На этапе S12 сообщение (сообщение переменной вершины) vi вычисляют путем осуществления преобразования (преобразование переменной вершины), представленного в равенстве (1), что делают на основе принятого значения u0i, полученного при приеме LDPC-кода, и сообщение uj вычисляют путем осуществления преобразования (преобразование проверочной вершины), представленного в равенстве (2), что делают на основе сообщения vi.

Здесь dv и dc в равенстве (1) и равенстве (2) являются соответственно параметрами, которые могут быть выбраны произвольным образом и которые представляют собой количество «1» в продольном направлении (направлении столбцов) и поперечном направлении (направлении строк) проверочной матрицы Н. Например, в случае LDPC-кода ((3, 6) LDPC-кода) с проверочной матрицей Н, в которой вес столбца равен 3, а вес строки равен 6, как показано на фиг. 1, устанавливают dv=3 и dc=6.

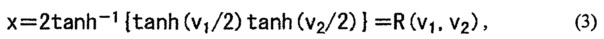

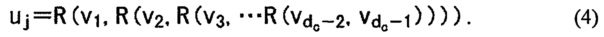

В преобразовании переменной вершины из равенства (1) и преобразовании проверочной вершины из равенства (2), так как сообщение, поступившее на вход по ребру (линии, соединяющей переменную и проверочную вершины) с целью подачи на выход сообщения, не является целью преобразования, результат преобразования находится в диапазоне от 1 до dv-1 или от 1 до dc-1. Преобразование проверочной вершины из равенства (2) фактически осуществляют путем предварительной подготовки таблицы значений функции R (v1, v2), которая представлена в равенстве (3) и результатом которой является одно число, полученное по двум входам v1 и v2 и последующим последовательным (рекурсивным) использованием таблицы в соответствии с равенством (4).

На этапе S12 значение переменной k увеличивается на «1» и обработка переходит на этап S13. На этапе S13 определяют, превосходит ли значение переменной k заранее заданное количество С повторений декодирования. Если на этапе S13 определяют, что значение переменной k не превосходит С, то обработка возвращается на этап S12 и повторяют аналогичный процесс.

Когда на этапе S13 определяют, что значение переменной k превосходит С, то обработка переходит на этап S14, и сообщение vi, которое соответствует результату декодирования, подаваемому на выход, вычисляют путем выполнения преобразования, представленного равенством (5), указанное сообщение подают на выход и заканчивают процесс декодирования LDPC-кода.

В рассматриваемом случае, преобразование из равенства (5) выполняют с использованием сообщений uj от всех ребер, соединенных с переменной вершиной, и указанное преобразование отлично от преобразования переменной вершины из равенства (1).

На фиг. 3 показан пример проверочной матрицы Н (3, 6) LDPC-кода (скорость кодирования равна 1/2, а длина кода равна 12).

В проверочной матрице Н с фиг. 3 вес столбца равен 3, а вес строки равен 6 аналогично фиг. 1.

На фиг. 4 показан граф Таннера проверочной матрицы Н с фиг. 3.

На фиг. 4 проверочные вершины обозначены «+» (плюс), а переменные вершины обозначены «=» (равно). Проверочная и переменная вершины соответствуют строке и столбцу проверочной матрицы Н соответственно. Линия, которая соединяет проверочную вершину с переменной вершиной является ребром и соответствует «1» из элементов проверочной матрицы.

То есть, когда элемент j-й строки и i-го столбца проверочной матрицы равен 1, на фиг. 4, i-я сверху переменная вершина (вершина «=») и j-я сверху проверочная вершина (вершина «+») соединены ребром. Ребро показывает, что на бит кода, соответствующий переменной вершине, наложено ограничение, соответствующее проверочной вершине.

В алгоритме суммы произведений, который представляет собой способ декодирования LDPC-кода, преобразование переменной вершины и преобразование проверочной вершины выполняются неоднократно.

На фиг. 5 показано преобразование переменной вершины, которое осуществляют в переменной вершине.

В переменной вершине сообщение vi соответствующее ребру для вычислений, вычисляют в ходе преобразования переменной вершины, которое соответствует равенству (1) и которое использует сообщения u1 и u2 из оставшихся ребер, соединенных с переменной вершиной, и использует принятое значение u0i. Сообщения, которые соответствуют другим ребрам, также вычисляют с помощью того же способа.

На фиг. 6 показано преобразование проверочной вершины, которое осуществляют в проверочной вершине.

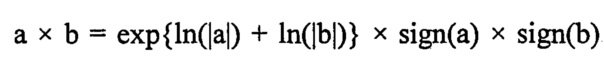

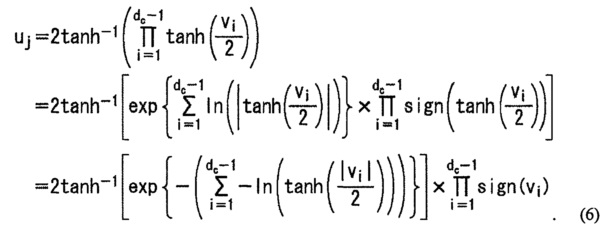

В этом случае преобразование проверочной вершины, которое соответствует равенству (2), может быть переписано с помощью равенства (6) с использованием равенства  . Тем не менее, sign(x) равен 1 в случае x≥0 и равен -1 в случае x<0.

. Тем не менее, sign(x) равен 1 в случае x≥0 и равен -1 в случае x<0.

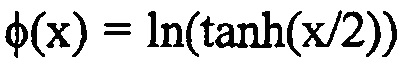

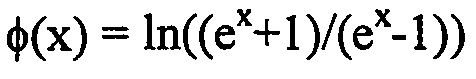

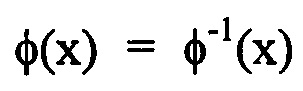

При x≥0, если функция φ(x) определена с помощью равенства  , то справедливо равенство

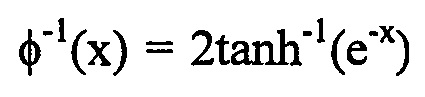

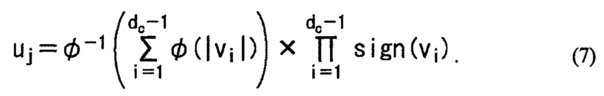

, то справедливо равенство  . По этой причине равенство (6) может быть заменено равенством (7).

. По этой причине равенство (6) может быть заменено равенством (7).

В проверочной вершине преобразование проверочной вершины, соответствующее равенству (2), осуществляют в соответствии с равенством (7).

То есть в проверочной вершине, как показано на фиг. 6, сообщение uj, соответствующее ребру для вычислений, вычисляют в ходе преобразования проверочной вершины, которое соответствует равенству (7) и которое использует сообщения v1, v2, v3, v4 и v5 из оставшихся ребер, соединенных с проверочной вершиной. Сообщения, которые соответствуют другим ребрам, также вычисляют с помощью того же способа.

Функция φ(x) из равенства (7) может быть представлена следующим образом  и

и  справедливо при x>0. Когда функции φ(x) и

справедливо при x>0. Когда функции φ(x) и  реализованы аппаратно, функции φ(x) и

реализованы аппаратно, функции φ(x) и  могут быть реализованы с использованием LUT (Таблица соответствия). Тем не менее, обе функции φ(x) и

могут быть реализованы с использованием LUT (Таблица соответствия). Тем не менее, обе функции φ(x) и  становятся одной и той же LUT.

становятся одной и той же LUT.

Пример конфигурации системы передачи, в которой применено настоящее изобретение

На фиг. 7 показан пример конфигурации варианта осуществления системы передачи (под системой понимается логическое объединение множества устройств и устройство любой конфигурации может быть расположено или может не быть расположено в одном и том же корпусе), в которой применено настоящее изобретение.

На фиг. 7, система передачи содержит устройство 11 передачи и устройство 12 приема.

Например, устройство 11 передачи передает (транслирует) (перемещает) программу телевизионного вещания и так далее. То есть, например, в устройстве 11 передачи кодируют целевые данные, которые являются целью передачи, такие как изображения, звуковые данные, как программу, с помощью LDPC-кода и, например, передают полученные данные, например, по каналу 13 связи, такому как спутниковая схема, поверхностные волны и кабель (проводная схема).

В устройстве 12 приема принимают LDPC-код, переданный устройством 11 передачи по каналу 13 связи, декодируют LDPC-код с целью получения целевых данных и подают на выход целевые данные.

В этом случае известно, что LDPC-код, использованный системой передачи с фиг. 7, показывает очень высокую эффективность в канале связи с AWGN (аддитивным белым гауссовским шумом).

Тем не менее, в канале 13 связи могут быть выработаны пакетные ошибки или стирание информации. Особенно в случае, когда канал 13 связи является поверхностной волной, например, в системе OFDM (ортогональное частотное разделение каналов) мощность конкретного символа может стать равной 0 (стирание) в соответствии с задержкой эха (каналы, отличные от главного) в многоканальной среде, в которой отношение сигнала к шуму равно 0 дБ (мощность шума = эха равна мощности сигнала = главный канал).

При дрожании (канал связи, в котором задержка равна нулю и добавляется эхо с доплеровской частотой), когда отношение сигнала к шуму равно 0 дБ, мощность всего OFDM символа в конкретный момент времени может стать равной 0 (стирание) из-за доплеровской частоты.

Кроме того, пакетные ошибки могут иметь место из-за ситуации с проводной линией от блока приема (не показан на чертежах) на стороне устройства 12 приема, например, когда антенна принимает сигнал от устройства 11 передачи, до устройства 12 приема, или в ситуации нестабильности подачи электроэнергии в устройство 12 приема.

Между тем, при декодировании LDPC-кода, в переменной вершине, соответствующей столбцу проверочной матрицы Н, и биту LDPC-кода, как показано выше на фиг. 5, осуществляют преобразование переменной вершины, соответствующее равенству (1) с добавлением (принятого значения u0i) бита LDPC-кода. По этой причине, если в битах кода, используемых для преобразования переменной вершины, происходит ошибка, то ухудшается точность вычисленного сообщения.

При декодировании LDPC-кода, в проверочной вершине преобразование проверочной вершины, соответствующее равенству (7), осуществляют с использованием сообщения, вычисленного в переменной вершине, соединенной с проверочной вершиной. По этой причине, если увеличивается количество проверочных вершин, для которых одновременно происходят ошибки (в том числе стирания) во множестве соединенных переменных вершин (соответствующие биты LDPC-кода), то уменьшается эффективность декодирования.

То есть, если в двух или нескольких переменных вершинах из переменных вершин, соединенных с проверочной вершиной, одновременно происходит стирание, то проверочная вершина возвращает сообщение, для которого вероятность того, что значение равно 0, и вероятность того, что значение равно 1, равны для всех переменных вершин. В этом случае проверочная вершина, которая возвращает сообщение с равными вероятностями, не вносит вклада в процесс декодирования (один набор из преобразования переменной вершины и преобразования проверочной вершины). В результате необходимо увеличить количество повторений процесса декодирования, эффективность декодирования уменьшается и увеличивается потребление электроэнергии устройством 12 приема, которое осуществляет декодирования LDPC-кода.

Следовательно, в системе передачи с фиг. 7 может быть улучшена устойчивость к пакетной ошибке или стиранию при одновременном поддержании эффективности в канале связи с AWGN (AWGN канал).

Пример конфигурации устройства 11 передачи

На фиг. 8 показана структурная схема примера конфигурации устройства 11 передачи с фиг. 7.

В устройстве 11 передачи один или несколько входных потоков, соответствующих целевым данным, подают в устройство 111 адаптации режима/мультиплексирования.

В устройстве 111 адаптации режима/мультиплексирования осуществляют выбор режима и, при необходимости, такие процессы, как мультиплексирование одного или нескольких поданных входных потоков, и подают полученные в результате данные в подстроечный конденсатор 112.

В подстроечном конденсаторе 112 осуществляют необходимое дополнение нулями (вставка пустот) данных, поданных из устройства 111 адаптации режима/мультиплексирования, и подают полученные в результате данные в устройство 113 ВВ скремблирования.

В устройстве 113 ВВ скремблирования осуществляют скремблирование основной полосы (ВВ скремблирование) данных, поданных из подстроечного конденсатора 112, и подают полученные в результате данные в устройство 114 ВСН кодирования.

В устройстве 114 ВСН кодирования осуществляют ВСН кодирование данных, поданных из устройства 113 ВВ скремблирования, и подают полученные в результате данные как целевые данные LDPC, являющиеся целью LDPC кодирования, в устройство 115 LDPC кодирования.

В устройстве 115 LDPC кодирования осуществляют LDPC кодирование в соответствии с проверочной матрицей, в которой матрица контроля четности, являющаяся частью, соответствующей биту четности LDPC-кода, обладает ступенчатой структурой для целевых данных LDPC, поданных из устройства 114 ВСН кодирования, и подают на выход LDPC-код, в котором целевыми данными LDPC являются информационные биты.

То есть в устройстве 115 LDPC кодирования осуществляют LDPC кодирование с целью кодирования целевых данных LDPC с использованием LDPC-кода, такого как LDPC-код (соответствующий проверочной матрице), определенный в заранее заданном стандарте DVB-S.2, DVB-T.2, DVB-C.2 или подобном, и как результат подают на выход полученный заранее заданный LDPC-код (соответствующий проверочной матрице) или подобный, полученный как результат.

LDPC-код, определенный в стандарте DVB-S.2, DVB-T.2 и DVB-C.2, является IRA-кодом (нерегулярный код повторения-накопления) и матрица контроля четности проверочной матрицы LDPC-кода имеет ступенчатую структуру. Далее будет описана матрица контроля четности и ступенчатая структура. IRA-код описан, например, в документе «Irregular Repeat-Accumulate Code», авторы X. Джин (Н. Jin), А. Хандекар (А. Khandekar) и Р.Дж. МакЭлис (R.J. McElece), опубликованном в материалах проходившего в сентябре 2000 года 2-го международного симпозиума по турбокодам и связанным с ними вопросам, стр. 1-8.

LDPC-код, полученный на выходе устройства 115 LDPC кодирования, подают в устройство 116 перемежения битов.

В устройстве 116 перемежения битов осуществляют описываемое ниже перемежение битов для LDPC-кода, поданного из устройства 115 LDPC кодирования, и подают LDPC-код после перемежения битов в устройство 117 преобразования.

В устройстве 117 преобразования осуществляют преобразование LDPC-кода, поданного из устройства 116 перемежения битов, в сигнальную точку, представляющую один символ ортогональной модуляции в блоке (блок символа) битов кода из одного или нескольких бит LDPC-кода, и осуществляют ортогональную модуляцию (многоуровневую модуляцию).

То есть в устройстве 117 преобразования осуществляют преобразование LDPC-кода, поданного из устройства 116 перемежения битов, в сигнальную точку, определенную способом модуляции для осуществления ортогональной модуляции LDPC-кода, на плоскости IQ (созвездие IQ), которая определена осью I, представляющей I компонент, который совпадает по фазе с несущей, и осью Q, представляющей Q компонент, который ортогонален несущей, и осуществляют ортогональную модуляцию.

В этом случае, в качестве способа ортогональной модуляции, осуществляемой в устройстве 117 преобразования, используют такие способы модуляции, как способ модуляции, определенный в стандартах DVB-S.2, DVB-T.2, DVB-C.2 и подобных, и другие способы модуляции, такие как BPSK (двоичная фазовая манипуляция), QPSK (квадратурная фазовая манипуляция), 8-позиционная PSK (фазовая манипуляция), 16-позиционная APSK (амплитудно-фазовая манипуляция), 32-позиционная APSK, 16-позиционная QAM (квадратурная амплитудная манипуляция), 64-позиционная QAM, 256-позиционная QAM, 1024-позиционная QAM, 4096-позиционная QAM, 4-позиционная РАМ (амплитудно-импульсная модуляция) или подобные. В устройстве 117 преобразования осуществляют ортогональную модуляцию, что делают на основе заранее установленного способа модуляции в соответствии с преобразованием, которое осуществляет оператор устройства 11 передачи.

Данные (результат преобразования, где символ преобразуют в сигнальную точку), которые получают при обработке в устройстве 117 преобразования, подают в устройство 118 перемежения по времени.

В устройстве 118 перемежения по времени осуществляют перемежения по времени (перемежения в направлении времени) в блоке символа для данных, поданных из устройства 117 преобразования, и подают полученные в результате данные в устройство 119 SISO/MISO кодирования (устройство SISO/MISO (Один вход один выход/несколько входов один выход) кодирования).

В устройстве 119 SISO/MISO кодирования осуществляют пространственно-временное кодирование данных, поданных из устройства 118 перемежения по времени, и подают данные в устройство 120 перемежения по частоте.

В устройстве 120 частотного уплотнения осуществляют перемежение по частоте (перемежение в направлении частоты) в блоке символа для данных, поданных из устройства 119 SISO/MISO кодирования, и подают данные в блок 131 построения кадра/выделения ресурса.

С другой стороны, например, данные управления (сигнализация) для управления передачей, такие как сигнализация основной полосы (сигнализация основной полосы) (ВВ заголовок), подают в устройство 121 ВСН кодирования.

В устройстве 121 ВСН кодирования, которое аналогично устройству 114 ВСН кодирования, осуществляют ВСН кодирование поданной сигнализации, и подают полученные в результате данные в устройство 122 LDPC кодирования.

В устройстве 122 LDPC кодирования, которое аналогично устройству 115 LDPC кодирования, устанавливают данные, поданные из устройства 121 ВСН кодирования, как целевые данные LDPC, осуществляют LDPC кодирование данных, и подают полученный в результате LDPC-код в устройство 123 преобразования.

В устройстве 123 преобразования, которое аналогично устройству 117 преобразования, осуществляют преобразование LDPC-кода, поданного из устройства 122 LDPC кодирования, в сигнальную точку, представляющую один символ ортогональной модуляции в блоке (символьный блок) битов кода из одного или нескольких битов LDPC-кода, осуществляют ортогональную модуляцию и подают полученные в результате данные в устройство 124 перемежения по частоте.

В устройстве 124 перемежения по частоте, которое аналогично устройству 120 перемежения по частоте, осуществляют перемежения по частоте в блоке символа для данных, поданных из устройства 123 преобразования, и подают данные в блок 131 построения кадра/выделения ресурса.

В блоке 131 построения кадра/выделения ресурса вставляют вспомогательные символы в необходимые позиции данных (символов), поданных из устройств 120 и 124 перемежения по частоте, конфигурируют кадр (например, кадр физического уровня (PL), Т2 кадр, С2 кадр и так далее), содержащий заранее заданное количество символов из полученных в результате данных (символов), и подают кадр в блок 132 генерирования OFDM.

В блоке 132 генерирования OFDM генерируют OFDM сигнал, соответствующий кадру из кадра, поданного из блока 131 построения кадра/выделения ресурса, и передают OFDM символ по каналу 13 связи (фиг. 7).

Здесь, например, устройство 11 передачи может быть выполнено без части блоков, показанных на фиг. 8, таких как устройство 118 перемежения по времени, устройство 119 SISO/MISO кодирования, устройство 120 перемежения по частоте и устройство 124 перемежения по частоте.

На фиг. 9 показан пример конфигурации устройства 116 перемежения битов с фиг. 8.

Устройство 116 перемежения битов содержит функцию для перемежения данных и содержит устройство 23 перемежения битов контроля четности, устройство 24 прокручивания столбцов и устройство 25 демультиплексирования (DEMUX). Здесь устройство 116 перемежения битов может быть выполнено без одного или обоих из следующих устройств: устройство 23 перемежения битов контроля четности и устройство 24 прокручивания столбцов.

В устройстве 23 перемежения битов контроля четности осуществляют перемежение битов контроля четности с целью перемежения битов контроля четности LDPC-кода, поданного из устройства 115 LDPC кодирования, на позиции других битов контроля четности, и подают LDPC-код после перемежения битов контроля четности в устройство 24 прокручивания столбцов.

В устройстве 24 прокручивания столбцов осуществляют прокручивание столбцов для LDPC-кода, поданного из устройства 23 перемежения битов контроля четности, и подают LDPC-код после прокручивания столбцов в устройство 25 демультиплексирования.

То есть в устройстве 117 преобразования с фиг. 8, биты кода, включающие в себя один или более битов LDPC-кода, преобразуют в сигнальную точку, представляющую один символ ортогональной модуляции и передают указанные биты кода.

В устройстве 24 прокручивания столбцов осуществляют описываемое ниже прокручивание столбцов, что выполняют как процесс перераспределения битов LDPC-кода, поданного из устройства 23 перемежения битов контроля четности, так что один символ не содержит нескольких битов LDPC-кода, которые соответствуют значению 1 и которые принадлежат любой одной строке проверочной матрицы, используемой в устройстве 115 LDPC кодирования.

В устройстве 25 демультиплексирования осуществляют процесс перестановки, заключающийся в перестановке позиций двух или более битов LDPC-кода, которые становятся символом, для LDPC-кода, поданного из устройства 24 прокручивания, и получают LDPC-код с увеличенной устойчивостью к AWGN и подобному. Кроме того, в устройстве 25 демультиплексирования подают два или более битов LDPC-кода, полученного в результате процесса перестановки, в качестве символа в устройство 117 преобразования (фиг. 8).

На фиг. 10 показана проверочная матрица Н, используемая для LDPC кодирования в устройстве 115 LDPC кодирования с фиг. 8.

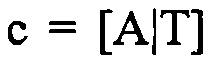

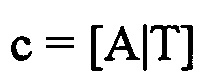

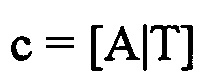

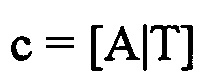

Проверочная матрица Н имеет LDGM (Низкоплотностная порождающая матрица) структуру и может быть представлена в следующем виде  (матрица, в которой элементы, расположенные на левой стороне, являются элементами информационной матрицы HA, а элементы, расположенные на правой стороне, являются элементами матрицы HT контроля четности), с использованием информационной матрицы HA, соответствующей информационным битам из битов LDPC-кода, и матрицы HT контроля четности, соответствующей битам контроля четности.

(матрица, в которой элементы, расположенные на левой стороне, являются элементами информационной матрицы HA, а элементы, расположенные на правой стороне, являются элементами матрицы HT контроля четности), с использованием информационной матрицы HA, соответствующей информационным битам из битов LDPC-кода, и матрицы HT контроля четности, соответствующей битам контроля четности.

В этом случае количество информационных битов среди битов LDPC-кода (одно кодовое слово) и количество битов контроля четности называют соответственно информационной длиной K и длиной М контроля четности, а количество битов в одном кодовом слове LDPC-кода называют длиной N кода (=K+М).

Информационная длина K и длина М контроля четности для LDPC-кода определенной длины N кода определяются скоростью кодирования. Проверочная матрица Н является матрицей, в которой количество строк × количество столбцов равно М×N. Информационная матрица HA является матрицей размера М×K, а матрица HT контроля четности является матрицей размера М×М.

На фиг. 11 показана матрица HT контроля четности для проверочной матрицы Н LDPC-кода, определенного в стандартах DVB-S.2, DVB-T.2 и DVB-C.2.

Матрица HT контроля четности для проверочной матрицы Н LDPC-кода, определенного в стандарте DVB-T.2 или подобных, имеет ступенчатую структуру (нижняя двухдиагональная матрица), в которой элементы, равные 1, расположены в форме ступенек, как показано на фиг. 11. Вес строки матрицы HT контроля четности равен 1 для первой строки и равен 2 для всех остальных строк. Вес последнего столбца равен 1, а для всех остальных столбцов вес столбца равен 2.

Как описано выше, LDPC-код, соответствующий проверочной матрице Н, в которой матрица HT контроля четности имеет ступенчатую структуру, может быть легко выработан с использованием проверочной матрицы Н.

То есть LDPC-код (одно кодовое слово) представляют в виде вектор-строки с, а вектор-столбец, полученный транспонированием вектор-строки, представляют в виде ст. Кроме того, часть вектор-строки с LDPC-кода, состоящую из информационных битов, представляют в виде вектор-строки А, а часть, состоящую из битов контроля четности, представляют в виде вектор-строки Т.

Вектор-строка с может быть представлена с помощью выражения  (вектор-строка, в которой элементы вектор-строки А являются элементами, расположенными слева, а элементы вектор-строки Т являются элементами, расположенными справа), с использованием вектор-строки А, соответствующей информационными битам, и вектор-строки Т, соответствующей битам контроля четности.

(вектор-строка, в которой элементы вектор-строки А являются элементами, расположенными слева, а элементы вектор-строки Т являются элементами, расположенными справа), с использованием вектор-строки А, соответствующей информационными битам, и вектор-строки Т, соответствующей битам контроля четности.

Для проверочной матрицы Н и вектор-строки  , соответствующей LDPC-коду, необходимо, чтобы выполнялось равенство HcT=0. Вектор-строка Т, которая соответствует битам контроля четности, содержащимся в вектор-строке

, соответствующей LDPC-коду, необходимо, чтобы выполнялось равенство HcT=0. Вектор-строка Т, которая соответствует битам контроля четности, содержащимся в вектор-строке  , которая удовлетворяет равенству HcT=0, может быть последовательно вычислена путем присвоения элементам каждой строки 0, что делают последовательно (по порядку), начиная с элементов первой строки вектор-столбца HcT из равенства HcT=0, где матрица HT контроля четности проверочной матрицы

, которая удовлетворяет равенству HcT=0, может быть последовательно вычислена путем присвоения элементам каждой строки 0, что делают последовательно (по порядку), начиная с элементов первой строки вектор-столбца HcT из равенства HcT=0, где матрица HT контроля четности проверочной матрицы  имеет ступенчатую структуру, показанную на фиг. 11.

имеет ступенчатую структуру, показанную на фиг. 11.

На фиг. 12 показана проверочная матрица Н LDPC-кода, определенного в стандарте DVB-T.2 или подобных.

Вес столбца равен X для KX столбцов, начиная с первого столбца проверочной матрицы Н LDPC-кода, определенной в стандарте DVB-T.2 или подобных, равен 3 для следующих K3 столбцов, равен 2 для следующих (М-1) столбцов и равен 1 для последнего столбца.

В этом случае сумма KX+K3+M-1+1 равна длине N кода.

На фиг. 13 показаны количества столбцов KX, K3 и М, а также вес X столбца для всех скоростей r кодирования LDPC-кода, определенного в стандарте DVB-T.2 или подобных стандартах.

В стандарте DVB-T.2 или подобных стандартах определены LDPC-коды, для которых длина N кода равна 64800 битам и 16200 битам.

Для LDPC-кода, длина N кода которого равна 64 800 битам, определено 11 скоростей кодирования (номинальные скорости) 1/4, 1/3, 2/5, 1/2, 3/5, 2/3, 3/4, 4/5, 5/6, 8/9 и 9/10. Для LDPC-кода, длина N кода которого равна 16 200 битам, определено 10 скоростей кодирования 1/4, 1/3, 2/5, 1/2, 3/5, 2/3, 3/4, 4/5, 5/6 и 8/9.

Здесь и далее, длина N кода, равная 64800 битам, называется длиной, равной 64 Кбитам, а длина N кода, равная 16200 битам, называется длиной, равной 16 Кбитам.

Для LDPC-кода частота появления ошибок обычно бывает низкой для бита кода, соответствующего столбцу с большим весом в проверочной матрице Н.

В проверочной матрице Н, которая показана на фиг. 12 и 13 и которая определена в стандарте DVB-T.2 или подобных стандартах, вес столбца верхней стороны (левой стороны) обычно бывает большим. Следовательно, для LDPC-кода, соответствующего проверочной матрице Н, бит кода верхней стороны обычно хорошо устойчив к появлению ошибки (существует устойчивость к появлению ошибки) и бит кода конечной стороны обычно слабо устойчив к появлению ошибки.

На фиг. 14 показан пример расположения (сигнальных точек, соответствующих) 16 символов на IQ плоскости, при этом 16-позиционную QAM осуществляют в устройстве 117 преобразования с фиг. 8.

То есть в участке А фиг. 14 показаны символы 16-позиционной QAM стандарта DVB-T.2 (сигнальная точка, соответствующая символу).

В 16-позиционной QAM один символ представлен 4 битами и существует 16 (=24) символов. 16 символов расположены так, что I направление × Q направление является квадратом 4×4 на основе исходной точки IQ плоскости.

Если (i+1)-й бит, начиная с самого старшего бита строки битов, представляющей один символ, обозначить через бит yi, то 4 бита, представляющие один символ из 16-позиционной QAM, могут быть последовательно представлены в виде битов y0, y1, y2 и y3, начиная с самого старшего бита. Когда способом модуляции является 16-позиционная QAM, то 4 бита из битов LDPC-кода представляют собой символ (значение символа) из 4 битов от y0 до y3 (являются символьным видом).

В участке В фиг. 14 показаны границы битов для каждого из 4 битов (здесь и далее также называют битами символа) от y0 до y3, которые представляют символ 16-позиционной QAM.

В этом случае, граница битов для бита yi символа (на фиг. 14, i=0, 1, 2 и 3) обозначает границу между символом, бит yi которого равен 0, и другим символом, бит yi которого равен 1.

Как ясно из участка В фиг. 14, для самого старшего бита y0 символа из 4 битов от y0 до y3 символа, представляющих символ 16-позиционной QAM, только одно расположение оси Q на IQ плоскости образует границу битов, а для второго бита y1 символа (второго по старшинству бита) только одно расположение оси I на IQ плоскости образует границу битов.

Для третьего бита y2 символа два места, а именно место между первым и вторым столбцами в левой стороне и место между третьим и четвертым столбцами из 4×4 символов, являются границами битов.

Для третьего бита y3 символа два места, а именно место между первой и второй строками в верхней стороне и место между третьей и четвертой строками из 4×4 символов, являются границами битов.

В битах у; символа, которые представляют символы, когда велико количество символов, находящихся в стороне от границ битов, ошибке трудно появиться (вероятность ошибки мала), а когда велико количество символов, близких к границам битов, ошибка появляется легко (вероятность ошибки велика).

Если биты, в которых ошибке трудно появиться (устойчивые к появлению ошибки), называют «сильными битами», а биты, в которых ошибка появляется легко (менее устойчивы к появлению ошибки), называют «слабыми битами», то среди 4 битов символа от y0 до y3, которые представляют символ 16-позиционной QAM, самый старший бит y0 символа и второй по старшинству бит y1 символа являются сильными битами, а третий бит y2 символа и четвертый бит y3 символа являются слабыми битами.

На фиг. 15-17 показаны примеры расположения 64 символов (соответствующих сигнальные точки) на IQ плоскости, то есть символы 16-позиционной QAM стандарта DVB-T.2, где 64-позиционную QAM осуществляют в устройстве 117 преобразования с фиг. 8.

В 64-позиционной QAM один символ представлен 6 битами и существует 64 (=26) символа. 64 символа расположены так, что I направление × Q направление является квадратом 8×8 на основе начальной точки IQ плоскости.

Биты одного символа 64-позиционной QAM могут быть последовательно представлены как y0, y1, y2 y3, y4 и y5, начиная с самого старшего бита. Когда способом модуляции является 64-позиционная QAM, то 6 битов из битов LDPC-кода представляют символ из 6 битов символа от y0 до y5.

В этом случае, на фиг. 15 показана граница битов для самого старшего бита y0 символа и второго бита y1 символа среди битов y0-y5 символов 64-позиционной QAM; на фиг. 16 показана граница битов для третьего бита y2 символа и для четвертого бита y3 символа, и на фиг. 17 показана граница битов для пятого бита y4 символа и для шестого бита y5 символа.

Как показано на фиг. 15, граница битов для самого старшего бита y0 символа и для второго бита y1 символа является единой. Как показано на фиг. 16, границы битов для третьего бита y2 символа и для четвертого бита y3 символа расположены в двух местах. Как показано на фиг. 17, границы битов для пятого бита y4 символа и для шестого бита y5 символа расположены в четырех местах.

Соответственно, для битов y0-y5 символа 64-позиционной QAM, самый старший бит y0 символа и второй бит y1 символа являются сильными битами и третий бит y2 символа и четвертый бит y3 символа являются следующими сильными битами. Кроме того, пятый бит y4 символа и шестой бит y5 символа являются слабыми битами.

Из фиг. 14 и 15-17, ясно, что для битов символа ортогональной модуляции расположенные выше биты обычно являются сильными битами, а расположенные ниже биты являются слабыми битами.

На фиг. 18 показан пример расположения 4 символов (соответствующих сигнальных точек) на IQ плоскости в случае, когда спутниковую схему используют в качестве канала 13 связи (фиг. 7) и QPSK осуществляют в устройстве 117 преобразования с фиг. 8, То есть, например, на фиг. 18 показано расположение сигнальных точек QPSK стандарта DVB-S.2.

В QPSK стандарта DVB-S.2 символ преобразуют в любую из 4 сигнальных точек на окружности с центром в начальной точке IQ плоскости и радиусом, равным ρ.

На фиг. 19 показан пример расположения 8 символов на IQ плоскости в случае, когда спутниковая схема используют в качестве канала 13 связи (фиг. 7) и 8-позиционную PSK осуществляют в устройстве 117 преобразования с фиг. 8, То есть, например, на фиг. 19 показано расположение сигнальных точек 8-позиционную PSK стандарта DVB-S.2.

В 8-позиционной PSK стандарта DVB-S.2 символ преобразуют в любую из 8 сигнальных точек на окружности с центром в начальной точке IQ плоскости и радиусом, равным р.

На фиг. 20 показан пример расположения 16 символов на IQ плоскости в случае, когда спутниковую схему используют в качестве канала 13 связи (фиг. 7) и 16-позиционную APSK осуществляют в устройстве 117 преобразования с фиг. 8, То есть, например, на фиг. 20 показано расположение сигнальных точек 16-позиционной APSK стандарта DVB-S.2.

В участке А фиг. 20 показано созвездие 16-позиционной APSK стандарта DVB-S.2.

В 16-позиционной APSK стандарта DVB-S.2 символ преобразуют в любую сигнальную точку из общего числа 16 сигнальных точек, состоящих из 4 сигнальных на окружности с центром в начальной точке IQ плоскости и радиусом R1 и 12 сигнальных точек на окружности с центром в начальной точке IQ плоскости и радиусом R2(R2>R1).

В участке В фиг. 20 показан параметр γ=R2/R1, который является отношением радиусов R2 и R1 в созвездии 16-позиционной APSK стандарта DVB-S.2.

В созвездии 16-позиционной APSK стандарта DVB-S.2 отношение у радиусов R2 и R1 разное при разных скоростях кодирования.

На фиг. 21 показан пример расположения 32 символов на IQ плоскости в случае, когда спутниковую схему используют в качестве канала 13 связи (фиг. 7) и 32-позиционную APSK осуществляют в устройстве 117 преобразования с фиг. 8, То есть, например, на фиг. 21 показано расположение сигнальных точек 32-позиционной APSK стандарта DVB-S.2.

В участке А фиг. 21 показано созвездие 32-позиционной APSK стандарта DVB-S.2.

В 32-позиционной APSK стандарта DVB-S.2 символ преобразуют в любую сигнальную точку из общего числа 32 сигнальных точек, состоящих из 4 сигнальных на окружности с центром в начальной точке IQ плоскости и радиусом R1, 12 сигнальных точек на окружности с центром в начальной точке IQ плоскости и радиусом R2 (R2>R1) и 16 сигнальных точек на окружности с центром в начальной точке IQ плоскости и радиусом R3 (R3>R2).

В участке В фиг. 21 показаны параметр γ1=R2/R1, который является отношением радиусов R2 и R1 в созвездии 32-позиционной APSK стандарта DVB-S.2, и параметр γ2=R3/R1, который является отношением радиусов R3 и R1.

В созвездии 32-позиционной APSK стандарта DVB-S.2 отношение γ1 радиусов R2 и R1 и отношение γ2 радиусов R3 и R1 разные при разных скоростях кодирования.

Даже для битов символов каждой квадратурной модуляции (QPSK, 8-позиционной PSK, 16-позиционной APSK и 32-позиционной APSK) стандарта DVB-S.2, которые показаны созвездием на фиг. 18 - фиг. 21, аналогично случаям с фиг. 14 - фиг. 17, существуют сильные и слабые биты.

Как показано на фиг. 12 и фиг. 13, для LDPC-кода, поданного на выход устройством 115 LDPC кодирования (фиг. 8) существуют устойчивые к ошибке биты кода и неустойчивые к ошибке биты кода.

Как показано на фиг. 14-21, среди битов символа ортогональной модуляции, осуществляемой в устройстве 117 преобразования, существуют сильные и слабые биты.

Соответственно, если биты LDPC-кода, устойчивые к появлению ошибок, выделяют для слабых битов символа ортогональной модуляции, то в целом устойчивость к появлению ошибок может снизиться.

Следовательно, предложено устройство перемежения, в котором разносят биты LDPC-кода таким образом, что биты LDPC-кода с низкой устойчивостью к появлению ошибок, выделяют для сильных битов (битов символа) символа ортогональной модуляции.

В устройстве 25 демультиплексирования с фиг. 9 могут осуществлять обработку данных, полученных от устройства перемежения.

На фиг. 22 показана обработка, осуществляемая в устройстве 25 демультиплексирования с фиг. 9.

То есть в участке А фиг. 22 показан пример конфигурации устройства 25 демультиплексирования.

Устройство 25 демультиплексирования содержит память 31 и блок 32 перестановки.

LDPC-код подают из устройства 115 LDPC кодирования в память 31.

Емкость памяти 31 такова, что она способна хранить mb битов в направлении строк (поперечном) и N/(mb) битов в направлении столбцов (продольном). В память 31 записывают поданные в нее биты LDPC-кода в направлении столбцов, считывают из памяти 31 биты кода в направлении строк и подают биты кода в блок 32 перестановки.

В этом случае N (=информационная длина K + длина М контроля четности) представляет собой длину LDPC-кода, как описано выше.

Кроме того, m является количеством битов LDPC-кода, представляющих один символ, a b является заранее заданным положительным целым числом и является множителем, который используют для умножения на число m. В устройстве 25 демультиплексирования преобразуют в символьный вид биты LDPC-кода в блок заранее заданных m бит. Тем не менее, множитель b представляет количество символов, полученных при однократном преобразовании в символьный вид, осуществляемом в устройстве 25 демультиплексирования.

В участке А фиг. 22 показан пример конфигурации устройства 25 демультиплексирования в случае, когда способом модуляции является 64-позиционная QAM или подобная, когда преобразование осуществляют с любую из 64 сигнальных точек и, следовательно, количество бит LDPC-кода для одного символа равно 6.

В участке А фиг. 22 множитель b равен 1. Следовательно, емкость памяти 31 в направлении столбцов × направление строк равна N/(6×1)×(6×1) битов.

В этом случае область хранения памяти 31, размер которой в направлении строк равен 1 и которая тянется в направлении столбцов, здесь и далее называют столбцом. В участке А фиг. 22 память 31 содержит 6 (=6×1) столбцов.

В устройстве 25 демультиплексирования запись битов LDPC-кода в направлении сверху вниз (направлении столбцов), начиная с верхней части столбцов, образующих память 31, осуществляют слева по направлению к столбцам правой стороны.

Если запись битов кода заканчивается внизу самого правого столбца, биты кода считывают блоками по 6 битов (mb битов) в направлении строк, начиная с первой строки, из всех столбцов, которые образуют память 31, и подают в блок 32 перестановки.

В блоке 32 перестановки осуществляют процесс перестановки, который заключается в перестановке позиций 6 битов кода из памяти 31, и подают полученные в результате 6 битов как биты y0, y1, y2 y3, y4 и y5, символа, которые представляют собой один символ 64-позиционной QAM.

То есть биты кода (в этом случае 6 битов) в количестве mb битов считывают из памяти 31 в направлении строк. Тем не менее, если i-й (i=0, 1, ... и mb-1) бит, начиная с самого старшего бита из битов кода в количестве mb бит, который считывают из памяти 31, обозначить как бит bi, биты кода в количестве 6 битов, которые считывают из памяти 31 в направлении строк, могут быть обозначены как биты b0, b1, b2 b3, b4 и b5, последовательно, начиная с самого старшего бита.

Что касается весов столбцов, описанных на фиг. 12 и 13, бит кода, расположенный в направлении бита b0, является битом кода, имеющим сильную устойчивость к появлению ошибки, а бит кода в направлении бита b5 является битом, имеющим слабую устойчивость к появлению ошибки.

В блоке 32 перестановки может быть осуществлен процесс перестановки, направленный на перестановку позиций битов b0-b5 кода в количестве 6 битов из памяти 31, при котором биты кода, слабо устойчивые к появлению ошибки, из битов b0-b5 кода в количестве 6 битов из памяти 31, сопоставляют сильным битам из битов y0-y5 символа 64-позиционной QAM.

В этом случае, в качестве способов перестановки, направленных на перестановку битов b0-b5 кода в количестве 6 битов из памяти 31 и сопоставление битам b0-b5 кода в количестве 6 битов битов y0-y5 символа, представляющих один символ 64-позиционной QAM, отдельными компаниями предложены различные способы.

В участке В фиг. 22 показан первый способ перестановки, в участке С фиг. 22 показан второй способ перестановки и в участке D фиг. 22 показан третий способ перестановки.

В участке В фиг. 22 и участке D фиг. 22 (аналогично фиг. 23, рассмотренной ниже) отрезок прямой, связывающий биты bi и yj обозначает, что бит bi кода сопоставляют биту yj символа (его переставляют на позицию бита yj символа).

В качестве первого способа перестановки из участка В фиг. 22 предложено использовать любой из трех типов способов перестановки. В качестве второго способа перестановки из участка С фиг. 22 предложено использовать любой из двух типов способов перестановки.

В качестве третьего способа перестановки из участка D фиг. 22 предложено последовательно выбрать и использовать любой из шести типов способов перестановки.

На фиг. 23 показан пример конфигурации устройства 25 демультиплексирования в случае, когда способом модуляции является 64-позиционная QAM или подобная, когда преобразование осуществляют с любой из 64 сигнальных точек (следовательно, количество m бит LDPC-кода преобразуемых в один символ равно 6, аналогично фиг. 22) и множитель b равен 2 и показан четвертый способ перестановки.

Когда множитель b равен 2, емкость памяти 31, в которой направление столбцов × направление строк равно N/(6×2)×(6×2) бит и содержит 12 (=6×2) столбцов.

В участке А фиг. 23 показан порядок записи LDPC-кода в память 31.

В устройстве 25 демультиплексирования, описанном на фиг. 22, запись битов LDPC-кода в направлении вниз (направлении столбцов), начиная с верхней части столбцов, образующих память 31, осуществляют слева по направлению к столбцам правой стороны.

Если запись битов кода заканчивается внизу самого правого столбца (если закончена запись кодового слова), биты кода считывают блоками по 12 битов (mb битов) в направлении строк, начиная с первой строки, из всех столбцов, которые образуют память 31, и подают в блок 32 перестановки.

В блоке 32 перестановки осуществляют процесс перестановки, который заключается в перестановке позиции 12 битов кода из памяти 31 с использованием четвертого способа перестановки и подают на выход полученные в результате 12 битов как 12 битов, которые представляют два символа (b символов) 64-позиционной QAM, то есть 6 битов y0, y1, y2 y3, y4 и y5 символа представляют один символ 64-позиционной QAM и 6 битов y0, y1, y2 y3, y4 и y5 символа представляют следующий символ.

В этом случае, в участке В фиг. 23 показан четвертый способ перестановки, соответствующий процессу перестановки, который осуществляют в блоке 32 перестановки из участка А фиг. 23.

Когда множитель b равен 2 (или 3 и более) в процессе перестановки mb битов кода сопоставляют mb битам символа b последовательных символов. В приведенном ниже объяснении, в том числе объяснении фиг. 23, для удобства описания (i+1)-й по старшинству бит среди mb битов символа для b последовательных символов обозначен как бит yj (бит символа).

Какие биты кода целесообразно переставлять, то есть улучшение частоты появления ошибок в AWGN канале связи или подобном, различается в зависимости от скорости кодирования или длины LDPC-кода и способа модуляции.

Перемежение битов контроля четности

Далее будет описано перемежение битов контроля четности, осуществляемое в устройстве 23 перемежения битов контроля четности с фиг. 9 со ссылками на фиг. 24-26.

На фиг. 24 показан (часть) граф Таннера проверочной матрицы LDPC-кода.

Как показано на фиг. 24, если в нескольких, например, двух переменных вершинах (соответствующих битах кода) из переменных вершин, соединенных с проверочной вершиной, одновременно появляется ошибка, такая как стирание, то проверочная вершина возвращает сообщение, для которого вероятность того, что значение равно 0, и вероятность того, что значение равно 1, равны для всех переменных вершин, соединенных с проверочной вершиной. По этой причине, если в нескольких переменных вершинах, соединенных с одной и той же проверочной вершиной, одновременно появляется ошибка, эффективность декодирования ухудшается.

Между тем, LDPC-код, полученный на выходе устройства 115 LDPC кодирования с фиг. 8 и определенный в стандарте DVB-S.2 или подобном, является IRA кодом и матрица HT контроля четности проверочной матрицы Н имеет ступенчатую структуру, показанную на фиг. 11.

На фиг. 25 показана матрица HT контроля четности, имеющая ступенчатую структуру, и показан граф Таннера, соответствующий этой матрице HT контроля четности.

То есть в участке А фиг. 25 показана матрица HT контроля четности, имеющая ступенчатую структуру, а в участке В фиг. 25 показан граф Таннера, соответствующий этой матрице HT контроля четности из участка А фиг. 25.

В матрице HT контроля четности, имеющей ступенчатую структуру, элементы, равные 1, расположены рядом в каждой строке (за исключением первой строки). Следовательно, в графе Таннера матрицы HT контроля четности две соседние переменные вершины, соответствующие столбцу с двумя соседними элементами, значение которых в матрице HT контроля четности равно 1, соединены с одной и той же проверочной вершиной.

Следовательно, когда в битах контроля четности, соответствующие двум упомянутым выше переменным вершинам, одновременно появляется ошибка стирания или пакетная ошибка и так далее, проверочная вершина, соединенная с двумя переменными вершинами (переменными вершинами для поиска сообщения с использованием битов контроля четности), соответствующим тем двум битам контроля четности, которые содержат ошибку, возвращают сообщение, для которого вероятность того, что значение равно 0, равна вероятности того, что значение равно 1, с переменными вершинами, соединенными с проверочной вершиной, и, следовательно, ухудшается эффективность декодирования. Более того, когда становится большой длина пакета (количество бит из непрерывных битов контроля четности, которые содержат ошибку), увеличивается количество проверочных вершин, которые возвращают сообщение с равной вероятностью, и дополнительно ухудшается эффективность декодирования.

Следовательно, в устройстве 23 перемежения битов контроля четности (фиг. 9) осуществляют перемежение битов контроля четности с целью перемежения битов контроля четности LDPC-кода, поданного из устройства 115 LDPC кодирования, на позиции других битов контроля четности, что делают для предотвращения ухудшения эффективности декодирования.

На фиг. 26 показана матрица HT контроля четности проверочной матрицы Н, соответствующей LDPC-коду, полученному после перемежения битов контроля четности, которое осуществляют в устройстве 23 перемежения битов контроля четности с фиг. 9.

В этом случае информационная матрица HA проверочной матрицы Н, соответствующей LDPC-коду, подаваемому на выход устройством 115 LDPC кодирования и определенному в стандарте DVB-S.2 или подобном, имеет циклическую структуру.

Циклическая структура является структурой, в которой любой столбец соответствует столбцу, полученному при циклическом сдвиге другого столбца. Например, циклическая структура содержит структуру, в которой положение 1 каждой строки Р столбцов является позицией, полученной циклическим сдвигом первого столбца из Р столбцов в направлении столбцов на значение, пропорциональное значению q, полученному делением длины М контроля четности, для каждого из Р столбцов. Здесь и далее, Р столбцов в циклической структуре соответственно называют количеством столбцов в блоке циклической структуры.

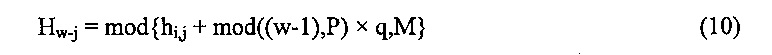

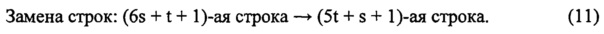

В качестве LDPC-кода, определенного в таком стандарте как DVB-S.2, показанного на фиг. 12 и фиг. 13, присутствуют два типа LDPC-кодов, для которых длина N кода равна 64800 битов и 16200 битов, и для обоих типов LDPC-кодов, количество Р столбцов, образующих блок циклической структуры, определяют как число 360, которое является одним из делителей, за исключением 1 и М, длины М контроля четности.

Длина М контроля четности является значением, отличным от простых чисел, и представленным в выражении M=q×P=q×360, с использованием различных значений q в соответствии со скоростью кодирования. Следовательно, аналогично количеству Р столбцов блока циклической структуры, значение q является одним из делителей длины М контроля четности, не совпадающим с 1 и М, и его получают делением длины М контроля четности на количество Р столбцов блока циклической структуры (произведение Р и q, которые являются делителями длины М контроля четности, равно длине М контроля четности).

Как описано выше, когда информационная длина обозначена через K, целое число, равное или большее 0 и меньшее Р, обозначено через x, целое число, равное или большее 0 и меньшее q, обозначено через у, в устройстве 23 перемежения битов контроля четности располагают K+qx+y+1-й бит кода среди битов LDPC-кода, количество которых равно N, на позиции K+Py+x+1-го бита кода, что делается в процессе перемежения битов.

Так как K+qx+y+1-й бит кода и K+Py+x+1-й бит кода являются битами кода после K+1-го бита, то они являются битами контроля четности и, следовательно, позиции битов контроля четности LDPC-кода перемещаются в соответствии с разнесением битов.

В соответствии с разнесением битов, переменные вершины (соответствующие биты контроля четности), соединенные с одной и той же проверочной вершиной, отделены Р столбцами блока циклической структуры, то есть 360 битами в рассматриваемом случае. По этой причине, когда длина пакета меньше 360 битов, предотвращается одновременное появление ошибки во множестве переменных вершин, соединенных с одной и той же проверочной вершиной. В результате может быть улучшена устойчивость к пакетной ошибке.

LDPC-код после перемежения, заключающегося в расположении (K+qx+y+1)-го бита кода на позиции (K+Py+x+1)-го бита кода, соответствует LDPC-коду с проверочной матрицей (здесь и далее также называем преобразованной проверочной матрицей), полученной заменой столбцов, которая заключается в замене (K+qx+y+1)-го столбца исходной проверочной матрицы Н на (K+Py+x+1)-й столбец.

В матрице контроля четности преобразованной проверочной матрицы Н, как показано на фиг. 26, появляется псевдоциклическая структура, в которой в качестве блока используется Р столбцов (на фиг. 26, 360 столбцов).

В этом случае под псевдоциклической структурой понимают структуру, в которой сформирована циклическая структура за исключением ее некоторой части. Преобразованная проверочная матрица, которая получена при осуществлении замены столбцов в соответствии с разнесением битов для проверочной матрицы LDPC-кода, определенного в стандарте DVB-S.2 или подобных, обладает псевдоциклической структурой, а не (точной) циклической структурой, так как количество элементов, равных 1, меньше 1 (существуют элементы, равные 0) в части (матрица со сдвигом, которая будет описана ниже) из 360 строк × 360 столбцов в правой угловой части преобразованной проверочной матрицы.

Преобразованная проверочная матрица с фиг. 26 является матрицей, которая получена при осуществлении замены столбцов в соответствии с разнесением битов контроля четности и заменой (замена строк) строк с целью сопоставления преобразованной проверочной матрицы с составляющей матрицей, описанной ниже, при этом указанные выше преобразования осуществляют с исходной проверочной матрицей Н.

Прокручивание столбцов

Далее, со ссылками на фиг. 27-30 будет описано прокручивание столбцов, соответствующее процессу перераспределения, осуществляемому в устройстве 24 прокручивания столбцов с фиг. 9.

В устройстве 11 передачи с фиг. 8 один или более битов LDPC-кода передают в виде одного символа. То есть, когда 2 бита кода установлены в качестве одного символа, в качестве способа модуляции используют QPSK, а когда 4 бита кода установлены в качестве одного символа, в качестве способа модуляции используют APSK или 16-позиционную QAM.

Фактически, когда два или более битов кода передают в виде одного символа и если в некотором символе произойдет стирание, то все биты кода этого символа становятся ошибочными (стирание).

Следовательно, с целью улучшения эффективности декодирования необходимо предотвратить ситуацию, когда переменные вершины, соответствующие битам кода одного символа, соединены с одной и той же проверочной вершиной, что нужно для уменьшения вероятности того, что в нескольких переменных вершинах (соответствующие биты кода), соединенных с одной и той же проверочной вершиной, одновременно появляется ошибка.

При этом, как описано выше, в проверочной матрице Н LDPC-кода, который подает на выход устройство 115 LDPC кодирования и который определен в стандарте DVB-S.2 или подобном, информационная матрица HA обладает циклической структурой, а матрица HT контроля четности обладает ступенчатой структурой. Как показано на фиг. 26, в преобразованной проверочной матрице, которая является проверочной матрицей LDPC-кода после выполнения перемежения битов контроля четности, циклическая структура (фактически псевдоциклическая структура, описанная выше) также появляется в матрице контроля четности.

На фиг. 27 показана преобразованная проверочная матрица.

То есть в участке А фиг. 27 показана преобразованная проверочная матрица для проверочной матрицы Н LDPC-кода, для которого длина N кода равна 64800 битам, а скорость (r) кодирования равна 3/4.

В участке А фиг. 27 в преобразованной проверочной матрице позиция элемента, значение которого равно 1, показана точкой (.).

В участке В фиг. 27 показана обработка, осуществляемая в устройстве 25 демультиплексирования (фиг. 9) для LDPC-кода с преобразованной проверочной матрицей из участка А фиг. 27, то есть для LDPC-кода после перемежения битов контроля четности.

В участке В фиг. 27, с предположением, что способ модуляции является способом, в котором символ преобразуют в любую из 16 сигнальных точек, таким как 16-позиционная APSK и 16-позиционная QAM, биты LDPC-кода после перемежения битов контроля четности записывают в направлении столбов в четыре столбца, которые образуют память 31 устройства 25 демультиплексирования.

Биты кода, записанные в направлении столбцов в четыре столбца, которые образуют память 31, считывают в направлении строк в блоки по 4 бита, которые образуют один символ.

В этом случае биты B0, B1, B2 и B3 кода в количестве четырех штук, которые образуют один символ, могут являться битами кода, соответствующими 1, в любой одной строке преобразованной проверочной матрицей из участка А фиг. 27. В этом случае переменные вершины, соответствующие битам B0, B1, B2 и B3 кода, соединены с одной и той же проверочной вершиной.

Следовательно, когда 4 бита B0, B1, B2 и B3 кода одного символа являются битами кода, соответствующими 1 в одной произвольной строке преобразованной проверочной матрицы, и если произойдет стирание символа, то надлежащее сообщение может быть не вычислено в проверочной вершине, к которой присоединены переменные вершины, соответствующие битам B0, B1, B2 и B3 кода. В результате ухудшается эффективность декодирования.

Что касается скоростей кодирования, отличающихся от скорости кодирования, равной 3/4, несколько битов кода, соответствующих нескольким переменным вершинам, соединенным с одной и той же проверочной вершиной, могут являться одним символом APSK или 16-позиционной QAM, аналогично приведенному выше случаю.

Следовательно, в устройстве 24 прокручивания столбцов осуществляют прокручивание столбцов, при котором биты LDPC-кода после перемежения битов контроля четности, которое выполняют в устройстве 23 перемежения битов контроля четности, разносят так, что несколько битов кода, значения которых соответствуют 1 в любой одной произвольной строке преобразованной проверочной матрицы, не содержатся в одном символе.

На фиг. 28 показано прокручивание столбцов.

То есть на фиг. 28 показана память 31 (фиг. 22 и 23) устройства 25 демультиплексирования.