Предлагаемое изобретение относится к цифровой вычислительной технике и может быть использовано для формирования цифровых сигналов управления элементом манчестерской цепи переноса.

Известно электронное устройство - «Схема управления элементом манчестерской цепи переноса» [1]. Указанное устройство предназначено для формирования четырех сигналов, описываемых логическими функциями: G; D; Р; Р, которые необходимы для обеспечения правильной работы «Манчестерской цепи переноса» (см. Рис. 11.8 [2]).

Данная «Схема управления элементом манчестерской цепи переноса» [1] содержит два инвертора (1, 2), один двухвходовой логический элемент И-НЕ (3) и два двухвходовых логических элемента ИЛИ-НЕ (4, 5).

Таким образом, для того чтобы выполнить перечисленные логические элементы в КМОП базисе, согласно [2] (Рис. 6.17), потребуется шестнадцать МОП транзисторов.

Недостатком описанной выше схемы является то, что она содержит большое количество элементов и, следовательно, требует большого количества коммутационных связей. Так как надежность любого физического объекта не является абсолютной и прямо зависит от количества компонентов в его составе и количества связей, соединяющих эти компоненты, то использование при создании любого устройства большего количества компонентов и связей между ними снижает надежность работы такого устройства.

Кроме того, использование большего количества компонентов и связей при создании устройства приводит к увеличению его массогабаритных показателей, в данном случае - «Схемы управления элементом манчестерской цепи переноса» [1].

Задачей предлагаемого изобретения является повышение надежности Схемы управления элементом манчестерской цепи переноса и снижение его массогабаритных показателей.

Поставленная задача достигается тем, что в «Схему управления элементом манчестерской цепи переноса» [1], содержащую двухвходовой логический элемент И-НЕ, выход которого является выходом сигнала Генерация-НЕ  , двухвходовой логический элемент ИЛИ-НЕ, выход которого является выходом сигнала Удаление D, вход операнда А, соединенный с первыми входами двухвходовых логических элементов И-НЕ и ИЛИ-НЕ, вход операнда В, соединенный со вторыми входами двухвходовых логических элементов И-НЕ и ИЛИ-НЕ, первый инвертор, вход которого соединен с выходом двухвходового логического элемента И-НЕ, второй инвертор, выход которого является прямым сигналом Распространение Р, а вход инверсным - Распространение-НЕ

, двухвходовой логический элемент ИЛИ-НЕ, выход которого является выходом сигнала Удаление D, вход операнда А, соединенный с первыми входами двухвходовых логических элементов И-НЕ и ИЛИ-НЕ, вход операнда В, соединенный со вторыми входами двухвходовых логических элементов И-НЕ и ИЛИ-НЕ, первый инвертор, вход которого соединен с выходом двухвходового логического элемента И-НЕ, второй инвертор, выход которого является прямым сигналом Распространение Р, а вход инверсным - Распространение-НЕ  , введены МОП транзистор Р-типа, затвор которого соединен с выходом двухвходового логического элемента ИЛИ-НЕ, исток - с выходом двухвходового логического элемента И-НЕ, а сток - с входом второго инвертора, и два МОП транзистора N-типа, затвор одного из которых соединен с выходом двухвходового логического элемента ИЛИ-НЕ, а другого - с выходом первого инвертора, стоки обоих МОП транзисторов N-типа - с входом второго инвертора, а истоки - с шиной источника питания низкого уровня напряжения GND.

, введены МОП транзистор Р-типа, затвор которого соединен с выходом двухвходового логического элемента ИЛИ-НЕ, исток - с выходом двухвходового логического элемента И-НЕ, а сток - с входом второго инвертора, и два МОП транзистора N-типа, затвор одного из которых соединен с выходом двухвходового логического элемента ИЛИ-НЕ, а другого - с выходом первого инвертора, стоки обоих МОП транзисторов N-типа - с входом второго инвертора, а истоки - с шиной источника питания низкого уровня напряжения GND.

В предлагаемой схеме формирователя управляющих сигналов, полностью выполняющей функцию схемы управления элементом манчестерской цепи переноса, вместо второго двухвходового логического элемента ИЛИ-НЕ введено три МОП транзистора - один Р-типа и два N-типа. В то же время согласно [2] (Рис. 6.17) известно, что для реализации двухвходового логического элемента ИЛИ-НЕ в КМОП базисе требуется четыре МОП транзистора - два Р-типа и два N-типа.

Таким образом, предлагаемая схема формирователя управляющих сигналов позволяет из схемы управления элементом манчестерской цепи переноса исключить один транзистор. Это уменьшает общее количество транзисторов, требуемое для реализации необходимых функций, а значит и общее количество связей, соединяющих эти транзисторы с остальной частью схемы и между собой, и тем самым позволяет повысить надежность схемы формирователя управляющих сигналов и уменьшить ее массогабаритные показатели.

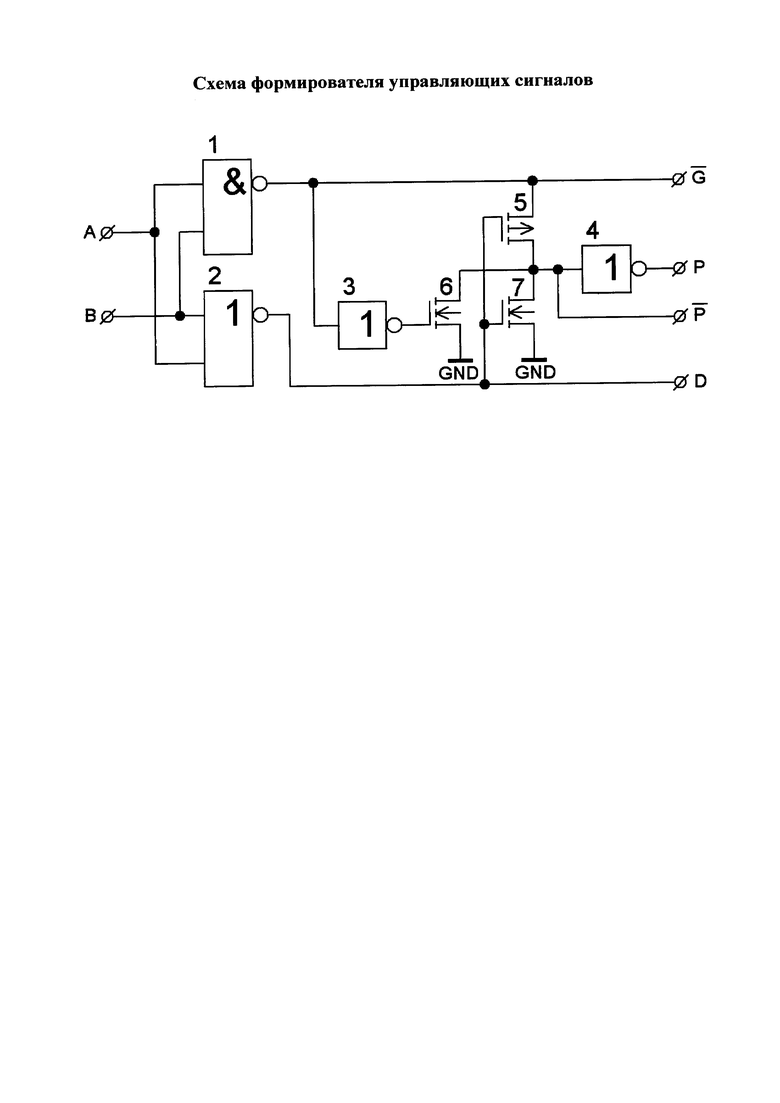

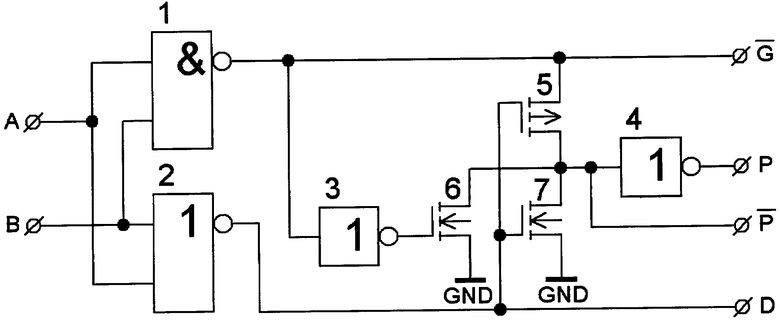

На чертеже приведена схема формирователя управляющих сигналов.

Предлагаемая схема формирователя управляющих сигналов содержит двухвходовой логический элемент И-НЕ 1, выход которого является выходом сигнала Генерация-НЕ  , двухвходовой логический элемент ИЛИ-НЕ 2, выход которого является выходом сигнала Удаление D, вход операнда А, соединенный с первыми входами двухвходовых логических элементов И-НЕ 1 и ИЛИ-НЕ 2, вход операнда В, соединенный со вторыми входами двухвходовых логических элементов И-НЕ 1 и ИЛИ-НЕ 2, первый инвертор 3, вход которого соединен с выходом двухвходового логического элемента И-НЕ 1, второй инвертор 4, выход которого является прямым сигналом Распространение Р, а вход инверсным - Распространение-НЕ

, двухвходовой логический элемент ИЛИ-НЕ 2, выход которого является выходом сигнала Удаление D, вход операнда А, соединенный с первыми входами двухвходовых логических элементов И-НЕ 1 и ИЛИ-НЕ 2, вход операнда В, соединенный со вторыми входами двухвходовых логических элементов И-НЕ 1 и ИЛИ-НЕ 2, первый инвертор 3, вход которого соединен с выходом двухвходового логического элемента И-НЕ 1, второй инвертор 4, выход которого является прямым сигналом Распространение Р, а вход инверсным - Распространение-НЕ  , МОП транзистор Р-типа 5, затвор которого соединен с выходом двухвходового логического элемента ИЛИ-НЕ 2, исток - с выходом двухвходового логического элемента И-НЕ 1, а сток - с входом второго инвертора 4, первый МОП транзистор N-типа 6, затвор которого соединен с выходом первого инвертора 3, сток - с входом второго инвертора 4, а исток - с шиной питания низкого уровня напряжения GND, и второй МОП транзистор N-типа 7, затвор которого соединен с выходом двухвходового логического элемента ИЛИ-НЕ 2, сток - с входом второго инвертора 4, а исток - с шиной питания низкого уровня напряжения GND.

, МОП транзистор Р-типа 5, затвор которого соединен с выходом двухвходового логического элемента ИЛИ-НЕ 2, исток - с выходом двухвходового логического элемента И-НЕ 1, а сток - с входом второго инвертора 4, первый МОП транзистор N-типа 6, затвор которого соединен с выходом первого инвертора 3, сток - с входом второго инвертора 4, а исток - с шиной питания низкого уровня напряжения GND, и второй МОП транзистор N-типа 7, затвор которого соединен с выходом двухвходового логического элемента ИЛИ-НЕ 2, сток - с входом второго инвертора 4, а исток - с шиной питания низкого уровня напряжения GND.

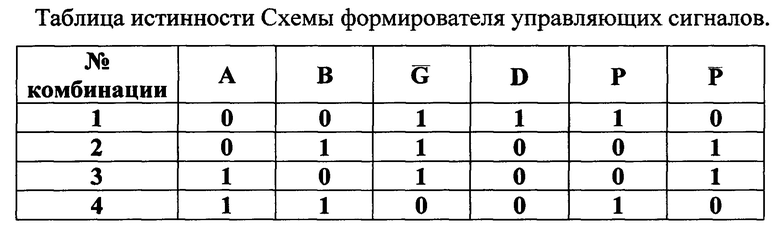

Предлагаемая схема формирователя управляющих сигналов предназначена для формирования сигналов Генерация-НЕ  , Удаление D, Распространение Р и Распространение-НЕ

, Удаление D, Распространение Р и Распространение-НЕ  , значение которых представлено ниже в Таблице истинности схемы формирователя управляющих сигналов.

, значение которых представлено ниже в Таблице истинности схемы формирователя управляющих сигналов.

Таким образом, предлагаемая схема формирователя управляющих сигналов представляет собой логическую схему комбинационного типа и работает следующим образом.

В комбинации №1 на входы операндов А и В поступает напряжение низкого уровня, которое соответствует логическому значению «0» таблицы истинности схемы формирователя управляющих сигналов. Так как входы операндов А и В соединены с входами, соответственно первым и вторым, двухвходовых логических элементов И-НЕ 1 и ИЛИ-НЕ 2, то на их выходах, в соответствии с выполняемыми этими элементами функциями, формируется напряжение высокого уровня, которое соответствует логическому значению «1» таблицы истинности схемы формирователя управляющих сигналов. Напряжение высокого уровня «1», сформированное на выходе двухвходового логического элемента И-НЕ 1 поступает на выход  схемы формирователя управляющих сигналов, исток МОП транзистора Р-типа 5 и вход первого инвертора 3, в результате чего на его выходе формируется инверсное напряжение низкого уровня «0», которое поступает на затвор первого МОП транзистора N-типа 6. Поэтому первый МОП транзистор N-типа 6 закрывается.

схемы формирователя управляющих сигналов, исток МОП транзистора Р-типа 5 и вход первого инвертора 3, в результате чего на его выходе формируется инверсное напряжение низкого уровня «0», которое поступает на затвор первого МОП транзистора N-типа 6. Поэтому первый МОП транзистор N-типа 6 закрывается.

Одновременно напряжение высокого уровня «1», сформированное на выходе двухвходового логического элемента ИЛИ-НЕ 2 поступает на затворы МОП транзисторов Р-типа 5 и второго МОП транзистора N-типа 7 и выход D схемы формирователя управляющих сигналов. Поэтому МОП транзистор Р-типа 5 закрывается, а второй МОП транзистор N-типа 7 - открывается, и через него на выход  схемы формирователя управляющих сигналов и на вход второго инвертора 4 поступает напряжение низкого уровня «0», которое поступает на выход Р схемы формирователя управляющих сигналов. Таким образом, значения сформированных напряжений логических сигналов на выходах

схемы формирователя управляющих сигналов и на вход второго инвертора 4 поступает напряжение низкого уровня «0», которое поступает на выход Р схемы формирователя управляющих сигналов. Таким образом, значения сформированных напряжений логических сигналов на выходах  , D, Р и

, D, Р и  полностью соответствуют комбинации №1 таблицы истинности схемы формирователя управляющих сигналов.

полностью соответствуют комбинации №1 таблицы истинности схемы формирователя управляющих сигналов.

В комбинации №2(3) на вход операнда А(В) поступает напряжение низкого уровня «0», а на вход В(А) - высокого «1». Так как входы операндов А и В соединены с входами, соответственно первым и вторым, двухвходовых логических элементов И-НЕ 1 и ИЛИ-НЕ 2, то на их выходах, в соответствии с выполняемыми этими элементами функциями, формируется напряжение высокого уровня «1» - на выходе двухвходового логического элемента И-НЕ 1 и низкого уровня «0» - на выходе двухвходового логического элемента ИЛИ-НЕ 2.

Напряжение высокого уровня «1», сформированное на выходе двухвходового логического элемента И-НЕ 1, поступает на выход  схемы формирователя управляющих сигналов и на вход первого инвертора 3, в результате чего на его выходе формируется инверсное напряжение низкого уровня «0», которое поступает на затвор первого МОП транзистора N-типа 6. Поэтому первый МОП транзистор N-типа 6 закрывается. Одновременно напряжение низкого уровня «0», сформированное на выходе двухвходового логического элемента ИЛИ-НЕ 2, поступает на затворы МОП транзисторов Р-типа 5, второго МОП транзистора N-типа 7 и выход D Схемы формирователя управляющих сигналов. Поэтому второй МОП транзистор N-типа 7 закрывается, а МОП транзистор Р-типа 5 открывается, и через него на выход

схемы формирователя управляющих сигналов и на вход первого инвертора 3, в результате чего на его выходе формируется инверсное напряжение низкого уровня «0», которое поступает на затвор первого МОП транзистора N-типа 6. Поэтому первый МОП транзистор N-типа 6 закрывается. Одновременно напряжение низкого уровня «0», сформированное на выходе двухвходового логического элемента ИЛИ-НЕ 2, поступает на затворы МОП транзисторов Р-типа 5, второго МОП транзистора N-типа 7 и выход D Схемы формирователя управляющих сигналов. Поэтому второй МОП транзистор N-типа 7 закрывается, а МОП транзистор Р-типа 5 открывается, и через него на выход  схемы формирователя управляющих сигналов и на вход второго инвертора 4 поступает напряжение низкого уровня «1», которое поступает на выход Р схемы формирователя управляющих сигналов. Таким образом, значения сформированных напряжений логических сигналов на выходах

схемы формирователя управляющих сигналов и на вход второго инвертора 4 поступает напряжение низкого уровня «1», которое поступает на выход Р схемы формирователя управляющих сигналов. Таким образом, значения сформированных напряжений логических сигналов на выходах  , D, Р и

, D, Р и  полностью соответствуют комбинации №2(3) таблицы истинности схемы формирователя управляющих сигналов.

полностью соответствуют комбинации №2(3) таблицы истинности схемы формирователя управляющих сигналов.

В комбинации №4 на входы операндов А и В поступает напряжение высокого уровня «1». Так как входы операндов А и В соединены с входами, соответственно первым и вторым, двухвходовых логических элементов И-НЕ 1 и ИЛИ-НЕ 2, то на их выходах, в соответствии с выполняемыми этими элементами функциями, формируется напряжение низкого уровня «0». Напряжение низкого уровня «0», сформированное на выходе двухвходового логического элемента И-НЕ 1, поступает на выход  схемы формирователя управляющих сигналов, исток МОП транзистора Р-типа 5 и вход первого инвертора 3, в результате чего на его выходе формируется инверсное напряжение высокого уровня «1», которое поступает на затвор первого МОП транзистора N-типа 6. Поэтому первый МОП транзистор N-типа 6 открывается и через него напряжение низкого уровня «0» поступает на выход

схемы формирователя управляющих сигналов, исток МОП транзистора Р-типа 5 и вход первого инвертора 3, в результате чего на его выходе формируется инверсное напряжение высокого уровня «1», которое поступает на затвор первого МОП транзистора N-типа 6. Поэтому первый МОП транзистор N-типа 6 открывается и через него напряжение низкого уровня «0» поступает на выход  и вход второго инвертора 4.

и вход второго инвертора 4.

Одновременно напряжение низкого уровня «0», сформированное на выходе двухвходового логического элемента ИЛИ-НЕ 2, поступает на затворы МОП транзисторов Р-типа 5 и второго МОП транзистора N-типа 7 и выход D схемы формирователя управляющих сигналов. Поэтому второй МОП транзистор N-типа 7 закрывается, а МОП транзистор Р-типа 5 открывается и через него на выход  схемы формирователя управляющих сигналов и на вход второго инвертора 4 также поступает напряжение низкого уровня «0». Так как на входе второго инвертора 4 напряжение низкого уровня «0», то на его выходе формируется инверсное напряжение высокого уровня «1», которое поступает на выход Р схемы формирователя управляющих сигналов. Таким образом, значения сформированных напряжений логических сигналов на выходах

схемы формирователя управляющих сигналов и на вход второго инвертора 4 также поступает напряжение низкого уровня «0». Так как на входе второго инвертора 4 напряжение низкого уровня «0», то на его выходе формируется инверсное напряжение высокого уровня «1», которое поступает на выход Р схемы формирователя управляющих сигналов. Таким образом, значения сформированных напряжений логических сигналов на выходах  , D, Р и

, D, Р и  полностью соответствуют комбинации №4 таблицы истинности схемы формирователя управляющих сигналов.

полностью соответствуют комбинации №4 таблицы истинности схемы формирователя управляющих сигналов.

Литература

1. Глухов А.В., Шубин В.В. Патент на изобретение РФ №2554853, G06F 7/503 (2006.01), Схема управления элементом манчестерской цепи переноса, Федеральная служба по интеллектуальной собственности, бюллетень №18, 27.06.2015 г.

2. Цифровые интегральные схемы. Методология проектирования / Б. Николич, Ж. Рабаи, А. Чандракасан // Изд. Дом «Вильяме», 2-изд. - г. Москва, 2007.

| название | год | авторы | номер документа |

|---|---|---|---|

| СХЕМА ФОРМИРОВАТЕЛЯ УПРАВЛЯЮЩИХ СИГНАЛОВ | 2020 |

|

RU2749178C1 |

| АДРЕСНЫЙ ФОРМИРОВАТЕЛЬ | 1991 |

|

RU2010361C1 |

| СХЕМА УПРАВЛЕНИЯ ЭЛЕМЕНТОМ МАНЧЕСТЕРСКОЙ ЦЕПИ ПЕРЕНОСА | 2014 |

|

RU2562754C1 |

| СХЕМА УПРАВЛЕНИЯ ЭЛЕМЕНТОМ МАНЧЕСТЕРСКОЙ ЦЕПИ ПЕРЕНОСА | 2014 |

|

RU2554853C1 |

| ОДНОРАЗРЯДНЫЙ ДВОИЧНЫЙ СУММАТОР | 2009 |

|

RU2408922C1 |

| ЛОГИЧЕСКОЕ КОНВЕЙЕРНОЕ УСТРОЙСТВО | 2000 |

|

RU2175811C1 |

| КОМПАРАТОР ДВОИЧНЫХ ЧИСЕЛ | 2021 |

|

RU2762061C1 |

| Устройство сбоеустойчивого разряда самосинхронного регистра хранения | 2020 |

|

RU2733263C1 |

| Входное устройство для электронных часов | 1990 |

|

SU1774471A1 |

| СУММАТОР | 2008 |

|

RU2380739C1 |

Изобретение относится к вычислительной технике. Технический результат – повышение надежности и уменьшение массогабаритных показателей. Схема формирователя управляющих сигналов содержит двухвходовой логический элемент И-НЕ, выход которого является выходом сигнала Генерация-НЕ (

Схема формирователя управляющих сигналов содержит двухвходовой логический элемент И-НЕ, выход которого является выходом сигнала Генерация-НЕ (

| СХЕМА УПРАВЛЕНИЯ ЭЛЕМЕНТОМ МАНЧЕСТЕРСКОЙ ЦЕПИ ПЕРЕНОСА | 2014 |

|

RU2554853C1 |

| Узел формирования переноса в сумматоре | 1985 |

|

SU1291969A1 |

| БРОНЕФУТЕРОВКА БАРАБАННЫХ МЕЛЬНИЦ САМОИЗМЕЛЬЧЕНИЯ | 0 |

|

SU360971A1 |

| KR 20010047845 A, 15.06.2001 | |||

| US 5140546 A, 18.08.1992 | |||

| JPH 01250137 A, 05.10.1989. | |||

Авторы

Даты

2018-08-14—Публикация

2017-07-04—Подача